International Workshop for Advanced System Integration and Packaging brings together leaders in microelectronic systems to tackle industry challenges

Organized by Purdue University’s Institute for Advanced System Integration and Packaging (ASIP), an international workshop Dec. 5-6 at Purdue’s Ross-Ade Stadium will feature globally acclaimed industry and academic leaders to address the challenges of research, “lab-to-fab” translation and necessary workforce to build future microelectronic systems.

Representing Advanced Micro Devices (AMD), IBM, imec, Intel, Joint2 Consortium of Japan and SK Hynix, these experts will explore solutions involving system architectural and physical design enabled by multiphysics modeling tools, high-density interposers and substrates, process development for interconnect pitch scaling, and thermal solution design, all while meeting reliability and manufacturing yield goals.

The workshop will bring together integrated device manufacturers, fabless companies, Electronics Design Automation (EDA) companies, tool vendors, materials suppliers, outsourced semiconductor assembly and test vendors, national labs and academics to describe current capabilities, identify challenges and develop partnerships in pursuit of future programmatic opportunities. Senior leaders from the CHIPS for America Office will present their vision and participate in a panel discussion of opportunities and partnerships for the nation.

The workshop is organized in partnership with Applied Research Institute, a non-partisan leader in technology innovation and strategy and host of the Silicon Crossroads Microelectronics Commons Hub. Additional partners are imec USA, Cadence and Osaka University.

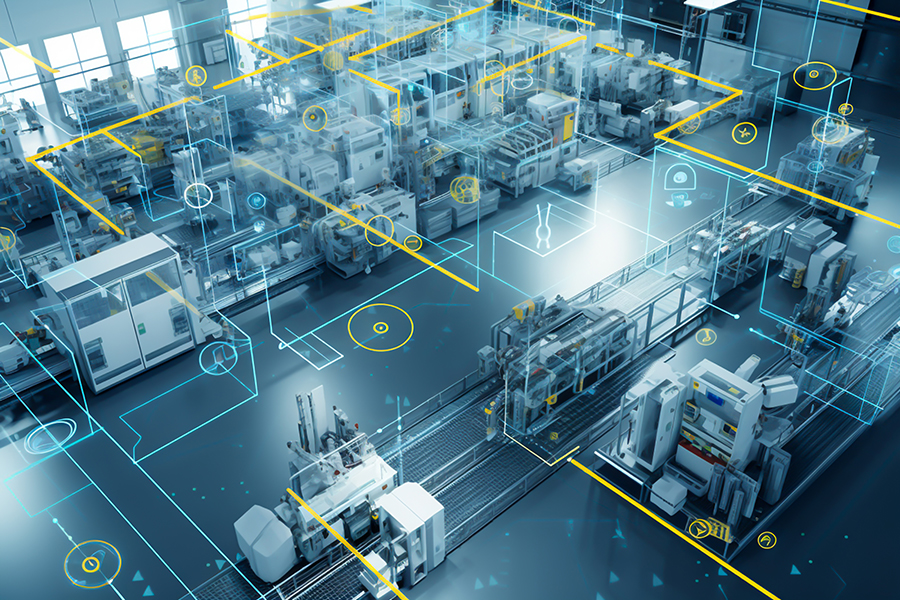

As transistor scaling according to Moore’s law slows, future applications will require novel system integration solutions to achieve performance, power and cost tradeoffs while ensuring efficient power conversion and delivery, signal and power integrity, sustainability, testability and security goals. Increasingly, future electronic systems for computing, mobile communications, IoT, automotive, defense and biological applications will rely on advanced integration of separately manufactured chiplets into a 2.5D/3D System-in-Package (SiP).

Major Japanese material and equipment suppliers scheduled to be represented at the workshop include AGC, Horiba, Mitsubishi Chemical, Okuno Chemical Industries, Resonac, Toray, TOWA Corporation and Yamato Scientific.

Sessions also will highlight Purdue ASIP research and education. A tour of Purdue’s Birck Nanotechnology Center, including its Scifres Nanofabrication Laboratory, will be held following lunch on Dec. 5. In addition, a poster session will display work of over 30 undergraduate and graduate students.

This workshop illustrates how ASIP institute and Purdue University are forging the future of microelectronics by advancing the frontiers of knowledge in a critical field like advanced packaging and convening key stakeholders in an industry-academia-government dialogue.