Performance Analysis of SiGe/Si core/shell NWFETs

| Performance analysis of SiGe/Si core/shell NWFETs | Abhijeet Paul, Saumitra Mehrotra, Mathieu Luisier and Gerhard Klimeck |

|

Objective:

Approach:

Result:

Impact: Work Published in IEEE, EDL, 31, 2010. doi: 10.1109/LED.2010.2040577 |

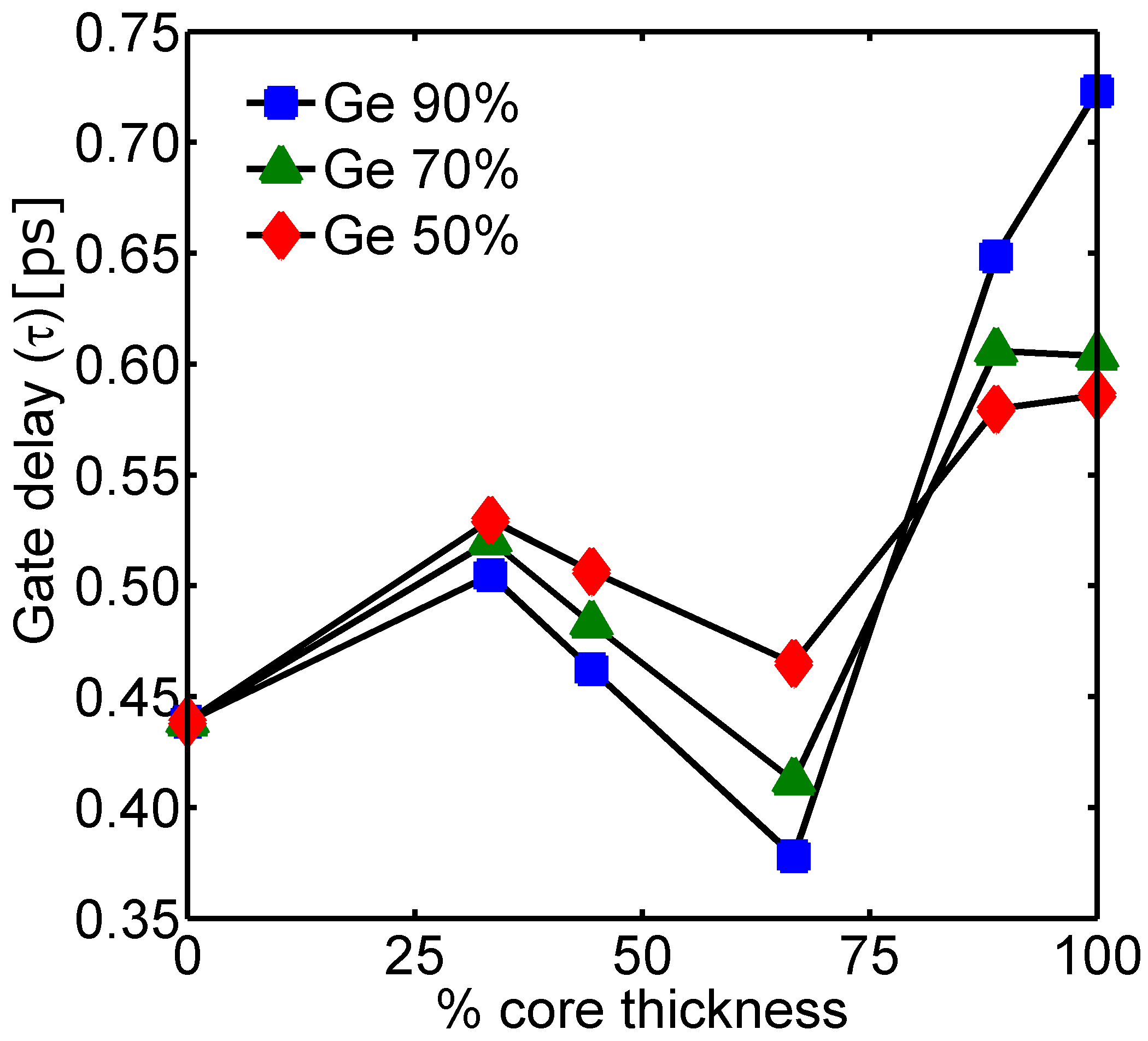

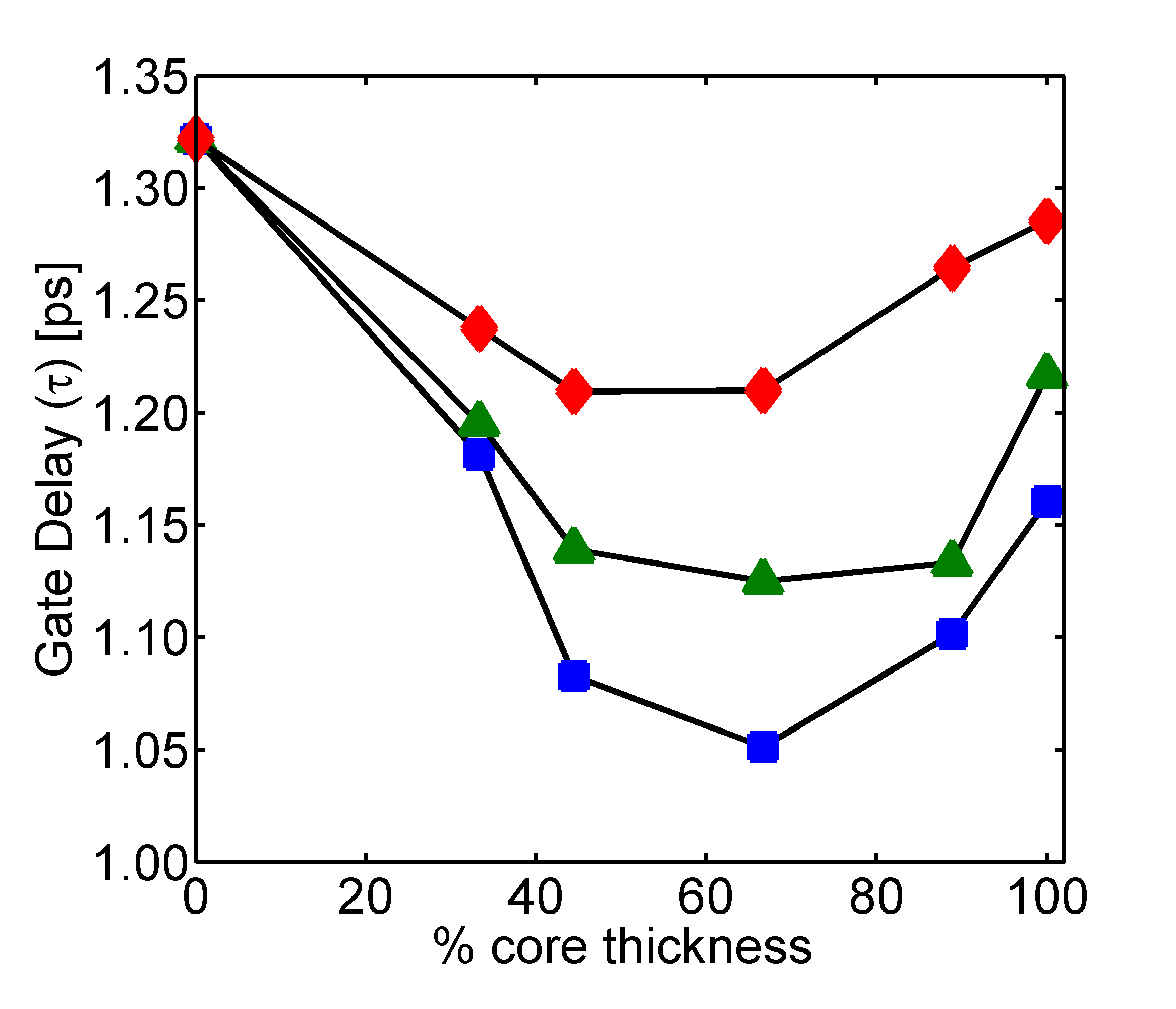

Intrinsic gate delay (tdelay) in n-FETs with core thickness and Ge%.  Intrinsic gate delay (tdelay) in p-FETs with core thickness and Ge%. |

Powerpoint slide as ppt, pdf, or as image below.