Top-of-the-Barrier Model

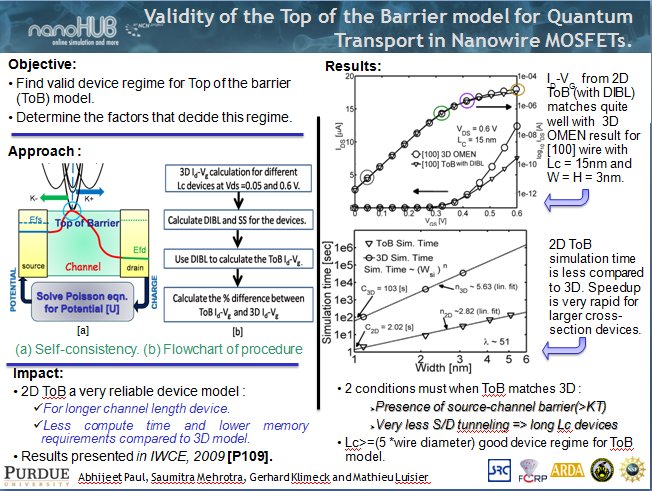

| Validity of the Top of the Barrier model for Quantum Transport in Nanowire MOSFETs | Abhijeet Paul, Saumitra Mehrotra, Gerhard Klimeck and Mathieu Luisier |

|

Objective:

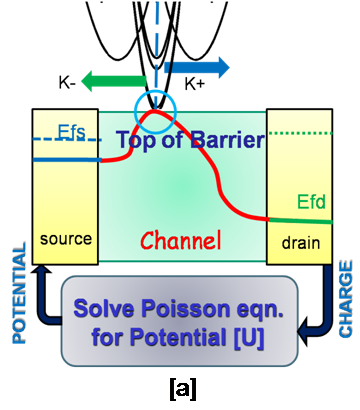

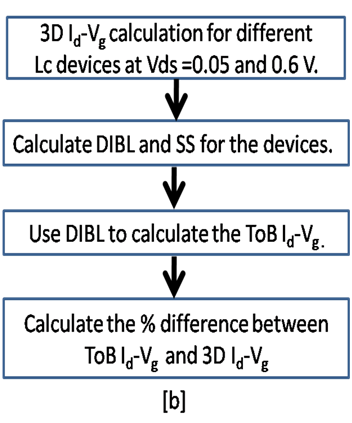

Approach  [a]Self-Consistent Scheme  [b]Flowchart of procedure Impact:

|

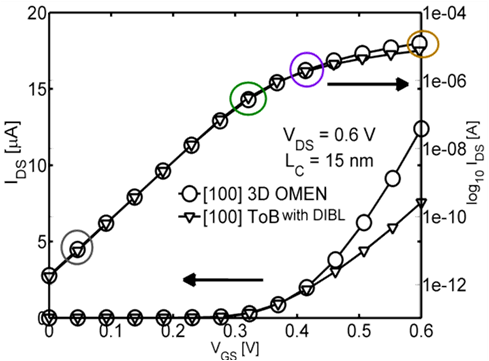

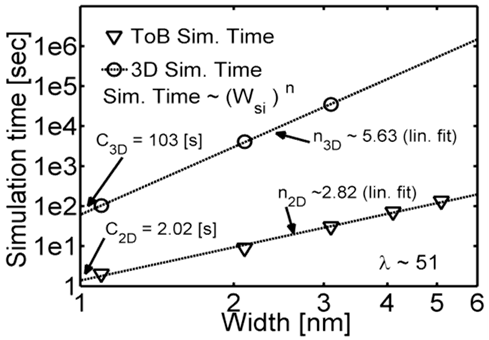

Results:  ID-VG from 2D ToB (with DIBL)matches quite well with 3D OMEN result for [100] wire with Lc = 15nm and W = H = 3nm.  2D ToB simulation time is less compared to 3D. Speedup is very rapid for larger cross-section devices.

|

Powerpoint slide as ppt, pdf, or as image below.