Home

> Research Group

> Members

> Abhijeet Paul

> Top-of-the-Barrier Model with experimental CV data

Top-of-the-Barrier Model with experimental CV data

| Benchmarking Top of the Barrier Model using experimental CV data This project was a collaboration between Purdue University and IME Singapore | Purdue Collaborators: Abhijeet Paul,Raseong Kim, Mathieu Luisier, Gerhard Klimeck and Mark Lundstrom IME Singapore Collaborators: Subash Rustagi, H Zhao. |

|

Objective:

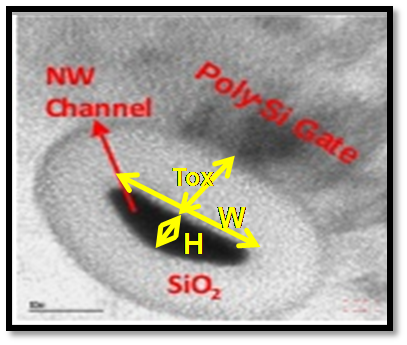

Device Details:  Self-Consistent Scheme

Approach:

Impact:

|

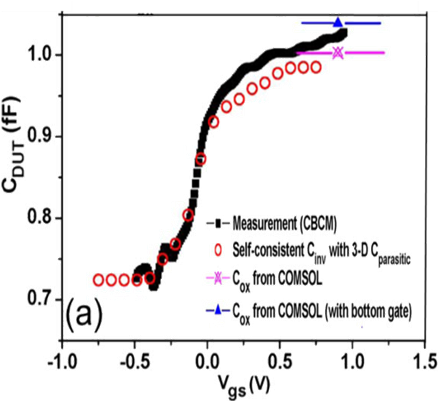

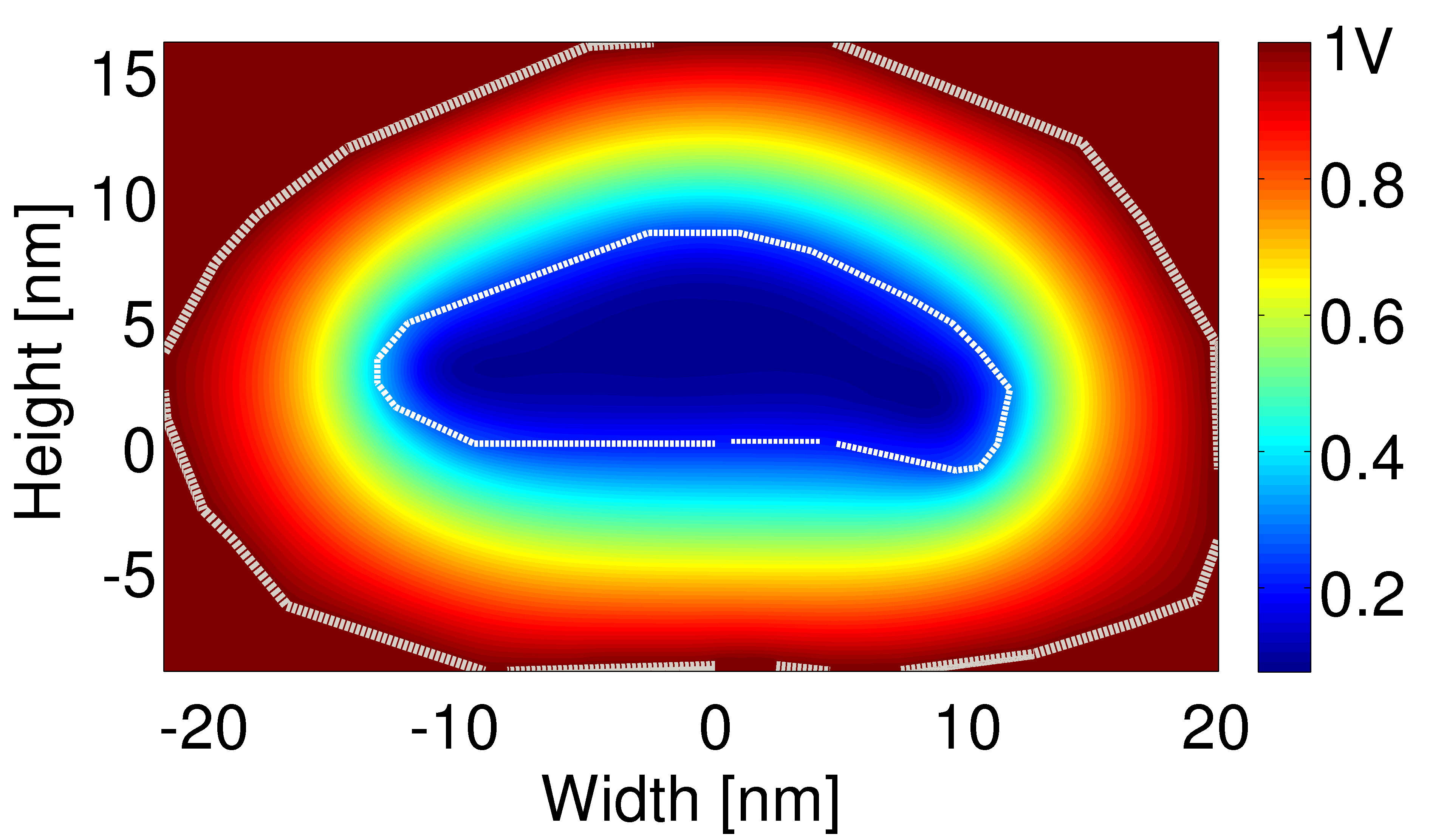

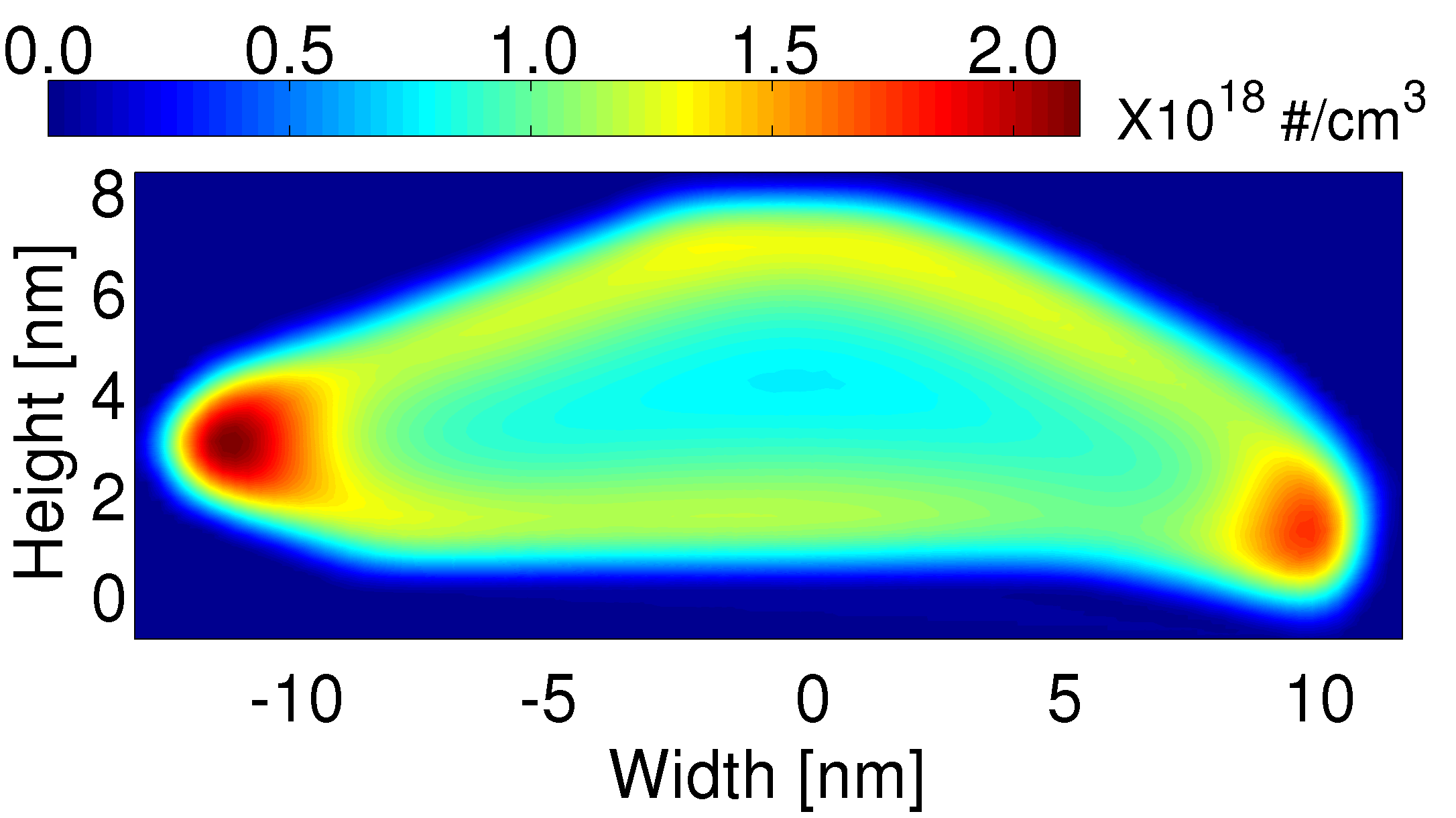

Results:  Measured C-Vgs using the CBCM technique and self-consistent intrinsic SiNW gate capacitance simulated using ToB model added with the 3-D electrostatic capacitance without considering NW obtained from COMSOL  Electric Potential Distribution at Vgs = 1V.  Electronic charge distribution at Vgs = 1V. units of charge: nm^-3. |

Powerpoint slide as ppt, pdf, or as image below.