Ferroelectric Transistor Technologies

Reconfigurable Ferroelectric Transistors (R-FEFETs):

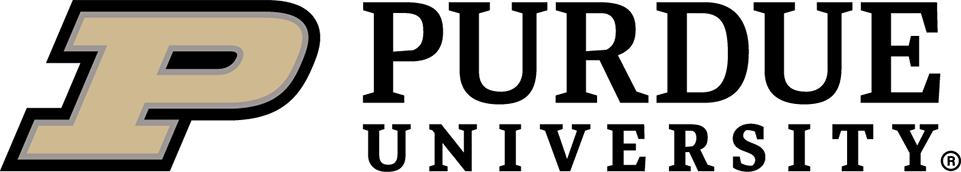

Ferroelectric Transistors (FEFETs) are emerging devices, in which FE is integrated in the gate stack of a transistor above the dielectric (DE). An optional metal may also be used in between FE and DE layers. The capacitance of FE couples with that of the underlying FET leading to unique characteristics: (i) sub 60mV/decade sub-threshold swing for low power logic and (ii) non-volatile transistor operation (due to P retention in the absence of E). Experimental studies have shown volatile (logic) or nonvolatile (memory) characteristics for FEFET by employing design-time/static device optimizations, for instance by modifying the composition of the gate-stack. However, if run-time tuning of nonvolatile and volatile modes can be achieved, several new avenues for circuit design will open.

We proposed a novel transistor called the reconfigurable FEFET or R-FEFET, which exhibits a unique characteristic of dynamic modulation between volatile (for logic) and non-volatile (for memory) modes of operations. The proposed emerging transistor technology showed the possibility of achieving uni-polar voltage design and mitigates the issues associated with gate leakage in existing ferroelectric technologies, opening up several new avenues for energy efficient circuit and system design.

References:

[1] S. K. Thirumala and S.K. Gupta, "Reconfigurable Ferroelectric Transistors - Part I: Device Design and Operation", IEEE Transactions on Electron Devices (TED), 66(6), pp. 2771-2779, 2019.

R-FEFET based Low Power Non-volatile Memory:

With an increasing demand for portable electronic gadgets as well as data centers for cloud services, the need for high density and low power memories has never been greater. Furthermore, with the advent of the internet of things (IoT) and the emergence of new applications with extremely small power budgets, the exploration of intermittently powered systems (IPS) has gained an immense attention. One of the most promising approaches to achieve ultra-low energy consumption is to introduce non-volatility at various levels of memory hierarchy – main memory, caches and possibly even at the core register level (especially for IPS). Non-volatility not only leads to zero stand-by leakage, but also enables energy efficient data back-up in the event of power failure.

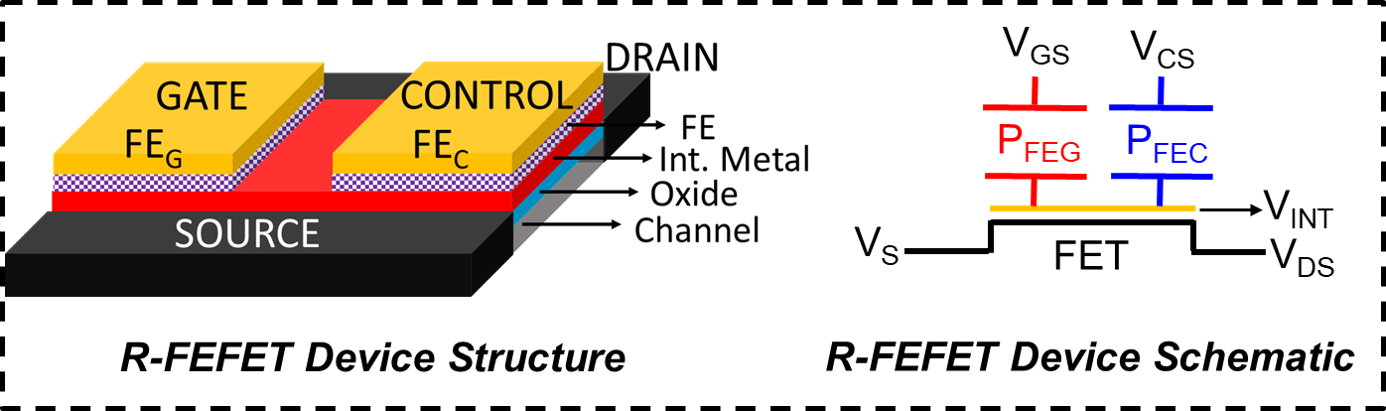

To that effect, there has been an immense interest in the exploration of non-volatile memory (NVM) technologies. Not only do such NVMs offer the promise of zero stand-by power, they also feature other appealing attributes such as (i) large integration densities to enable high capacity memories and (ii) easy integration with CMOS technologies. However, the existing NVMs suffer from key drawbacks such as design conflicts and issues associated with reliability, robustness and high write power. We proposed a 3T non-volatile memory (3T-R) based on the intriguing properties of R-FEFET to overcome the drawbacks of existing emerging NVM technologies. The proposed memory overcomes the drawbacks faced by conventional FEFET-based memory designs due to gate leakage. The 3T-R memory does not require any negative voltages unlike the conventional 2T and 3T memories for writing into the bit cell, leading to lower write power consumption at iso-access time. The possibility of dynamic reconfigurability between the volatile and nonvolatile modes of operation leads to a simplified read operation with respect to the conventional FEFET-based memories, resulting in lower read power. Based on our comprehensive device analysis and memory design implementation, the proposed R-FEFETs shows a lot of promise for the design of novel nonvolatile circuits and systems.

References:

[1] S. K. Thirumala and S.K. Gupta, "Reconfigurable Ferroelectric Transistors - Part II: Application in Low Power Nonvolatile Memories", IEEE Transactions on Electron Devices (TED), 66(6), pp. 2780-2788, 2019.

Overcoming von-Neuman Bottleneck with in-Memory Computation:

Memory speed has not kept up with processor speed over the last few decades leading to the so-called Memory Wall problem. It is estimated that the gap between the improvement in processor and memory speeds is increasing by more than 50% every year. Furthermore, in the era of big data, cloud computing and artificial intelligence, data-intensive applications have come to the forefront. This has led to restricted processor-memory bandwidth, resulting in overall performance/energy degradation in modern day systems. One solution to this problem is to perform Computing-in-Memory (CiM), which can mitigate the aforementioned issues. CiM is being looked at a potential alternative to existing von-Neuman architecture and is largely driven by advances in nonvolatile memory (NVM) and 3D monolithic technologies, but also to the meet the demands of extensive data processing for current/next generation computing.

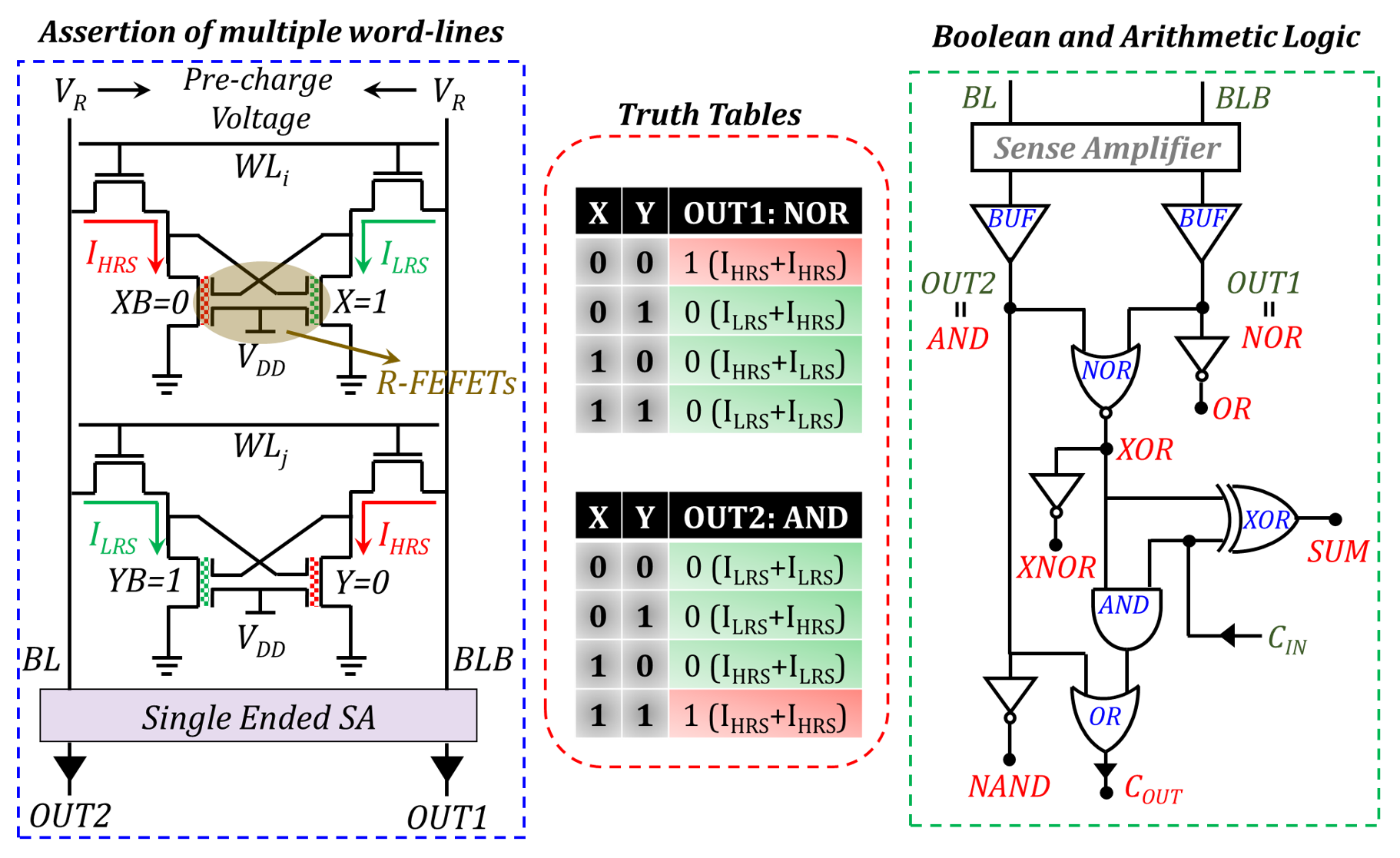

We proposed a novel 4T non-volatile differential memory with energy efficient computation in memory support. The differential access of the proposed memory not only enhances the sense margin during read, but also enables natural computation of AND and NOR logic functions between two bits stored in the array, with the assertion of two word-lines. Using this feature, we propose a CiM architecture involving the use of a compact compute module integrated to a sense amplifier which performs Boolean logic as well as arithmetic operations such as addition of two words with a single array access. Unlike existing non-volatile CiM designs, our work features: (i) a self-referenced read operation due to differential access and (ii) a single universal voltage reference for all compute operations. The proposed R-FEFET based CiM design achieves significant energy savings and performance efficiency over traditional computing approaches and other emerging CiM architectures.

References:

[1] S. K. Thirumala, S. Jain, A. Raghunathan and S.K. Gupta, "Non-Volatile Memory utilizing Reconfigurable Ferroelectric Transistors to enable Differential Read and Energy-Efficient In-Memory Computation", IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED), 2019.

Non-volatile Flip-flops based on R-FEFETs:

Non-volatile computing is an emerging solution to mitigate computation progress loss due to unexpected power failures. Systematic consistency-aware check-pointing mechanisms have been proposed to avoid data inconsistency and computation errors due to power failures. This is achieved by backing up the states of a circuit such as, on-chip memory, flip-flops (FFs) and registers into an off-chip non-volatile memory (NVM). However, this incurs significant energy/delay overheads due to long distance data transmissions and constrained parallelism. Embedded non-volatile computing is an attractive alternate method to back up the computation states into a local on-chip NVM, eliminating the transmission overheads.

To that effect, we proposed two variants of R-FEFET based non-volatile flip-flops for implementation in intermittently powered systems. In both designs, R-FEFETs are operated in the volatile mode for normal operations and in the non-volatile mode to backup the state of the flip-flop during a power outage. The first design, RNVFF-1, comprises of a truly embedded non-volatile element (R-FEFET) which enables a fully automatic backup operation. In the second design, RNVFF-2, we introduce need-based backup, which lowers energy during normal operation at the cost of area with respect to the first design. Both the designs outperforms (in terms of computation efficiency) standard FEFET based NVFF designs proposed in the past and overcomes the challenges associated with conventional ferroelectric technologies. System level implementation of the proposed RNVFFs showcased significant energy savings over conventional von-Neuman computing and other emerging technology based embedded non-volatile computing.

References:

[1] S. K. Thirumala, A. Raha, K. Ma, V. Narayanan, V. Raghunathan and S.K. Gupta, "Dual Mode Ferroelectric Transistor Based Non-Volatile Flip-Flops for Intermittently-Powered Systems", IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED), 2018.

FEFET based coupled Oscillators for non-Boolean Computing:

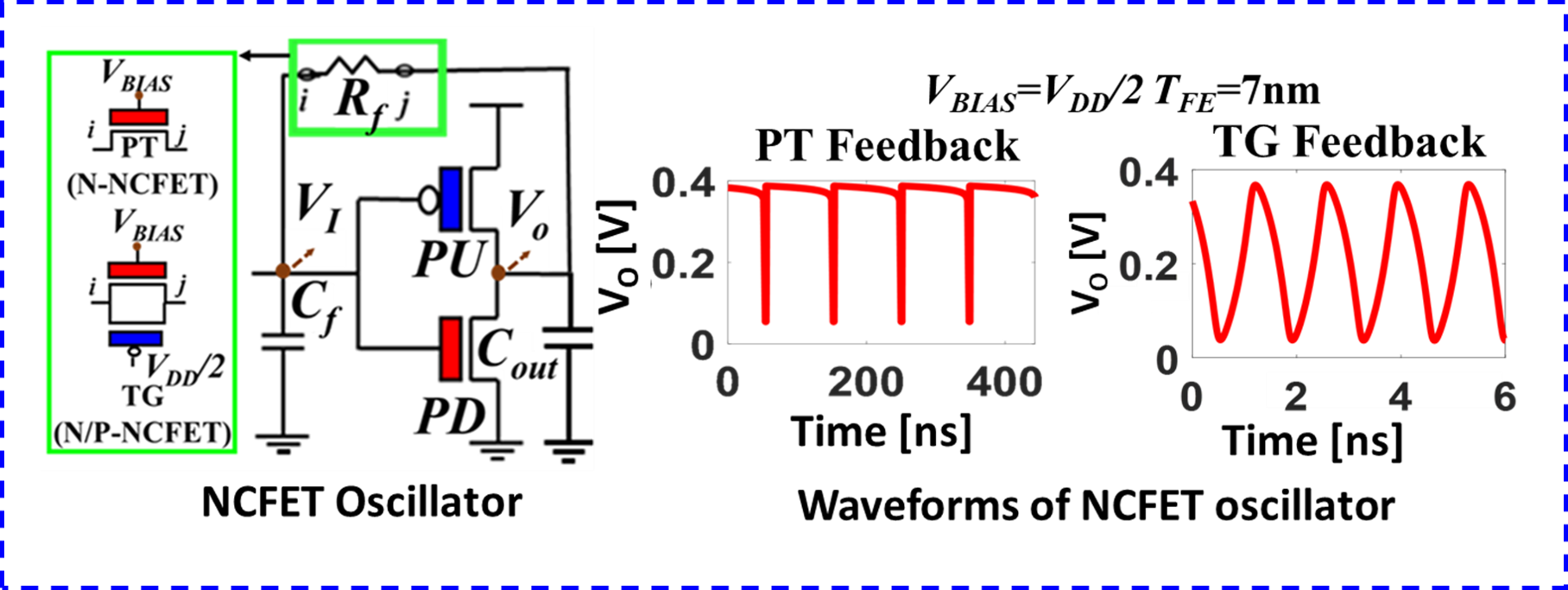

Computing based on coupled oscillators has shown an immense promise for tasks associated with recognition and optimization such as pattern matching, graph coloring etc. While CMOS based oscillators can be utilized for such a computing paradigm, emerging technologies have been shown to offer energy efficient implementations due to their unique properties amenable for oscillations. For instance, spin-based and insulator-metal-transition material based oscillators have exhibited a large potential for the design of coupled oscillators, albeit with their own overheads. In our group, we are exploring the design of coupled oscillators based on another promising technology based on ferroelectric materials. We have proposed compact low power oscillators, which utilize the negative output conductance of negative capacitance FETs (NCFETs) or the hysteretic characteristics of ferroelectric FETs (FEFETs) to achieve oscillations with high frequency [1]. For example, our NCFET based oscillator shows MHz-GHz performance. Moreover, our oscillators can be dynamically reconfigured to achieve relaxation or sinusoid/pulse-like characteristics. We are exploring the coupling between different flavors of the proposed oscillators which can be utilized in non-Boolean/neuromorphic computing.

References:

[1] N. Thakuria, et al, "Oscillators Utilizing Ferroelectric-Based Transistors and Their Coupled Dynamics," in IEEE Transactions on Electron Devices, vol. 66, no. 5, pp. 2415-2423, May 2019.