System-on-Chips

Items on Roadmap for AFTx07 and Later

- 6 stage RISCV pipeline created

- Vector extension to RISCV CPU

- ISA extensions: atomic, compressed, floating point, privileged

- Developing an LLVM based compiler to exploit the sparsity optimizations in our current RISCV core.

- Adding support for RUST programming language

- freeRTOS

- FPGA prototyping of our design with an eye to using it as a software development platform for our design.

- Multi-core

- L1/L2 cache

- Multi-core interrupts

- Branch predictor

- RISCV verification

- RISCV debug

- DMA controller

- Power management

Other projects and collaborations

- Several analog mixed signal student projects including a low drop-out regulator, op-amp, DAC, and adding wireless support to a future version of our chip, as part of a collaboration with the HINET lab (https://engineering.purdue.edu/~saeedm/index.html)

- Collaboration with C-BRIC on in-memory computing, Hard AI - K Roy, A Raghunathan

- GPU accelerator design - T Rogers

- Side-channel attach countermeasures - S Sen

- Reverse engineering countermeasures - J Appenzeller

- MRAM hardware security - J Appenzeller

AFTx06

Added features:

- Add compressed instruction set support (RV32C) to our core.

- Integrated PLIC interrupt controller

- On chip SRAM thanks to SRAM macros available for Skywater 130nm open source PDK

- Added SPI and I2C interfaces

- Ability to program through JTAG port. Already programmable through UART debugger

- Integrated with Caravelle test harness required for Google sponsored open-source chip fabrication

Taped out June 2021 for fabrication on Skywater 130nm through the Google sponsored open-source chip fabrication program as described at https://www.skywatertechnology.com/press-releases/google-partners-with-skywater-and-efabless-to-enable-open-source-manufacturing-of-custom-asics.

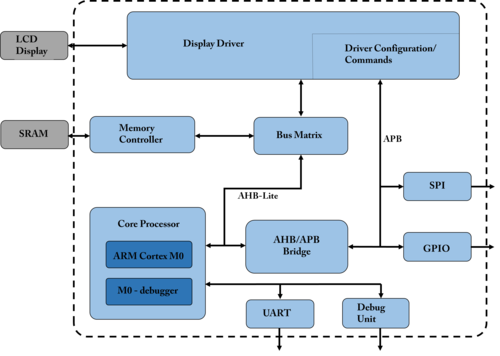

AFTx05

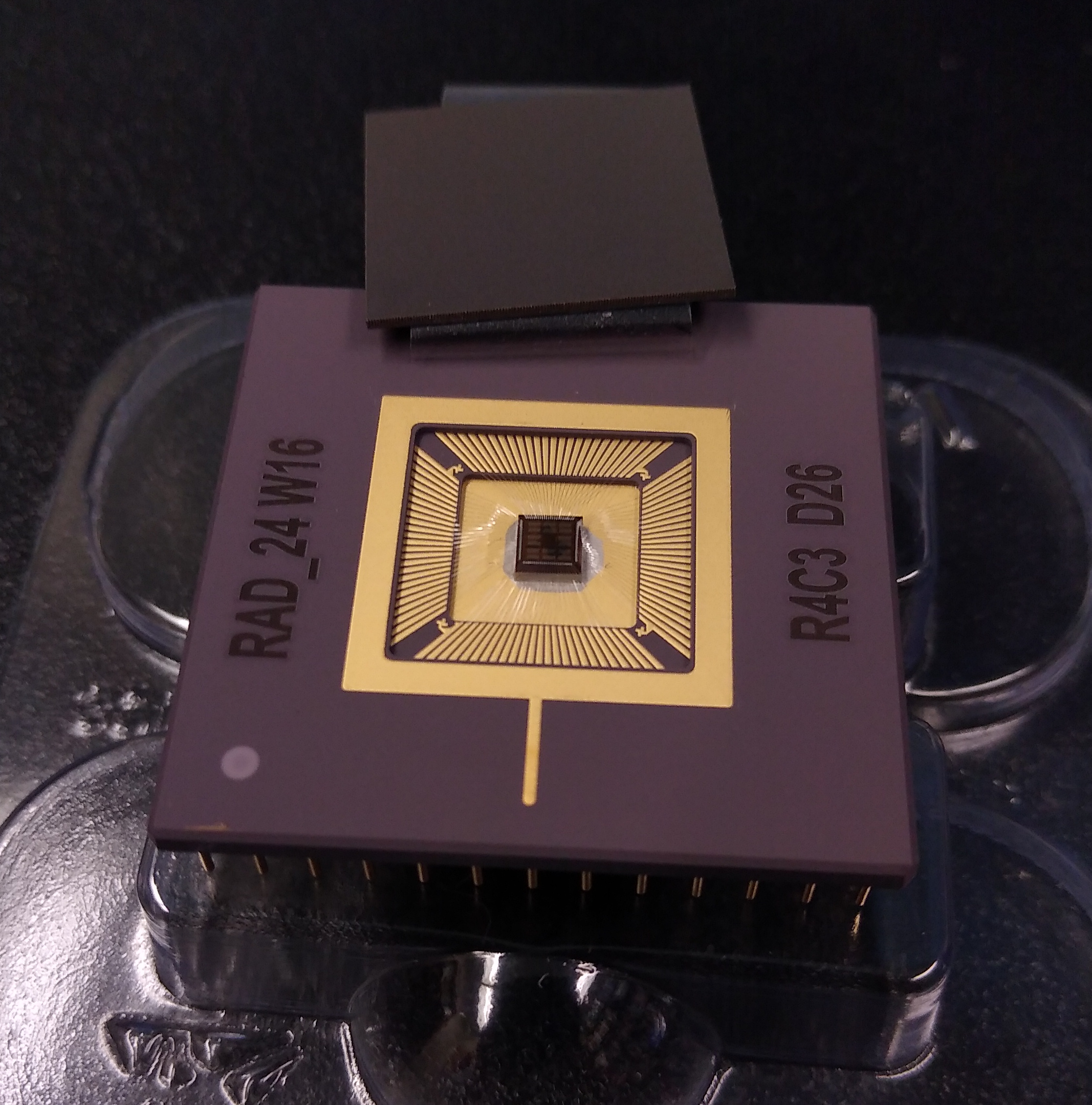

AFTx04

AFTx03

Goal: AFT-X03’s main focus was to create an SoC with basic functionality. The only supported peripheral is GPIO. This was the team’s first attempt at on-chip SRAM. The simplicity of the chip allows us to focus on establishing a team design flow before moving onto more complex designs

Status: A minimal chip bring up was performed but due to choice in package the chip proved to be very difficult to test mount to a PCB and test.

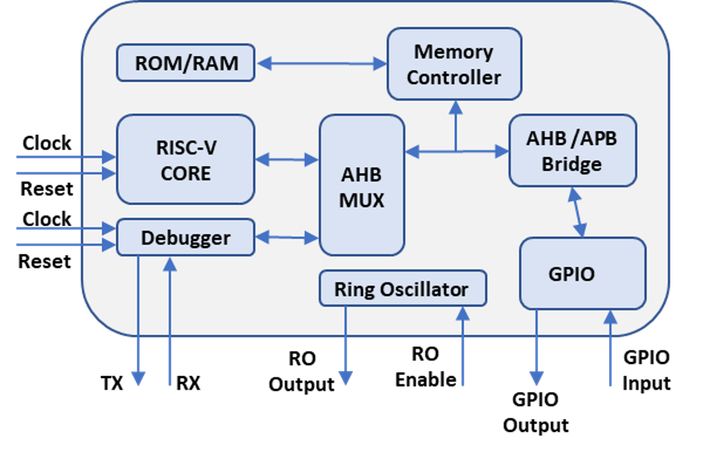

AFTx01/AFTx02

Goal: AFT-X01 and AFT-X02 were the team’s first attempt at designing and taping-out an SoC. Both chips have the same architecture. The bus structure of this chip was adopted by all of our current SoCs.

Status: AFT-X01 had an error in the power distribution and could not successfully be powered up. AFT-X02 was successfully powered on during bring-up. We were able to communicate with the debugger through UART.