Home

> Research Group

> Members

> Pengyu Long

> Suppression of source to drain tunneling in short channel MOSFET

Suppression of source to drain tunneling in short channel MOSFET

| Suppression of source to drain tunneling in short channel MOSFET | P. Long, S. Mehrotra, M. Povolotskyi, G. Klimeck, M. Rodwell |

|

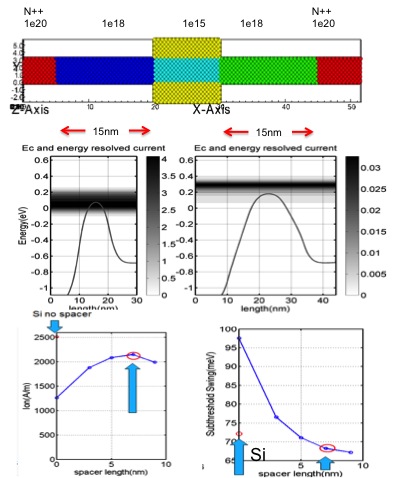

Objective:

Approach:

Results:

|

|