Wide Bandgap Devices Group

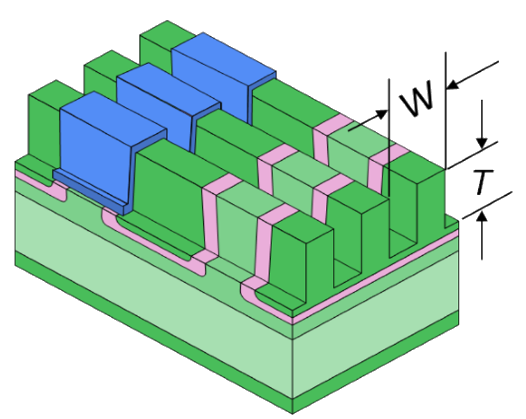

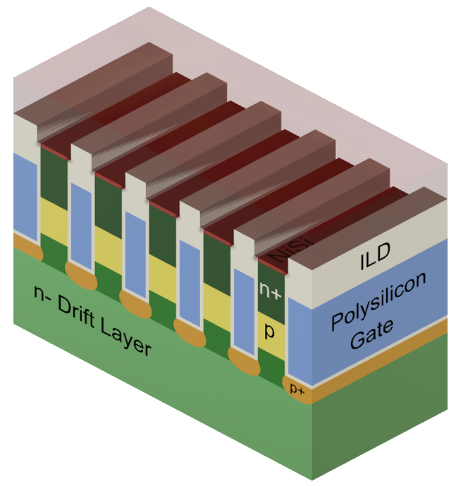

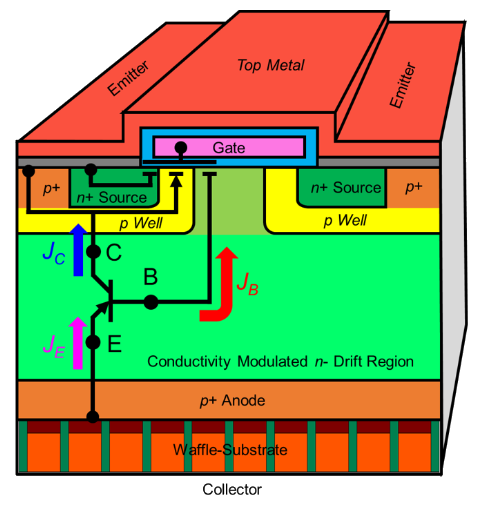

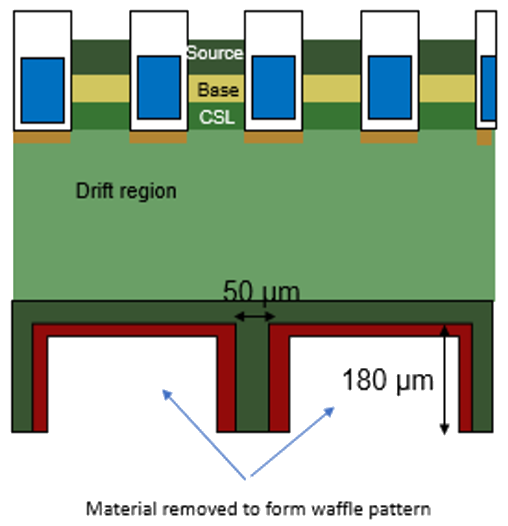

Our research focuses on the design and fabrication of vertical 4H-SiC devices. The devices that we are currently working on are Vertical Tri-Gate Power MOSFET (3G MOSFET), Deeply scaled fully self-aligned Trench MOSFET (IMOSFET), and IGBT.