TAPE OUTS

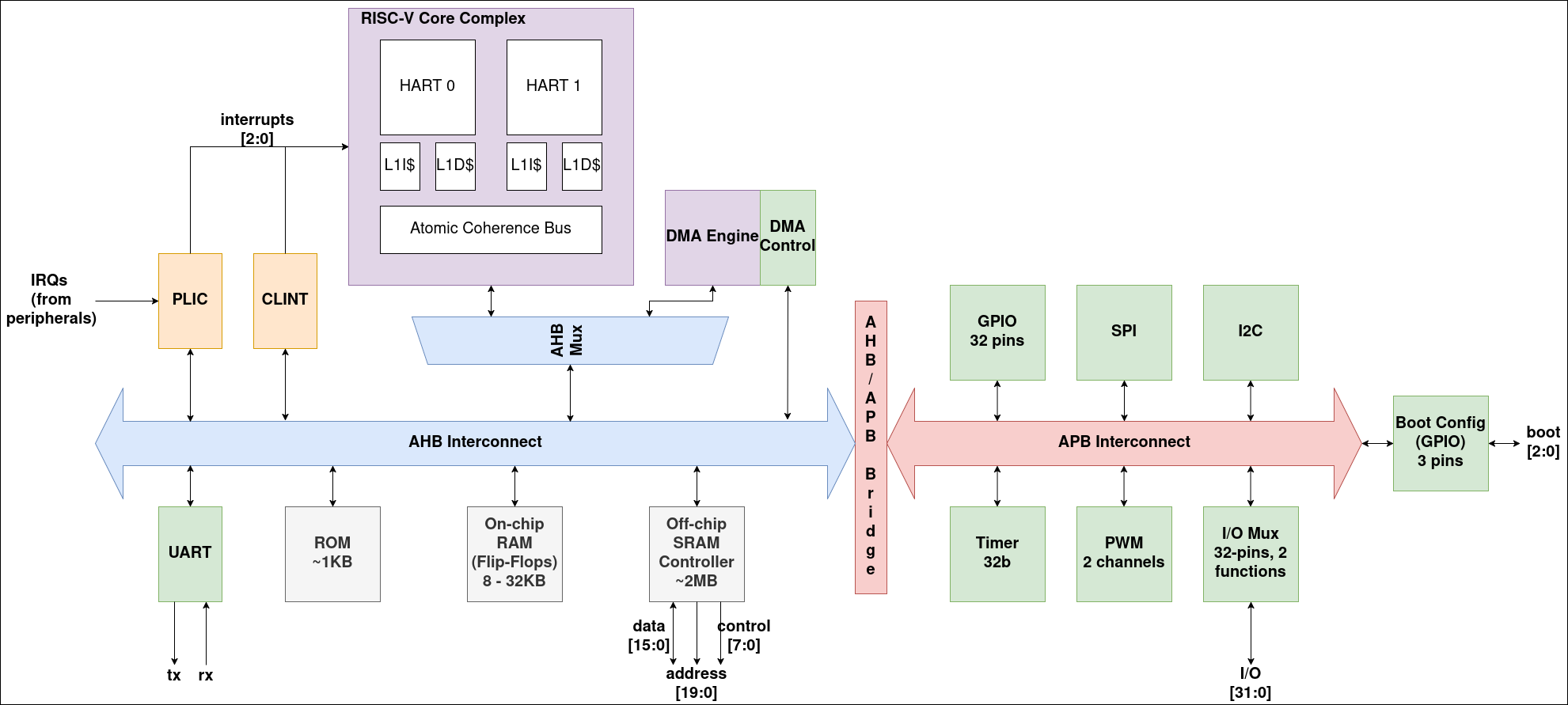

AFTx08

Added features:

- Major RISC-V core enhancements with redesigned compressed instruction (RV32C) support and improved branch prediction

- Expanded ISA support including bit-manipulation (B), conditional (Zicond), and load-reserved/store-conditional atomics (Zalrsc)

- Parameterizable instruction and data caches with significantly increased cache sizes

- Multicore support with MESI cache coherence and sequential consistency

- Optimized PLIC interrupt controller with tree-based priority resolution for reduced critical path

- True on-chip SRAM generated from memory compiler (replacing synthesized RAM structures)

- Integrated on-chip ROM for first-stage boot and improved memory hierarchy

- Hardware I2C controller added and integrated into the boot process (replacing software bit-banged I2C)

- Improved boot flow with single-core initialization and multicore bring-up via interrupts

Status: will be sent to tape-out this April!

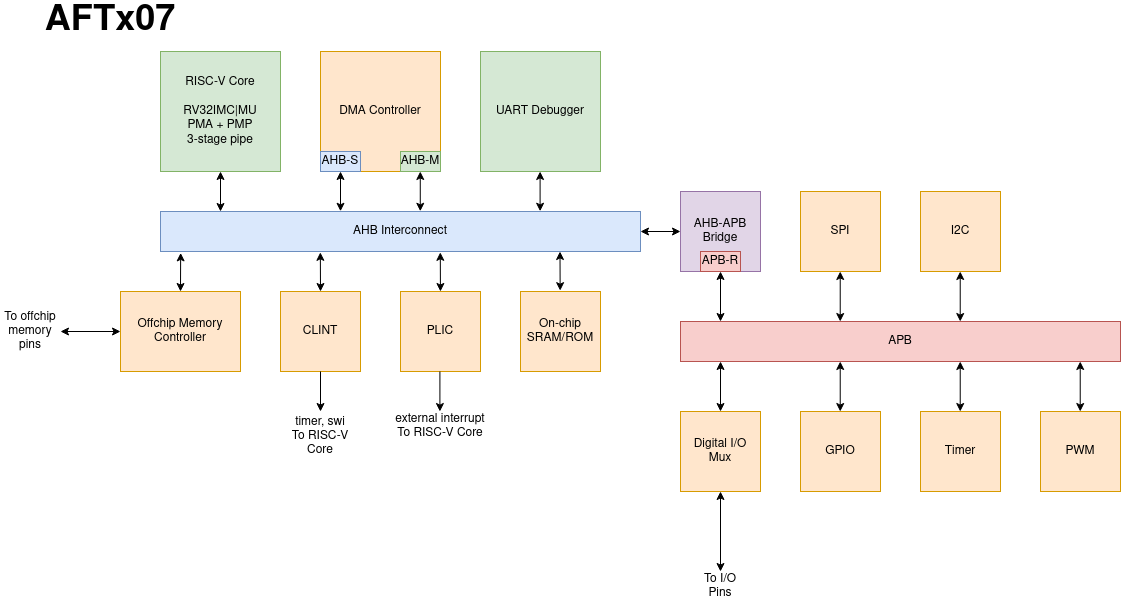

AFTx07

Added features:

- Numerous improvements to RISC-V core

- More reliable off-chip memory

- I/O multiplexing

AFTx07+: New boot process.

AFTx07++: Smaller process — MITLL 90nm

Status: In fab, currently being taped-out.

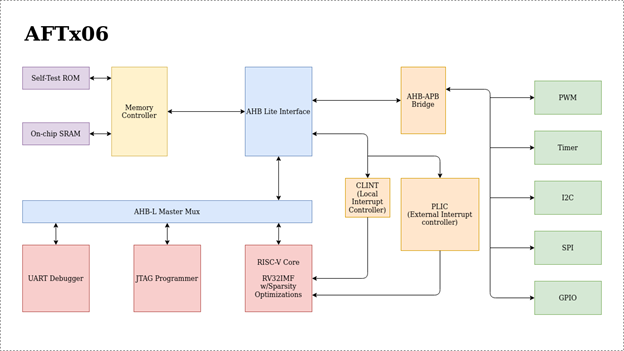

AFTx06

Added features:

- Add compressed instruction set support (RV32C) to our core

- Integrated PLIC interrupt controller

- On chip SRAM thanks to SRAM macros available for Skywater 130nm open source PDK

- Added SPI and I2C interfaces

- Ability to program through JTAG port (already programmable through UART debugger)

- Integrated with Caravelle test harness required for Google sponsored open-source chip fabrication

Taped out June 2021 for fabrication on Skywater 130nm through the Google sponsored open-source chip fabrication program as described here.

AFTx05

Goal: AFTx05 will be our second tape-out to MIT-LL on their 90nm FDSOI process. This design incorporates several features intended for research and demonstration including sparsity optimizations of the RISC-V core, polymorphic logic, and electromigration test structures.

Status: This design was taped-out on Feb. 18, 2020.

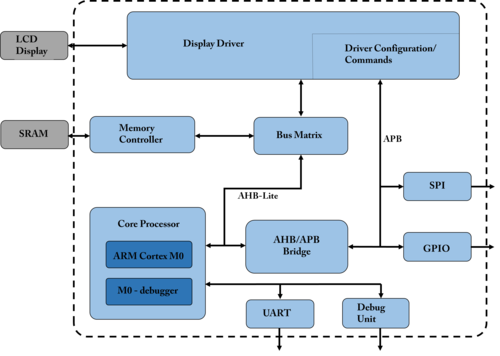

AFTx04

Goal: AFTx04 is an implementation of a simple microcontroller based on a RISC-V core. It is also our first attempt at fabrication through the MIT Lincoln Labs 90nm FDSOI process.

Status: The dice passed manufacturing test at MIT-LL and packaged ICs were delivered in September 2019. Functional test vectors were run on an automated tester. Except for some odd debugger behavior on reset, the design functions as intended.

AFTx03

Goal: AFTx03 focused on creating an SoC with basic functionality. GPIO was the only supported peripheral. This was the team’s first attempt at on-chip SRAM and helped establish a complete design flow.

Status: Minimal chip bring-up was performed, but the chosen package made PCB mounting and testing difficult.

AFTx01 / AFTx02

Goal: AFTx01 and AFTx02 were the team’s first SoC tape-outs. Both chips share the same architecture, and the bus structure was adopted by all subsequent designs.

Status: AFTx01 had a power distribution error and could not be powered up. AFTx02 was successfully powered and communicated with the debugger via UART.