Ab-initio studies of III-V surfaces and III-V oxide interfaces

Silicon has been the main workhorse of the semiconductor industry since the invention of the Integrated Circuit. Since then, the continuous miniaturization of Silicon transistors given by Moore's Law has resulted in an explosive growth in computing power. A class of materials such as GaAs, InAs and so on - collectively known as III-V's - have long been known to conduct electrons at higher speeds than Silicon. However, the uniformly poor electrical characteristics of the III-V/native oxide interface have prevented their incorporation into mainstream semiconductor logic technology. This is the so-called 'Fermi Level Pinning (FLP)' problem in III-V oxide interfaces.

Recent efforts in creating III-V CMOS devices using methods such as Atomic Layer Deposition (ALD) of oxides have resulted in interfaces that have 'reasonable' electrical properties. However, recent ALD experiments on III-V's suggest that our understanding of FLP is still far from complete.

Our goal in this project is to understand how III-V interface chemistry affects their electrical characteristics using ab-initio density functional theory (DFT). We are adopting a two-pronged strategy in our investigation. The first part involves understanding and explaining some of the latest ALD experiments on the III-V system. Using this understanding, we hope to eventually come up with some general predictive rules that are applicable across III-V's and oxides. It is also our endeavor to eventually use the insights we gain from this study to help experimentalists in their search for a 'good' III-V/oxide system.

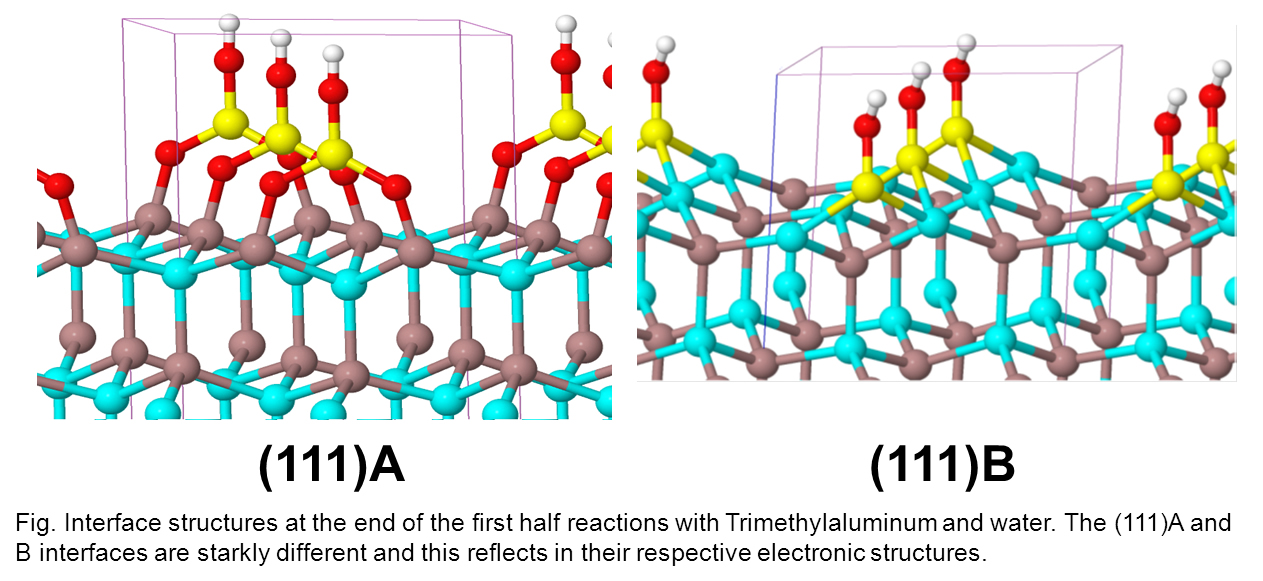

Our initial results indicate that interface chemistry in the ALD process on III-V's depends heavily on the surface orientation of the underlying semiconductor substrate. The interface chemistry in turn, strongly affects the electrical characteristics of the interface and consequently causes a variation in CMOS performance by up to four orders of magnitude. Our results indicate that FLP may not be an intrinsic property of a semiconductor as previously postulated in some models of FLP, but instead depends heavily on interface chemistry.