Matt Waldersen's Lab Notebook

Week 01 (August 19 - August 26)

August 22, 2012 (2 hours):

Created preliminary project proposal.

August 23, 2012 (2 hour):

Met as a team after class to discuss preliminary project proposal. Each team member's project

responsibilities were agreed upon and each individual's area's of expertise were finalized. With these things established the preliminary project proposal

was updated to reflect what was decided upon in our meeting.

August 25, 2012 (2 hours):

Watched video tutorials on artificial neural network algorithms. The videos covered the fundamental

ideas of artificial neural networks, the calculations performed by artificial neural networks and training artificial nueral networks.

Artificial Neural Network Video Tutorials were provided by Heaton Research.

August 25, 2012 (1 hours):

Finalized analog EOG circuit topology: The circuit consists of three statges, all of which will both amplify and filter the

EOG signal. The first stage will be an instrumentation amplifier with a band pass filter integrated into it. The second stage will be a 2nd order Sallen-Key Low Pass Filter and the last stage

will be an averaging circuit. The voltage range of the instrumentation amplifier and 2nd order Sallen-Key low pass filter will be from -5v to +5V, and the averaging circuit will be used to

create a virtual ground at +2.5v and range from ground to +5v in order to better accommodate the voltage ranges of most ADC modules. An external ADC will be implimented primarily to reduce the effects

of noise on the circuit. With this design, it is possible to keep the analog circuitry as close as possible to the signal source as well as digitize the signal as closely as possible to the analog ciruitry while

maintaining seperation from the noise caused by digital circuitry. The decision was made to integrate some form of filtering into every stage of the circuit to optimize the functionality of each operational amplifier.

Applying this technique, though efficient, is poorly documented. At this point I have not been able to find documentation describing a similiar instrumentation amplifier or averaging circuit design's transfer function with an algorithm to

determine the high pass filter and low pass filter's cutoff frequency. Also, a possible revision including a variable gain amplifier-attentuator may need to be included if the signal magnitude widely varies from person to person to

prevent saturating the operational amplifiers and the ADC.

Preliminary EOG Circuit

WEEK 01 SUMMARY

Accomplishments: Submitted preliminary project proposal and finalized analog EOG circuit toplogy.

Weekly Work Total: 7 hours

Project Work Total: 7 hours

Week 02 (August 27 - September 2)

August 29, 2012 (4 hours):

Wrote preliminary final project proposal and created a preliminary block diagram.

Final Project Proposal Block Diagram

August 29, 2012 (1.5 hours):

Met with Professor Johnson and T.J. Strzelecki to discuss FPGA implimentation of artificial neural networks.

T.J. and I presented our proposal and discussed the use of NueroSky's "esense" outputs if we were not able to correctly impliment a artificial nueral network on an FPGA.

Professor Johnson informed us that a possible method of implimenting an artificial nueral network on an FPGA would be with the aid of MATLAB's artificial network toolbox.

We decided to use this approach for two main reasons. First, this method would allow us to rapidly prototype different artificial nueral network topologies in software without

allowing us to place as much time and resources into the FPGA as possible. Second, Professor Johnson had mentioned that there are software packages in MATLAB that can take MATLAB code

and translate it into various harware description languages. Though we don't expect it to translate MATLAB code perfectly, it would provide a good foundation to modify and impliment our

program.

August 30, 2012 (0.5 hours):

Met as a team to discuss preliminary final project proposal and block diagram. Homework assignments

were chosen based off each of our class and exam schedules this semester as well as personal interest. With the major sub-systems of our project finalized and the

responsibilities required to complete our project deligated to each team member our PSSC's were formulated.

PSSC's:

1.) An ability to implement a UART or USB connection to connect to the Mindwave's wireless

dongle to recieve raw EEG data values.

2.) An ability to develop an algorithm to determine an accurate selecting mechanism from the

Mindwave data signals.

3.) An ability to navigate between different applications on a display using EOG signals.

4.) An ability to develop applications(s) that demonstrate the potential uses of a mobile

brain-computer interface.

5.) An ability to reviece a live video stream from an external camera module and integrate

it into an augmented reality display.

August 30, 2012 (1 hours):

The final project proposal was updated to reflect the responsibilities of each team member as

well as the PSSC's.

WEEK 02 SUMMARY

Accomplishments: Project proposal finalized.

Weekly Work Total: 7 hours

Project Work Total: 14 hours

Week 03 (September 3 - September 9)

September 3, 2012 (2 hours):

Read through course PCB documentation and began PCB Tutorial.

September 4, 2012 (1 hours):

Created PSSC's powerpoint presentation to be presented in class September 5th.

The major changes to the PSSC's were meant to make them more about what the device does rather than what we hope to accomplish. the updated PSSC's are as follows:

1.) An ability for the system to exchange data with a Nuerosky Mindwave EEG.

2.) An ability for a user to select applications based on signals from the Nuerosky Mindwave EEG.

3.) An ability for a user to navigate between different applications on a display using EOG signals.

4.) An ability for the system to perform socially redeeming tasks using various applications.

5.) An ability to display a live video stream from an external camera module, and integrate applications into the video stream.

September 4, 2012 (0.5 hours):

Met as a team to update and discuss PSSC's as well as design questions brought up during the presentation.

Common questions regarding the design and PSSC's included:

-The need to redefine PSSC's in terms of what the device does rather than how it will be done.

-The accuracy and quality of the NueroSky Mindwave EEG.

-Which single board computer will be used.

-How the artificial nueral network will be calibrated and trained.

-Defince the term "applications" and "socially redeeming" more specifically.

-Whether our design is tractable.

September 6, 2012 (0.5 hours):

Met with Professor Meyer to discuss PCB design and analog EOG circuitry. The major topic of discussion regarding

PCB design was how to route both positive and negative voltages and to use a seperate ADC module to aquire the EOG signal.

September 7, 2012 (4 hours):

Completed PCB tutorial exercise.

September 8, 2012 (13 hours):

Created analog EOG instrumentation amplifier circuitry simulations in PSPICE and created an algorithm in MATLAB designed to choose optimal passive components in order to be able to rapidly prototype circuit.

The program worked by asking the user to enter the desired gains and cut-off frequencies of the circuit then calculating the cut-off frequencies off of every possible combination of resistor and capacitor values

in a look up table. A major issue with the preliminary program was the number of possible combinations of components created. MATLAB simply doesn't allow the user to create matricies of the sizes required to include all of the

compinations of components. The major goal in the PSPICE simulations is to develope equations describing the behavior of the instrumentation amplifier. It was found that the input buffers to the instrumentation

amplifier could be modeled as two systems consisting of a low pass and high pass amplifier. The figure below shows the frequency response of the input buffers with only a low pass filter, the frequency response of the input buffers with

only a high pass filter and the frequency response of the input buffers with a bandpass filter.

Instrumentation Amplifier Input Buffer Frequency Response

WEEK 03 SUMMARY

Accomplishments: PCB tutorial completed, EOG instrumentation amplifier simulation conducted and an algorithm to rapidly increase efficiency prototype circuit created.

Weekly Work Total: 21 hours

Project Work Total: 35 hours

Week 04 (September 10 - September 16)

September 10, 2012 (8 hours):

Completed MATLAB rapid prototyping algorithm as well as EOG sallen-key 2nd order low pass filter and 1st order low pass filter averaging circuit simulations.

The memory issue previously mentioned was solved by measuring determinging the amount of error from the ideal values each combination has and only keeping the top 500 resistor-capacitor combinations with the lowest error.

There will be only two cut-off frequencies for the circuit. From my research I have chosen a preliminary high pass filter cut-off frequency of 0.1 Hz and a low pass filter cut-off frequency of 35 Hz. It was also decided

to impliment a K-Nearest Neighbor algorithm as the method used to recognize eye gestures.

The documents I used in my research are listed as follows:

Human Electrooculography Interface

Mouse Control with EOG Signals

EOG for REM Sleep Detection

September 11, 2012 (0.25 hours): Met with Professor Meyer to discuss PSSC's. The updates made are as follows:

1.) An ability to encode/decode data packets from a NueroSky EEG.

2.) An ability for a user to select applications based on signals from a NueroSky EEG.

3.) An ability for a user to navigate between different applications on a display using EOG signals.

4.) An ability for the system to interactively train the user to effectively operate the device.

5.) An ability to display a live video stream from an external camera module, and integrate applications into the video system.

September 11, 2012 (0.75 hours): Contacted sales offices from major semiconductor distributors in order to

find a lithium ion/lithium polymer battery charger IC that can charge a battery with a voltage large enough to power our single board

computer (+12V) in order to avoid the use of a boost converter. The reason our team has decided to avoid the use of DC-DC converters to

power our single board computer is because we want to make sure that it's current requirements are always met. The easiest way to do this

would be to choose a battery with a supply voltage higher than needed and use regulators to attentuate it to the required voltage.

September 11, 2012 (3 hours):Started research into which microcontroller to impliment in our system.

The major selection criteria were that it should have some type of signal processing abilities. Since the microcontrollers only purpose

is to aquire EOG signals from an external ADC and process them into four different commands there would be a need for a built in DSP

library and no need for internal PWM or ADC modules. Another criteria is that it needs enough communication modules to communicate with

the FPGA, the external ADC modules and the single board computer. These criteria narrowed the selection down to two families of microcontrollers.

The first was the dsPIC family and the second was the Freescale signal processing controller family. The dsPIC family, specifically

the dsPIC33EP512MU10, was chosen. Reasons behind it's selection include it's extensive DSP library that includes a built FFT function, the

number of communication modules,it's optimization for C compiling and it's large online community. The FFT function is of tremendious use due to the fact

we will now be able to perform an fourier transform on the raw signal from the EEG which comes in at a rate of 512 Hz as opposed all other values which

refresh at a rate of 1 Hz. The fact it is optimized for C compiling is desirable as well due to the fact it will make implimenting a K-Nearest Neighbor Algorithm

much simplier.

DSPIC33EP512MU10 Datasheet

September 11, 2012 (3 hours): Started researching different external ADC modules. The desired ADC module should include the highest resolution

possible, have a low noise footprint as well as accepted duel polarity signals.

September 11, 2012 (1 hours): Created the slides regarding microcontroller selection for the in class Constraint Presentation.

September 12, 2012 (2 hours): After being contacted by a sales representitive from Texas Instruments, I was informed that

lithium ion/lithium polymer charger IC that charge voltages above 4V are not produced by major semiconductor manufactures. With this information

I began searching through various charging modules and battery types. I was able to narrow it down to one online distributor called

All-Battery.com. This online distributor was chosen due to their large variety of both

batteries and battery chargers. Since a battery above 12V was still high even with a charging module, it was decided to begin searching for a battery that

opperated on 5V and to regulate the output of 7.4V battery down to the necessary voltages. 7.4V was chosen simply because it was the closest voltage level above

out maximum voltage requirements.

September 12, 2012 (4 hours): Began searching for an operational amplifier to impliment in the analog EOG circuitry. The selection

criteria for an operational amplifier was one that is able marketed as a "precision amplifier", operated with both positive and negative voltages, has low noise capabilities and has a model in PSPICE. The reason

I required the operational amplifier to have a working model in PSPICE was so I could compare its response to a replica EOG signal to an ideal operational amplifier

model. Characteristics like low DC offest and a wide frequency band were not of interest due to the fact a high pass filter essentially eliminates all DC characteristics and

EOG signals only operate up to roughly 35 Hz. Circuit simulation programs were downloaded from the Texas Instrument website in order to possibly expand the number of

operational amplifiers to compare to an ideal operational amplifier model. After some time it became clear that remaining with PSPICE as the sole circuit simulation software

would be more effiecient use of time as well as a better means of simulating the EOG circuitry.

September 13, 2012 (4 hours): Worked with Rick Schuman to finalize major component selection and aspects of homework 3 relating to my responsibilities. These components include:

-Analog to Digital Converter Module

-7.4V Lithium Ion Battery

-Battery Protection Circuit Module

-Video Glasses

-Battery Fuel Gauge

September 13, 2012 (1 hour): Made preliminary calculations describing the computational requirements for the EOG and added these calculations to the homework 3 document.

September 14, 2012 (1 hours): Had a team meeting to discuss how to redistribute the work load amoung the entire team. Created a "to-do-list"

in order to establish a clear and explicit way to cooridinate team effort. I will remain in charge of developing the EOG circuitry and algorithms as well as aiding

T.J. Strzlecki with artificial nueral network development. T.J. Strzelecki will be in charge of implimenting the artificial nueral network on the FPGA. Krishna will

be in charge of the communication protocal between all subsystems of the project as well as develop the training applications. Rick will be in charge of all aspects of video

overlay and live video feed acquisition. Krishna and I also decided to switch design component homeworks in order to better accomidate both of our class schedules.

September 14, 2012 (5 hours): Spent time creating a model EOG signal in PSPICE to test each circuit on. A vast majority of the time spent was in an

attempt to recreate a accurate "white noise source" to the circuit. Unfortunately no such component exists in PSPICE. There was references to interfacing PSPICE with MATLAB

to create such a source but I was unable to successfully integrate the two software packages.

September 15, 2012 (5 hours): Began working with the MATLAB Artificial Neural Network Toolbox

and was able to succesfully impliment an XOR artificial neural network. Once this was accomplished, I began to research artificial neural network topologies. The primary source of information on this subject

was A Neural Network Based BCI for Classification of Movement Related EEG. This document

described a project very similiar to the Mind Reader as well as the selection process in choosing an artificial neural network topology. Time was also spent research various mental tasks and activities designed to get a distinguishable response

with respect to the NeuroSky Mindwave's electrode position. Time was also spent establishing a communcation link in matlab with a NeuroSky Mindflex EEG donated to our team for the semester.

WEEK 04 SUMMARY

Accomplishments: Completed a MATLAB program in select resistor and capacitor values in the EOG circuit. Researched and decided that a K-Nearest

Neighbor algorithm would be best suited for our EOG application. Selected major components of our system. Reassigned team member responsibility to better distribute the work load.

Created a model EOG signal in PSPICE. Began work with the MATLAB artificial neural network toolbox and did extensive research in artificial neural network topologies.

Weekly Work Total: 38 hours

Project Work Total: 73 hours

Week 05 (September 17 - September 23)

September 17, 2012 (8 hours): Finishing the PSPICE implimintation of an EOG signal. Instead of inputing a completely random white noise source

it was decided to use the summation of two sine waves. One wave had a frequency of 60 Hz and the other had a frequency of 50 Hz. These frequencies were chosen because a vast majority

of electronics operate at this frequency. With a replica input EOG signal created, I continued researching various operational amplifiers and comparing them to an ideal operational amplifier model.

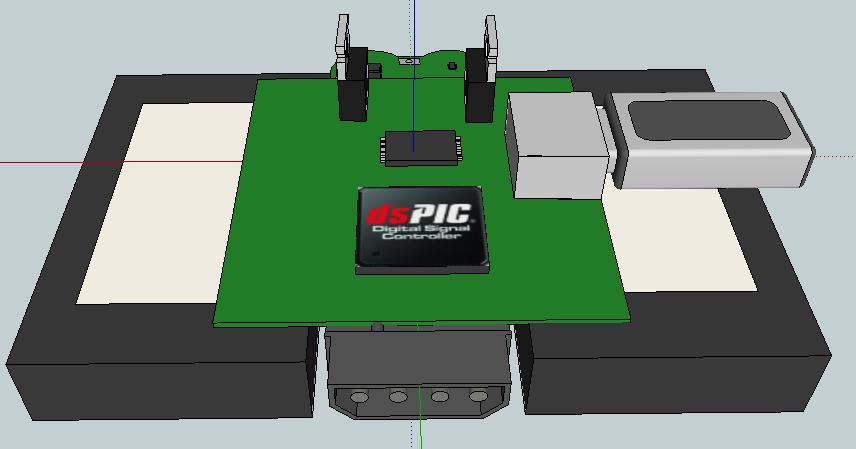

September 18, 2012 (10 hours): Created 3D models of our system in Google Sketchup for the Packaging Specifications and Design Presentation.

Images of the 3D models used in the presentation are shown below.

Back View

Side View

Front View

FPGA

Power Supply and Microcontroller PCB

Single Board Computer

September 20, 2012 (8 hours): Finilized choice in operational amplifier. The operational amplifier chosen

is the OPA4131. This operational amplifier was chosen due to its impressive simulation results,it's

packaging variety, and it's low cost.A majority of other discrete components were chosen and finalized. Simulations of the OPA4131 are shown below.

OPA4131 Schematic

EOG Signal No Noise

OpAmp Comparison Without Noise

EOG Signal With Noise

OpAmp Comparison With Noise

September 20, 2012 - September 21, 2012 (15 hours): Spent time updating models to reflect added detail in components. Created PCB footprints for each one of these components in EAGLE as well as finishing the Homework 4 document. Updated

models are shown below.

EOG PCB Footprint

EOG PCB Model

Microcontroller PCB Footprint

EOG PCB Model

EOG PCB Model

WEEK 05 SUMMARY

Accomplishments: Selected discrete components including an operational amplifier to use in the EOG circuitry. Created 3D models of the

system, created PCB footprints for all newly added components and completed Homework 4.

Weekly Work Total: 41 hours

Project Work Total: 114 hours

Week 06 (September 24 - September 30)

September 24, 2012 (4 hours): Begain work on a preliminary algorithm in MATLAB to recognize EOG Signals. So far the algorithm

has two major components. First the signal is averaged. The purpose of doing this is to further reduce the effects of noise. It should be noted that

The reason the simulation EOG signal is much smaller at the beginning than at the end is due to the fact I wanted to test the minimum EOG signal (0.4mV) and

the maximum EOG signal (1mV) in one test. It is expected that the EOG signal from one person will not vary as drastically.

Averaged Signal vs Raw Analog EOG Signal

Averaged EOG Signal in MATLAB

The second major phase is to normalize the signal. This eliminates any DC offset that could throw off the K-Nearest Neighbor Algorithm. This

is accomplished by simply taking the derivative of the signal. A plot of the normalized signal is shown below:

Normalized EOG Signal

September 24, 2012 (2 hours): Registered with component manufacturer's and ordered free samples of the following components:

-OPA4131

-ADS1210

-MAX3003

-dsPIC33EP512MU810

-LTC4150

September 25, 2012 (0.5 hours): Downloaded MPLAB IDE v8.87. This will be the IDE that the team will use

to develop all of our microcontroller code in. This particular version of MPLAB was chosen because the course staff had informed us that, based off

of past class experiences, this IDE has had less problems in development. A link to Microchip's webpage with documentation concerning the MPLAB IDE and MPLAB IDE v8.87 can be

found here.

September 26, 2012: Recieved ADS1210 and OPA4131 free samples from Texas Instruments.

September 26, 2012 (3 hours): Searching for electrodes to use in the EOG circuit. It has been decided

to use reusable electrodes over disposable for two main reason. First, it makes the system more mobile and commercially practicle.

Second, I'm worried that constantly changing electrodes will result in inconsistent signals. This issue would likely result in a

large amount of time trying to troubleshoot a system where the electrodes are the problem, also I don't want to be in a position where

we just have to hope that our electrodes will cooperate while demonstrating our PSSC's to the course staff. The electrode characteristics

that are required for our system is that they can operate without special gels or preperation. They should be able to mount directly onto the skin at

their intended position. Electrodes with these characteristics are proving difficult to find. I will contact the course staff to see if they

have any contacts in the biomedical engineering department that can aid me in my search. I was also contacted by a sales representitive from an electrode

company and she referred me to another company that may distribute electrodes that meet the design criteria. I will contact them and see if they distribute

electrodes that meet the design criteria.

September 27, 2012 (0.5 hours): Worked with T.J. Strzlecki and got him up to speed on how our team plans on implimenting a Fast Fourier Transform

to seperate the raw singal from the eeg into it's individual frequency bands. The biggest question regarding how to successfully impiment this is how big each array of raw

signal should be. The problem being if it's too small we wont be realizing the full potential of the device and if it's too big then the algorithm wont be operating at optimal speed.

The first possible solution to this would to review our past class notes regarding Nyquist Rates. I'm somewhat

skeptical on whether or not this will be directly applicable to this particular problem though. I know Nyquist rates are used for digitizing continuous time signals, which isn't really what we need.

It could be applicable in the sense we know what the miniumum frequency bands of the brain signals we want are, so that might coorilate to the number of samples needed in an a array to impliment an optimal FFT.

Another possible solution is to use the array size fom a research project similiar to ours. A link to the research paper can be found here.

September 28, 2012: Recieved dsPIC33 development board with is system programmer as well as disposable electrodes to begin preliminary EOG testing.

September 28, 2012 (1.5 hours): Continued to research and contacting medical electrode manufactures.

WEEK 06 SUMMARY

Accomplishments: Recieving major components and development kits. Downloading the MPLAB IDE onto the team computer.

Began preliminary development into algorithms associated with coorilating the raw EOG signal with specific gesture commands. Contacted multiple electrode manufacturers. Began preliminary research into

decomposition of raw EEG signals.

Weekly Work Total: 11.5 hours

Project Work Total: 125.5 hours

Week 07 (October 1 - October 7)

October 1, 2012 (8 hours): Began researching components used in the microcontroller schematic as well as the EOG schematic. A majority of the time spent was put towards researching voltage regulators and logic level translators. We want to use voltage regulators for simplicity sake but we are starting to become more and more aware that finding a voltage regulator that can supply enough current will be a difficult task. The biggest issue our team is running into is that most voltage regulators rated to supply enough current to power our entire system require is that they require a heatsink pad located underneath the IC that would be required to be soldered to ground. The reason this is an issue is that we simply can't do that with a soldering iron. The biggest requirement we have in terms of a logic level translator is we want input and output information to be transmitted simultaneously. This is an important requirement due to the fact that all of the methods used to communicate amoung subsystems are tranmitted simultaneously. This functionality will also greatly simplify the microcontroller software in the sense that timing is less of a concern. The one major restriction to this is that we wont be able to find a logic level translator that has pins that can be configured as both inputs and outputs and can transmit data. Though this restricts our microcontroller functionality, it also simplifies it's design because we wont have to worry about reconfiguring pins multiple times in software.

October 2, 2012 - October 3, 2012 (15 hours): Finished reasearching components used in the microcontroller and EOG schematic. Once all of the components were selected I began researching the functionality of the

ADS1210. The ADS1210 was chosen due to it's relitively low cost (compared to other analog to digital converter modules with similiar functionality), it's high resolution, the fact it communicates via an SPI interface, it's built in digital filter, it's programmable gain amplifier and it's programmable bias voltage output. The digital filter will be used to further filter all 60Hz noise from external circuitry. The programmable gain amplifier will be used for two major purposes. First, the horizontal and verticle EOG signals differ in magnitude. The programmable gain amplifier allows us to use the same analog EOG circuit despite the fact horizontal and verticle signals require different gains. The second reason a programmable gain amplifier is benificial is that EOG signals vary in magnitude from person to person, and a programmable gain amplifier makes the EOG circuit usable my a larger group of people. The programmable bias output voltage functionality of the ADS1210 is benificial because it eliminates the need for an external circuit that establishes a virtual ground. Since the ADS1210 has differential inputs, +2.5V will be fed from the voltage bias into the noninverting input of the differential amplifier and the EOG signal will be fed into the inverting input. This means that the ADS1210 will transmit a signal that is equal to the difference of 2.5V and the EOG signal. With a sufficient (but still somewhat limited) knowledge of the ADS1210's functionality I was able to complete the EOG schematic and lay out each component's footprint in a general configuration similiar to what should go onto the final PCB.

October 3, 2012 (0 hours): The major critiques from the PCB presentation are as follows:

-Use a switch mode power supply on the microcontroller PCB in order to meet our current requirements more efficiently

-Place all voltage regulation/inversion circuitry as locally as possible.

-Use a smaller package for resistors and capacitors on the EOG circuit.

-Use a different form of logic level translator to simplify the PCB design.

October 3, 2012 (5 hours): After a careful analysis of suggestions made in the PCB presentation, it was decided to continue using the MAX3002 as the logic level translater used on the microcontroller circuit. The reason behind this is though the logic level translator suggested by the course staff is much simplier as far as the schematic/PCB design is concerned, it still requires external timing and pin configuration in order to function properly. We also decided to continue to use a 12-06 package for the resistors and capacitors used in the analog EOG circuitry simply to make the process of soldering each component to the PCB simplier. At this time we plan on incorporating a switching mode regulator but given the time that goes into finding one suitable for our application as well as all of it's additional components, we will have to incorporate it onto our pcb after the preliminary PCB homework is due. We moved the MAX764

voltage inverter IC onto each of the EOG boards as well as included each EOG circuit with it's own MAX8881 voltage regulator.

October 4, 2012 (2 hours): Had a team meeting to check team's progress towards completing items on the to-do-list as well as assigned new items to each team member. A vast majority of these items were pertinent to the formal design review presentation. Once the team meeting had finished we discussed a preliminary communication protocal and how we will modify our schematic and PCB to accomodate said communication. Once that was complete time was spent getting Krishna up to speed with the ADC's functionality.

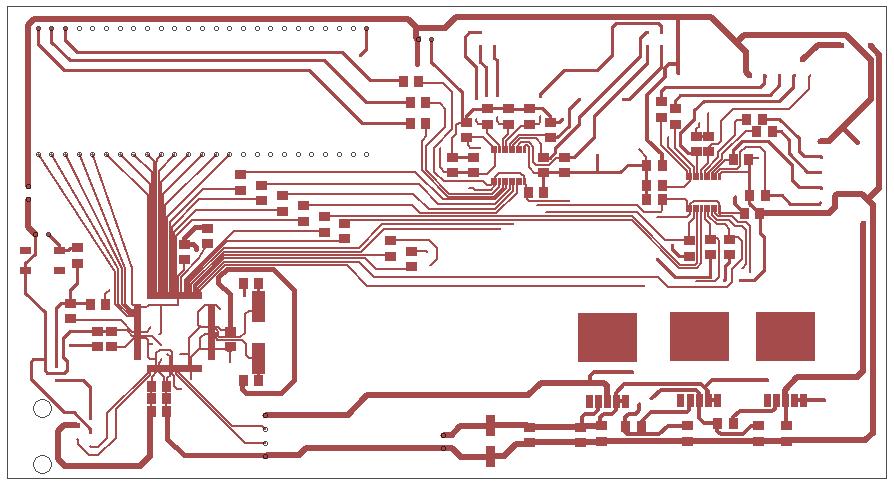

October 4, 2012 (8 hours): Worked on incorporating new design changes previously mentioned into the EOG schematic. Once that was completed time was spent routing all analog EOG circuitry. While working on routing all of the EOG PCB leads, it quicly became clear that it was a mistake creating the schematic and PCB seperately and that it would have been much more efficient to design both simutaniously. It also became clear that trying to only use the 4 operational amplifier package IC is making the PCB and schematic design much more difficult that it needs to be. Future designs will need to incorporate multiple operational amplifier form factors. Once I had completed routing all analog EOG circuitry, T.J. finished all of the remaining work on the PCB. Screen shots of the tob and bottom copper of the EOG and microcontroller PCB are shown below.

Main Components

Main PCB Top Copper

Main PCB Bottom Copper

EOG Components

EOG PCB Top Copper

EOG PCB Bottom Copper

October 5, 2012 (1 hour): Stopped by the lab to insure that T.J. didn't require any additional help with the PCB design homwork and proofread his assignment before submission.

October 5, 2012 (3 hours): Continued researching electrodes as well as contacted electrode manufactures to determine if any of their products could be used in our team's design. Emailed course staff about possible members of Purdue's facility that could help point me in the right direction.

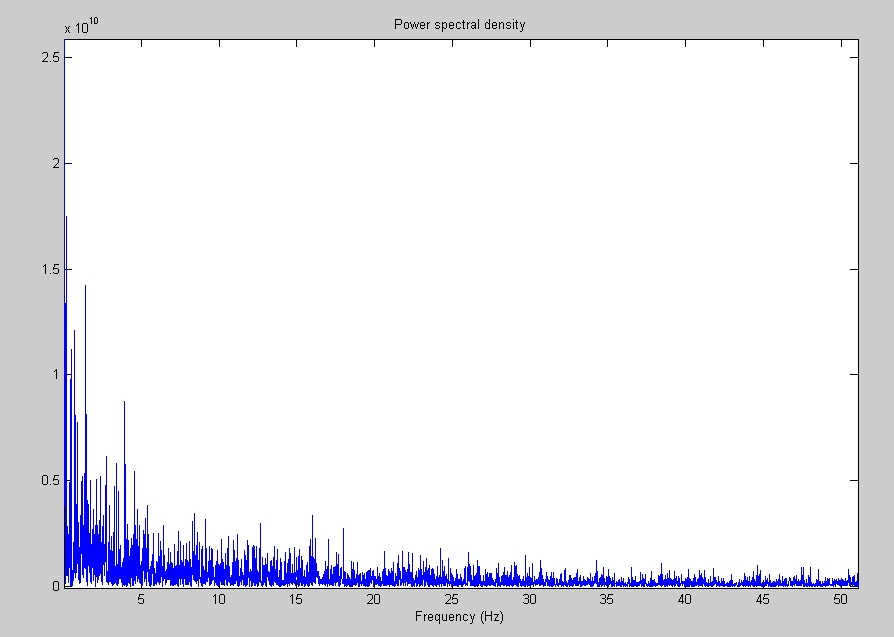

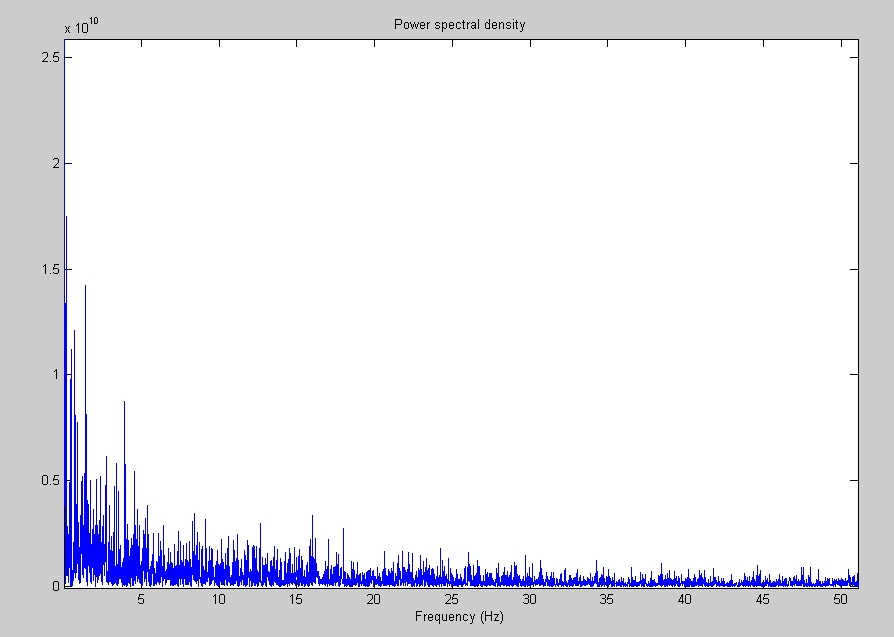

October 5, 2012 (5 hours): Got a functional fast fourier transform based frequency spectrum analysis algorithm working in MATLAB. The program loads a set of raw eeg values transmited from the NeuroSky Mindwave EEG from a csv file, performs a fast fourier transform on the EEG values and plots the magnitude of the signal as a function of frequency. The program was heavly based on sample code provided on the MathWorks website. A link to the sample code can be found

here. The program described above can be found

here. A csv file filled with sample values can be accessed

here. A plot of these sample values' magnitude as a function of frequency is shown below.

EEG FFT Output

October 6, 2012 (4 hours): Began rebuilding the EOG schematic and began constructing a preliminary bill of materials.

October 7, 2012 (5 hours): One of the major concerns my teammates and I have had about our project is that we don't have any real evidence that we will be able to elicite a "selecting mechanism" response with such a poor quality EEG that takes samples from a very non-ideal electrode position at a very poor sampling rate. Another major concern is how accurate the ANN will be with a very limited training set. After conducting much research it was decided to use an ANN to process the EOG signals. Research shows that a network to detect eye gestures can be put together using a simple topology and are effective over a large sample population with limited training. This allows us to develope an artificial neural network in software to interperate EEG signals. The new approach that the team will be taking to select applications on the screen will be through the detection of Steady State Visually Evoked Potential. Documents describing the use of both are given below:

E.O.G Guidance of a Wheelchar Using Neural Networks

A User-Friendly SSVEP-Based BCI Using a Time-Domain Classifier

WEEK 07 SUMMARY

Accomplishments: Completed a preliminary EOG schematic and PCB. Contacted course staff about electrodes to incorporate into our project. Began a preliminary Bill of Materials. Got a functional FFT based frequency spectrum analysis algorithm working in matlab. Decided to use the ANN on the FPGA to analyze EOG signals and to use SSVEP to select applications on the heads up display

Weekly Work Total: 56 hours

Project Work Total: 181.5 hours

Week 08 (October 8 - October 14)

October 9, 2012 (0.5 hours): Spent time getting T.J. and Rick up to speed about the new approach to analyzing the EOG and EEG signals.

October 10, 2012 (8 hours): Spent time researching new components specifically a switch mode power supply. The TPS5420 switch mode regulator will be used to regulate the voltage powering our microcontroller board as well as our single board computer. In the process of creating the slides showing the accuracy of our operational amplifiers, I came across a new and more accurate operational amplifier known as the TLC2272. This operational amplifier comes in a 4 operataional amplifier (TLC2274) package as well as the two operational package. Though the TLC2272 does not come in a single operational amplifier package, Texas Instruments does state that the TLV2211 can be used as its single operational amplifier equivalent. While we were researching these new components we had a quick team meeting so I could fill Krishna in on the new design approach as well as how the a fast fourier transform frequency spectroscopy algorithm works.

October 11, 2012 - October 12, 2012 (10 hours): Recreated the EOG schematic to incorporate multiple operational amplifier form factors as well as begain laying out the newest EOG PCB. While doing this for a second time, I realized that I should have just started over from scratch and built a new circuit instead of trying to modify the old one as well as taken the course staff's advice and layed out the power rails first. At first this would have seemed that this way would have taken much longer, but in reality it just made the PCB exponentially more complicated. T.J. was able to help me by finishing up some of the final routing while I finished the slides for the formal design review.

October 14, 2012 (5.5 hours): Rick, T.J. and I spent time researching and ordering all of the parts needed to complete our PCB proof or parts and submission.

WEEK 08 SUMMARY

Accomplishments: Got team up to speed with new design approach. Researched and ordering new components. Completed formal design review.

Weekly Work Total: 27 hours

Project Work Total: 208.5 hours

Week 09 (October 15 - October 21)

October 15, 2012 (2.5 hours): Continued to research and order new parts.

October 17, 2012 (5 hours): In the process of redlining the PCB, it was descovered that our switch mode power supply can not provide enough current to power the entire system. In order to resolve this issue we needed to find another switching regulator. The switching regulator we chose to use is the LT1374. We will still be using the TPS5420 to provide power to the microcontroller board and will only use the LT1374 to power the single board computer.

October 18, 2012 - October 19, 2012(14 hours): Began work creating the final EOG schematic. Using previous experience, I decided to only use the single form factor operational amplifier to simplify circuit design. Since T.J. is the most skilled member of the team at laying out PCB's, he will be in charge of laying out the PCB once I have finished the schematic. A RCA connection will be used to the PCB because I wanted to find a connector cable that we would be able is easily plugged in while still protecting a sensitive analog signal. The final schematic can be viewed by clicking

here.

WEEK 09 SUMMARY

Accomplishments: Finished the EOG schematic as well as the PCB proof of parts and submission. Selected a new switch mode power supply to provide enough current to the single board computer.

Weekly Work Total: 21.5 hours

Project Work Total: 230 hours

Week 10 (October 22 - October 28)

October 22, 2012 (1 hour): Had a meeting to discuss what needed to be completed and how we could prepare as much as possible for the software design narritive. It was decided that due to my busy schedule that week it would be best if I made it my primary effort to prototype and create a working EOG circuit.

October 25, 2012 (4 hours): Had a quick meeting finalizing communication protocal between each subsystem of the circuit. Began prototyping the EOG circuit, namly the instrumentation amplifier. The first step to doing this was creating a working simulation in PSPICE. Pictures of the PSPICE models of the sample EOG input signal, the instrumentation amplifier,the sallen-key filters and the first order filter/amplifiers are shown below respectively.

EOG_V3_0_Signal

EOG_V3_0_IntAmp

EOG_V3_0_Filters

EOG_V3_0_Amp

Extra time was spent making sure the layout of the EOG circuit on the breadboard was as need and easy to troubleshoot as possible in order to make the process of tuning resistor and capacitor values as simple as possible in the future. A picture of the final prototyped instrumentation amplifier is shown below.

Int Amp Close-Up

In order to test the circuit a 0.1V peak-to-peak square wave was used as an input to the circuit and it's output was compared with it's simulation output. A picture of the prototyped circuit input, the simulation output and the prototype output are shown respectively below.

Int Amp Input

IntAmp_PSPICE_Out

Int Amp Output

October 26, 2012 (10 hours): Began prototyping the EOG filters. Each filter has a gain of 1 and a cut-off frequency of 35Hz. A picture of the final prototyped EOG filter circuit is shown below.

Filter Close-Up

The biggest issue I ran into in the process of prototyping the EOG filters was exactly how to test it. Since there was a gain of 1 there isn't a noticable gain, and I wanted to avoid having to set up multiple functional generators and sum a high frequency and low frequency together. I eventually realized that a simple way to test to see if higher frequencies were being attentuated was to input a signal at 1Hz then briefly turn up the frequency and see if it attentuates the signal. This test was conducted and a picture of the results are shown below.

Filter Response

October 27, 2012 (5 hours): With success in prototyping both the instrumentation amplifier and filters, I began to prototype the EOG amplifiers. A picture of the prototyped amplifiers are shown below.

Amplifier Close-Up

At this point the functional generator could no longer be used to test the EOG circuit due to the fact it can't produce a signal smaller than 10mV peak-to-peak. Due to this I decided to just go ahead and test it. Unfortunately it didn't work. I went though and rechecked to make sure I didn't miss any connections and I wasn't able to find the problem with the circuit. At this point I honestly have no idea what could possible be wrong with the circuit. I went back online and researched other EOG circuitry and realized that a others had designed circuits with gains nearly 5 times mine with a much lower cut-off frequency at ~10-15Hz. A link to the research article used ("Adapted TV Remote Control") can be found by clicking here.

WEEK 10 SUMMARY

Accomplishments: Had a team meeting to discuss and finalize the communication protocal between the major subsystems of our design as well as prototyped the EOG instrumentation amplifier and sallen-key filters.

Weekly Work Total: 20 hours

Project Work Total: 250 hours

Week 11 (October 29 - November 4)

October 29, 2012 (0.5 hours): Had a brief meeting with the team and course staff to discuss the distribution of work amoungst the team.

October 31, 2012 (5 hours): I decided that before I completely redesigned the entire circuit I should figure out a way to test and make sure the circuit actually works prior to moving forward. In order to get a signal small enough to test the EOG circuit without saturating the operational amplifiers I had to create an signal attentuation circuit. With the aid of the signal attentuation circuit, a 1mv peak-to-peak square wave was used as the circuit input. With this test it was discovered that two wires had been mixed up. Once that was corrected I finished tests on the remainder of the circuit. A picture of the completed prototype EOG circuit is shown below.

EOG_V1

I hooked myself up to the prototype circuit to test to see if it was functional. Unfortunately the output of the circuit was completely saturating the operational amplifiers. From there I set the output of the probe to the output of each previous amplifier and at the output of the second amplifier I was able to view a functional EOG signal. A picture of this EOG signal is shown below.

Working Prototype 1 Output Signal

In spite the success from being able to display an actual EOG signal, there are still disign issues that need to be accounted for. The first being that the analog ground needs to be connected directly to the source. When the analog ground is fed through a unity gain buffer it actually distorts the EOG signal. If the analog ground is not connected then motion artifacts greatly distort the signal. This solution will have to be solved by fly wiring the physical analog ground connection to the analog ground plane on the PCB. The second major problem was that there was still a significant amount of noise and distortion in the signal. This distortion consists mostly of a DC bias and random swings that occur in the signal. At this point, it is believed that some of this can be accounted for by the fact that the circuit is built on a solderless breadboard and that aligator clips are used to transfer the signal from the electrodes to the system. In spite of this, I don't want to take the chance that this isn't the source of noise and design to circuit to better compensate for it. In order to further reduce the effect of noise I will place a majority of the gain in the instrumentation amplifier in hopes that raising the common-mode rejection will better eliminate the DC bias. The next major design chance will be to lower the cut-off frequency of the circuit to 15Hz. Hopefully this will better attentuate the random swings that are currently contaminating the signal.

It is worth noting that the signal output is different than the PSPICE simulations. This can be accounted for by human behavior rather than an inaccurate signal/system model. It is human tendency to glance back to the center position immediately after they glance in a given direction. If one were to glance in one direction and continue to look in the same direction the ouput of the circuit would be nearly identical to that in the PSPICE simulation.

December 1, 2012 (3 hour): Practiced soldering with the soldering kits given out in class. Reorganized the component drawer and did a quick inventory of what components we had.

December 1, 2012 (5 hour): Began creating the second prototype of the EOG circuit. The circuit gain is as follows:

-Instrumentation Amplifier Buffer Gain: 30

-Instrumentation Amplifier Differential Amplifier Gain: 10

-First-Order Filter Amplifier #1 Gain: 2

-First-Order Filter Amplifier #2 Gain: 2

-First-Order Filter Amplifier #3 Gain: 2

-First-Order Filter Amplifier #4 Gain: 1.5

-Total Gain: 3600

December 2, 2012 (0.5 hour): Briefly meet up with T.J. to reorganize the bill of materials and determine what still needed to be ordered before I returned home for the weekend.

WEEK 11 SUMMARY

Accomplishments: Created a working EOG prototype and began work on creating a second prototype circuit.

Weekly Work Total: 14 hours

Project Work Total: 264 hours

Week 12 (November 5 - November 11)

November 5, 2012 (5 hours): Ordered the

Battery, the

Battery Charger, the

EOG Electrodes, the

Ear Clip and other miscellaneous components. Once that was completed I began working on choosing components for the second EOG prototype's instrumentation amplifier.

November 6, 2012 (10.5 hours): Began working on the safety and reliability homework as well as the safety and reliability presentation.

November 7, 2012 (3 hours): Finished up final aspects of the safety and reliability presentation and continued to work on the safety and reliability homework.

November 8, 2012 (12 hours): During the presentation, the course staff pointed out that I had been using the maximum junction temperature values which resulted in an unusually low level of reliability. I went back and found more accurate values junction temperature values which drastically raised component reliability. In the process of recalculating these values, a critical design flaw was discovered in the EOG circuit. The amount of power the MAX8881 dissipates from the 11.1V battery will result in device failure. This problem will be solved by keeping the PCB seperate from the battery until it is completely populated and functional, at this point we will need to measure the circuit input impedance and impliment a voltage divider in the connector cable to drop the voltage down to an accpetable level.

November 9, 2012 (1 hour): Prior to submitting the reliability and safety homework, my laptop experienced some type of failure that resulted in everything I had done being completely lost. Time was spent searching for the lost files.

November 10, 2012 (12 hours): Began redoing the entire reliability and safety homework assignment. Had a quick meeting with Rick and Krishna to see what progress had been made. Significant progress had been made with the beagleboard-xm but unfortunately communication between the microcontroller was far from finished. Since Rick had reached a good stopping point with the beagleboard-xm, he put that aside and began to work on communication between the microcontroller and ADS1210 and Krishna will work on establishing a UART connection between the microcontroller and the NeuroSky Mindwave EEG Dongle. While Rick began troubleshooting the previous EOG SPI code, I wired the ADS1210 and logic level translator onto the same breadboard as the EOG prototype. I also made sure to add the functionality to choose between a analog signal from a digital potentiometer or the EOG signal so the ADS1210 testing isn't completely dependent on the EOG prototype to be finished.

November 11, 2012 (8 hours): Finished the reliability and safety homework. red-lined and compleded the digital EOG circuit prototype. A picture of the digital EOG prototype circuit is shown below.

EOG Digital Circuitry

WEEK 12 SUMMARY

Accomplishments: Completed the Reliability and Safety Homework, Discovered an issue with the 5V regulator on the EOG board, redistributed the work load to get the microcontroller development moving faster, Implimented the digital EOG circuitry on the EOG prototype board.

Weekly Work Total: 51.5 hours

Project Work Total: 315.5 hours

Week 13 (November 12 - November 18)

November 12, 2012 (8 hours): Unfortunately no progress had been made establishing communication between the microcontroller and the EEG dongle. I assigned TJ to that task in order to make progress with that task. While working with the microcontroller development board, Rick reported unusually high voltage output signals. Due to noticable scorch marks on parts of the development board, it was decided to request for a different one. There were also concerns that the transition from the development board to our actual system will be made more difficult due to the fact the development boards plug-in-module (PIM) utilizes a different microcontroller. Rick sent in a requested for a new development board and I sent Chuck a purchase form for the Plug-In Module.

November 13, 2012 (10 hours): TJ soldered the microcontroller on the board, and I checked each pin connection with the microscope to verify that no solder bridges were present. The device was recognized but it was not able to program the device. T.J. realized it was soldered on incorrectely and removed it with the heat gun. A new microcontroller was then resoldered onto the PCB in the correct orientation. Once this was done the programmer was no longer recognized the microcontroller. Along with this error it was discovered that now the 3.3V SMPS and the 5V SMPS that powered the beagle board were no longer working. the 3.3V SMPS voltage was reduced to ~0.8V and the 5V SMPS was outputting 0V. After a close analysis two capacitors that were found to be no longer functional. New power supply components were ordered to correctly supply power to the microcontroller in hopes that the heatgun somehow damaged our power supplies, and that the faulty power supplies were causing the microcontroller programming errors.

November 14, 2012 (12 hours): Time was spent designing the second EOG prototype. I had doubts that the previous EOG design had a true Butterworth response due to the fact its band-pass wasn't optimally flat. Upon further research, I discovered that I wouldn't be able to get a true Butterworth response with the cascaded first order low-pass filters that were integrated into the amplifier stage. The filters were removed from the amplifier stage and I began work on a new MATLAB component selection algorithm.

November 15, 2012 (10 hours): Continued to research Butterworth polynomials and how to incorporate them into a new selection algorithm. Other modifications to the part selection algorithm include an updated inventory of the parts in both the ECE 477 and ECE 402 design lab.

November 16, 2012 (5 hours): Finshed the final component selection algorithm. The code for this algorithm can be found here.TJ had replaced all of the power supply components and the issue was not resolved.

November 17, 2012 (10 hours): I started the day fully dedicated to troubleshooting the problem with the microcontroller board. It was descovered that a short had occured between power and ground somewhere in the micrcontroller setup. Because of the short, a current limiting transistor had been activated in the 3.3V power supply causing it to shut down. It was also discovered that the 3.3V output was the enabiling input to the 5V SMPS, which explains why that power supply was also failing. My best guess to the cause of the issue was a decoupling capacitor had been damaged during removal of the second microcontroller and was now shorting the system. TJ later informed me that the VSS and VCC had been mixed up on the microcontroller, which was causing the short in our system. This means that the microcontroller needed to be removed again in order to cut traces underneath the microcontroller. I began work on the PSPICE simulation circuit for the second EOG prototype. TJ and I had a brain-storming session about how to normalize EOG data from the 24-bit external ADC to the 5-bit transfer lines. No practicle solution was found and we decided to aproach the problem again tomorrow.

November 18, 2012 (7 hours): Researched and found new logic level translators to use for communication between the beagleboad and the microcontroller board. A link to these logic level translators can be reached

here. Continued to work on the Second EOG prototype in PSPICE.

WEEK 13 SUMMARY

Accomplishments: Created new MATLAB algorithm to aid in the design of an EOG circuit with an true Butterworth response, found new Logic Level Translators, Began development on PSPICE EOG prototype, found short between power and ground on microcontroller board.

Weekly Work Total: 62 hours

Project Work Total: 377.5 hours

Week 14 (November 19 - November 25)

November 19, 2012 (8 hours): Finished second EOG prototype in PSPICE. The Simulation Schematic can be found by clicking here. The circuit's frequency response is shown below.

Frequency Response

I met with T.J. and we decided that, given the time left in the semester and the problem with the data resolution, that we abandon the ANN on the FPGA and create a new selection algorithm based solely on 'esense' values.

November 20, 2012 (7 hours): Finished the second EOG prototype on the breadboard. As expected, the DC bias was reduced and the noise rejection improved. TJ and I went out and purchased plastic sheets that will be used to build the enclosure as well as a bike helmet to build the frame onto.

November 21, 2012 (6 hours): Time was spent creating an initial prototype for the helmet enclosure in cardboard. Cardboard was chosen becuase we had it in ample supply, it was easy to cut and it can be used as a stencil to accurately cut the plastic sheets one the prototype was finished.

November 22, 2012 (10 hours): Continued to work on the helmet enclosure prototype. Purchased a power supply switch and ski goggles to mount the EOG electrodes on. The battery charger terminals were also converted from aligator cips to a USB outlet in order to prevent someone from accidentally switching the polarity of the charger.

November 23, 2012 (10 hours): Finished the helmet enclosure prototype and ordered the resistors and capacitors used in the EOG circuit.

November 24, 2012 (5 hours): Soldered jumpers onto the EOG board. A new RJ-11 connector arrived and we attempted to program the microcontroller. The issue with the power supplies were resolved but unfortunately the ICSP problem wasn't resolved. Time was spent re-examining the circuit with hopes of the problem. After some research online, I discovered that some people had similiar errors that were resolved with reinstalling MPLAB X. I reinstalled all of the software and this didn't resolve the problem either.

November 25, 2012 (4 hours): Continued to troubleshoot the microcontroller problem. Time was spent trying to see if this error was the result of misconfigured software. no solution was found. Upon analysis of the power rails, T.J. and I discovered that the power and ground rails were extremly noisy. We disconnected them from the circuit and tried to power the microcontroller externally, unfortunatley this didn't resolve the issue either.

WEEK 14 SUMMARY

Accomplishments: Finished preliminary enclosure. Purchased final enclosure building materials. Resloved power supply issues. Still no solution to the ICSP problem.

Weekly Work Total: 42 hours

Project Work Total: 419.5 hours

Week 15 (November 26 - December 2)

November 26, 2012 (8 hours): Talked to chuck about power issues, he suggested that we cut the ground around the micro and jump it to the ground closest to the power supply to reduce the noise. this was done and noise was reduced. Discussed ways to reduce noise on 3.3V line with Rick and T.J. It was decided to use a regulator from the clean 5V supply going to the beagle board. T.J. found a regulator at radioshack and realized it was able to handle the 11.1V input. so it was hooked up to that instead of the 5V output. Continued to troubleshoot the circuit, no solution was found.

November 27, 2012 (10 hours): At this point we are operating under the assumption that our microcontroller had experienced ESD damage. The basis for this conclusion is that we know that it was recieving a clean 3.3V from the programmer and the microcontroller that we're using was the one used in the proof of parts submission, which means it was handled a lot prior to being put on the board. thankfully T.J. had ordered more after we removed the second microcontroller. I briefly tested the eog board and was getting a constant -5V output. checked all connections and at first glance nothing was wrong. I plan on returning to this issue once we've made more significant progress towards finding the error with the microcontroller.

November 28, 2012 (10 hours): Got course staff up to speed with our accomplishments as well as our current issues (namely the inability to program the microcontroller on the board.) we discussed the possibility of ESD and asked for their permission that under the circumstances that we would not be able to successfully debug the ICSP if we could use the PIM as a proof of concept. We realize that this would be far from ideal, but we agreed that though it is a VERY last resort, it would be better than nothing. Chuck told us that it would be better if he removed the microcontroller this time and that our board can only handle removing a 100 pin micro so many times before it is completely destroyed, and that we would be better off with if he used his tools and experience. He removed it with no damage to the board. He also recommended we watch the programming lines on our board and the dev board and see what the differences were. The only major difference observed was that the MCLR pin didn't go entirely low. We attributed this to power supply noise, which would be consistent with the information online. All sources of noise will be removed from the circuit including the oscillator circuit and old decoupling capacitors. I also went and reread some of the microcontroller literature to see if there were any setup errors in our circuit. It was found that we weren't supply current to the usb pin, which if unused needed to be connected to VCC. worked with rick to build the logic level translator circuit to test the connection between the beagleboard and the microcontroller dev board. We realized that the unusually high voltage levels were attributed to not having a common ground between the beagle board and the microcontroller development board.

November 29, 2012 (1 hour): The USB VCC was connected and we still had the same problem. I spent some time looking into possible misconfigurations with MPLAB that could result in the programming error. Nothing was found.

November 30, 2012 (12 hours): Created the new 3D models for the user manual and worked with TJ and Rick to revise components of the user manual that krishna had wrote, wrote parts of the user manual that were pertinant to the EOG circuitry and funtionality. Began troubleshooting the EOG board, found an error in the EOG schematic where a (+) and (-) had been mixed up. I cut the traces to those pins and fly wired the inputs to their correct traces. in the process of flywiring the wires, one of our eog boards was dammaged from esd. Tj had passed me the board when while I didn't have an anti-static wrist band on and a loud zap was heard. from that point on the board escentially was completely unfunctional. there wasn't enough time to order new parts and a new board so we decided to scrap vertical EOG capabilities. This meant that rick was going to have to update the GUI. An error on the EOG PCB was found where the high pass filter intigrated into the input buffers of the instrumentation amplifier had been completely bypassed. My best guess to how this error occured was due to the fact that the schematic was made prior to laying out the PCB and that both the schematic and PCB were made by two different people. another error was traced to a suspected opamp that no always seemed to output -5V regaurdless of what the imput was. My first guess was that there was that an incorrect resistor was placed on the PCB which resulted in a extremely large gain which was saturating the amplifier. after checking the values, they all ended up being correct. tj removed all discrete components and it was found that the output is always -5V even with no input signal. the op amp was removed and the issue wasn't resolved, this meant that it wasn't coming from the output but rather the input from the next op amp. a new op amp was soldered on and the other op amp was replaced. swapping out this op amp resolved the issue and we now had a functional analog EOG circuitry.

December 1, 2012 (12 hours): I performed my final tests on the EOG board and determined that the circuit was more stable when using the disposable electrodes rather that the electrodes mounted on the goggle frame. Though I would prefer to use the electrodes on the frame, it is likely we will use the disposable electrodes. The final decision depends on the accuracy of the k-nearest neighbor algorithm. Time was spent trying to find issues with the programmer. without being able to find any problems in how we had set up MPLAB X, I went through an analyized our ICSP circuit. One error that I had found was that we had a decoupling capacitor at the VCC that was connected to MCLR. I cut this decoupling capacitor and though it slightly improved the signal at the MCLR pin, it didn't resolve the issue. My attention then turned the all of the connections to the MCLR pin. The devices that could be influencing the connection at that pin included the debounce switch and a 2-resistor network. I doubt that it's the debounce IC because it's output is connected to VCC through a jumper terminal which is disconnected. My guess was that it had to do with the resistor set up. R1 was there for current limiting purposes, which was not needed with a 10K resistor. by removing R1, the voltage drop across R would be greater and a lower voltage would be read at MCLR, which could possibly resolve the issue.

December 2, 2012 (5 hours): TJ had adjusted the values of the resistors and though improving the signal, it didn't remove the problem. After testing this, TJ was able to find the problem. The problem came from the debounce IC. The output of the debounce IC was supplying voltage to the MCLR line when the programmer was trying to drive it low, which made the microcontroller impossible to program. I began cutting out some of the plastic components that were going to be used in the final enclosure. started programming the k-nearest neighbor algorithm.

WEEK 15 SUMMARY

Accomplishments: Found the solution to the microcontroller programming problem. Got the EOG PCB analog circuitry completely functional

Weekly Work Total: 60 hours

Project Work Total: 479.5 hours

Week 16 (December 3 - December 7)

December 3, 2012 (6 hours): Rick T.J. and I tested to see if our microcontroller was able to program with our previous noisy power supply. Unfortunately it was not able to. Since we had plenty of op amps, I decided to use one of our TLC2274 DIP op amp IC to create a filter for the power supply. The circuit was desined and created in PSPICE. I measured the current output and unfortunately it was nowhere near high enough to supply enough current to our microcontroller circuitry. We decided to stick with the regulator setup and completely disconnect the 3.3V switch mode power supply from the circuit. Continued working on the k-nearest neighbor algorithm and aided T.J. in assembling the final helmet enclosure. We tried powering the system from the battery but the beagle board wasn't able to start up. While watching the power-supply output on the oscilloscope, a current spike caused in the beagleboard's initial configuration was causing the power supply to cut power to the board. We then looked at the battery output and the battery was no longer providing a 11.1V DC output. We determined that the battery protection circuitry had been damaged due to an instance where I had accidently shorted the two power leads several days back. A new battery was going to have to be purchased. I located an RC Hobby Store in the west lafayette area that sold batteries that met our requirements.

December 4, 2012 (12 hours): Finished the k-nearest neighbor algorithm. Went to the RC hobby store and purchased a new battery. The customer service was outstanding and they were able to find a battery that met our requirements almost immediatly. We tested to see whether it was able to function as a power supply for our circuit, unfortunatly the same problem occured. The only possible source of the problem would be with the switch mode power supply itself. Incorrect component selection seemed unlikely seeing as it was able to provide up to 4.5A and the beagleboard would at most require 3A. After close examination of the power supply circuit an incorrect connection in the schematic was found. this connction was corrected, the problem was resolved, and we could now power the entire system from a single battery.

December 5, 2012 (3 hours): After showing the k-nearest neighbor algorithm to Rick and Tj, they informed me that my program could not be implemented on the microcontroller due to the fact I used several functions that utilized recursion. I went back and modified my previous program to function without recursion. The final k-nearest neighbor algorithm can be found by clicking here.

December 6, 2012 (1.5 hours): Time was spent with T.J. and Rick trying to aid their software issues as much as possible. I updated the block diagram for the final homework assignment and helped demostrating some of our devices functionality for the royal design showcase video. I rewired another ADC circuit prototype.

December 8, 2012 (2 hours): Had a meeting with Rick, Tj and Krishna to discuss individual contribution to the project and what will go into the final report and final presentation.

WEEK 16 SUMMARY

Accomplishments: Fixed issues with beagleboard power supply. Finished k-nearest neighbor selection algorithm.

Weekly Work Total: 24.5 hours

Project Work Total: 504 hours