Device-to-System Modeling

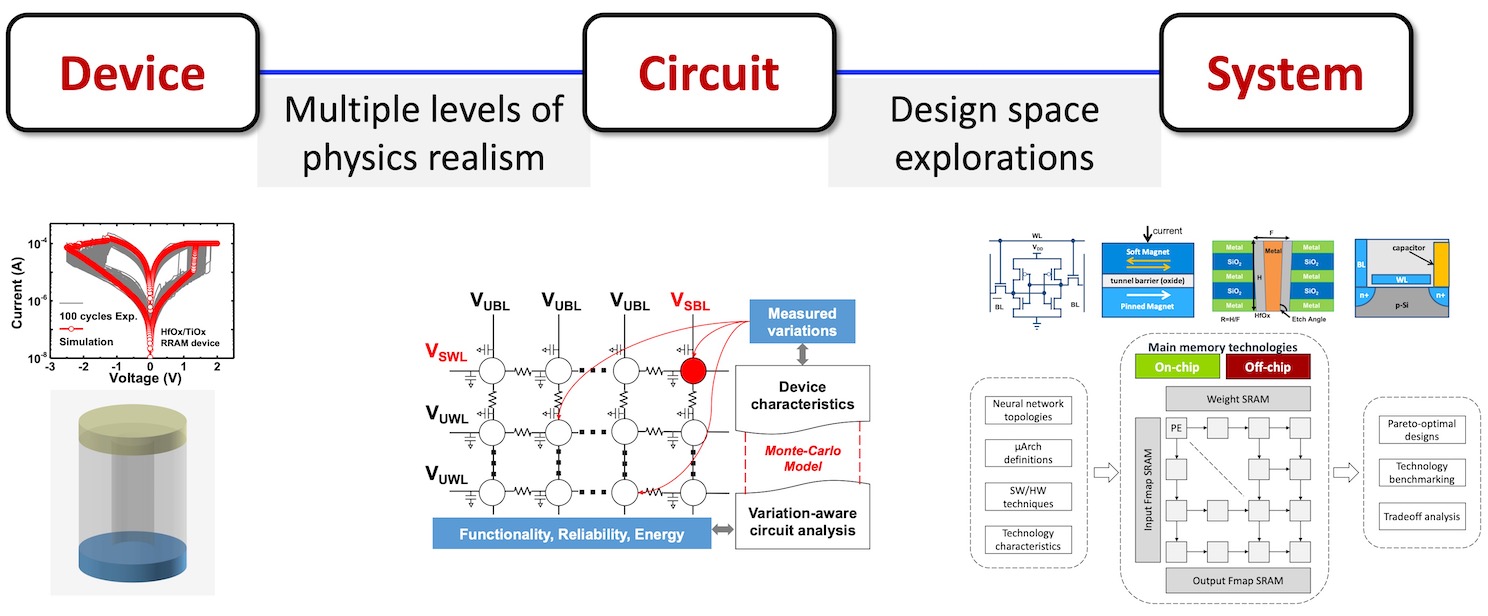

Cross-layer modeling for non-volatile memory technologies to understand the interactions across various layers of abstraction, down to device physics.

Modeling serves as a “common ground” while both technologies and applications keep evolving. It also allows one to understand the interactions across various layers of abstraction, down to device physics, and enables circuit and system design explorations. This becomes particularly important when new device physics is involved. We have done extensive case studies with non-volatile memories and in particular, resistive RAM (RRAM).

At the device level, we develop an RRAM SPICE model having a hierarchy of three model levels. With experimental calibration on metal-oxide RRAM devices, the developed RRAM model can facilitate circuit designs and analysis with different design needs, without loss of physics realism.

At the circuit level, we develop a full-array Monte Carlo modeling framework for variation-aware RRAM circuit analysis, leading to a deeper understanding of device-circuit interaction and co-optimization.

At the system level, a technology-system design space exploration framework is developed to explore on-chip memory technologies (SRAM, eDRAM, MRAM, 3D RRAM) for edge DNN accelerators in mobile SoCs. The analysis indicates that dense memory-compute integration provides ample opportunities for energy and area efficiency through optimal chip resource partition.

Related publications:

DAC 2019, TCAS-I 2017, TED 2017, DATE 2015