# Exploration of Interplay between Charge Trapping Dynamics and Polarization Switching in α-In<sub>2</sub>Se<sub>3</sub> Ferroelectric Semiconductor FETs

Minah Park, Jaewook Yoo, Seohyeon Park, Hongseung Lee, Hyeonjun Song, Soyeon Kim, Seongbin Lim, Sojin Jung, Gang Qiu, Sungjune Park, TaeWan Kim, Peide D. Ye, *Fellow*, *IEEE*, and Hagyoul Bae, *Member*, *IEEE*

Abstract—The trap behavior in a two-dimensional (2D) ferroelectric semiconductor (FeS) field-effect transistors (FETs) that can overcome the device scaling limit of conventional ferroelectric FETs was analyzed. The conventional ferroelectric FETs exhibit a counterclockwise hysteresis loop, whereas ferroelectric channel-based FETs with high effective oxide thickness exhibit a clockwise hysteresis loop. Therefore, it is challenging to determine the contribution of ferroelectric polarization switching and trap states to the current conduction of FeS-FETs and to quantify their respective impacts, owing to their complex interaction. The modified conductance method with a four-element equivalent circuit model was employed to analyze the behavior of intrinsic trap states, with parasitic capacitance de-embedded, depending on the polarization switching states. As a result, we confirmed that over the full energy range trap density can be extracted by unique characteristics of FeS-FETs. The retention characteristic was maintained at over 70 % of the initial memory on/off ratio when extrapolated to 104 s. Based on these results, guidelines for undefined trap state behavior of 2D α-In<sub>2</sub>Se<sub>3</sub> FeS-FETs were presented.

Index Terms—Alpha-indium selenide ( $\alpha$ -ln<sub>2</sub>Se<sub>3</sub>), ferroelectric semiconductor field-effect transistors (FeS-FETs), intrinsic trap states ( $D_{\text{trap}}$ ), modified conductance method (MCM), nonvolatile memory device.

Manuscript received 2 May 2025; This work was supported by the Nano & Material Technology Development Program through the National Research Foundation of Korea (NRF) funded by Ministry of Science and ICT (RS-2024-00460372), in part by the Samsung Electronics University R&D program, in part by the Institute of Information & Development for Local Intellectualization program grant funded by the Korea government (MSIT) (IITP-2025-RS-2024-00439292), and in part by Jeonju City under the Semiconductor Specialized University Project. The EDA tool was supported in part by the IC Design Education Center (IDEC).

M. Park, J. Yoo, S. Park, H. Lee, H. Song, S. Kim, S. Lim, S. Jung, and H. Bae are with the Department of Electronic Engineering, Jeonbuk National University, Jeonju 54896, Republic of Korea (e-mail: hagyoul.bae@jbnu.ac.kr). G. Qiu is with the Department of Electrical and Computer Engineering, University of Minnesota, Minneapolis, MN 55455, USA. S. Park is with the School of Chemical Engineering, Sungkyunkwan University, Suwon 16419, Republic of Korea. T.W. Kim is with the School of Advanced Fusion Studies and Department of Intelligent Semiconductor Engineering, University of Seoul, Seoul 02504, Republic of Korea. P. D. Ye is with the School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN 47907, USA.

# I. INTRODUCTION

$I_{n_2}Se_3$  exhibits ferroelectricity in the  $\alpha$ -/ $\beta$ -phase. In particular, **L**α-In<sub>2</sub>Se<sub>3</sub> demonstrates interlocking between out-of-plane (OOP) and in-plane (IP) polarization at room temperature, resulting in strong spontaneous polarization [1], [2], [3], [4], [5]. OOP and IP polarizations can be controlled by both planar and vertical electric fields, making α-In<sub>2</sub>Se<sub>3</sub> suitable for multiterminal device applications, unlike other ferroelectrics that only have controllable OOP polarization [6], [7], [8]. In addition,  $\alpha$ -In<sub>2</sub>Se<sub>3</sub> is a two-dimensional (2D) material with a bandgap energy of 1.46 eV, characterized by its ultrathin geometry, free dangling bonds across the interface, easy manipulation for integration with other materials, and no limit of critical thickness, which is the primary problem in conventional ferroelectric films [9], [10], [11], [12].  $\alpha$ -In<sub>2</sub>Se<sub>3</sub> is expected to provide a solution to nonvolatile memory applications currently facing scaling limitations. However, unlike conventional ferroelectric field-effect transistors (FETs), hysteresis a counterclockwise ferroelectric-semiconductor (FeS)-FETs with high effective oxide thickness (EOT) have a clockwise hysteresis loop [13]; thus, the hysteresis direction in FeS-FETs reflects the combined influence of both trap states and ferroelectric polarization switching. Therefore, accurate analysis of trap states is necessary to address the performance degradation and confusion in the device's operation, for example, threshold voltage instability, memory window reduction, and on/off ratio lowering [14], [15]. Nevertheless,  $\alpha$ -In<sub>2</sub>Se<sub>3</sub> is still in the early stages of research, hence, the specific characterization of the device's properties is yet to be fully established. In this work, for the first time, we quantitatively analyzed the intrinsic trap density of α-In<sub>2</sub>Se<sub>3</sub> FeS-FETs after de-embedding parasitic capacitance based on the modified conductance method (MCM), in consideration of the unique operation mechanism of α-In<sub>2</sub>Se<sub>3</sub> FeS-FETs.

# II. EXPERIMENTS

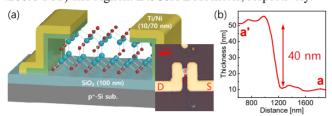

Fig. 1(a) depicts a schematic of the device, which indicates both the down and up states of ferroelectric polarization. The optical microscopy (OM) image of fabricated  $\alpha$ -In<sub>2</sub>Se<sub>3</sub> FeS-FETs can be shown in the inset image.  $\alpha$ -In<sub>2</sub>Se<sub>3</sub> flakes were transferred by using a mechanical exfoliation method on a 100 nm-SiO<sub>2</sub>/p<sup>+</sup>-Si substrate. The channel width (W) and length

Exploration of Interplay between Charge Trapping Dynamics and Polarization Switching In α-In<sub>2</sub>Se<sub>3</sub> Ferroelectric Semiconductor FETs

(L) of the  $\alpha$ -In<sub>2</sub>Se<sub>3</sub> FeS-FETs were 6  $\mu$ m and 4  $\mu$ m, respectively. The thickness of the transferred flake was confirmed to be 40 nm by using the atomic force microscopy (AFM) line profile, as shown in Fig. 1(b). Subsequently, Ti/Ni (10/70 nm) was deposited via e-beam evaporation as source (S) and drain (D) contacts, patterned by the photolithography process. The current-voltage (I-V) and capacitance-voltage (C-V)characteristics of the fabricated α-In<sub>2</sub>Se<sub>3</sub> FeS-FETs were measured by a semiconductor parameter analyzer (Keithley 4200A-SCS) and Agilent E4980A LCR meter, respectively.

Fig. 1. (a) Device schematic reflecting polarization-down and -up states of the ferroelectric channel material with inset OM image and (b) AFM line profile of α-In<sub>2</sub>Se<sub>3</sub> flake.

## III. RESULTS AND DISCUSSION

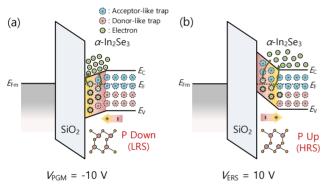

Fig. 2. Energy band diagram of α-In<sub>2</sub>Se<sub>3</sub> FeS-FETs at ferroelectric (a) polarization-down state and (b) polarization-up state, which indicates the behavior of trap state.

Figs. 2(a) and (b) show the energy band diagram of  $\alpha$ -In<sub>2</sub>Se<sub>3</sub> FeS-FETs at ferroelectric polarization-down and -up states, respectively. In the partially polarization-down state induced by a negative gate bias  $(V_{GS})$ , band bending due to the polarization charge increases the density of free carriers near the insulator/channel interface, inducing a low resistance state (LRS) in FeS-FETs with high EOT gate oxide. Concurrently, band bending caused by an internal electric field due to the polarization charge enhances the predominance acceptor-like trap behavior. Conversely, when positive  $V_{GS}$  was applied, the polarization was partially switched to upstate. Owing to the band bending by the internal electric field caused by the polarization charge, the free carrier near the insulator/channel interface is depleted and also donor-like trap behavior is dominated. In addition, free carriers could not be accumulated on the top side of the channel by the high EOT, resulting in a high resistance state (HRS).

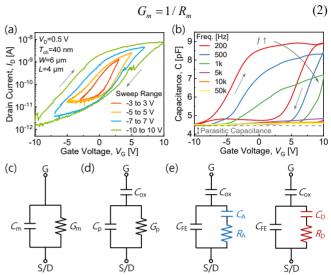

Fig. 3(a) shows the transfer characteristics of the  $\alpha$ -In<sub>2</sub>Se<sub>3</sub> FeS-FETs, which indicate a clockwise gate hysteresis loop, reflecting the unique operation mechanism mentioned above. The multifrequency C-V curve is shown in Fig. 3(b). Free carriers were excited from the channel trap states by the frequency and  $V_{GS}$ , enabling the quantitative extraction of trap states according to the frequency dispersion. The parallel mode capacitance-conductance (C<sub>m</sub>-G<sub>m</sub>) was obtained from the measured capacitance-dissipation factor  $(C_m-D_m)$  using the following equation:

$$D_m = 1/\omega C_m R_m \tag{1}$$

Fig. 3. (a) Transfer characteristics and (b) frequency-dispersive C-V curve of fabricated α-In<sub>2</sub>Se<sub>3</sub> FeS-FETs. Equivalent circuit model of (c) a two-element model for the parallel mode  $C_m$ - $G_m$ , (d) a three-element model for the  $C_{ox}$  including parallel mode  $C_p$ – $G_p$ , and (e) a four-element model for the  $C_{ox}$  including parallel mode  $C_{FE}$ - $C_A/R_A$  or  $-C_D/R_D$ according to polarization switching states.

As presented in Figs. 3(c) and (d),  $C_m$ – $G_m$  was converted into oxide capacitance ( $C_{ox}$ ) and parallel capacitance-conductance  $(C_p-G_p)$ . Subsequently, depending on the polarization  $C_{\rm p}$ – $\hat{G}_{\rm p}$ switching states, was converted frequency-dependent acceptor- or donor-like trap capacitance  $(C_A \text{ or } C_D)$ /resistance  $(R_A \text{ or } R_D)$ , which are physical parameters related to the capture and emission of free carriers, in parallel with the  $\alpha$ -In<sub>2</sub>Se<sub>3</sub> ferroelectric channel capacitance ( $C_{\text{FE}}$ ), shown in Fig. 3(e). The intrinsic capacitance  $(C_{m,int})$  without parasitic capacitance  $(C_{par})$ , which is inevitably included because of the S/D metal overlap region, was calculated from the measured C-V curves [16].  $G_p/\omega$  was calculated as the following equation:

$$C_{\text{m,int}} = C_{\text{m}} - C_{\text{par}} [F] \tag{3}$$

$$C_{\text{m,int}} = C_{\text{m}} - C_{\text{par}} [F]$$

$$\frac{G_{\text{p}}}{\omega} = \frac{\omega G_{\text{m,int}} C_{\text{ox}}^2}{G_{\text{m,int}}^2 + \omega^2 (C_{\text{ox}} - C_{\text{m,int}})^2} = \frac{q \omega \tau_{\text{trap}} D_{\text{trap}}}{1 + (\omega \tau_{\text{trap}})^2} [S \cdot s]$$

(4)

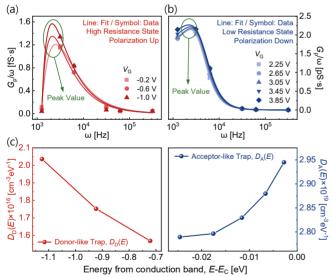

Here,  $G_{m,int}$  is the intrinsic conductance;  $D_{trap}$  is the intrinsic trap density, which represents either acceptor-like trap density  $(D_A(E))$  or donor-like trap density  $(D_D(E))$ , depending on the polarization switching state;  $\tau_{\text{trap}}$  (= $R_{\text{trap}} \cdot C_{\text{trap}}$ ) is the time constant; and  $\omega$  (=2 $\pi f$ ) is the angular frequency. The obtained  $G_p/\omega$  was plotted as a function of  $\omega$ , shown in Figs. 4(a) and 4(b) at polarization-down and -up states, respectively.  $D_{\text{trap}}$  is obtained from the maximum value of  $G_p/\omega$  at  $\omega=1/\tau_{trap}$  as follows:

$$C_{\text{trap}} = \frac{2 \times G_{\text{p,max}}}{\omega} \tag{5}$$

Exploration of Interplay between Charge Trapping Dynamics and Polarization Switching In α-In<sub>2</sub>Se<sub>3</sub> Ferroelectric Semiconductor FETs

$$D_{\text{trap}} = \frac{(dQ_{\text{trap}}(E)/dE)}{W \times L \times T_{\text{ch}}} = \frac{(dQ_{\text{trap}}(E)/dV_{\text{G}})}{W \times L \times T_{\text{ch}} \times q}$$

$$= \frac{C_{\text{trap}}}{W \times L \times T_{\text{ch}} \times q} \left[ \text{cm}^{-3} \cdot \text{eV}^{-1} \right]$$

(6)

The extracted and characterized by energy distribution  $D_{\text{trap}}$  profiles, with the frequency- and  $V_{\text{GS}}$ -dependent trapped charge  $(Q_{\text{trap}})$  inside the energy bandgap, are shown in Fig. 4(c) as a function of surface potential  $(\psi_{\text{S,A}}$  and  $\psi_{\text{S,D}})$  as expressed in (7) and (8), respectively:

$$\psi_{S,A} = \int_{V_{FB}}^{V_{on}} (1 - \frac{C_{m,int}}{C_{ov}}) dV_{G} \text{ [eV]}$$

(7)

$$\psi_{S,D} = \int_{V_{FB}}^{V_{off}} (1 - \frac{C_{m,int}}{C_{ox}}) dV_{G} \text{ [eV]}$$

(8)

Herein, the  $\psi_{S,A}$  and  $\psi_{S,D}$  was calculated from the flat band voltage to the voltage representing the on and off states in both LRS and HRS. In LRS, integration proceeded in a positive direction, while in HRS, it proceeded in the negative direction, mapping to the energy levels near the conduction and valence band, respectively. The  $\psi_S$  corresponding to the voltage range, where the effective  $G_P/\omega$  peak appears, was used to represent  $D_{\text{trap}}$  within the subgap energy region.  $D_A(E)$  and  $D_D(E)$  were extracted from  $2.79 \times 10^{19}$  cm<sup>-3</sup>eV<sup>-1</sup> to  $2.94 \times 10^{19}$  cm<sup>-3</sup>eV<sup>-1</sup> and from  $1.57 \times 10^{16}$  cm<sup>-3</sup>eV<sup>-1</sup> to  $2.04 \times 10^{16}$  cm<sup>-3</sup>eV<sup>-1</sup> at polarization-down and -up states, respectively, within the subgap energy range. We note that the interface and bulk traps have a high density near the conduction band ( $E_C$ ) and valence band ( $E_V$ ) rather than near the midgap energy [17], resulting in the order of magnitude difference between  $D_A(E)$  and  $D_D(E)$ .

Fig. 4. The obtained  $G_p/\omega$  from the MCM with a four-element model at (a) polarization-up and (b) -down states, respectively. (c) The  $D_{\text{trap}}$  was extracted separately for donor-like traps near the  $E_V$  and acceptor-like traps near the  $E_C$ , considering polarization switching states.

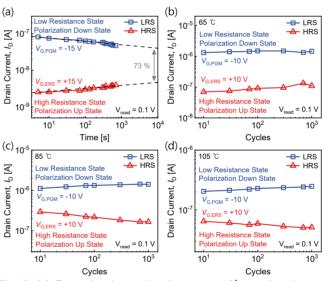

The retention and endurance characteristics for investigating the ferroelectric memory device reliability of the  $\alpha$ -In<sub>2</sub>Se<sub>3</sub> FeS-FETs were measured and shown in Fig. 5. In the retention characteristics, when linearly extrapolated to  $10^4$  s, the LRS and HRS states remained over 70 % compared to the initial data.

The endurance characteristics were measured with the program and erase repeated at -10 V and 10 V, respectively. The LRS and HRS states of fabricated FeS-FETs were maintained over the  $10^3$  program/erase cycles under various operation temperatures of 65 °C, 85 °C, and 105 °C.

It's noteworthy that band bending caused by ferroelectric polarization charge determines the types of trap states, which affect the transfer characteristics of FeS-FETs. Hence, trap states were extracted at polarization-down and -up states using the frequency-dispersive conductance method excluding parasitic capacitance. The energy profile of trap states can be extracted using C-V characteristics that precisely measure the time constant by examining the trapping/de-trapping speed of through frequency-dependent behaviors. C-V-based trap analysis techniques are suitable for an intuitive, quantitative, and accurate evaluation of the spatial distribution of trap states compared to the I-V-based analysis method. Therefore, the proposed technique in this study is expected to be extensively utilized for analyzing trap states in FeS-FETs. While this study provides critical insight into the role of electrically active traps associated with polarization switching, further studies are required to clarify the correlation between the physical mechanisms and electrical characteristics, considering device geometry and polarization switching behavior.

Fig. 5. (a) Extrapolated retention time up to 10<sup>4</sup> s and endurance characteristics for 10<sup>3</sup> cycles under (b) 65 °C, (c) 85 °C, and (d) 105 °C for investigating the reliability of ferroelectric memory device.

# IV. CONCLUSION

In this work, for the first time, the trap states behavior of 2D ferroelectric  $\alpha$ -In<sub>2</sub>Se<sub>3</sub> FeS-FETs was investigated through the frequency-dispersive C-V characteristics de-embedding the  $C_{\rm par}$ . The acceptor- and donor-like trap density in the polarization-down and -up states were extracted over the full range of subgap energy levels in high EOT  $\alpha$ -In<sub>2</sub>Se<sub>3</sub> FeS-FETs. We expect that the proposed technique will become an effective tool for analyzing the unique behavior of trap density in FeS-FETs, which have not yet been fully understood.

8

### REFERENCES

- [1] W. Ding, J. Zhu, Z. Wang, Y. Gao, D. Xiao, Y. Gu, Z. Zhang, and W. Zhu, "Prediction of intrinsic two-dimensional ferroelectrics in In<sub>2</sub>Se<sub>3</sub> and other III<sub>2</sub>-VI<sub>3</sub> van der Waals materials," *Nat. Commun.*, vol. 8, Apr. 2017, Art. no. 14956, doi: 10.1038/ncomms14956.

- [2] C. Cui, W.-J. Hu, X. Yan, C. Addiego, W. Gao, Y. Wang, Z. Wang, L. Li, Y. Cheng, P. Li, X. Zhang, H. N. Alshareef, T. Wu, W. Zhu, X. Pan, and L.-J. Li, "Intercorrelated in-plane and out-of-plane ferroelectricity in ultrathin two-dimensional layered semiconductor In<sub>2</sub>Se<sub>3</sub>," *Nano Lett.*, vol. 18, no. 2, pp. 1253–1258, Feb. 2018, doi: 10.1021/acs.nanolett.7b04852.

- [3] Y. Chen, M. Zhang, D. Li, Y. Tang, H. Ren, J. Li, K. Liang, Y. Wang, L. Wen, W. Li, W. Kong, S. Liu, H. Wang, D. Wang, and B. Zhu, "Bidirectional synaptic phototransistor based on two-dimensional ferroelectric semiconductor for mixed color pattern recognition," ACS Nano, vol. 17, no. 13, pp. 12499-12509, Jun. 2023, doi: 10.1021/acsnano.3c02167.

- [4] F. Xue, W. Hu, K.-C. Lee, L.-S. Lu, J. Zhang, H.-L. Tang, A. Han, W.-T. Hsu, S. Tu, W.-H. Chang, C.-H. Lien, J.-H. He, Z. Zhang, L.-J. Li, and X. Zhang, "Room-temperature ferroelectricity in hexagonally layered α-In<sub>2</sub>Se<sub>3</sub> nanoflakes down to the monolayer limit," *Adv. Funct. Mater.*, vol. 28, no. 50, Oct. 2018, Art. no. 1803738, doi: 10.1002/adfm.201803738.

- [5] Y. Li, C. Chen, W. Li, X. Mao, H. Liu, J. Xiang, A. Nie, Z. Liu, W. Zhu, and H. Zeng, "Orthogonal electric control of the out-of-plane field-effect in 2D ferroelectric α-In<sub>2</sub>Se<sub>3</sub>," Adv. Electron. Mater., vol. 6, no. 7, Jun. 2020, Art. no. 2000061, doi: 10.1002/aelm.202000061.

- [6] T. Jin, J. Mao, J. Gao, C. Han, K. P. Loh, A. T. S. Wee, and W. Chen, "Ferroelectrics-integrated two-dimensional devices toward next-generation electronics," ACS Nano, vol. 16, no. 9, pp. 13595-13611, Sep. 2022, doi: 10.1021/acsnano.2c07281.

- [7] F. Guo, W. F. Io, Z. Dang, R. Ding, S.-Y. Pang, Y. Zhao, and J. Hao, "Achieving reinforcement learning in a three-active-terminal neuromorphic device based on a 2D vdW ferroelectric material," *Mater. Horizons*, vol. 10, pp. 3719-3728, Jun. 2023, doi: 10.1039/D3MH00714F.

- [8] Y. Chen, D. Li, H. Ren, Y. Tang, K. Liang, Y. Wang, F. Li, C. Song, J. Guan, Z. Chen, X. Lu, G. Xu, W. Li, S. Liu, and B. Zhu, "Highly linear and symmetric synaptic memtransistors based on polarization switching in two-dimensional ferroelectric semiconductors," *Small*, vol. 18, no. 45, Sep. 2022, Art. no. 2203611, doi: 10.1002/smll.202203611.

- [9] P. Gao, Z. Zhang, M. Li, R. Ishikawa, B. Feng, H.-J. Liu, Y.-L. Huang, N. Shibata, X. Ma, S. Chen, J. Zhang, K. Liu, E.-G. Wang, D. Yu, L. Liao, Y.-H. Chu, and Y. Ikuhara, "Possible absence of critical thickness and size effect in ultrathin perovskite ferroelectric films," *Nat. Commun.*, vol.

- 8, Jun. 2017, Art. no. 15549, doi: 10.1038/ncomms15549.

- [10] Q. He, Z. Tang, M. Dai, H. Shan, H. Yang, Y. Zhang, and X. Luo, "Epitaxial growth of large area two-dimensional ferroelectric α-In<sub>2</sub>Se<sub>3</sub>," Nano Lett., vol. 23, no. 7, pp. 3098-3105, Feb. 2023, doi: 10.1021/acs.nanolett.2c04289.

- [11] A. Belianinov, Q. He, A. Dziaugys, P. Maksymovych, E. Eliseev, A. Borisevich, A. Morozovska, J. Banys, Y. Vysochanskii, and S. V. Kalinin, "CuInP<sub>2</sub>S<sub>6</sub> room temperature layered ferroelectric," *Nano Lett.*, vol. 15, no. 6, pp. 3808-3814, May. 2015, doi: 10.1021/acs.nanolett.5b00491.

- [12] M. Dai, K Li, F. Wang, Y. Hu, J. Zhang, T. Zhai, B. Yang, Y. Fu, W. Cao, D. Jia, Y. Zhou, and P. Hu, "Intrinsic dipole coupling in 2D van der Waals ferroelectrics for gate-controlled switchable rectifier," *Adv. Electron. Mater.*, vol. 6, no. 2, Nov. 2019, Art. no. 1900975, doi: 10.1002/aelm.201900975.

- [13] M. Si, A. K. Saha, S. Gao, G. Qiu, J. Qin, Y. Duan, J. Jian, C. Niu, H. Wang, W. Wu, S. K. Gupta, and P. D. Ye, "A ferroelectric semiconductor field-effect transistor," *Nat. Electron.*, vol. 2, pp. 580-586, Dec. 2019, doi: 10.1038/s41928-019-0338-7.

- [14] N. Gong and T.-P. Ma, "A study of endurance issues in HfO<sub>2</sub>-based ferroelectric field effect transistors: Charge trapping and trap generation," *IEEE Electron Device Lett.*, vol. 39, no. 1, pp. 15-18, Jan. 2018, doi: 10.1109/LED.2017.2776263.

- [15] C. Garg, N. Chauhan, A. Sharma, S. Banchhor, A. Doneria, S. Dasgupta, and A. Bulusu, "Investigation of trap-induced performance degradation and restriction on higher ferroelectric thickness in negative capacitance FDSOI FET," *IEEE Trans. Electron Devices*, vol. 68, no. 10, pp. 5298-5304, Oct. 2021, doi: 10.1109/TED.2021.3105952.

- [16] S. Kim, A. Konar, W.-S. Hwang, J. H. Lee, J. Lee, J. Yang, C. Jung, H. Kim, J.-B. Yoo, J.-Y. Choi, Y. W. Jin, S. Y. Lee, D. Jena, W. Choi, and K. Kim, "High-mobility and low-power thin-film transistors based on multilayer MoS<sub>2</sub> crystals," *Nat. Commun.*, vol. 3, Aug. 2012, Art. no. 1011, doi: 10.1038/ncomms2018.

- [17] G. Rodrigues-Fontenele, G. Fontenele, M. R. Valentim, L. V. C. Freitas, G. Rodrigues-Junior, R. Magalães-Paniago, and A. Malachias, "Structural and electronic response of multigap n-doped In<sub>2</sub>Se<sub>3</sub>: A prototypical material for broad spectral optical devices," ACS Appl. Mater. Interfaces, vol. 16, no. 37, pp. 49902-49912, Sep. 2024, doi: 10.1021/acsami.4c08610.