## $_{\beta}\text{--}\text{Ga}_2\text{O}_3$ on insulator field-effect transistors with drain currents exceeding 1.5 A/mm and their self-heating effect

Hong Zhou, Kerry Maize, Gang Qiu, Ali Shakouri, and Peide D. Ye

Citation: Appl. Phys. Lett. 111, 092102 (2017); doi: 10.1063/1.5000735

View online: http://dx.doi.org/10.1063/1.5000735

View Table of Contents: http://aip.scitation.org/toc/apl/111/9

Published by the American Institute of Physics

## Articles you may be interested in

Modulation-doped  $\beta$ -(Al<sub>0.2</sub>Ga<sub>0.8</sub>)<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> field-effect transistor Applied Physics Letters **111**, 023502 (2017); 10.1063/1.4993569

Electron paramagnetic resonance study of neutral Mg acceptors in β-Ga<sub>2</sub>O<sub>3</sub> crystals

Applied Physics Letters 111, 072102 (2017); 10.1063/1.4990454

Terahertz spectroscopy of an electron-hole bilayer system in AIN/GaN/AIN quantum wells Applied Physics Letters 111, 073102 (2017); 10.1063/1.4996925

High responsivity in molecular beam epitaxy grown  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> metal semiconductor metal solar blind deep-UV photodetector

Applied Physics Letters 110, 221107 (2017); 10.1063/1.4984904

Improved interface properties of GaN-based metal-oxide-semiconductor devices with thin Ga-oxide interlayers Applied Physics Letters **110**, 261603 (2017); 10.1063/1.4990689

Highly conductive homoepitaxial Si-doped  $Ga_2O_3$  films on (010)  $\beta$ - $Ga_2O_3$  by pulsed laser deposition Applied Physics Letters **111**, 012103 (2017); 10.1063/1.4991363

## β-Ga<sub>2</sub>O<sub>3</sub> on insulator field-effect transistors with drain currents exceeding 1.5 A/mm and their self-heating effect

Hong Zhou, Kerry Maize, Gang Qiu, Ali Shakouri, and Peide D. Ye<sup>a)</sup> School of Electrical and Computer Engineering and Birck Nanotechnology Center, Purdue University, West Lafayette, Indiana 47907, USA

(Received 12 April 2017; accepted 17 August 2017; published online 28 August 2017)

We have demonstrated that depletion/enhancement-mode  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> on insulator field-effect transistors can achieve a record high drain current density of 1.5/1.0 A/mm by utilizing a highly doped  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> nano-membrane as the channel.  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> on insulator field-effect transistor (GOOI FET) shows a high on/off ratio of  $10^{10}$  and low subthreshold slope of 150 mV/dec even with 300 nm thick SiO<sub>2</sub>. The enhancement-mode GOOI FET is achieved through surface depletion. An ultra-fast, high resolution thermo-reflectance imaging technique is applied to study the self-heating effect by directly measuring the local surface temperature. High drain current, low R<sub>c</sub>, and wide bandgap make the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> on insulator field-effect transistor a promising candidate for future power electronics applications. *Published by AIP Publishing*. [http://dx.doi.org/10.1063/1.5000735]

Recently,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> has shown its great promise for next generation high power device applications due to its ultra-wide bandgap of 4.6–4.9 eV. This allows  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> to possess a corresponding empirical estimated electrical breakdown field (E<sub>br</sub>) of 8 MV/cm, which is several times higher than GaN and SiC. Despite the very early development stage, depletionmode (D-mode) β-Ga<sub>2</sub>O<sub>3</sub> metal-oxide-semiconductor fieldeffect transistors (MOSFETs) have demonstrated a high blocking voltage of 750 V and an E<sub>br</sub> of 3.8 MV/cm (Refs. 2 and 3) and enhancement-mode (E-mode) MOSFET has shown a breakdown voltage (BV) of more than 600 V. <sup>4</sup> β-Ga<sub>2</sub>O<sub>3</sub> metal-semiconductor field-effect transistors (MESFETs) and Schottky barrier diodes (SBDs) have also demonstrated a BV of 257 V and 1000 V, respectively. 5,6 In addition to the excellent direct current (DC) breakdown characteristic, a high pulsed drain current (ID) of 478 mA/mm has also been achieved for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs.<sup>7</sup> Until very recently, radio frequency (RF) performance of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET was demonstrated, yielding cut off frequency and maximum oscillation frequency ( $f_T$  and  $f_{max}$ ) of 3.3 GHz and 12.9 GHz, respectively. Meanwhile,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> also has the advantage of a lowcost native bulk substrate that can be synthesized in large size through melt-grown Czochralski, edge defined film fed growth, and floating zone method. 9-14 However, a crucial disadvantage of this material is its low thermal conductivity of 0.1-0.3 W/cm·K depends on its various crystal orientation. 15,16 One of the approaches to solve the low thermal conductivity issue of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is to introduce a high thermal conductivity substrate rather than the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> native substrate. Our previous study has demonstrated a high performance  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> on insulator field-effect transistors (GOOI FETs) by transferring  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> nano-membrane or nano-belts to SiO<sub>2</sub>/Si substrate with SiO<sub>2</sub> thickness of 300 nm to mitigate gate-drain overlap breakdown and serve as gate dielectric as well. The monoclinic structure of bulk  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> crystals would allow a facile cleavage into nano-membrane along the [100] direction even though  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is not a van der Waals

2D material, possibly due to its large lattice constant of 12.23 Å along this [100] direction. <sup>18</sup>

To realize all merits of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> as a power device, there are still some challenges to be encountered ahead. The reported D/E mode maximum drain current density (I<sub>DMAX</sub>) for GOOI FETs are 600/450 mA/mm and continuous wave DC of 200 and 2 mA/mm for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> homoepitaxial D/E mode MOSFETs, respectively. 19,20 How to further enhance the device performance in terms of higher I<sub>DMAX</sub> and lower on-resistance (Ron) and make them comparable to GaN and SiC technologies remained to be demonstrated. In this letter, we have shown that by increasing the doping concentration of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> nano-membrane and further scale the device, the I<sub>DMAX</sub> of D/E-mode GOOI FETs can achieve a record value of 1.5/1.0 A/mm, which is around twice of previous record I<sub>DMAX</sub>. Our results reveal that the contact resistance (R<sub>c</sub>) can also be reduced by highly doped channel. Finally, we have evaluated the thermal effect of GOOI FETs and observed the pronounced self-heating effect by using an ultra-fast, high resolution thermo-reflectance (TR) imaging technique.

In our experiment, n-type Sn doping concentration (n) of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is determined to be  $8.0 \times 10^{18} \, \text{cm}^{-3}$  from Capacitance-Voltage (C-V) measurement. 21 The thickness of (100)  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> nano-membranes vary from 50 to 70 nm determined by atomic force microscopy (AFM) measurements with surface roughness of 0.33 nm, and the D/E-mode devices are achieved based on the thickness of the nanomembranes. More details about the device fabrication can be found in our previous work.<sup>17</sup> For comparison, devices with lower doping concentration of  $3.0 \times 10^{18} \,\mathrm{cm}^{-3}$  were also fabricated. Figures 1(a) and 1(b) are device schematic and AFM image of a fabricated device, respectively. The device electric characterizations were carried out with Keithley 4200 Semiconductor Parameter Analyzer. A Microsanj TR system with a high-speed light-emitting diode (LED) pulse and a synchronized charge coupled device (CCD) camera was used for the thermal measurement. 22–25

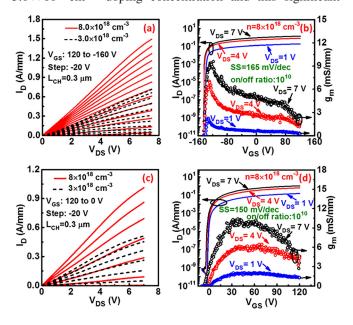

Figure 2(a) presents the DC output characteristics ( $I_D$ - $V_{DS}$ ) of D-mode GOOI FETs. Devices have a channel

a)Author to whom correspondence should be addressed: yep@purdue.edu

FIG. 1. (a) Schematic cross-section view of a GOOI FET with a 300 nm  $SiO_2$  layer on Si substrate and (b) AFM image of fabricated GOOI FET with  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> nano-membrane thickness of 70 nm.

length ( $L_{CH}$ , also source to drain spacing  $L_{SD}$ ) of 0.3  $\mu$ m, channel width (W) of 0.15 µm and channel thickness (t) of 70 nm for  $8.0 \times 10^{18} \, \text{cm}^{-3}$ , and  $W = 0.6 \, \mu \text{m}$  and  $t = 100 \, \text{nm}$ for  $3.0 \times 10^{18} \, \text{cm}^{-3}$  device. The device dimensions are accurately determined by scanning electron microscopy (SEM). A record high I<sub>DMAX</sub> of 1.5 A/mm is obtained, which is more than 2 times of lower doping channel. Compared with our previous work with  $L_{CH} = 0.87 \,\mu\text{m}$  and  $3.0 \times 10^{18} \,\text{cm}^{-3}$ doping concentration, the I<sub>DMAX</sub> of same doping device with  $L_{CH} = 0.3 \,\mu m$  increased from 600 to 750 mA/mm for D-mode. D-mode GOOI FET with n of  $3 \times 10^{18} \, \text{cm}^{-3}$  and  $L_{CH}$  of 0.3  $\mu$ m has a  $R_{C}$ ,  $R_{SH}$ , and  $R_{on}$  of 4.5  $\Omega$  mm, 5.6  $k\Omega$ /  $\square$ , and 11  $\Omega$  mm, showing that the total contact resistance  $(2R_C)$  of  $9\Omega$  mm is dominate. Therefore, further scaling the L<sub>CH</sub> shows no significant effect in boosting the I<sub>DMAX</sub>, which is mainly limited by the high R<sub>C</sub> of lower doped channel underneath the contacts. The much improved I<sub>DMAX</sub> of 1.5 A/mm mainly originates from the higher doping concentration induced lower R<sub>c</sub> rather than the simply channel length scaling.<sup>26</sup> The high doping device also has a much lower  $R_{on}$  of 5.3  $\Omega$  mm compared with that of 11  $\Omega$  mm with  $3.0 \times 10^{18} \, \text{cm}^{-3}$  doping concentration and this significant

FIG. 2. (a) and (c)  $I_{D^-}V_{DS}$  output characteristics of D-mode and E-mode GOOI FETs with  $3.0\times10^{18}$  and  $8.0\times10^{18}\,\mathrm{cm^{-3}}$  doping channel, respectively. (b) and (d)  $I_{D^-}g_{m^-}V_{GS}$  transfer characteristics of D-mode and E-mode GOOI FETs with  $8.0\times10^{18}\,\mathrm{cm^{-3}}$  doping channel, respectively. Record high  $I_{DMAX}$  of 1.5 and 1.0 A/mm are demonstrated for D/E mode devices. Both D and E-mode devices have high on/off ratio of  $10^{10}$  and low SS of  $150-165\,\mathrm{mV/dec}$  for  $300\,\mathrm{nm}$  SiO $_2$ .

lower  $R_{on}$  is mostly from the much reduced  $R_C$  of 1.7  $\Omega$  mm. At low V<sub>DS</sub> regime, high doping I<sub>D</sub>-V<sub>DS</sub> shows linear behavior with lower R<sub>c</sub> while the lower doping counterpart displays a Schottky-like contacts with higher R<sub>c</sub>. Figure 2(b) is the log-scale I<sub>D</sub>-g<sub>m</sub>-V<sub>GS</sub> transfer characteristics of the same D-mode GOOI FET with  $8.0 \times 10^{18} \,\mathrm{cm}^{-3}$  doping concentration. This D-mode GOOI FET has a threshold voltage (V<sub>T</sub>) of -135 V, extracted from the log-scale  $I_D$ - $V_{GS}$  at  $V_{DS} = 1 \text{ V}$ and  $I_D = 0.1 \text{ mA/mm}$ . A peak transconductance  $(g_{max})$  of 9.2 mS/mm is achieved which is 2 times of the g<sub>max</sub> with lower doping concentration, showing the much improved R<sub>c</sub> of the higher doping concentration device. Figures 2(c) and 2(d) depict the I<sub>D</sub>-V<sub>DS</sub> output and I<sub>D</sub>-g<sub>m</sub>-V<sub>GS</sub> transfer characteristics of an E-mode GOOI FET with  $L_{CH}=0.3~\mu m$ , t=55~nm, and  $W=0.17~\mu m$  for  $8.0\times 10^{18}~cm^{-3}$ , and t=75~nm and  $W=0.45~\mu m$  for  $3.0\times 10^{18}~cm^{-3}$  device also shown in Fig. 2(c) as black dashed curves for comparison. Similar to D-mode devices, lower doped E-mode GOOI FETs have an increased I<sub>dmax</sub> from 450 mA/mm to 550 mA/mm when the  $L_{CH}$  is scaled from 1.3  $\mu$ m to 0.3  $\mu$ m. Higher E-mode  $I_{DMAX}$ is also achieved with higher doping concentration induced lower  $R_c$  of 0.75  $\Omega$  mm compared to that of 1.2  $\Omega$  mm with lower doping concentration. A record high  $I_{DMAX} = 1.0 \,\text{A/}$ mm for higher doping channel is obtained, which is more than 80% higher than lower doping channel. E-mode GOOI FET has a  $V_T$  of 2 V determined from the  $I_D$ - $V_{GS}$  at  $V_{DS} = 1 \text{ V}$ and  $I_D = 0.1 \, \text{mA/mm}$ . Unfortunately, no  $I_D$  saturation is observed since applying higher V<sub>DS</sub> will lead to an abrupt I<sub>D</sub> increase and then device breakdown. The drain induced barrier lowering (DIBL) is extracted to be 0.73 and 0.38 V/V for D/E-modes devices, respectively. Finally, benefited from its wide-bandgap and high quality interface between  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and SiO<sub>2</sub>, both D/E-mode devices have achieved high on/off ratio of 10<sup>10</sup> and low subthreshold slope (SS) of 150–165 mV/ dec for 300 nm SiO<sub>2</sub>.

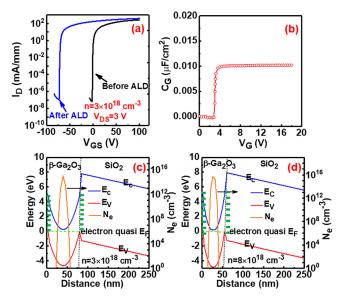

The significant V<sub>T</sub> shift with respect to different  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> nano-membrane thickness is due to the surface depletion effect of the unpassivated GOOI FET surface. This is because Sn-doped  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is a 3D semiconductor, which has dangling bonds and surface states on the device surface. Surface depletion could deplete the whole  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> nanomembrane tens of nanometers thick. This is the reason why E-mode GOOI FETs can also be realized in high doping  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> nano-membrane. The surface depletion effect is verified by using atomic layer deposition (ALD) to deposit 15 nm Al<sub>2</sub>O<sub>3</sub> on top to passivate the top surface. As shown in Fig. 1, the V<sub>T</sub> is significantly shifted to the left for more than 70 V after the ALD passivation, showing the existence of top and bottom surface depletion on unpassivated GOOI FET surfaces. Similar surface or interface charges induced depletion effect was also observed by Moser et al. Based on the surface depletion, we can obtain each surface depleted charge density (n<sub>s</sub>) by using the technology computer aided design (TCAD) C-V simulation to match the measured and simulated  $V_T$  from E-mode devices with  $V_T$  near zero. The  $n_s$  is determined and simulated to be  $1.2 \times 10^{13} \,\text{cm}^{-2}$  and  $2.2 \times 10^{13} \,\text{cm}^{-2}$  for  $3.0 \times 10^{18} \, \mathrm{cm}^{-3}$  and  $8.0 \times 10^{18} \, \mathrm{cm}^{-8}$  nano-membranes with thickness of 80 nm and 55 nm, respectively. Therefore, the flatband voltage (VFB) for lower doped and high doped devices are determined to be 135 V and 235 V through the equation  $V_{FB} = \Phi_{MS}/e-2n_s/C_{ox}$ , where  $\Phi_{MS}$ , e, and  $C_{ox}$  are gate-semiconductor work function difference, electron charge quantity, and oxide capacitance, respectively. Higher  $n_s$  for higher doping  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> nano-membrane is most likely related to the higher surface states with more Sn<sup>4+</sup> dopants. Therefore, the actual C-V curve and  $I_D$ -V<sub>GS</sub> curve are significantly shifted to the right compared with the ideal case without considering surface depletion. Figure 2 shows the simulated C-V curve for E-mode GOOI FET and the  $V_T$  from C-V simulation is in good agreement with the  $V_T$  from  $I_D$ -V<sub>GS</sub> characterization. Figure 3 is the simulated band diagram of the E-mode GOOI FET at  $V_{GS} = 0$  V with lower doping and high doping channels by considering surface depletion effect. The top and bottom depletion regions pull up the conduction band of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> with very few carriers left behind in the nano-membrane.

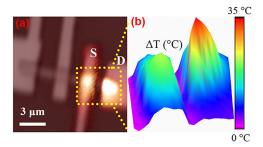

As a low thermal conductivity material and also its substrate, the heat dissipation is a big issue for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> devices which needs to be seriously considered. We have used an ultra-fast TR set-up to study its thermal property. The system has a high-speed LED pulse illumination and a CCD camera to image temperature dependent reflectance change. Briefly, the source/drain Au pads are illuminated through an LED  $(\lambda = 530 \text{ nm})$ , and the change in reflectance under bias is calibrated with Au thermo-reflectance coefficient to translate into temperature change. Figure 4(a) is the CCD camera and TR image merged view of another D-mode GOOI FET device with  $V_{DS} = 4 V$  and  $V_{GS} = 0 V$  with  $I_D = 0.3 A/mm$ . Figure 4(b) shows the 3D view of the TR image along the channel length and channel width directions. Even at a low bias power regime (P= $V_{DS} \times I_{D} = 1.2 \, \text{W/mm}$ ), the local temperature has increased by 35 °C compared to room temperature or unbiased devices. It seems that there is a "cold" channel between source and drain contact. This is because

FIG. 3. (a)  $I_D\text{-}V_{GS}$  comparison between GOOI FETs with and without ALD passivation for  $\beta\text{-}Ga_2O_3$  nano-membrane with doping concentration of  $3.0\times10^{18}\,\text{cm}^{-3}$ , (b) simulated C-V curve for E-mode GOOI FET at a  $\beta\text{-}Ga_2O_3$  nano-membrane thickness of  $80\,\text{nm}$  and doping concentration of  $3.0\times10^{18}\,\text{cm}^{-3}$  after considering the top and bottom negative surface charge  $(n_s=1.2\times10^{13}\,\text{cm}^{-2})$  depletion effect. Band diagram and electron density distribution of E-mode GOOI FETs with surface negative charge depletion on (c) lower doping  $(n_s=1.2\times10^{13}\,\text{cm}^{-2})$  and (d) high doping  $(n_s=2.2\times10^{13}\,\text{cm}^{-2})$   $\beta\text{-}Ga_2O_3$  nano-membrane channels at  $V_{GS}=0\,\text{V}$ .

FIG. 4. (a) CCD camera and TR image merged temperature change on the source and drain sides of back-gate GOOI FETs. (b) 3D view of the TR image of GOOI FET. The device is biased at  $V_{DS}=4\,V,\,V_{GS}=0\,V,$  and  $I_D=0.3\,A/mm.$  The temperature is calibrated for the S and D gold electrodes.

the thermal reflectance coefficient of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> channel is more than 10 times lower than that of Au electrodes. The temperature measurement is only calibrated with Au surface and we use Au electrodes as the thermometer of the device. Higher power bias will increase device temperature more significantly, and lead to degrade electron mobility and reliability, and eventually breakdown the device. Other self-heating effects induced  $I_D$  reduction was observed by Moser and Wong *et al.*<sup>27,28</sup> The work by applying large thermal conductivity substrates and advanced device structures to mitigate the self-heating effect for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs is on-going and will be reported elsewhere.

We have demonstrated record high  $I_{DMAX}$  of 1.5/1.0 A/mm for D/E-mode GOOI FETs by increasing the  $\beta$ -Ga $_2$ O $_3$  doping concentration from  $3.0 \times 10^{18}$  to  $8.0 \times 10^{18}$  cm $^{-3}$  and further scaling the channel length. The significant  $V_T$  shift with respect to different  $\beta$ -Ga $_2$ O $_3$  nano-membrane thicknesses is due to the surface depletion effect of the unpassivated GOOI FET surface. High on/off ratio of  $10^{10}$  and low SS of 150 mV/dec are achieved. Self-heating effect is also directly observed with the TR measurement. GOOI FETs with wide bandgap, high  $I_{DMAX}$ , and low  $R_c$  offer the promise in the power device applications if the low thermal conductivity issue can be solved.

The authors thank the technical guidance from the Sensors Directorate of Air Force Research Laboratory.

<sup>&</sup>lt;sup>1</sup>M. Higashiwaki, K. Sasaki, H. Murakami, Y. Kumagai, A. Koukitu, A. Kuramata, T. Masui, and S. Yamakoshi, Semicond. Sci. Technol. 31, 034001 (2016).

<sup>&</sup>lt;sup>2</sup>M. H. Wong, K. Sasaki, A. Kuramata, S. Tamakoshi, and M. Higashiwaki, IEEE Electron Device Lett. **37**, 212 (2016).

<sup>&</sup>lt;sup>3</sup>A. J. Green, K. D. Chabak, E. R. Heller, R. C. Fitch, M. Baldini, A. Fiedler, K. Irmscher, G. Wagner, Z. Galazka, S. E. Tetlak, A. Crespo, K. Leedy, and G. H. Jessen, IEEE Electron Device Lett. 37, 902 (2016).

<sup>&</sup>lt;sup>4</sup>K. D. Chabak, N. Moser, A. J. Green, D. E. Walker, Jr., S. E. Tetlak, E. Heller, A. Crespo, R. Fitch, J. P. McCandless, K. Leedy, M. Baldini, G. Wagner, Z. Galazka, X. Li, and G. Jessen, Appl. Phys. Lett. 109, 213501 (2016).

<sup>&</sup>lt;sup>5</sup>M. Higashiwaki, K. Sasaki, A. Kuramata, T. Masui, and S. Yamakoshi, Appl. Phys. Lett. **100**, 013504 (2012).

<sup>&</sup>lt;sup>6</sup>K. Konishi, K. Goto, H. Murakami, Y. Kumagai, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, Appl. Phys. Lett. 110(10), 103506 (2017).

<sup>&</sup>lt;sup>7</sup>N. A. Moser, J. P. Mccandless, A. Crespo, K. D. Leedy, A. J. Green, E. R. Heller, K. D. Chabak, N. Peixoto, and G. H. Jessen, Appl. Phys. Lett. 110, 143505 (2017).

- <sup>8</sup>A. J. Green, K. D. Chabak, M. Baldini, N. Moser, R. C. Gilbert, R. Fitch, G. Wagner, Z. Galazka, J. Mccandless, A. Crespo, K. Leedy, and G. H. Jessen, IEEE Electron Device Lett. 38, 790 (2017).

- <sup>9</sup>K. Irmscher, Z. Galazka, M. Pietsch, R. Uecker, and R. Fornari, J. Appl. Phys. 110, 063720 (2011).

- <sup>10</sup>Z. Galazka, K. Irmscher, R. Uecker, R. Bertram, M. Pietsch, A. Kwasniewski, M. Naumann, T. Schulz, R. Schewski, D. Klimm, and M. Bickermann, J. Cryst. Growth 404, 184 (2014).

- <sup>11</sup>H. Aida, K. Nishighuchi, H. Takeda, N. Aota, K. Sunakawa, and Y. Yaguchi, Jpn. J. Appl. Phys., Part 1 47, 8506 (2008).

- <sup>12</sup>A. Kuramata, K. Koshi, S. Watanabe, Y. Yamaoka, T. Masui, and S. Yamakoshi, Jpn. J. Appl. Phys., Part 1 55, 1202A2 (2016).

- <sup>13</sup>N. Ueda, H. Hosono, R. Waseda, and H. Kawazoe, Appl. Phys. Lett. **70**, 3561 (1997).

- <sup>14</sup>E. G. Víllora, K. Shimamura, Y. Yoshikawa, K. Aoki, and N. Ichinose, J. Cryst. Growth 270, 420 (2004).

- <sup>15</sup>M. D. Santia, N. Tandon, and J. D. Albrecht, Appl. Phys. Lett. **107**, 041907 (2015).

- <sup>16</sup>Z. Guo, A. Verma, X. Wu, F. Sun, A. Hickman, T. Masui, A. Kuramata, M. Higashiwaki, D. Jena, and T. Luo, Appl. Phys. Lett. 106, 111909 (2015).

- <sup>17</sup>H. Zhou, M. Si, S. Alghamdi, G. Qiu, L. Yang, and P. D. Ye, IEEE Electron Device Lett. **38**, 103 (2017).

- <sup>18</sup>W. S. Hwang, A. Verma, H. Peelaers, V. Protasenko, S. Rouvimov, H. Xing, A. Seabaugh, W. Haensch, C. Van de Walle, Z. Galazka,

- M. Albrecht, R. Fornari, and D. Jena, Appl. Phys. Lett. 104, 203111 (2014).

- <sup>19</sup>S. Krishnamoorthy, Z. Xia, S. Bajaj, M. Brenner, and S. Rajan, Appl. Phys. Express 10, 051102 (2017).

- <sup>20</sup>M. H. Wong, Y. Nakata, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, Appl. Phys. Express 10, 041101 (2017).

- <sup>21</sup>K. Maize, J. Christofferson, and A. Shakouri, in *Proceedings of the 24th IEEE SEMI-THERM Symposium* (2008), p. 55.

- <sup>22</sup>H. Zhou, S. Alghamdi, M. W. Si, and P. D. Ye, IEEE Electron Device Lett. 37, 1411 (2016).

- <sup>23</sup>K. Maize, A. Ziabari, W. D. French, P. Lindorfer, B. OConnell, and A. Shakouri, IEEE Trans. Electron Devices 61, 3047–3053 (2014).

- <sup>24</sup>S. H. Shin, M. A. Wahab, M. Masuduzzaman, K. Maize, J. J. Gu, M. Si, A. Shakouri, P. D. Ye, and M. A. Alam, IEEE Trans. Electron Devices 62, 3516 (2015).

- <sup>25</sup>M. Farzaneh, K. Maize, D. Lüerßen, J. A. Summers, P. M. Mayer, P. E. Raad, K. P. Pipe, A. Shakouri, R. J. Ram, and J. A. Hudgings, J. Phys. D: Appl. Phys. 42, 143001 (2009).

- <sup>26</sup>H. Zhou, Y. Du, and P. D. Ye, Appl. Phys. Lett. **108**, 202102 (2016).

- <sup>27</sup>N. A. Moser, A. Crespo, S. E. Tetlak, A. J. Green, K. D. Chabak, and G. H. Jessen, in *74th IEEE Device Research Conference* (Technical Digest, 2016), p. 95.

- <sup>28</sup>M. H. Wong, Y. Morikawa, K. Sasaki, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, Appl. Phys. Lett. 109, 193503 (2016).