# First Demonstration of BEOL Wafer-Scale All-ALD Channel CFETs Using IGZO and Te for Monolithic 3D Integration

Chang Niu<sup>1,†</sup>, Pukun Tan<sup>1,†</sup>, Jian-Yu Lin<sup>1</sup>, Linjia Long<sup>1</sup>, Zehao Lin<sup>1</sup>, Yizhi Zhang<sup>2</sup>, Haiyan Wang<sup>2</sup>, Glen D. Wilk<sup>3</sup> and Peide D. Ye<sup>1,\*</sup>

<sup>1</sup>Elmore Family School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN, USA, <sup>2</sup>School of Materials Engineering, Purdue University, West Lafayette, IN, USA <sup>3</sup>ASM, Phoenix, AZ, USA

<sup>†</sup>equal contribution, \*Email: <u>yep@purdue.edu</u>

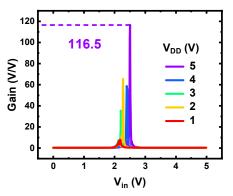

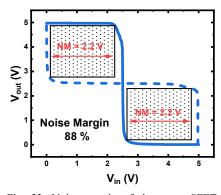

Abstract- In this work, we demonstrated for the first time Back-End-Of-Line (BEOL) compatible complementary fieldeffect transistors (CFETs) with wafer-scale all atomic-layerdeposited (ALD) channels for monolithic 3D integration. A ptype transistor based on Tellurium (Te)/Tellurium oxide (TeO<sub>x</sub>) heterostructure was fabricated on top of an InGaZnO (IGZO) n-type transistor using a common gate structure. An excellent IGZO device performance was achieved with an oncurrent (Ion) of 1 mA/µm at Vds=1 V in an enhancement-mode operation with a channel thickness (T<sub>ch</sub>) of 2 nm. The uniform wafer-scale growth of p-type semiconductor Te was achieved by introducing methanol in ALD process. Transistor arrays were measured on a four-inch wafer, demonstrating good uniformity and yield based on statistical electrical characterization. The ALD CFET-inverters were fabricated and confirmed by cross-sectional scanning transmission electron microscopy (STEM). They exhibit good electrical performance with a high gain of 116.5 V/V and a large noise margin of 2.2V (88%) at  $V_{DD} = 5$  V. The thermal budget of the entire ALD-CFET fabrication process is 225 °C and BEOL compatible.

## I. INTRODUCTION

In the rapidly evolving landscape of semiconductor technology, achieving higher performance while maintaining compatibility with existing manufacturing processes is paramount. BEOL-compatible CMOS technology for monolithic 3D integration emerges as a compelling solution for advancing chips with higher transistor densities, reduced power consumption, enhanced functionality, scalability, and cost efficiency. Recently, ALD InO<sub>x</sub>-based oxide semiconductors (including Zn and Ga doping) [1] has garnered significant interest due to its ultrathin channel thickness, superior electrical performance [2], ultra-low contact resistance [3], and robust bias stabilities [4]. The wafer-scale conformal growth achievable through ALD at low processing temperatures positions ALD channel materials well as the promising candidates for BEOL monolithic 3D integrations.

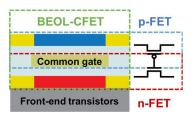

CFETs (Fig. 1), integrated vertically to minimize the footprint of CMOS transistors along with BEOL compatibility, offer an alternative path for scaling semiconductor devices. Traditionally, the scalability of BEOL-compatible p-type semiconducting channel materials with wafer-scale production has been limited. This paper explores the use of ALD  $TeO_x/Te$  heterostructure [5, 6] as a novel p-type semiconductor channel, paired with ALD IGZO as a n-type semiconductor channel, to construct CFETs with wafer-scale BEOL compatibility.

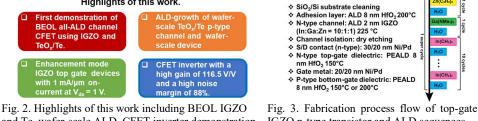

We highlight this work as the first demonstration of BEOLcompatible CFETs with all ALD semiconducting channels (Fig. 2). We developed a stacking process of vertically integrated p-type Te channels on top of IGZO transistors paving the way for future monolithic 3D integration. The 2nm-thick IGZO n-type transistors, post-stacking, exhibit excellent performance, with an on-current of 1 mA/µm at Vds = 1 V and enhancement-mode operation. Using ALD  $TeO_x/Te$ heterostructure, p-type transistor arrays were fabricated and measured on a four-inch wafer, with statistical analysis of 300 devices demonstrating the uniformity of the ALD Te film. Furthermore, ALD-CFET inverters were fabricated and verified by cross-sectional STEM, featuring verticallyintegrated channel-dielectric-metal-dielectric-channel stacks. These inverters show outstanding performance, with a gain of 116.5 V/V and a noise margin of 2.2V (88%) at  $V_{DD} = 5$  V. Our work presents a new approach for BEOL CMOS development with CFET structure and novel channel materials.

#### II. EXPERIMENTS

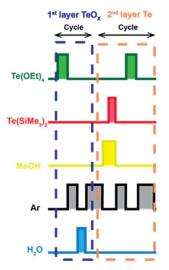

The ALD-CFET fabrication starts with top-gate IGZO ntype devices (Fig. 3). An 8-nm-thick ALD HfO<sub>2</sub> adhesion layer was deposited using [(CH<sub>3</sub>)<sub>2</sub>N]Hf (TDMAHf) and H<sub>2</sub>O at 200 °C after the solvent cleaning of 90 nm SiO<sub>2</sub>/Si substrate. The 2 nm IGZO (10:1:1) was deposited by ALD at 225 °C using In(CH<sub>3</sub>)<sub>3</sub>, (C<sub>2</sub>H<sub>5</sub>)<sub>2</sub>Zn, and Ga<sub>2</sub>(NMe<sub>2</sub>)<sub>6</sub> as precursors. The thickness of the IGZO layer is controlled by depositing 7 supercycles which contains the sequential deposition of ZnO, Ga<sub>2</sub>O<sub>3</sub>, and 10 cycles of In<sub>2</sub>O<sub>3</sub>. 30 nm/20 nm Ni/Pd was deposited by e-beam evaporation as source/drain contact metals after channel isolation by dry etching. An 8-nm-thick HfO<sub>2</sub> top-gate dielectric for IGZO channel was deposited by plasmaenhanced ALD (PEALD) at 150 °C, followed by the deposition of 20 nm/20 nm Ni/Pd as the common gate metal, which also serves as the gate for top-layer p-type transistors. An 8-nmthick HfO<sub>2</sub> bottom-gate dielectric for Te channel was then deposited using PEALD at 150 or 200 °C. ALD TeO<sub>x</sub>/Te film was newly developed as a novel BEOL p-channel material so that it was investigated on different substrates: previously fabricated IGZO n-type transistors for CFETs, SiO<sub>2</sub> fin structures, and four-inch 90 nm SiO<sub>2</sub>/Si wafer. ALD TeO<sub>x</sub> was grown using Te(OEt)<sub>4</sub> and H<sub>2</sub>O. ALD Te was grown using Te(SiMe<sub>3</sub>)<sub>2</sub> (BTMS-Te), Te(OEt)<sub>4</sub>, and MeOH. The growth temperature is optimized at 80 °C. Optional via opening was performed using dry etching. 40 nm Ni was deposited as source/drain metal contacts followed by the channel isolation using dry etching.

Scanning electron microscope (SEM), high-angle annular dark-field scanning transmission electron microscopy (HAADF-STEM), and energy dispersive x-ray spectroscopy (EDS) elemental mappings were used to characterize and confirm the CFET stack structure and material composition. The low temperature characterization was performed in a Lakeshore CRX-VF cryogenic probe station. The electrical characterization of transistors and inverters was measured with the Keysight B1500 system in a Cascade probe station.

## **III. RESULTS AND DISCUSSION**

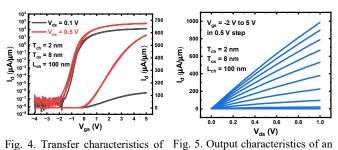

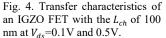

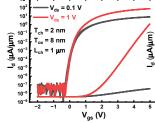

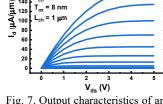

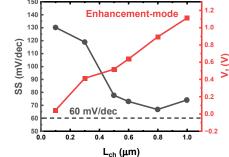

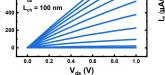

The top-gate n-type IGZO transistors were characterized after the deposition of dielectrics for p-channel. Figs. 4 and 5 present the typical transfer and output characteristics of an enhancement-mode short-channel IGZO FET with a channel length (L<sub>ch</sub>) of 100 nm, showing a threshold voltage (V<sub>t</sub>) of 0.04 V determined by linear extrapolation method. At  $V_{ds} = 1$ V, it achieves a high on-current ( $I_{on}$ ) of 1 mA/µm and an  $I_{on}/I_{off}$ ratio of  $10^{10}$ . Figs. 6 and 7 show the transfer and output characteristics of a long-channel device with L<sub>ch</sub> of 1 µm, demonstrating good current saturation at high V<sub>ds</sub>. The IGZO film thickness is 2 nm and the dielectric thickness of HfO<sub>2</sub> is 8 nm. Fig. 8 illustrates transfer curves of various channel lengths, with threshold voltage and subthreshold swing extracted and summarized in Fig. 9. At longer channel (0.5 to 1 µm) devices, the SS approaches 60 mV/dec, indicating a clean oxide (semiconductor) - oxide (dielectric) interface. The threshold voltage shifts positively with increasing channel length. Postprocessing temperatures (150 or 200 °C during deposition of the 8-nm-thick dielectric for p-channel) slightly affect the properties of the underlying n-type IGZO layer, with higher temperatures resulting in a lower threshold voltage for IGZO devices. After the process optimization, the p-channel fabrication has minor effect on n-channel devices in general.

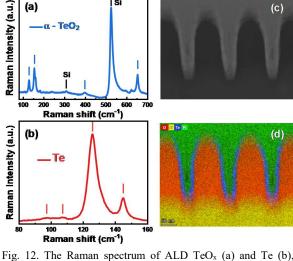

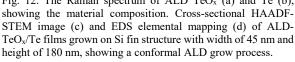

Fig. 10 illustrates the fabrication process flow for TeO<sub>x</sub>/Te p-type transistors. This heterostructure can be grown on various substrates, including IGZO n-type transistors. Detailed ALD sequences are shown in Fig. 11. The TeO<sub>x</sub> layer acts as a connection between HfO<sub>2</sub> dielectric and the semiconducting facilitating conformal wafer-scale growth. Te, The introduction of MeOH provides precursor coverage by in-situ formation of TeH<sub>2</sub>. Fig. 12 (a, b) shows the Raman spectrum of  $TeO_x$  and Te, respectively, revealing their material composition. Fig. 12 (c, d) shows the cross-sectional STEM image and EDS elemental mapping of TeO<sub>x</sub>/Te grown on 3D SiO<sub>2</sub> fin structures fabricated by SEMATECH with a fin height of 180 nm and fin pitch of 130 nm. EDS elemental mapping confirms the conformal Te coating on the fin structure, highlighting the conformality and uniformity of the ALD process.

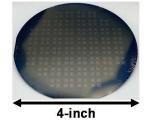

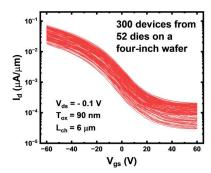

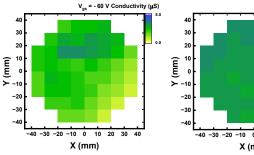

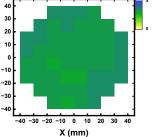

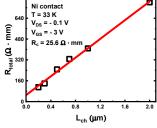

Fig. 13 shows the photograph of transistor arrays fabricated on a four-inch wafer with 14-nm-thick ALD TeO<sub>x</sub>/Te heterostructure. The transfer curves of 300 devices with the channel length of 6  $\mu$ m from transistor arrays of 52 dies on a four-inch wafer are presented in Fig. 14, indicating the consistent electrical performance across the whole wafer. Fig. 15 and 16 present the spatial color map of the transistor conductivity at V<sub>gs</sub> = -60 V and the I<sub>on</sub>/I<sub>off</sub> ratio, respectively. The I<sub>on</sub>/I<sub>off</sub> ratio is about 10<sup>3</sup> across the wafer indicating the uniformity of the TeO<sub>x</sub>/Te film and meanwhile a 0.35 eV narrow bandgap of Te film. Fig. 17 and 18 show the length-dependent transfer characterizations and scaling properties of p-type TeO<sub>x</sub>/Te transistors fabricated on top of IGZO n-type transistors with 8-nm-thick HfO<sub>2</sub> as bottom gate at 33 K. The  $I_{on}/I_{off}$  ratio of Te transistors can be significantly increased to  $10^{6}$ - $10^{7}$  at cryogenic temperatures. The contact resistance of these Te transistors is decent, higher than that of n-type contacts.

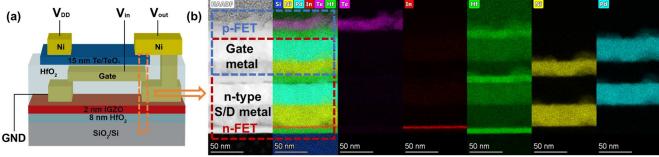

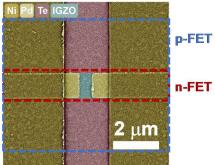

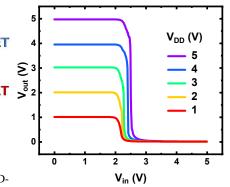

Furthermore, ALD-CFET inverters were fabricated with TeO<sub>x</sub>/Te as the top p-FET and IGZO as the bottom n-FET, as illustrated in Fig. 19(a). The cross-sectional STEM image and EDS elemental mapping of the vertical material stack at the source/drain region are shown in Fig. 19(b). The two channels are separated by a shared metal gate and two dielectric layers of 8-nm-thick HfO<sub>2</sub>, with a spacing of approximately 60 nm between p- and n-channels. Fig. 20 shows an SEM image of the top view of an ALD-CFET, with p-FET vertically stacked on top of n-FET. Fig. 21 depicts the voltage transfer characteristic (VTC) of the ALD-CFET at various V<sub>DD</sub> from 1 V to 5 V, exhibiting a full-output-swing behavior. The midpoint voltage can be tuned by adjusting the threshold voltage, which is achievable by varying the channel thickness and doping concentrations. The inverter gain is extracted at different V<sub>DD</sub> as shown in Fig. 22. A high gain of 116.5 V/V is achieved at  $V_{DD} = 5$  V. Fig. 23 shows the butterfly curve of the ALD-CFET inverter, where a high noise margin of 2.2 V (88%) at  $V_{DD} = 5$  V is extracted using the largest possible square method, demonstrating its potential for realizing SRAM. The large gain and noise margin indicates highperformance CMOS achievable by the ALD-CFETs. Table-1 benchmarks the state-of-the-art monolithic 3D CMOS inverters using oxide semiconductors and 2D materials [7-12]. Our work stands out as the first all ALD-CFET with a low process temperature of 225 °C and a high gain of 116.5 V/V.

### **IV. CONCLUSION**

In conclusion, this work demonstrates the first BEOLcompatible all ALD channel CFET with 60 nm p- and nchannels spacing using a common gate structure, highperformance enhancement-mode IGZO n-type transistors, wafer-scale growth of TeO<sub>x</sub>/Te p-type channel material, and high-performance CFET inverter (116.5 V/V gain, 2.2V (88%) noise margin). Our work provides the promise for considering novel ALD channel materials as BEOL-compatible CMOS technologies for monolithic 3D integration.

### ACKNOWLEDGMENT

The development of ALD IGZO channel is supported by SRC and Samsung Electronics. The development of ALD Te process is supported by ASM.

## REFERENCES

[1] M. Si, et al., Nano Lett., 21, 500, 2021. [2] Z. Lin, et al., ACS Nano, vol. 16, p. 21536, 2022. [3] C. Niu, et al., IEDM, 37-2, 2023. [4] Z. Zhang, et al., VLSI, T11-3, 2023. [5] C. Kim, et al., ACS Nano, 17, 16, 15776, 2023. [6] P. Tan, et al., Nano Lett., under review. [7] T. Kim, et al., npj 2D Materials and Applications, 6.1, 2022. [8] A. Liu, et al., Nature, 629, 798, 2024. [9] M. Kim, et al., IEEE Silicon Nanoelectronics Workshop, 2024. [10] S.-W. Chang, et al., IEEE TED, 69, 4, 2101, 2022. [11] Y. Li, et al., IEEE EDL, 39, 2, 208, 2017. [12] X. Xiong, et al., IEDM, 20-6, 2022.

Fig. 1. Device schematic of a BEOL-CFET using a common gate structure.

Fig. 8. Channel length-dependent transfer characteristics of IGZO FETs with 1010 Ion/Ioff ratio.

20

180

160

140

120

50

40

30

20

and Te, wafer-scale ALD, CFET inverter demonstration. IGZO n-type transistor and ALD sequences.

$V_{gs} = 0 V \text{ to } 5 V$

in 0.5 V step

= 8 nm

T<sub>ch</sub> = 2 nm

TeO,/Te p-ty

CFET inverter with

and a high noise

irgin of

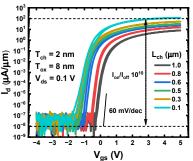

Fig. 6. Transfer characteristics of Fig. 7. Output characteristics of an at  $V_{ds}$ =0.1V and 1V.

ゞ

an IGZO FET with the  $L_{ch}$  of 1 µm IGZO FET with the  $L_{ch}$  of 1 µm, showing good current saturation.

- \* 90 nm SiO<sub>2</sub>/Si substrate or 8 nm HfO<sub>2</sub> on top of IGZO n-type devices

- ♦ P-type channel: ALD 15 nm TeO<sub>4</sub>/Te 80 °C

- \* Via formation (optional)

- \* S/D contact (p-type): 40 nm Ni

- \* Channel isolation: dry etching

Fig. 10. Fabrication process flow of bottom-gate TeOx/Te p-type transistor on pre-defined

structures or substrates.

Fig. 13. Photograph of ALD-TeO<sub>x</sub>/Te FET arrays fabricated on a four-inch Si/SiO2 wafer.

Fig. 11. ALD growth sequences of TeOx and Te. The growth temperature is optimized at 80 °C.

Fig. 14. Statistical electrical performance of 300 14-nm-thick ALD-TeO<sub>x</sub>/Te FETs with  $L_{ch} = 6 \ \mu m$ . The gate dielectric is 90 nm SiO<sub>2</sub>.

Highlights of this work.

Fig. 9. Channel length-dependent subthreshold swing SS and threshold voltage Vt on the devices in Fig. 8.

IGZO FET with the  $L_{ch}$  of 100 nm, showing  $I_{on} = 1 \text{ mA}/\mu\text{m}$  at  $V_{ds} = 1 \text{ V}$ . 150

BEOL all-ALD channe

CFET using IGZO and

TeO /Te

IGZO top g

V<sub>as</sub> = -2 V to 5 V

in 0.5 V step

= 2 nm

. = 8 nm

60

four-inch wafer.

log(I<sub>on</sub>/I<sub>off</sub>)

Fig. 15. Spatial mapping of Fig. 16. Spatial mapping of  $I_{on}/I_{off}$  different channel length ALD-conductivity at  $V_{gs}$  =-60V of 300 ratio of 300 devices with the  $L_{ch}$  of TeO<sub>x</sub>/Te FETs measured at 33 K. devices with the  $L_{ch}$  of 6 µm on a 6 µm on a four-inch wafer, showing The gate dielectric is 8 nm HfO<sub>2</sub>. uniform ALD growth.

Fig. 18. Total resistance as a function of channel length at 33 K showing the scaling of Te p-type transistors.

Fig. 19. (a) Structure schematic of an ALD-IGZO/Te CFET inverter. (b) Cross-sectional HAADF-STEM image and EDS elemental mapping of the ALD-IGZO/Te CFET structure at the S/D metal area showing the material stack. 2-nm-thick IGZO and 15-nm-thick TeO<sub>x</sub>/Te are used as n-type and p-type channel material, respectively. The space between p and n channel separated by the gate metal layer and two dielectric layers is about 60 nm.

Fig. 20. Top view SEM image of ALD-IGZO/Te CFET, showing p-FET stacked on n-FET with shared metal gate.

Fig. 21. Voltage transfer characteristics of a typical CFET inverter with different VDD. ntype:  $L_{ch}=0.5\mu m$ ,  $W_{ch}=1\mu m$ , p-type:  $L_{ch}=5\mu m$ ,  $W_{ch}=10\mu m.$

Fig. 22. The voltage gains at various  $V_{DD}$ extracted from Fig. 21. A high voltage gain of 116.5 V/V is demonstrated at V<sub>DD</sub>=5V.

Fig. 23. Noise margin of the same CFET invertor as in Fig. 21. A large noise margin of 2.2V (88%) is achieved.

Table 1. Comparisons of state-of-the-art monolithic 3D CMOS inverters using oxide semiconductors and 2D materials as channels.

| Semiconductors and 2D materials as chamilets. |                      |            |                                |          |            |            |                  |

|-----------------------------------------------|----------------------|------------|--------------------------------|----------|------------|------------|------------------|

|                                               | This work            | [7]        | [8]                            | [9]      | [10]       | [11]       | [12]             |

| n-FET                                         | IGZO                 | IGZO       | In <sub>2</sub> O <sub>3</sub> | ZnO      | IGZO       | IGZO       | MoS <sub>2</sub> |

| p-FET                                         | TeO <sub>x</sub> /Te | Те         | SeTe-TeO <sub>x</sub>          | Te       | Poly-Si    | SnO        | WSe <sub>2</sub> |

| Structure                                     | CFET                 | Planar     | Planar                         | Planar   | CFET       | Planar     | CFET             |

| Gain (V/V) (V <sub>DD</sub> )                 | 116 (5 V)            | 75.2 (3 V) | 1300 (20 V)                    | 46 (3 V) | 18 (1.4 V) | 112 (10 V) | 18 (3 V)         |

| Process<br>temperature (°C)                   | < 225                | < 400      | < 250                          | < 200    | < 700      | < 225      | < 200            |

| N-channel<br>process                          | ALD                  | Sputter    | Inkjet-<br>printing            | ALD      | Sputter    | Sputter    | CVD              |

| P-channel<br>process                          | ALD                  | Sputter    | Thermal evaporation            | ALD      | PECVD      | Sputter    | CVD              |