# TOWARDS HIGH-SPEED NETWORKING IN THE POST-MOORE ERA

#### A Dissertation

Presented to the Faculty of the Graduate School of Cornell University

in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

> by Vishal Shrivastav August 2020

© 2020 Vishal Shrivastav

ALL RIGHTS RESERVED

## TOWARDS HIGH-SPEED NETWORKING IN THE POST-MOORE ERA

Vishal Shrivastav, Ph.D.

#### Cornell University 2020

The motivation behind this dissertation stems from two polarizing trends inside modern datacenters—on the one hand, the bandwidth demand and link speed within datacenters keep increasing rapidly as applications keep getting more distributed, and resources (e.g., storage) keep getting disaggregated; but on the other hand, the processing and switching speeds of the underlying networking infrastructure, comprising primarily of general-purpose CPUs and packet switches, is scaling much more slowly due to the slowdown in Moore's law and the end of Dennard scaling. Thus, at the end-hosts, it is becoming increasingly difficult to saturate the high-speed links using CPU-based network stack, and in the network core, it is becoming increasingly difficult to build high-speed switching fabric in a cost and power effective manner using packet switches. To that end, this dissertation looks beyond the general-purpose CPUs and the packet switches as the building blocks for datacenter networks, and instead presents two promising alternatives that demonstrate that it is possible to build high-performance, high-speed end-host network stacks and switching fabrics at low cost and power, even as Moore's law continues to slow down.

First, with regards to the end-host network stack, this dissertation demonstrates the need to complement general-purpose CPUs with domain-specific processors for network processing, to keep up with increasing link speeds. However, one of the key challenges with designing a domain-specific processor is providing the right balance between programmability and performance.

Using packet scheduling as the target network processing application, our main contribution here is a new packet scheduling primitive, called Push-In-Extract-Out (PIEO), and the corresponding hardware architecture implementing the primitive, that together form an idealistic packet scheduler which is *simultaneously* programmable, scalable, and high-speed—PIEO primitive is more expressive (programmable) than any state-of-the-art packet scheduling primitive, and PIEO's hardware architecture could easily scale to 10s of thousands of flows (>30× more scalable than state-of-the-art) while making scheduling decisions in O(1) time (up to 300× faster than a single CPU core).

Second, with regards to the switching fabric, this dissertation demonstrates that by using fast circuit switches (that could reconfigure within nanoseconds) as building blocks, one could build extremely high-speed and highperformance switching fabrics in a cost and power effective manner. The key challenge here is designing a high-speed control plane for the circuit-switched network that could complement the fine-grained reconfiguration technology by being able to schedule the right set of circuits every few nanoseconds. In that regard, our main contribution here is a new control plane architecture for circuit switching which is a stark departure from the traditional (slow) centralized controller-based architectures, and is in fact a fully de-centralized and traffic agnostic design that could schedule high-performing circuit configurations at nanosecond granularity. Further, our design is agnostic to the underlying circuit switching technology, and can operate with electrical, optical, or wireless technologies alike. We demonstrate that the resulting circuit-switched network, called Shoal, can effectively scale to high switching speeds while achieving comparable or better throughput and latency than several state-of-the-art packetswitched network designs at significantly lower power and cost.

Overall, through PIEO and Shoal, this dissertation demonstrates that by effectively leveraging the promise of domain-specific processing and fast circuit switching, one can indeed build efficient high-speed end-host network stacks and switching fabrics even in light of continued slowdown in Moore's law and the end of Dennard scaling.

## **BIOGRAPHICAL SKETCH**

Vishal Shrivastav is a Ph.D. candidate in the department of Computer Science at Cornell University, advised by Hakim Weatherspoon. He holds a Master of Science in Computer Science from Cornell University and a Bachelor of Technology in Computer Science and Engineering from the Indian Institute of Technology, Kharagpur.

Dedicated to my grandmother, the late Renuka Sahay, for being the kindest, most loving soul that ever lived.

#### **ACKNOWLEDGEMENTS**

First, I would like to express my deepest gratitude to my advisor, Hakim Weatherspoon. It is very true that your Ph.D. advisor has the greatest influence on how your graduate study experience would turn out, and so it is no coincidence that I had such am amazing experience as a graduate student with Hakim as my advisor. I am so thankful for all his support and guidance over the years, and for all the independence he gave me with my research. In fact, there is an endless list of things that I could thank Hakim for, so instead I am just going to say this to him – Thank you for everything!

Next, I would like to thank my amazing research collaborators, starting with Rachit Agarwal. I worked with Rachit through most of my graduate studies, and learned a lot from him during that time, especially about how to critique research ideas and how to effectively present and defend my own ideas. I cannot thank him enough for his mentorship. Next, I would also like to express my sincerest gratitude to Hitesh Ballani and Paolo Costa. I worked closely with Hitesh and Paolo for almost two years during the early days of my graduate studies. During this time, they helped me navigate the existing landscape of computer networking research, which really helped kick-start my research career. Finally, I would like to thank the entire computer science faculty at Cornell, for always being so kind to me and for being such great sources of inspiration. In particular, I would like to thank Nate Foster (for securing the NetLab for us, and for providing us with an endless supply of nuts that fed us through the many all-nighters during paper deadlines), Christina Delimitrou (for accepting to be on my thesis committee even after I had already passed my A-Exam), Robbert van Renesse (for always encouraging me since my very first year at Cornell when I worked under him as a T.A.), and Lorenzo Alvisi and Bobby Kleinberg

(for always being so supportive and approachable). As I begin my own journey as a Professor in the next few months, I am so glad to have such great role models to look up to. I would also like to take this opportunity to thank the amazing staff at Cornell, especially Becky Stewart, for helping me out with so many administrative issues over the years.

Next, I would like to thank my peers at Cornell for making the entire graduate study experience so enjoyable. During my first two years of graduate school, senior graduate students Han Wang and Ki Suh Lee took me under their wing and guided me through everything, from research to life as a graduate student in general. I cannot thank them enough for all their support and guidance in those early years. I will always cherish my friendship with Praveen Kumar, Saksham Agarwal, Qizhe Cai, and Hardik Soni, for all the great times we shared, both inside and outside of Cornell. And more generally, I would like to thank all the amazing graduate students, too many to name, that I came to know during my time at Cornell. I can only hope that the friendships and connections I forged at Cornell would last a lifetime.

During the summer of 2017 and 2018, I got the opportunity to intern with Microsoft Azure's Host Networking team in Redmond. It turned out to be a great learning experience for me, and also inspired some of the work presented in this dissertation. I would like to thank Microsoft for giving me this opportunity, especially Daniel Firestone, Andrew Putnam, Jitu Padhye, Yibo Zhu, Larry Luo, Norman Lam, and Gautham Popuri.

I would also like to take this opportunity to acknowledge some of the people from my undergraduate years who got me interested in graduate studies in the first place. Back in 2013, I got an opportunity to spend a few months as an undergraduate researcher at University of Toronto, working with Eyal de

Lara. I will always remember this trip as the first time I ever flew in an airplane, but more than that, I also had an amazing time working with all the graduate students in Eyal's group, especially Nilton Bila, Utkarsh Roychoudhury, Akshay Kumar, and Sahil Suneja. Looking back, those few months in Toronto had a big influence over my decision to go for graduate studies. But perhaps I owe the biggest gratitude to my undergraduate research advisor, Partha Pratim Chakrabarti (or PPC, as known to IIT Kgpians). I did undergraduate research under PPC for almost two years, and I would like to thank him for his amazing mentorship and his constant encouragement that finally convinced me to apply for graduate studies.

Finally, I would like to thank (by far) the most important people in my life, my parents and my two sisters, as well as my entire extended family of uncles, aunts, and cousins, for always being there for me and proudly supporting me through all my endeavors. Every little success that I have had so far, and every success that I might enjoy in the future, I owe it all to them. They are my rock and I am so blessed to call them my family.

Overall, graduate school has truly been an experience of a lifetime. And it is all because of the people mentioned above.

## TABLE OF CONTENTS

|   | Biog | graphical Sketch                                           | iii |

|---|------|------------------------------------------------------------|-----|

|   | Ded  | lication                                                   | iv  |

|   | Ack  | knowledgements                                             | v   |

|   |      |                                                            | iii |

|   | List | of Figures                                                 | xi  |

|   |      |                                                            | iv  |

| 1 | Intr | roduction                                                  | 1   |

|   | 1.1  | Background                                                 | 1   |

|   |      | 1.1.1 Modern Datacenter Networks                           | 1   |

|   |      | 1.1.2 Trends in Transistor Scaling                         | 6   |

|   | 1.2  | Motivation                                                 | 7   |

|   | 1.3  | Limitations of Existing Approaches                         | 9   |

|   |      | 1.3.1 General-purpose Processor-based Network Stacks       | 9   |

|   |      |                                                            | 11  |

|   | 1.4  |                                                            | 14  |

|   | 1.5  |                                                            | 16  |

|   |      |                                                            | 16  |

|   |      | <u>.</u>                                                   | 19  |

|   |      |                                                            | 22  |

|   | 1.6  | U 1                                                        | 23  |

|   |      | 1.6.1 Fast Domain-specific Processor for Packet Scheduling | 23  |

|   |      |                                                            | 24  |

|   | 1.7  | <u> </u>                                                   | 26  |

|   | 1.8  |                                                            | 29  |

|   | 1.9  | •                                                          | 29  |

| 2 | Fast | t Domain-specific Processor for Packet Scheduling : PIEO   | 30  |

|   | 2.1  | Overview                                                   | 30  |

|   | 2.2  |                                                            | 34  |

|   |      | 2.2.1 Packet Scheduling Model                              | 35  |

|   |      |                                                            | 36  |

|   |      |                                                            | 37  |

|   | 2.3  | <u> </u>                                                   | 41  |

|   |      | $\epsilon$                                                 | 41  |

|   |      |                                                            | 43  |

|   | 2.4  |                                                            | 47  |

|   |      |                                                            | 47  |

|   |      |                                                            | 49  |

|   |      |                                                            | 51  |

|   |      |                                                            | 53  |

|   |      |                                                            | 54  |

|   | 2.5 | Hardy | ware Architecture                                       | . 55  |

|---|-----|-------|---------------------------------------------------------|-------|

|   |     | 2.5.1 | Hardware Model                                          | . 55  |

|   |     | 2.5.2 | Architecture and Key Complexity Results                 | . 55  |

|   |     | 2.5.3 | Implementation                                          |       |

|   | 2.6 | Evalu | ation                                                   | . 64  |

|   |     | 2.6.1 | Prototype                                               | . 64  |

|   |     | 2.6.2 | Prototype Experiments: Scheduling Rate                  | . 65  |

|   |     | 2.6.3 | Prototype Experiments: Scalability                      |       |

|   |     | 2.6.4 | Prototype Experiments: Programmability                  |       |

|   | 2.7 | Discu | ssion                                                   |       |

|   |     | 2.7.1 | PIEO as a Generic Priority Queue                        | . 70  |

|   |     | 2.7.2 | · · · · · · · · · · · · · · · · · · ·                   |       |

|   | 2.8 | Sumn  | nary                                                    |       |

|   | _   |       |                                                         |       |

| 3 |     |       | it-switched Switching Fabric : Shoal                    | 72    |

|   | 3.1 |       | view                                                    |       |

|   | 3.2 | _     | ground                                                  |       |

|   |     | 3.2.1 | Strawman Design 1: Packet Switching                     |       |

|   |     | 3.2.2 | Strawman Design 2: Direct-connect Network               |       |

|   | 2.2 | 3.2.3 | Circuit Switching                                       |       |

|   | 3.3 | _     | n                                                       |       |

|   |     | 3.3.1 | Design Overview                                         |       |

|   |     | 3.3.2 | Shoal Switching Fabric                                  |       |

|   |     | 3.3.3 | Shoal Data Plane                                        |       |

|   |     | 3.3.4 | Shoal Control Plane: Static Schedule & Virtual Topology |       |

|   |     | 3.3.5 | Shoal Control Plane: Routing                            |       |

|   |     | 3.3.6 | Shoal Control Plane: Congestion Control                 |       |

|   | 2.4 | 3.3.7 | Shoal Control Plane: Configuration Parameters           |       |

|   | 3.4 |       | ling Practical Concerns                                 |       |

|   |     | 3.4.1 | Clock and Data Recovery (CDR)                           |       |

|   |     | 3.4.2 | Accounting for Propagation Delay                        |       |

|   |     | 3.4.3 | Cell Re-ordering and Re-assembly                        |       |

|   | 2.5 | 3.4.4 | Failures                                                |       |

|   | 3.5 |       | ware Implementation                                     |       |

|   |     | 3.5.1 | Switch Implementation                                   |       |

|   | 2.6 | 3.5.2 | Network Interface Card (NIC) Implementation             |       |

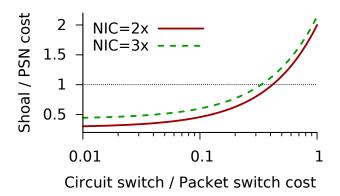

|   | 3.6 |       | r and Cost Implications                                 |       |

|   | 3.7 |       | ation                                                   |       |

|   |     | 3.7.1 | Prototype                                               |       |

|   |     | 3.7.2 | Prototype Experiments: Throughput and Latency           |       |

|   |     | 3.7.3 | Simulation                                              |       |

|   |     | 3.7.4 | Simulation Experiments: Microbenchmarks                 |       |

|   |     | 3.7.5 | Simulation Experiments: Datacenter Workloads            |       |

|   |     | 3.7.6 | Simulation Experiments: Disaggregated Workloads         | . 116 |

|    | 3.8             | Discussion                                                    | 118 |

|----|-----------------|---------------------------------------------------------------|-----|

|    |                 | 3.8.1 Running Applications on top of Shoal                    | 118 |

|    |                 | 3.8.2 Quality-of-Service on top of Shoal                      | 118 |

|    | 3.9             | Summary                                                       | 119 |

| 4  | Rela            | ted Work                                                      | 120 |

|    | 4.1             | High-speed End-host Network Stacks                            | 120 |

|    | 4.2             | High-speed Programmable Network Data Plane                    | 121 |

|    | 4.3             | Switching Fabric Topologies and Technologies                  | 122 |

|    | 4.4             | Congestion Control via Tight Host-Fabric Coupling             | 124 |

| 5  | Futu            | re Work                                                       | 126 |

|    | 5.1             | High-speed Programmable Architectures for Middleboxes         | 126 |

|    | 5.2             | Low Latency Optical Circuit Switching                         | 128 |

| 6  | Con             | clusion                                                       | 130 |

| A  | Proc            | of of INVARIANT 1 and bound on the number of sublists in PIEO | 132 |

| В  | Glos            | ssary of Terms                                                | 137 |

| Ri | Bibliography 16 |                                                               |     |

## LIST OF FIGURES

| 1.1        | End-host networking infrastructure inside modern datacen-                                                                                                                                |    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|            | ters, comprising general-purpose CPU, Network Interface Card (NIC), and accelerators such as FPGA. CPU implements majority of the network stack, while NIC implements a part of the Data |    |

|            | Link Layer and the Physical Layer. For higher performance, certain network stack functionalities are offloaded to NIC and ac-                                                            |    |

|            | celerator. CPU communicates with NIC and accelerator over the                                                                                                                            |    |

|            | Peripheral Component Interconnect Express (PCIe) bus, while NIC and accelerator optionally communicate via their respective                                                              |    |

|            | network interfaces                                                                                                                                                                       | 3  |

| 1.2        | Typical specifications of networking hardware inside datacenters around the year 2020. CPU specifications are from In-                                                                   |    |

|            | tel [117], NIC specifications are from Mellanox [159], FPGA spec-                                                                                                                        |    |

|            | ifications are from Terasic Stratix DE boards [163], fixed-function                                                                                                                      |    |

|            | packet switch specifications are from Broadcom [143], and programmable packet switch specifications are from Barefoot Net-                                                               |    |

|            | works (an Intel company) [149]                                                                                                                                                           | 4  |

| 1.3        | A typical packet-switched switching fabric inside modern datacenters. The example comprises 20 packet switches forming                                                                   |    |

|            | a three-tier Fattree topology with full bisection bandwidth con-                                                                                                                         |    |

|            | necting 16 end-hosts                                                                                                                                                                     | 5  |

| 1.4<br>1.5 | Exponential rise in datacenter link speed over the last decade [32]. Scaling of CPU performance over the years. Since 2018, the per-                                                     | 7  |

| 1.5        | formance improvement is just 3.5% per year, or doubling every                                                                                                                            |    |

|            | 20 years. (Image source: Hennessy & Patterson 6e [43])                                                                                                                                   | 10 |

| 1.6        | Broadcom switching chips double in speed every two years. The most recent generation of Broadcom switching chip (Tomahawk                                                                |    |

|            | 4) runs at 25.6 Terabits/second and is built using 7 nm process                                                                                                                          |    |

| 1 7        | technology.                                                                                                                                                                              | 12 |

| 1.7        | A traditional packet switch with one switching chip per switch box versus a chassis packet switch with multiple switching chips                                                          |    |

|            | per switch box                                                                                                                                                                           | 14 |

| 1.8        | Growing gap in the scaling of link speeds versus the CPU and                                                                                                                             |    |

|            | packet switching speeds—link speed is practically doubling every year, whereas packet switch chip speed is doubling every                                                                |    |

|            | 2 years, while CPU clock speed has practically stagnated (dou-                                                                                                                           |    |

| 4.0        | bling every 20 years)                                                                                                                                                                    | 15 |

| 1.9        | A DE5-Net board with Stratix V FPGA                                                                                                                                                      | 26 |

| 1.10       | Small-scale network for evaluation comprising 8 end-host NICs and 6 switches connected in a two-tier Fattree topology with full                                                          |    |

|            | bisection bandwidth (also known as leaf-spine topology) con-                                                                                                                             |    |

|            | nected inside the PCIe expansion system                                                                                                                                                  | 28 |

| 2.1 2.2 | A generic packet scheduling model                                                                                                 | 35       |

|---------|-----------------------------------------------------------------------------------------------------------------------------------|----------|

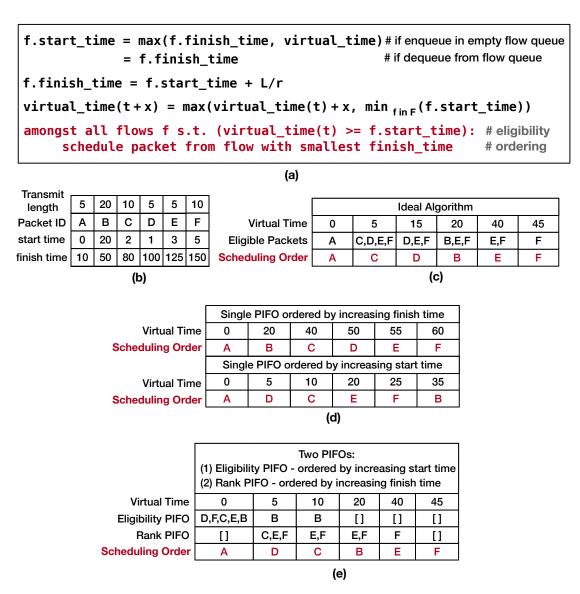

|         | Scheduling order in an ideal run of $WF^2Q+$ . (d) and (e) scheduling orders when running $WF^2Q+$ using PIFO                     | 38       |

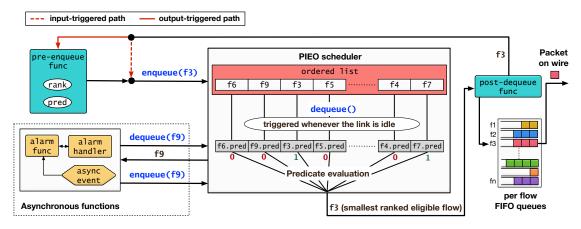

| 2.3     | PIEO programming framework.                                                                                                       | 43       |

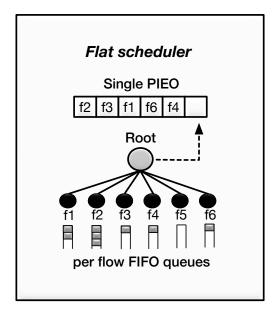

| 2.4     | Classic flat PIEO scheduler                                                                                                       | 51       |

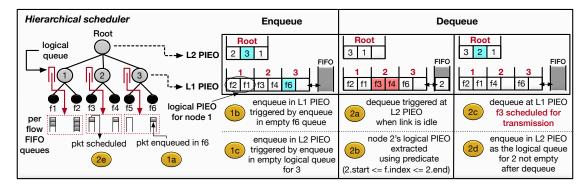

| 2.5     | Hierarchical packet scheduling in PIEO                                                                                            | 51       |

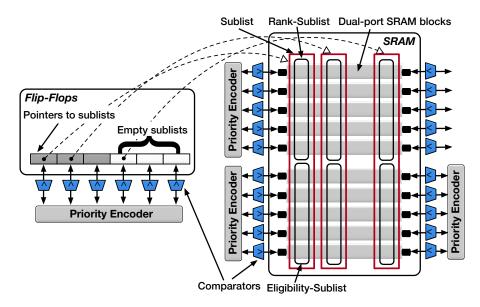

| 2.6     | PIEO scheduler hardware architecture. A priority encoder takes                                                                    |          |

|         | as input a bit vector and returns the smallest index containing 1.                                                                | 56       |

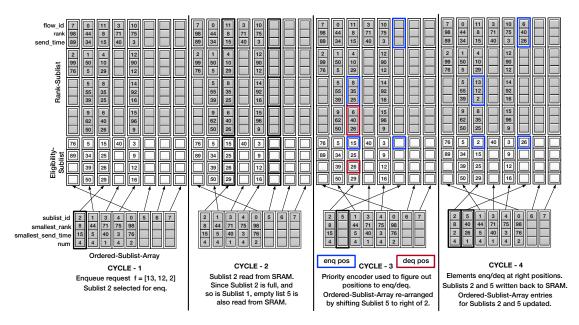

| 2.7     | An example enqueue into the PIEO ordered list of size 16 ele-                                                                     |          |

| 2.0     | ments (8 sublists each of size 4)                                                                                                 | 60       |

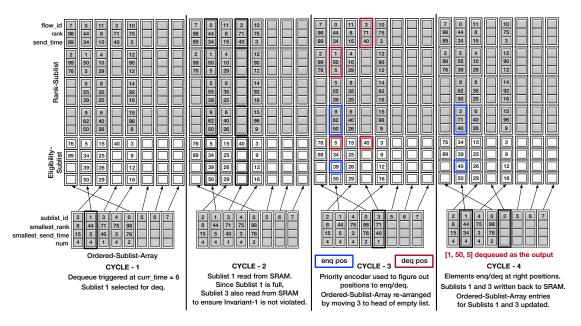

| 2.8     | An example dequeue from the PIEO ordered list of size 16 ele-                                                                     | ()       |

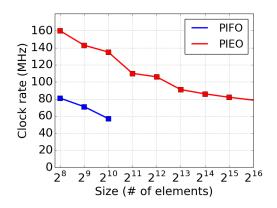

| 2.9     | ments (8 sublists each of size 4)                                                                                                 | 62<br>65 |

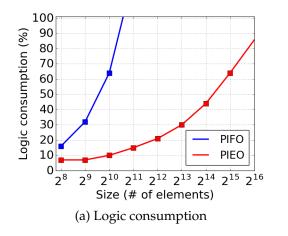

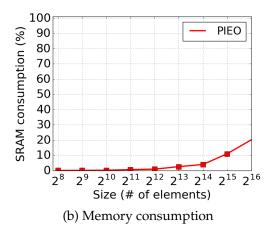

| 2.9     | Percentage of logic modules (ALMs) consumed (out of 234K)                                                                         | 00       |

| 2.10    | and Percentage of SRAM consumed (out of 6.5 MB)                                                                                   | 67       |

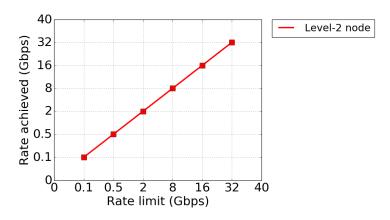

| 2.11    | Rate limit enforcement in PIEO prototype                                                                                          | 68       |

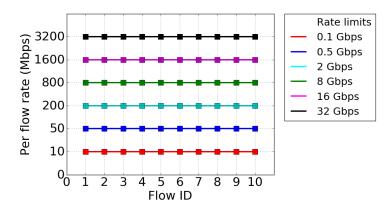

| 2.12    | Fair queue enforcement in PIEO prototype                                                                                          | 68       |

|         |                                                                                                                                   |          |

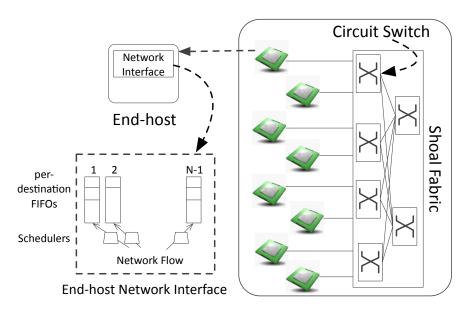

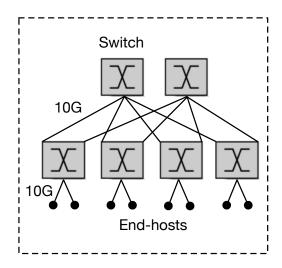

| 3.1     | Shoal architecture.                                                                                                               | 79       |

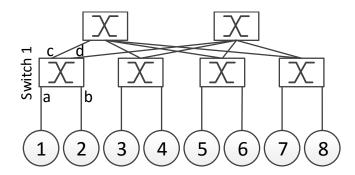

| 3.2     | A non-blocking Clos topology of circuit switches. This particular topology is also largery as two tien full bioaction has devided |          |

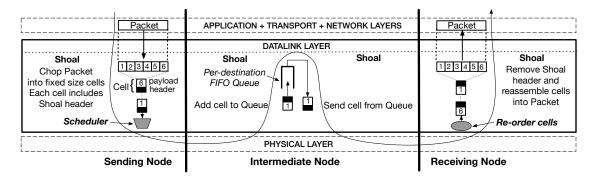

|         | lar topology is also known as two-tier full bisection bandwidth Fattree topology or a leaf-spine topology                         | 81       |

| 3.3     | Shoal data plane                                                                                                                  | 82       |

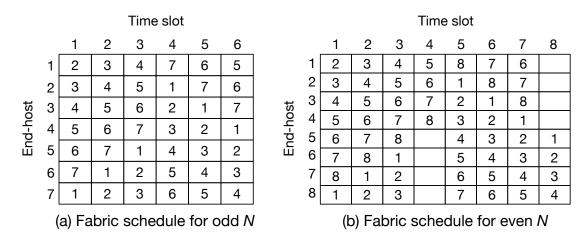

| 3.4     | Fabric schedule for a network with 8 end-hosts (see Figure 3.2                                                                    | 02       |

| 0.1     | for the physical topology).                                                                                                       | 83       |

| 3.5     | Switch 1's schedule (see Figure 3.2 for the physical topology)                                                                    | 83       |

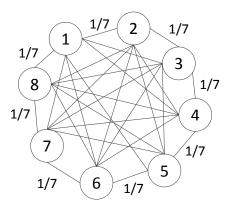

| 3.6     | Shoal's virtual full mesh topology with 8 end-hosts (see Fig-                                                                     |          |

|         | ure 3.2 for the physical topology)                                                                                                | 84       |

| 3.7     | Fabric schedule for a network with $N = 7$ end-hosts (odd $N$ ) and                                                               |          |

|         | N = 8 end-hosts (even $N$ ) after accounting for propagation delay.                                                               |          |

| 2.0     | For the original fabric schedule with 8 end-hosts refer to Figure 3.4                                                             | . 95     |

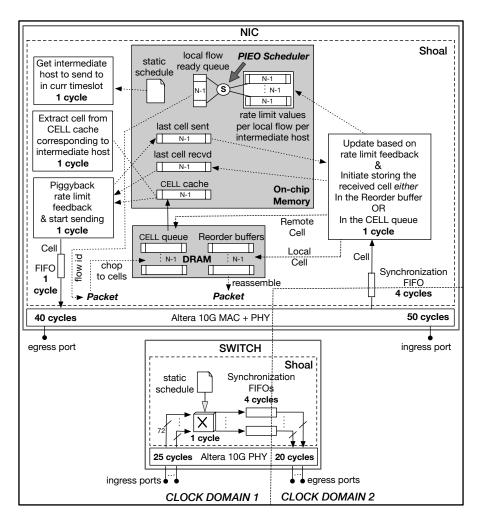

| 3.8     | Switch and NIC implementation with the latency of each block.                                                                     |          |

|         | Clock cycle is 6.4 ns. N = number of end-hosts. The NIC sched-                                                                    | 99       |

| 3.9     | uler is implemented using PIEO (Chapter 2)                                                                                        | 101      |

| 3.10    | Shoal prototype's topology                                                                                                        | 101      |

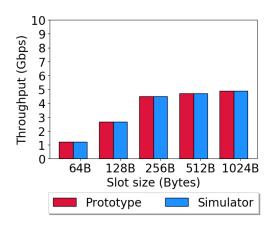

| 3.11    | [Prototype] Average destination throughput for full permutation                                                                   | 100      |

|         | matrix                                                                                                                            | 106      |

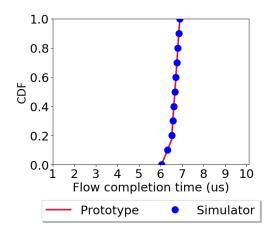

| 3.12 | [Prototype] Flow completion time for 7:1 synchronized incast    | 108 |

|------|-----------------------------------------------------------------|-----|

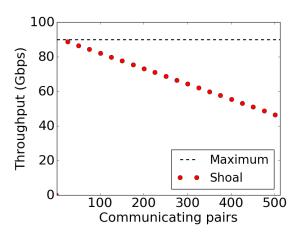

| 3.13 | Average destination throughput vs. size of permutation matrix   | 109 |

| 3.14 | Flow completion times against synchronized short flow incast    | 110 |

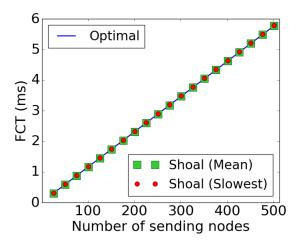

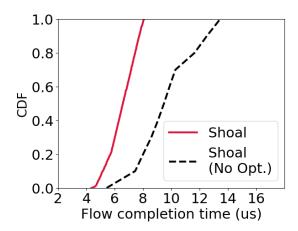

| 3.15 | Reduced impact of detouring on latency via optimizations in     |     |

|      | Section 3.3.6                                                   | 111 |

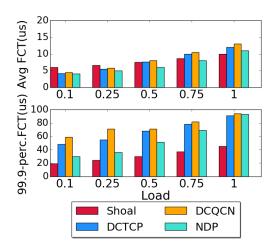

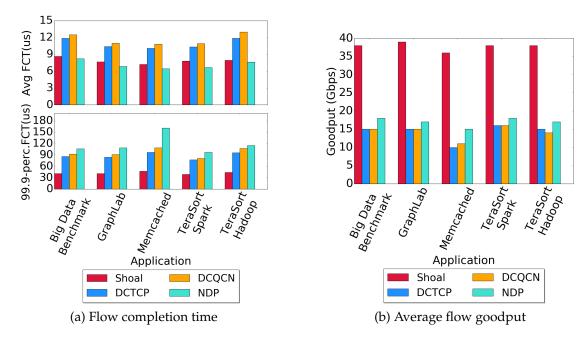

| 3.16 | Flow completion time (short flows ≤100 KB) vs. traffic load     | 114 |

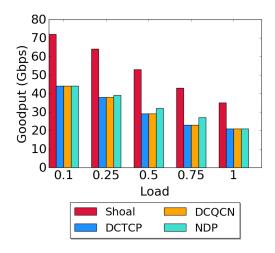

| 3.17 | Average flow goodput (long flows ≥1 MB) vs. traffic load        | 114 |

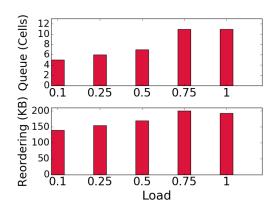

| 3.18 | Max queue size and max cell re-ordering vs. traffic load        | 115 |

| 3.19 | Short flow 99.9 percentile FCT and long flow average goodput    |     |

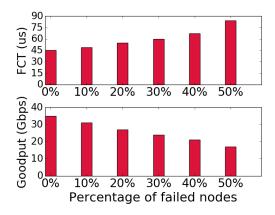

|      | vs. failures                                                    | 115 |

| 3.20 | Flow completion time (short flows ≤100 KB) and average flow     |     |

|      | goodput (long flows ≥1 MB) for different applications with dis- |     |

|      | aggregated workload                                             | 117 |

|      |                                                                 |     |

#### PREVIOUSLY PUBLISHED MATERIAL

Chapter 2 in this dissertation is adapted from a previous publication [99] –

Vishal Shrivastav. Fast, Scalable, and Programmable Packet Scheduler in Hardware. In Proceedings of the ACM Special Interest Group on Data Communication (SIGCOMM), 2019.

Chapter 3 in this dissertation is adapted from a previous publication [101] –

Vishal Shrivastav, Asaf Valadarsky, Hitesh Ballani, Paolo Costa, Ki Suh Lee, Han Wang, Rachit Agarwal, and Hakim Weatherspoon. *Shoal: A Network Architecture for Disaggregated Racks*. In Proceedings of the 16th USENIX Conference on Networked Systems Design and Implementation (NSDI), 2019.

#### CHAPTER 1

#### **INTRODUCTION**

The modern datacenter has emerged as the dominant computing platform that powers most of world's consumer online services, financial, military, and scientific application domains. Further, virtually every application and service running inside the datacenter relies on network connectivity. In this dissertation, we study the impact of slowdown in Moore's law and the end of Dennard scaling on datacenter networking, and propose new designs and architectures for high-performance, high-speed networking in the Post-Moore era.

## 1.1 Background

We begin by giving a brief overview of the modern datacenter network, followed by a discussion of the ongoing trends in transistor scaling, the underlying technology behind the existing datacenter networking infrastructure.

#### 1.1.1 Modern Datacenter Networks

Modern datacenters comprise a cluster of compute nodes or "end-hosts", that can range from an order of few thousands to a million, interconnected using a datacenter-wide network. The primary job of the datacenter network is to effectively facilitate all remote communications between the applications running at the end-hosts, which puts network on the critical path to performance, availability, and even security of applications inside datacenters.

The communication over a datacenter network typically has two components—(a) a *network stack* at the end-host that moves data from the applications onto the wire, and (b) a *switching fabric* that moves data between the end-hosts. We discuss both of them below.

End-host Network Stack. The network stack at each end-host provides the interface to the applications to communicate over the network. Typically, the entire network stack functionality is divided into smaller independent modules called layers. The Open Systems Interconnection (OSI) model introduces seven abstraction layers [133] — Physical layer (the lowest layer in the stack), Data Link Layer, Network Layer, Transport Layer, Session Layer, Presentation Layer, and Application Layer (the highest layer in the stack). Each layer serves the layer above it and is served by the layer below it.

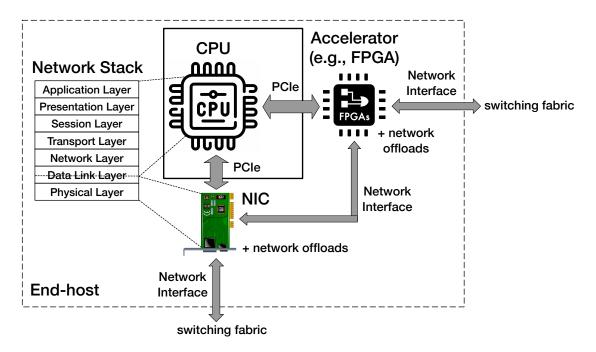

Further, end-hosts in modern datacenters are built using commodity servers. Each server is equipped with networking hardware infrastructure (Figure 1.1) that implements the end-host network stack, as described below.

General-purpose Central Processing Unit (CPU). Most of the network stack at the end-hosts (from Application Layer through most of the Data Link Layer) is typically implemented on top of general-purpose CPUs. The key advantage of such a design is the ease of programmability, that provides the datacenter operators with the flexibility to rapidly experiment, test, and deploy new network stack functionalities, or update the existing ones. Figure 1.2 shows the typical CPU specifications of commodity servers around the year 2020.

*Network Interface Card (NIC).* A Network Interface Card (NIC) is an Application-specific Integrated Circuit (ASIC), that typically implements a part

Figure 1.1: End-host networking infrastructure inside modern datacenters, comprising general-purpose CPU, Network Interface Card (NIC), and accelerators such as FPGA. CPU implements majority of the network stack, while NIC implements a part of the Data Link Layer and the Physical Layer. For higher performance, certain network stack functionalities are offloaded to NIC and accelerator. CPU communicates with NIC and accelerator over the Peripheral Component Interconnect Express (PCIe) bus, while NIC and accelerator optionally communicate via their respective network interfaces.

of the Data Link Layer and the entire Physical Layer of the network stack. In addition, modern NICs also implement a few other network stack functionalities offloaded from the CPUs for higher performance, such as Large Send Offload (LSO) [129], Receiver Side Scaling (RSS) [156], Quality-of-Service (QoS), and Remote Direct Memory Access (RDMA) [135]. While offloading functionalities to NICs result in higher performance, a key limitation of this approach is that commodity ASIC NICs at the time of writing this dissertation are mostly fixed-function, thus not allowing users to modify or program new functionalities once the NIC has been manufactured. Figure 1.2 shows the typical specifications of commodity ASIC NICs around the year 2020.

| Component              | Specifications                               |

|------------------------|----------------------------------------------|

| General-purpose CPU    | Number of cores: 4–56                        |

|                        | Clock speed: 1.8–4.5 GHz                     |

|                        | L2/L3 cache size: 8.25–77 MB                 |

|                        | Power: 165 W                                 |

| Network Interface Card | Number of ports: 1–2                         |

|                        | Per port speed: 200/100/50/40/25/10 Gbps     |

| FPGA Board             | Number of logic elements: 200–3000 K         |

|                        | Embedded SRAM size: 52–234 MBits             |

|                        | Number of ports: 1–4                         |

|                        | Per port speed: 100/50/40/25/10 Gbps         |

| Packet Switch          | Aggregate switching speed: 6.4–25.6 Tbps     |

| (fixed-function)       | Number of ports: 32–256                      |

|                        | Per port speed: 400/200/100/50/40/25/10 Gbps |

| Packet Switch          | Aggregate switching speed: 6.4–12.8 Tbps     |

| (programmable)         | Number of ports: 32–256                      |

|                        | Per port speed: 400/200/100/50/40/25/10 Gbps |

Figure 1.2: Typical specifications of networking hardware inside datacenters around the year 2020. CPU specifications are from Intel [117], NIC specifications are from Mellanox [159], FPGA specifications are from Terasic Stratix DE boards [163], fixed-function packet switch specifications are from Broadcom [143], and programmable packet switch specifications are from Barefoot Networks (an Intel company) [149].

Network Accelerator. Modern datacenters also equip end-hosts with network accelerators to offload certain network stack functionalities from the CPU for higher performance. The most prominent network accelerator used in modern datacenters are the Field-programmable Gate Arrays (FPGAs). As an example, in 2018, Microsoft datacenters introduced AccelNet [33], a system that offloaded the virtual switch (vSwitch) from the CPUs onto the FPGAs. The advantage of offloading functionalities onto an FPGA as opposed to a commodity NIC is that FPGAs are programmable, unlike fixed-function commodity NICs. Thus FPGAs give the datacenter operators more flexibility, at the cost of lower performance and power efficiency compared to commodity NICs. Figure 1.2 shows the typical specifications of FPGAs around the year 2020.

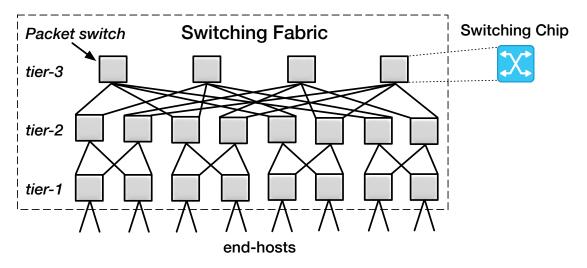

Figure 1.3: A typical packet-switched switching fabric inside modern datacenters. The example comprises 20 packet switches forming a three-tier Fattree topology with full bisection bandwidth connecting 16 end-hosts.

**Switching Fabric.** The end-hosts inside datacenters are interconnected using a datacenter-wide switching fabric. The switching fabric comprises a collection of *packet switches* connected in some network topology to provide the necessary bisection bandwidth. The most common topology inside modern datacenters is a Folded Clos topology, such as Fattree [1] (Figure 1.3).

Packet Switch. The building blocks of modern datacenter switching fabric are the packet switches. Traditionally, each packet switch comprises a fixed-function switching chip that implements the Ethernet protocol. Figure 1.2 shows the typical specifications of fixed-function packet switches around the year 2020. More recently however, there has been an introduction of programmable packet switches inside the datacenters, that comprise a programmable switching chip that allows the users to program custom packet processing protocols, rather than being restricted to the conventional Ethernet protocol. Figure 1.2 shows the typical specifications of programmable packet switches around the year 2020.

## 1.1.2 Trends in Transistor Scaling

In 1965, Gordon Moore postulated that the number of transistors on a given chip would double every year. He later revised it in 1975 to doubling every two years. This came to be known as the *Moore's law*. Around the same time in 1974, Robert H. Dennard proposed a power scaling law that roughly stated that as transistors get smaller, their power density stays constant, so that the power use stays in proportion with area. This came to be known as *Dennard scaling*. Combined with Moore's law, this meant that the performance per Watt of transistor-based technology would double every 18 months.

For a better part of four decades, Moore's law and Dennard scaling drove the entire transistor-based industry, that powers everything from processors to memory to (solid-state) storage to packet switches—in every technology generation, as the number of transistors on a chip doubled, the circuit became roughly 40% faster, while power consumption (with twice the number of transistors) stayed the same.

However, towards the later half of 2000s, both Moore's law and Dennard scaling started to deviate from their original trends—Dennard scaling ended in 2006, while Moore's law has slowed down significantly since 2010, and is expected to end altogether by as early as 2025 according to some projections [131]. This seismic shift in the transistor scaling trends has had, and continues to have, profound implications for every field in computing. This dissertation focuses specifically on its impact on datacenter networking, and proposes new designs and architectures for networking in the Post-Moore era.

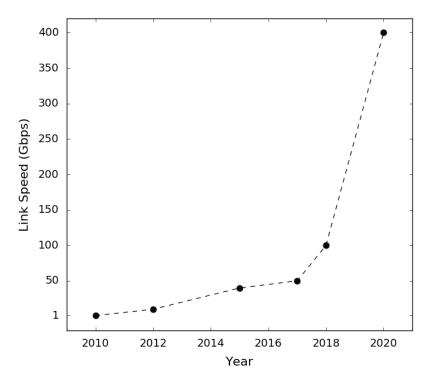

Figure 1.4: Exponential rise in datacenter link speed over the last decade [32].

#### 1.2 Motivation

The number of users on the Internet continues to grow steadily [126], from 1.04 billion in 2005 (16% of the world population in 2005) to 4.15 billion in 2019 (53.6% of the world population in 2019). Popular web applications such as Facebook alone has over 2.6 billion monthly active users as of early 2020 [162]. And almost entirety of all such web applications and services are hosted inside one of the datacenters worldwide. Next, we are also living in a time of massive data explosion, with over 90% of the total data in human history generated in just last few years [158]. According to a market intelligence company [161], the total amount of world's data reached 18 zettabytes in 2018 (a zettabyte is  $10^{21}$  or  $2^{70}$  bytes), and is expected to reach 175 zettabytes by 2025. Further, over 40%

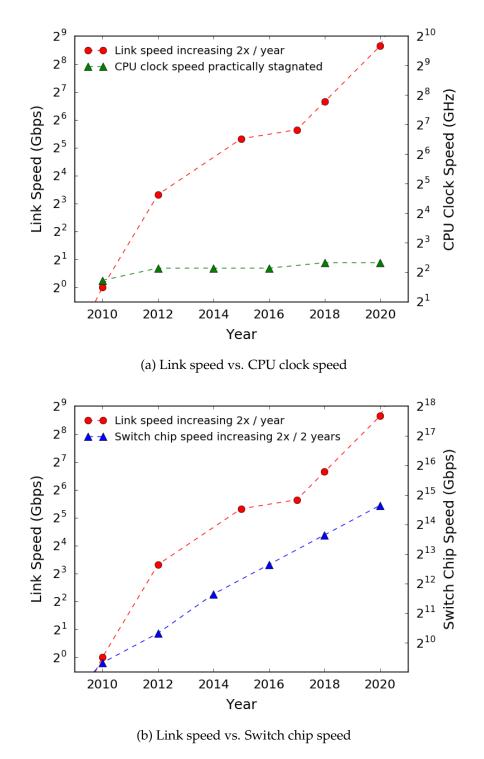

of that data in 2018 was stored and processed inside datacenters worldwide, and by 2025 that number is expected to reach over 65% [161]. Thus, to be able to scale to the large number of users, and process and analyze the large amounts of data, computation inside modern datacenters tends to be massively distributed in nature, i.e., the computation for a given application or service is distributed across multiple end-hosts to overcome the limited processing capacity of a single end-host. A key upshot of such a distributed computation is that all the communication between the end-hosts has to go over the datacenter network connecting the end-hosts. Thus the bandwidth demand from the datacenter network, to effectively facilitate all the remote communications, is rising very rapidly. This demand is further exacerbated by the slowdown in Moore's law and the end of Dennard scaling, that has stagnated the scaling of processing capacity of individual end-hosts, thus forcing the applications to get even more distributed to meet their performance and scalability objectives. In addition, the resources within datacenters (e.g., storage) are also becoming increasingly disaggregated [34], as disaggregation promises to significantly improve the efficiency of datacenters, e.g., via more efficient resource pooling and provisioning, higher compute density, and elastic scaling. This further adds to the rising bandwidth demand. In fact, Google reports that the bandwidth demand inside their datacenters doubles every year [7]. This is also evident from the exponential rise in link speeds inside datacenters, that has increased by 400× during a ten year period of 2010—2020 (virtually doubling every year), as illustrated in Figure 1.4.

Thus overall, there is a pressing need to design a high-speed datacenter networking infrastructure (for both the end-host network stack and the switching fabric) that could effectively scale with the ever-increasing link speeds and bandwidth demand. This is precisely the focus of this dissertation.

## 1.3 Limitations of Existing Approaches

In this section, we discuss how the existing approaches to designing the end-host network stacks (Section 1.3.1) and switching fabrics (Section 1.3.2) fall short when it comes to scaling to ultra-high link speeds and bandwidth demands.

## 1.3.1 General-purpose Processor-based Network Stacks

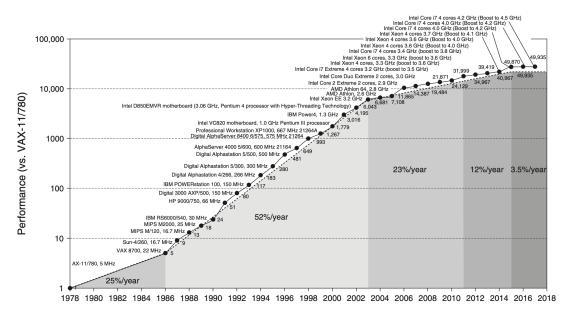

The major portion of the network stack at the end-hosts inside modern datacenters is implemented on top of general-purpose CPUs (Figure 1.1). The key benefit of such a design is the ease of programmability, that allows users the flexibility to program and deploy new algorithms and protocols in software at very small timescales, which is a key enabler for innovations. Further, while the link speeds inside datacenters were relatively slow and CPU processing speeds were scaling exponentially according to Moore's law, a CPU-based network stack was also sufficient to saturate the network access link. However, the slowdown in Moore's law and the end of Dennard scaling has meant that the processing speed of a single CPU core, which once used to double every 18 months, is now doubling every 20 years (Figure 1.5), whereas the link speeds are doubling virtually every year (Figure 1.4). As a result, it is becoming increasingly difficult to saturate the high-speed links using CPU-based network stack [33, 5, 6]. For a concrete example, we consider packet scheduling, a key end-host network stack operation. The job of a packet scheduler is to transmit packets from end-hosts onto the wire in accordance with some scheduling algorithm running at the end-host. Unfortunately, the state-of-the-art CPU-based packet schedulers are barely able to saturate a 10 Gbps link using a single CPU

Figure 1.5: Scaling of CPU performance over the years. Since 2018, the performance improvement is just 3.5% per year, or doubling every 20 years. (Image source: Hennessy & Patterson 6e [43])

core [93]. This is clearly not sufficient, given that the link speeds inside datacenters have already reached over 100 Gbps.

Using multiple CPU cores to implement the network stack can potentially improve the performance, but the performance scaling is typically sub-linear with the number of cores due to Amdahl's law [121] and the overheads of stateful operations (e.g., locking overheads and cache coherency). Further, several prior studies [5, 42, 52] have shown that saturating a 100 Gbps or a 400 Gbps link using a CPU-based network stack would require prohibitively large number of cores. Using the example of packet scheduling from above, even with perfect scaling, it would require 10 cores to schedule packets at line rate over a 100 Gbps link, and a whopping 40 cores for a 400 Gbps link. Even the most powerful commodity servers in 2020 only have a few 10s to up to a 100 cores, and to make matters even worse, the multi-core scaling is fundamentally limited by the power consumption, typically forcing only a subset of cores to be powered-

on at any given time or forcing the cores to run at slower clock speeds [30]. Thus, allocating a large number of cores for exclusively network processing is not only becoming unsustainable but is also a poor utilization of the general-purpose computation power, which could have otherwise been used to run actual applications. For datacenter operators, this could result in significant loss in revenue [33].

Some recent designs have also explored alternative general-purpose architectures for implementing the network stack, such as Graphics Processing Units (GPUs) [52] and NICs with embedded CPU cores [67]. However, these architectures are just different manifestations of a multi-core architecture described above, and hence ultimately suffer from the same fundamental limitations.

## 1.3.2 Packet-switched Switching Fabrics

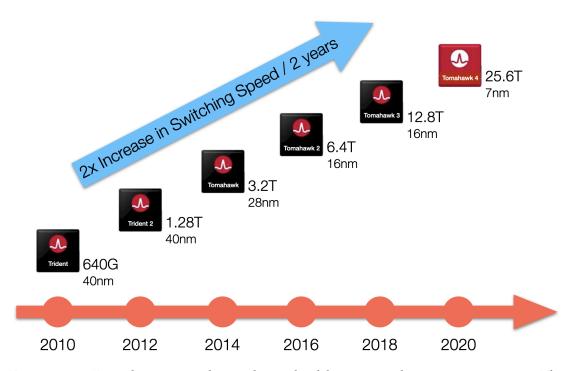

Packet switches are the building blocks of modern datacenter switching fabrics. Each packet switch typically comprises a switching chip responsible for forwarding data at line rate. However, slowdown in transistor and power scaling, due to slowdown in Moore's law and end of Dennard scaling, has also impacted the scaling of switching speeds of packet switches [75]—(i) it has become increasingly difficult to increase the number of I/O pins on a switching chip, thus limiting the number of I/O channels per switching chip, and (ii) it has also become increasingly difficult to increase the rate of serialization and deserialization (SerDes) hardware, thus limiting the data rate per I/O channel. Fortunately, over the last decade (Figure 1.6), by supplementing the slow transistor scaling (40 to 7 nanometer(nm) process shrink over 10 years) with higher-level archi-

Figure 1.6: Broadcom switching chips double in speed every two years. The most recent generation of Broadcom switching chip (Tomahawk 4) runs at 25.6 Terabits/second and is built using 7 nm process technology.

tectural innovations, leading switch chip manufacturers like Broadcom have managed to double the switching speeds of their packet switches every two years [152]. Unfortunately however, even with the current scaling trend, the increase in switching speed is still not able to keep pace with the rising bandwidth demand (Figure 1.8), and even worse, the current scaling trend of packet switches is only going to get slower in the coming years, as transistor scaling is expected to end altogether [131], and the gains from higher-level architectural innovations (such as pipeline parallelism) tend to hit a wall eventually, partly because of power constraints, as observed with multi-core scaling [30].

Next, a typical datacenter switching fabric comprises a collection of packet switches connected in some network topology, the most common being a Folded Clos topology such as Fattree [1] as illustrated in Figure 1.3. Now given that the switching speeds of individual packet switches are unable to keep pace with the increasing bandwidth demand, scaling the switching fabric to higher bandwidth would require more number of switches, more number of tiers in the topology, more number of fibers, and more number of transceivers, which together translates to increased power, cost, and number of hops through the network (latency). As an illustration, consider a 8,192 end-host network. Assuming 25 Gbps links and 128-port × 25 Gbps switches, one could build a full bisection bandwidth Fattree network using two tiers (4 hops), 192 switching chips, 24 K transceivers, and 12 K fibers. Now suppose the end-host link bandwidth increased to 100 Gbps due to an increased bandwidth demand. If the switching speed of individual packet switches was able to scale perfectly with the bandwidth demand, then we would now have 128-port × 100 Gbps switches, and we could build a full bisection bandwidth Fattree network using the same number of resources as before. However, at the other extreme, if the switching speed of individual switches does not scale with the bandwidth demand, each 128port × 25 Gbps switch would now operate as 32-port × 100 Gbps switch, and we would now require three tiers (6 hops), 1,280 switching chips, 40 K transceivers, and 20 K fibers to build a full bisection bandwidth Fattree network, resulting in significant cost, power, and latency overhead even for this toy example.

To overcome some of the cost and power overheads of scaling a traditional Fattree topology, that comprises one switching chip per switch box, datacenter operators have started to build a chassis-based Fattree topology where multiple switching chips are integrated into the same switch box and connected using energy-efficient copper backplane traces (Figure 1.7). Such an architecture increases the switching capacity within each box resulting in fewer transceivers and fibers compared to a traditional Fattree, but it comes at the cost of more

(a) Traditional Packet Switch

(b) Chassis Packet Switch

Figure 1.7: A traditional packet switch with one switching chip per switch box versus a chassis packet switch with multiple switching chips per switch box.

switching chips and more number of hops through the network (latency) [75]. Further, scaling a chassis to higher switching speeds is limited by the power consumption inside a chassis, thus making it difficult to scale to higher speeds.

## **Research Question**

Figure 1.8 summarizes the growing gap in the scaling of link speed versus the CPU and packet switching speed, as explained in detail in Section 1.2 and Section 1.3. As a result, it is becoming increasingly unsustainable to use generalpurpose CPUs and packet switches to build high-speed end-host network stacks and switching fabrics respectively. To that end, this dissertation investigates the following research question —

Research Question # 1 How to design high-speed end-host network stacks and switching fabrics for datacenters that achieve high performance at low cost and power even in light of the continued slowdown in Moore's law and the end of Dennard scaling?

We further breakdown this overarching research question into two subquestions in the following section.

Figure 1.8: Growing gap in the scaling of link speeds versus the CPU and packet switching speeds—link speed is practically doubling every year, whereas packet switch chip speed is doubling every 2 years, while CPU clock speed has practically stagnated (doubling every 20 years).

## 1.5 Approach, Challenges, and Thesis

Given the limitations of existing solutions (Section 1.3), in this section we describe the approach taken in this dissertation to design high-speed end-host network stacks (Section 1.5.1) and switching fabrics (Section 1.5.2) in Post-Moore era. We conclude this section by stating the thesis in this dissertation (Section 1.5.3).

## 1.5.1 Domain-specific Processing: Promise and Challenges

Section 1.3.1 described the limitations of using general-purpose processing architectures for building high-speed end-host network stacks. Hence, in this dissertation, we explore the idea of complementing general-purpose processors with domain-specific processors for network processing, as a way to build high-speed end-host network stacks.

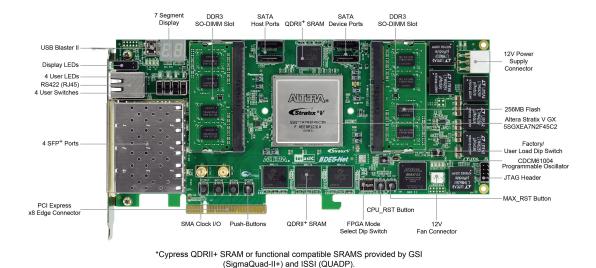

A general-purpose processor is characterized by a fixed, general-purpose hardware architecture, that cannot be customized for specific applications. As a result, one has to rely solely on instruction-level optimizations to extract higher performance. An alternative is Field-programmable Gate Array (FPGA), which can be programmed with any custom hardware architecture (general-purpose or otherwise). The ability to customize low-level hardware architecture means that an FPGA-based implementation of an application typically achieves higher performance compared to a general-purpose processor-based implementation, but unfortunately, the performance (and power efficiency) is much lower compared to an Application-specific Integrated Circuit (ASIC)-based implementa-

tion [56]. This is because FPGAs rely on a generic reconfigurable substrate to program arbitrary hardware architectures, and unfortunately, this comes with performance overhead—in essence, FPGAs are just another general-purpose platform, albeit with a much lower-level programming abstraction compared to general-purpose processors, and this generality comes at the cost of performance. In fact, in a world where performance is the first-order objective, it has been previously argued [145] that FPGAs are better suited as experimental platforms for prototyping and validating new hardware architectures, prior to porting those architectures to an ASIC (which is a much more time-intensive and irreversible process). As described in Section 1.7, we use FPGAs extensively in this dissertation to prototype and validate new hardware architectures.

On the other hand, a domain-specific processor presents a different set of trade-offs. A domain-specific processor is an Application-specific Integrated Circuit (ASIC), that comprises a custom hardware architecture targeted towards a specific set of applications. The promise of domain-specific processors is that they can potentially achieve much higher performance compared to general-purpose processors and FPGAs, for the target set of applications for which they were designed. The trade-off, of course, is that unlike general-purpose processors and FPGAs, domain-specific processors cannot support arbitrary applications. Thus, domain-specific processors present a fundamental trade-off between the range of applications a processor can support (programmability) and the rate at which it can process those applications (performance).

Unfortunately, even in light of recent advances in programmable network data plane [16, 15, 103], most state-of-the-art domain-specific processors for end-host network processing still tend to be fixed-function, that give up on

programmability altogether in favor of performance<sup>1</sup>. Examples include fixed-function ASIC NICs that support a specific congestion control algorithm [187] or a specific packet scheduling algorithm [88] or a handful of other network stack functionalities [129, 156, 135], none of which can be modified or augmented with new functionalities once the NIC has been manufactured. The reason for such a design choice is rooted in the conventional wisdom that it is extremely difficult to achieve both programmability and high-performance. And given that performance is the first-order objective, domain-specific processors make a fair trade-off by compromising on programmability. However, in the fast evolving field of datacenter networking, one needs the flexibility to experiment and adopt new algorithms and protocols without having to re-design the entire processor from scratch, which could take of the order of years. Hence, one cannot completely give up on programmability.

Thus overall, the challenge with realizing the promise of domain-specific processors for network processing lies in designing the hardware architecture for the processor that achieves the right balance between programmability and performance. This dissertation focuses specifically on packet scheduling as the target network processing application. Unfortunately, all state-of-the-art processors for packet scheduling compromise either on programmability or on performance (either speed or scalability) [99].

To that end, this dissertation investigates the following research question — **Research Question # 1.1** *How to design a domain-specific processor for packet scheduling that is simultaneously programmable and high-performance (in terms of both speed and scalability)?*

<sup>&</sup>lt;sup>1</sup>There are some works done concurrently with this dissertation, most notably Tonic [6], that share our vision of programmable domain-specific processors for end-host network processing.

## 1.5.2 Circuit Switching: Promise and Challenges

Section 1.3.2 described the limitations of using packet switches for building high-speed switching fabrics. Hence, in this dissertation, we explore the idea of using circuit switches to build high-speed switching fabrics in a cost and power efficient manner.

Unlike packet switches, circuit switches do not make forwarding decisions for each packet (via the packet's header contents). As a result, circuit switches are fundamentally much simpler than packet switches—unlike packet switches, circuit switches have no packet processing pipeline, no packet buffers, and no serialization-deserialization circuit. A circuit switch simply has a *crossbar* used to set-up connections (or circuits) between the switch's input and output ports for forwarding data.

One can use different technologies to build the crossbar for circuit switches, the two most common being the *electrical* and the *optical* technology. An electrical circuit switch is built using the same transistor technology as a packet switch, and hence is fundamentally limited by the transistor scaling trends. But given the simplicity of circuit switches over packet switches, an electrical circuit switch can be far more cost and power efficient than an equivalent packet switch [101]. Thus, one can potentially scale an electrical circuit-switched fabric to higher speeds at significantly lower power and cost than a packet-switched fabric. On the other hand, an optical circuit switch is fundamentally different from an electrical packet or circuit switch. An optical circuit switch is a layer 0 switch—it operates directly on light beams without needing to translate the optical signals into electrical signals and vice-versa. Thus an optical circuit switch, e.g., it

does not need transceivers at each switch to convert between optical and electrical signals. But more importantly, since optical circuit switches operate directly on light beams, these switches are data rate agnostic, meaning as the link speeds in datacenters scale to higher speeds (e.g., 100 Gbps to 400 Gbps and beyond), an optical switching fabric need not be upgraded. Hence, in summary, a packet-switched fabric can scale to higher speeds with significant increase in cost and power, an electrical circuit-switched fabric can scale to higher speeds with much smaller increase in cost and power compared to a packet-switched fabric, whereas an optical circuit-switched fabric can scale to higher speeds with zero increase in cost and power (on account of being data rate agnostic).

Interestingly, the scaling advantages of circuit switches over packet switches have been known for decades. And yet, modern datacenters use packet switches over circuit switches to build their switching fabrics. The reason being that the scaling advantages of circuit switches come at a price—unlike packet switches, circuit switches first need to be configured (i.e., the circuits between input and output ports need to be set-up) prior to sending any data. One can further break down this operation into a control plane operation (i.e., deciding on when and what circuits to set-up, or circuit scheduling) and a data plane operation (i.e., creating/changing the physical circuits as asked by the control plane, or *circuit reconfiguration*). Unfortunately, circuit switches have traditionally been bottlenecked by the data plane reconfiguration delay, that could be of the order of milliseconds [31] to 10s of microseconds [74]. As a result, these switches are unsuitable for carrying low latency traffic or traffic patterns that change unpredictably and at a very fine granularity, all of which are the case with the datacenter traffic [36]. As a result, prior designs [31, 74] have to rely on a hybrid network, comprising a circuit-switched fabric carrying the stable bulk traffic

and a separate packet-switched fabric carrying the unpredictable low latency traffic. Unfortunately, such a design has several known challenges, including complexity of managing two separate networks, the challenge of precisely dividing the host bandwidth between the two networks (which would depend upon what fraction of the traffic is low latency and what fraction is bulk, something that is a function of the current workload and keeps changing over time), and the challenge of recognizing in the first place what traffic constitutes low latency and what traffic constitutes bulk traffic. Further, by relying on a packet-switched network, the hybrid network is fundamentally limited by the scaling limitations of packet switches (Section 1.3.2). Ideally, we would want an entirely circuit-switched fabric that could efficiently support any arbitrary traffic.

Fortunately, recent advances in the circuit switching technology means that we now have electrical circuit switches commercially available [167], and optical circuit switches available as research prototypes [97, 27, 106, 55, 22, 29, 183, 63], that could reconfigure within nanoseconds. Hence for these switches, the data plane is no longer the bottleneck to supporting unpredictable low latency traffic, and in fact, the bottleneck has shifted to the control plane.

Traditional control planes for circuit-switched networks typically comprise a centralized controller that takes in the current traffic pattern as input and runs some optimization algorithm to figure out the right set of circuits to schedule [31]. While such a design was not a bottleneck for slow reconfigurable circuit switches, unfortunately it is too slow for fast reconfigurable circuit switches, completely neutralizing the advantage of having a fast data plane.

Thus overall, one can potentially use fast circuit switches to build high-speed switching fabrics that could support arbitrary traffic with high-performance at

low power and low cost. However, to realize this promise, one needs a fast and high-performance control plane for circuit-switched networks.

To that end, this dissertation investigates the following research question — **Research Question # 1.2** *How to design a control plane for circuit switching that can schedule high-performing circuit configurations at nanosecond granularity?*

#### 1.5.3 Thesis for High-speed Networking in the Post-Moore Era

The central thesis in this dissertation is that by effectively leveraging the promise of domain-specific processing and fast circuit switching, one can indeed build efficient high-speed network stacks and switching fabrics even in light of continued slowdown in Moore's law and the end of Dennard scaling.

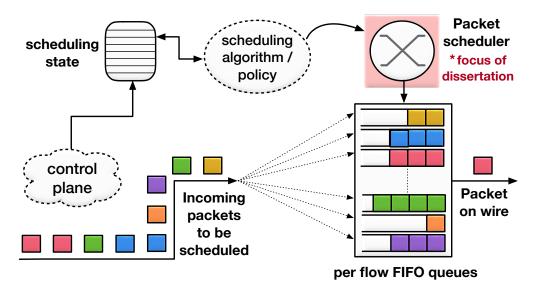

The challenge with domain-specific processing is in designing an architecture that achieves the right balance between programmability and performance (Section 1.5.1). This dissertation focuses specifically on a domain-specific processor for packet scheduling. Packet scheduling algorithms assign packets a time and a rank to decide when packets become eligible for scheduling and in what order to schedule eligible packets. The thesis in this dissertation is that a processor that simply schedules the "smallest ranked eligible packet" at any given time, is sufficient to program a wide-range of packet scheduling algorithms. Further, by leveraging hardware-level parallelism and indirection techniques, one can also design a fast and scalable architecture for such a processor.

The challenge with fast circuit switching is in designing a control plane that is both fast and high-performance, since the traditional dynamic, traffic-aware

centralized solutions are too slow (Section 1.5.2). The thesis in this dissertation is that it is not necessary to have a dynamic, traffic-aware centralized control plane to achieve high performance, and in fact, by carefully choosing a static, pre-defined schedule for circuit scheduling, it is possible to build a fully decentralized, traffic-agnostic control plane that can schedule high-performing circuit configurations at nanosecond granularity.

#### 1.6 Contributions

In this section, we summarize the key contributions of this dissertation that validate the thesis proposed in Section 1.5.3.

#### 1.6.1 Fast Domain-specific Processor for Packet Scheduling

Packet scheduling is one of the most fundamental network stack operations. Packet scheduling algorithms assign packets a *time* and a *rank* to decide *when* packets become eligible for scheduling and *in what order* to schedule eligible packets onto the wire. Unfortunately, state-of-the-art packet schedulers either compromise on programmability or on performance (either speed or scalability). In PIEO (Chapter 2), we designed and implemented a domain-specific processor for packet scheduling that is *simultaneously* programmable, scalable, and high-speed. For programmability, we introduced a new primitive called Push-In-Extract-Out (PIEO) that can express a wide-range of packet scheduling algorithms by always scheduling the "smallest ranked eligible packet". In fact, we show that PIEO primitive is more expressive than any state-of-the-art packet

scheduling primitive. Unfortunately, while being expressive, designing an efficient hardware implementation of PIEO is challenging, as it requires maintaining a fully ordered list. Implementing an ordered list in hardware presents a fundamental trade-off between time complexity and hardware resource consumption, which translates into a fundamental trade-off between performance and scalability. To keep up with increasing link speeds, scheduling decisions ideally need to be made in O(1) time, but the best know implementation of an O(1)-time ordered list requires O(N) flip-flops and comparators (where N is the list size), which greatly limits the scalability of the design. In PIEO, we improve the O(N) bound on resource consumption for an O(1)-time ordered list by an order of complexity to  $O(\sqrt{N})$ . The result being that PIEO can make scheduling decisions in O(1) time (up to 300× faster than a single CPU core), while also scaling to 10s of thousands of flows (>30× more scalable than state-of-the-art). Looking further, PIEO's design is more general than merely a packet scheduler. In essence, PIEO presents the design of a scalable O(1)-time ordered list in hardware. This can be leveraged for high-performance implementations of several key datastructures in hardware, including priority queues [134], key-value stores [128], and balanced search trees [136]. Many applications use one or more of these datastructures, and hence as more applications are offloaded to hardware for higher performance in the Post-Moore era, PIEO can serve as a basic building block for those applications, packet scheduling being one of them.

## 1.6.2 Fast Circuit-switched Switching Fabric

In Shoal (Chapter 3), we present the design and implementation of a circuitswitched network comprising entirely of fast (nanosecond) reconfigurable circuit switches. The key contribution here is the design and implementation of a control plane for the circuit-switched network that could schedule highperforming circuit configurations at nanosecond granularity. At the core of the design is a new primitive for circuit scheduling that comprises a static, pre-defined schedule to determine what circuits to set-up at any given time. By precluding any dynamic traffic-aware decision-making for circuit scheduling, the design ensures that circuits can be scheduled at nanosecond granularity to match the data plane reconfiguration speed. Further, we show that by appropriately configuring the static schedule, one can also extract very high network performance. More specifically, different configurations of the static schedule creates a different virtual network topology, and in Shoal, we configure the schedule to create a *virtual full mesh* topology. Next, we leverage the well-known Valiant Load Balancing (VLB) [171] to route data on top of the virtual full mesh topology that guarantees bounded worst-case network throughput. Unfortunately, such a routing scheme, while bounding the worst-case throughput, could result in congestion at the intermediate hop for certain traffic patterns. To that end, we propose a novel congestion control algorithm, that leverages the static schedule to provide bounded worst-case queuing and fair share of bandwidth for arbitrary traffic. Further, the entire design of Shoal's control plane is agnostic to the underlying circuit-switching technology, and could work with electrical, optical, or wireless technologies alike.

Overall, we demonstrate that Shoal can effectively scale to high switching speeds while achieving comparable or better performance (in terms of both throughput and latency) than several recent packet-switched network designs at significantly lower power and cost.

Figure 1.9: A DE5-Net board with Stratix V FPGA.

## 1.7 Evaluation Methodology

The systems presented in this dissertation propose fundamental changes to the networking hardware, that includes both the switches and the end-host Network Interface Cards (NICs). Hence, to evaluate these systems, we design and implement custom switches and NICs on top of Field-programmable Gate Arrays (FPGAs). In addition, this dissertation also proposes novel network protocols and algorithms to run on top of our custom hardware. To evaluate them, we use a small-scale network prototype built using our FPGA-based switches and NICs, and complement it with a packet-level network simulator for large-scale evaluations. Below we provide an overview of the hardware, prototype, simulator, and workloads used to evaluate the systems in this dissertation. The detailed evaluations can be found in Chapter 2 and Chapter 3.

**Hardware.** We use DE5-Net boards (Figure 1.9) from Terasic [113] to implement our custom hardware. A DE5-Net board is an FPGA development board with an Altera Stratix V FPGA [154] comprising 234 K Adaptive Logic Modules

(ALMs), 52 MBits SRAM, and four 10 Gbps ports for a total of 40 Gbps interface bandwidth. The code is written in System Verilog [139] and Bluespec System Verilog [118]. We synthesize our design using Quartus Prime software [155].

The DE5 boards are plugged into Peripheral Component Interconnect Express (PCIe) Gen 3.0 slots in a PCIe expansion system (Figure 1.10). The PCIe expansion system is a  $4U \times 24''$  deep  $\times$  19" box from One Stop Systems (OSS) [160], comprising 16 PCIe Gen 3.0  $\times$ 8 electrical,  $\times$ 16 mechanical expansion slots using two OSS-452 backplanes, two 1200 W power supplies, two OSS-HIB38- $\times$ 16 host and two target interface boards, and two 1 m PCIe cables.

Finally, the PCIe expansion system is connected to a Dell T720 server using the two PCIe cables. The server comprises a dual socket, 2.93 GHz six core Xeon X5670 processor with 12 MB of shared Level 3 (L3) cache, 12 GB of DRAM (6 GB connected to each of the two CPU sockets), 4 PCIe  $\times$ 8 slots, 1 PCIe Gen 2.0  $\times$ 4 slot, and 1 PCIe Gen 2.0  $\times$ 16 slot.

The network interface of DE5 boards are connected using Myricom 10 G Small Form-factor Pluggable (SFP+) transceiver modules with Ethernet 10 GBase-SR type [150] and 2 m full duplex singlemode fiber cables [151].

**Small-scale network prototype.** For evaluation, we build a small-scale network comprising eight end-host NICs and six switches using our FPGA-based switches and NICs (Figure 1.10). Two FPGAs are used to implement eight NICs, one per port. Six FPGAs implement six 4-port switches. The switches are connected in a two-tier Fattree topology with full bisection bandwidth.

Large-scale network simulations. For large-scale network evaluations, we complement our small-scale prototype with a packet-level network simulator

Figure 1.10: Small-scale network for evaluation comprising 8 end-host NICs and 6 switches connected in a two-tier Fattree topology with full bisection bandwidth (also known as leaf-spine topology) connected inside the PCIe expansion system.

written in C. Before running any large-scale simulations, we first cross-validate our simulator with our prototype by running our prototype experiments on the simulator (configured with the same parameters as the prototype) and ensuring that the results match. This gives us confidence in our simulation results. All the system-specific simulation parameters are guided by our prototype.

**Workloads.** We use a variety of workloads to evaluate our systems. These include a set of custom workloads, used primarily to microbenchmark our systems, followed by more realistic workloads modeled after published datacenter traces [2, 36]. For the sake of robustness, we also evaluate our systems against workloads derived from the emerging disaggregated workload traces [34].

#### 1.8 Source Code Availability

Source code for the systems presented in this dissertation is available online at:

PIEO (Chapter 2): https://github.com/vishall303/PIEO-Scheduler

Shoal (Chapter 3): https://github.com/vishall303/Shoal

- For PIEO, the source code consists of the hardware implementation of PIEO primitive written in System Verilog [139]. The code was synthesized on an Altera Stratix V FPGA [154].

- For Shoal, the source code consists of the hardware implementation of Shoal switch and NIC written in Bluespec System Verilog [118]. The code was synthesized on an Altera Stratix V FPGA [154]. The source code also contains a custom packet-level network simulator written in C.

## 1.9 Organization

The rest of this dissertation is organized as follows. In Chapter 2, we describe PIEO, a domain-specific processor for high-speed packet scheduling. In Chapter 3, we describe Shoal, a fast circuit-switched switching fabric for datacenters. We survey the related work in Chapter 4, which is followed by future work in Chapter 5. We finally conclude in Chapter 6.

#### **CHAPTER 2**

# FAST DOMAIN-SPECIFIC PROCESSOR FOR PACKET SCHEDULING : PIEO