# Process-Tolerant Low-Power Design for the Nano-meter Regime

Kaushik Roy

Electrical & Computer Engineering

Purdue University

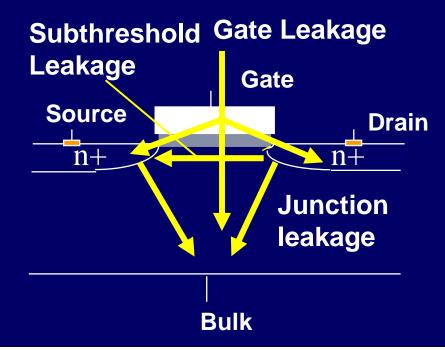

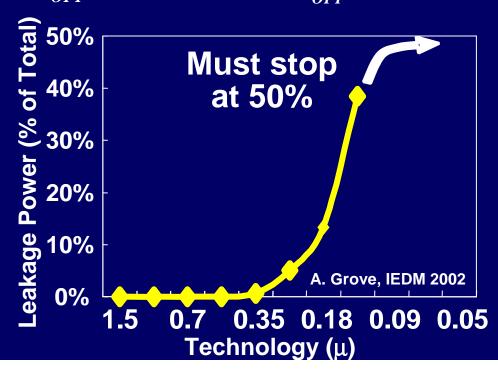

# Exponential Increase in Leakage

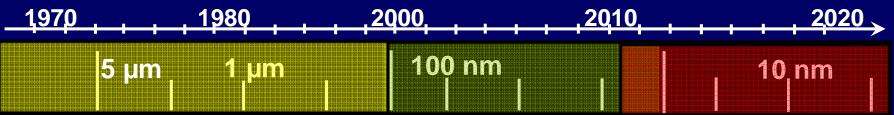

# Silicon Micro- electronics

$$\frac{I_{ON}}{I_{OFF}} = 10^6$$

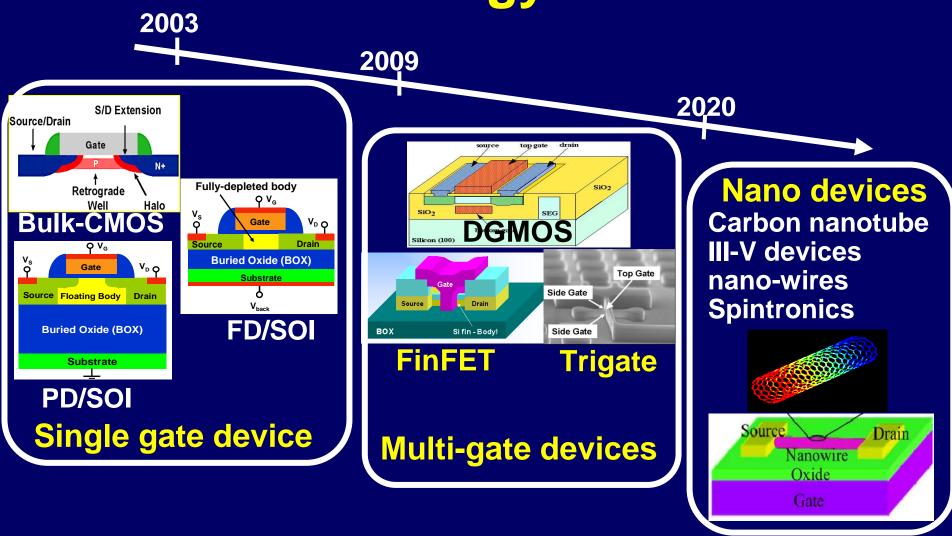

# Silicon Nano- electronics

$$\frac{I_{ON}}{I_{OFF}} = 10^3$$

#### Non-Silicon Technology

$$\frac{I_{ON}}{I_{OFF}} \sim 10^{2\sim6}$$

### **Technology Trend**

Design methods to exploit the advantages of technology innovations

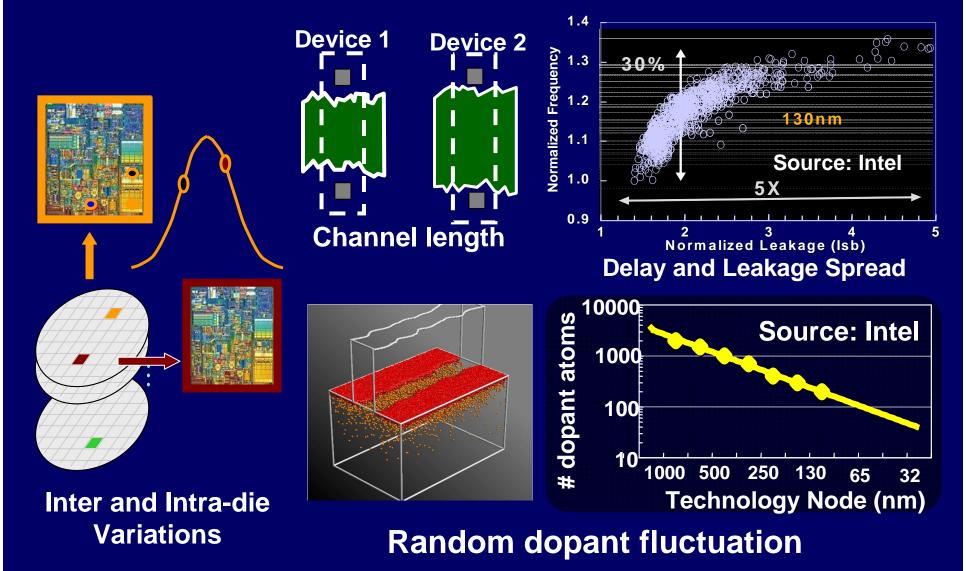

#### **Variation in Process Parameters**

Device parameters are no longer deterministic

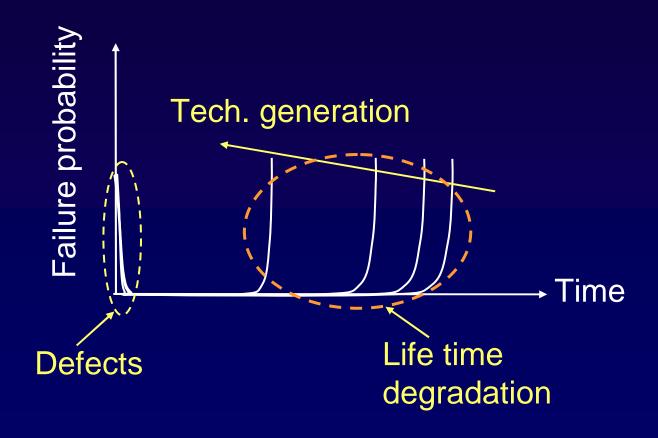

# Reliability

Temporal degradation of performance -- NBTI

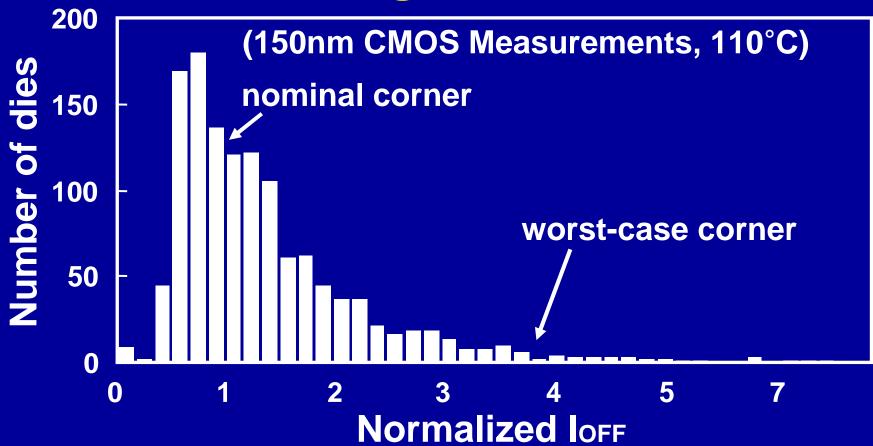

#### Pessimistic Design Hurts Performance

- Substantial variation in leakage across dies

- 4X variation between nominal and worst-case leakage

- Performance determined at nominal leakage

- Robustness determined at worst-case leakage

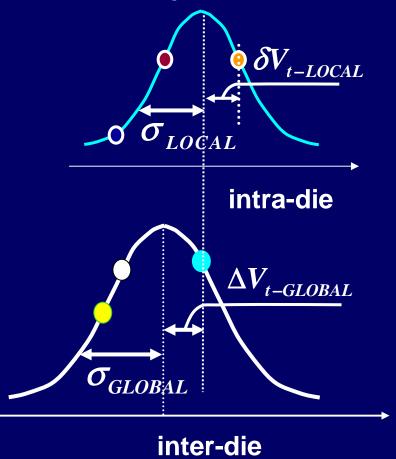

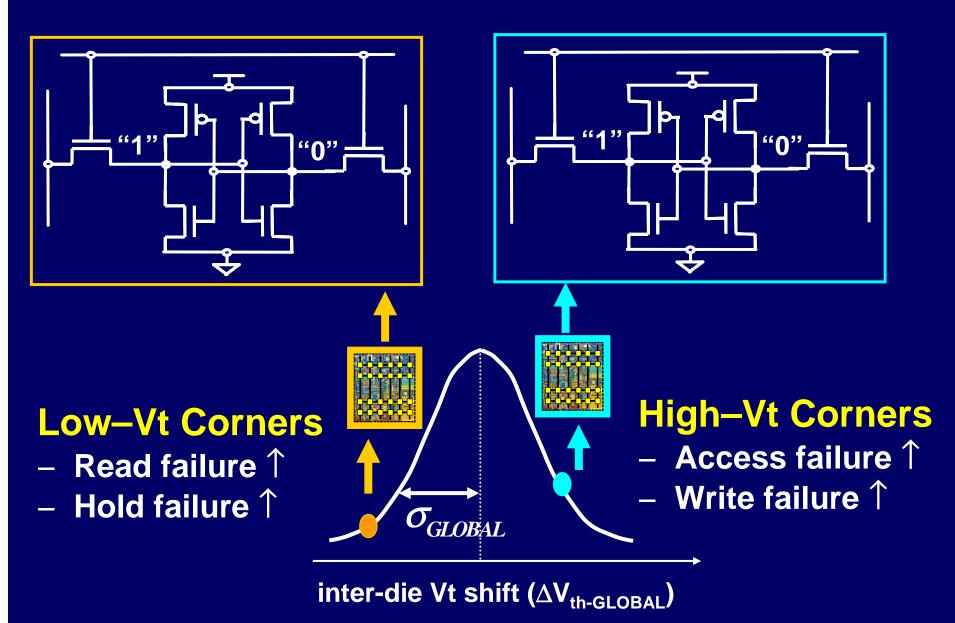

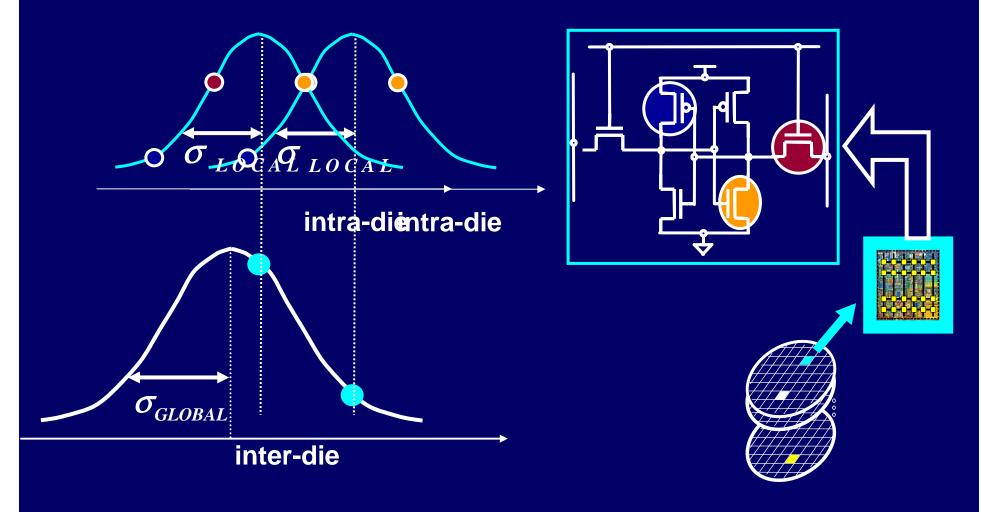

#### **Global and Local Variations**

$$\delta V_{t} = \Delta V_{t-GLOBAL} + \delta V_{t-LOCAL}$$

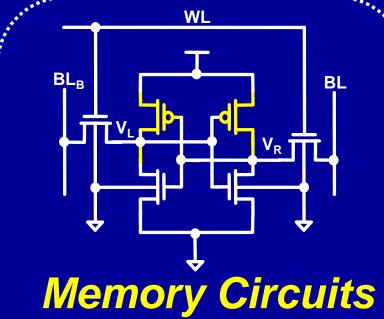

#### **Process Tolerance: Memories**

S. Mukhopadhaya, Mahmoodi, Roy VLSI Circuit Symposium 2006, JSSC 2006, TCAD

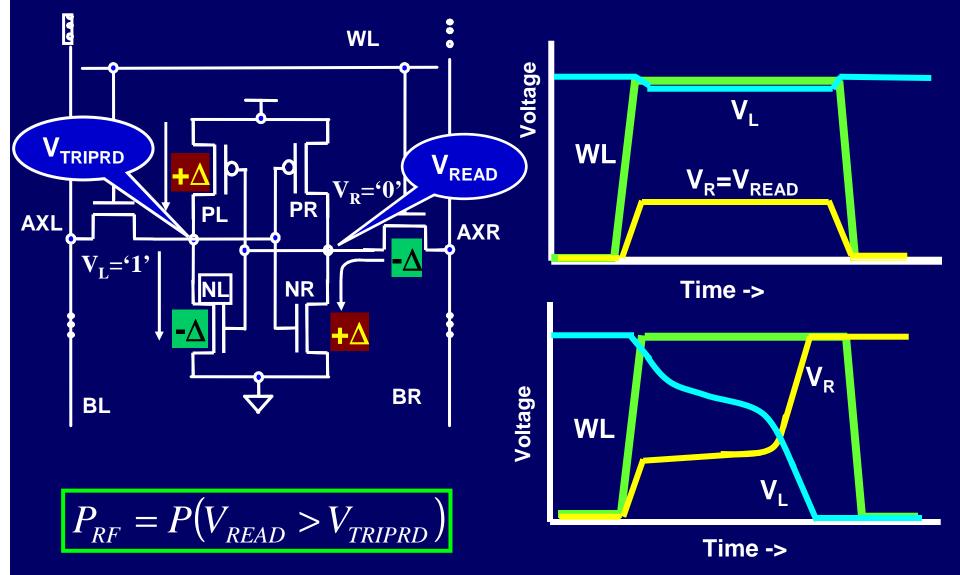

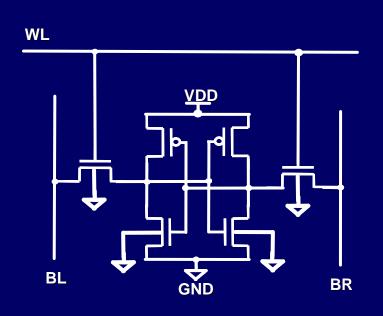

#### Parametric Failures: Read Failure

Read failure => Flipping of Cell Data while Reading

#### **Parametric Failures in SRAM**

#### **Parametric failures**

- Read Failures

- Write Failures

- Access Failures

- Hold Failures

Parametric failures can degrade SRAM yield

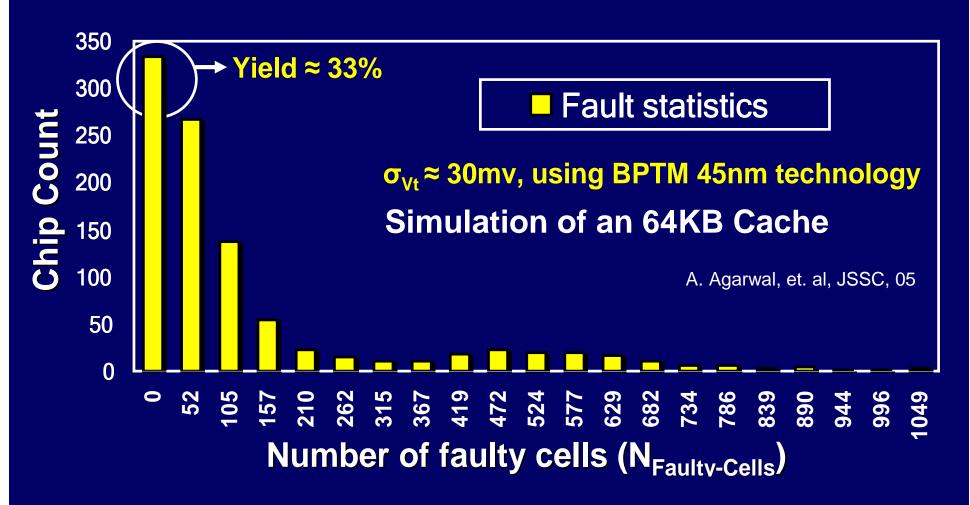

#### **Process Variations in On-chip SRAM**

Parametric failures → Yield degradation

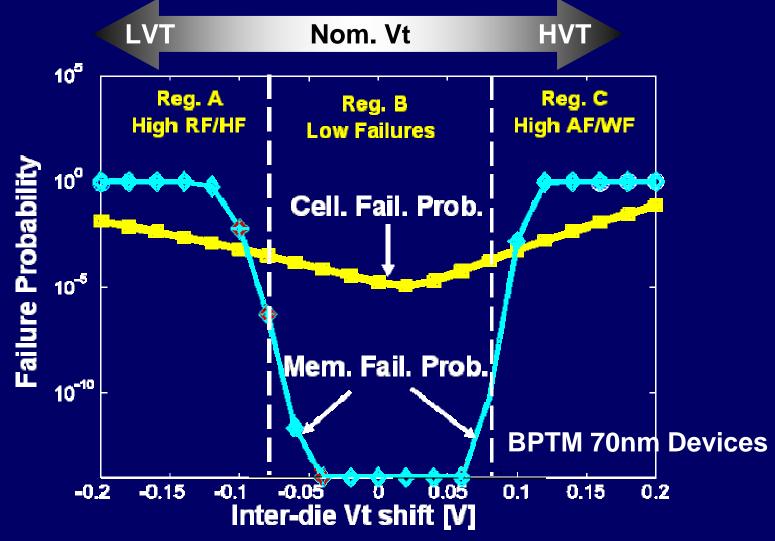

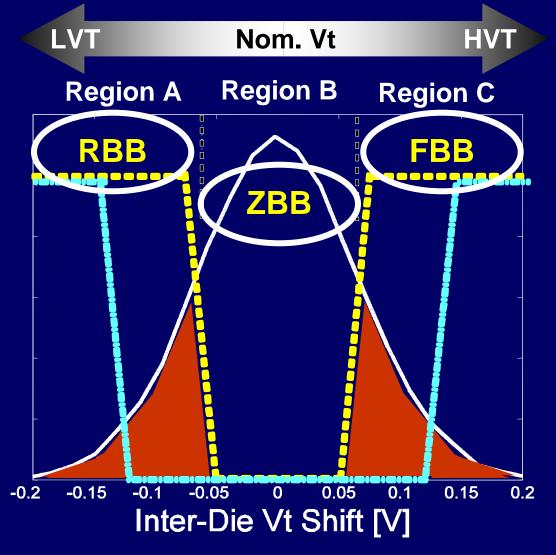

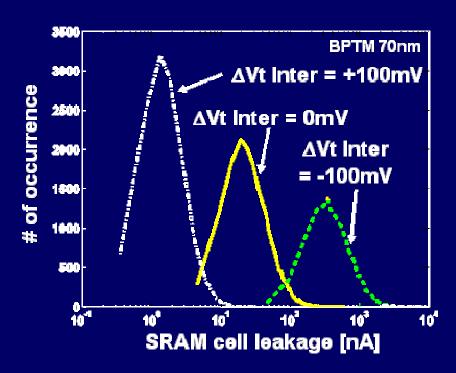

#### **Inter-die Variation & Cell Failures**

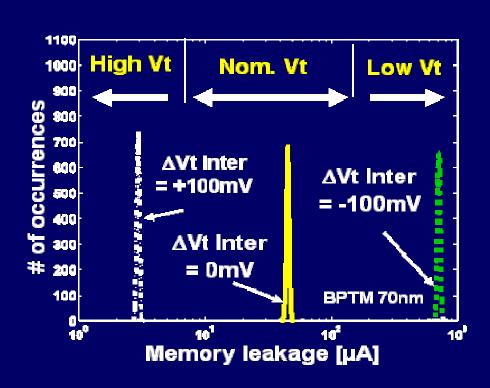

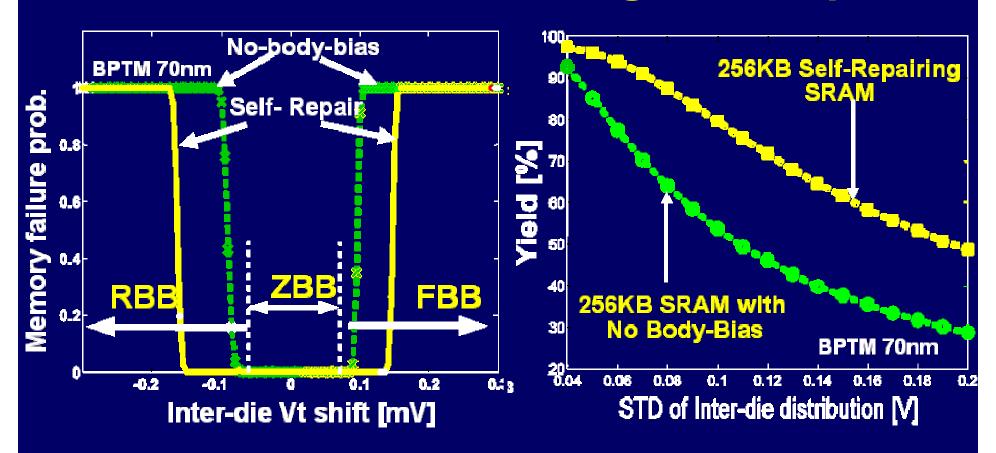

#### **Inter-die Variation & Memory Failure**

Memory failure probabilities are high when inter-die shift in process is high

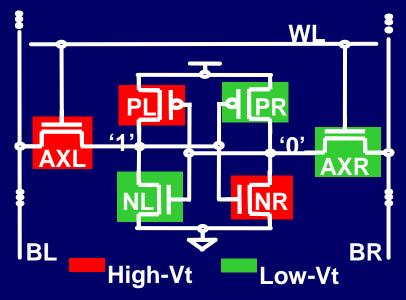

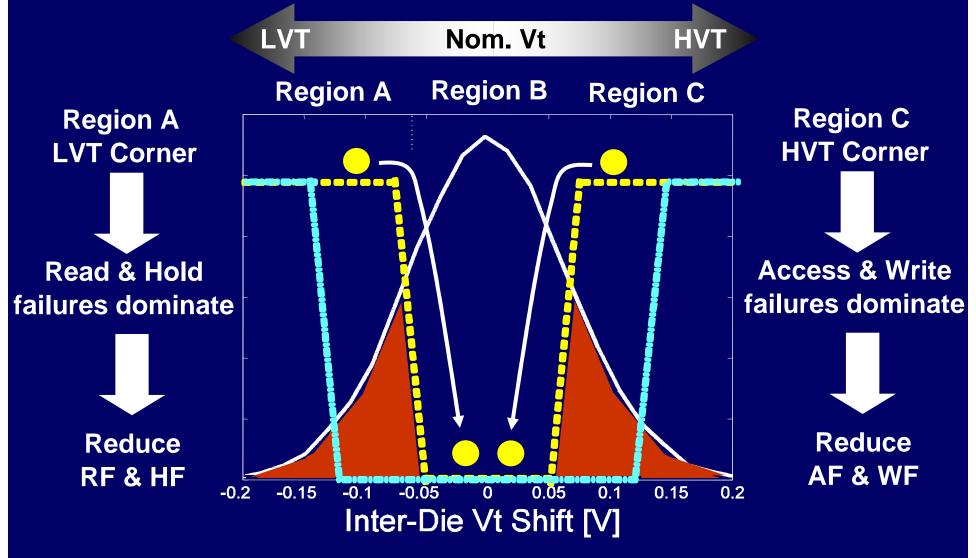

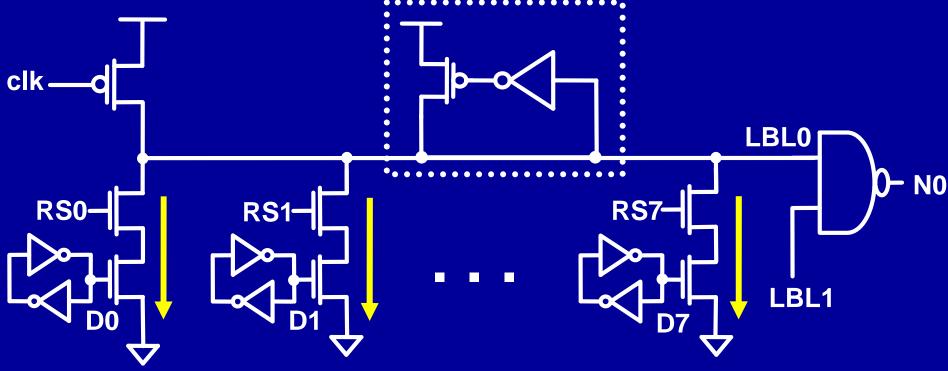

#### **Self-Repairing SRAM Array**

Reduce the dominant failures at different inter-die corners to increase width of low failure region

#### Post-Silicon Repair: Proposed Approach

Apply correction to the global variation to reduce number of failures due to local variations

#### **Self-Repairing SRAM Array**

Reduce the dominant failures at different inter-die corners to increase width of low failure region

# How to identify the inter-die Vt corner under a large intra-die variation?

Monitor circuit parameters, e.g. leakage current

Effect of inter-die variation can be masked by intra-die variation

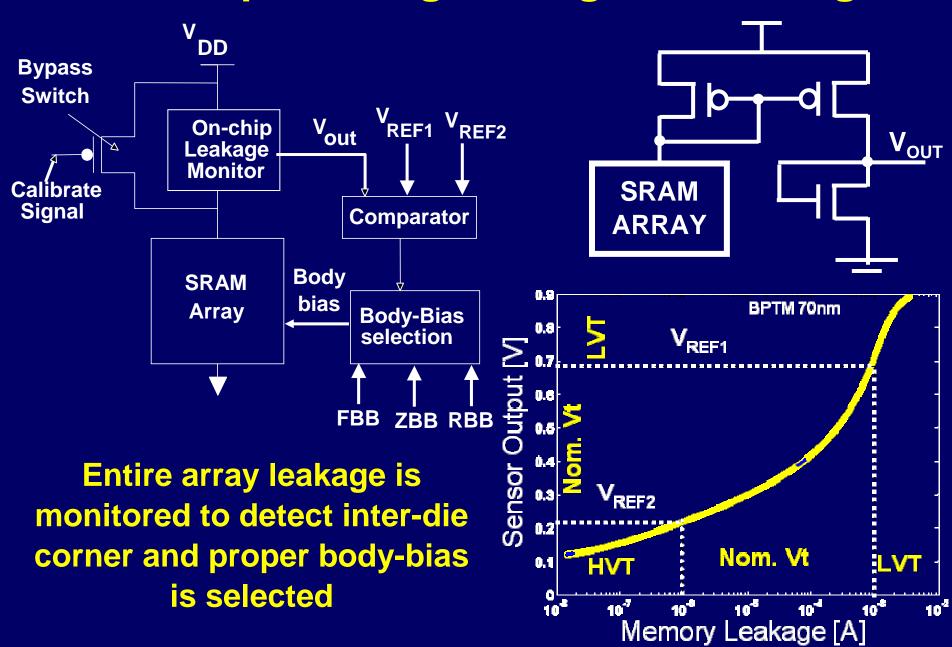

# **Array Leakage Monitoring**

$$Y = \sum_{i=1}^{N} X_i \Longrightarrow \frac{\sigma_Y}{\mu_Y} = \frac{1}{\sqrt{N}} \frac{\sigma_X}{\mu_X}$$

Adding a large number of random variables reduces the effect of intra-die variation

Leakage of entire SRAM array is a reliable indicator of the inter-die Vt corner

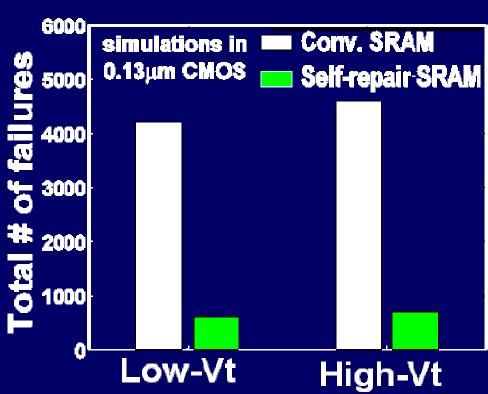

#### Self-Repair using Leakage Monitoring

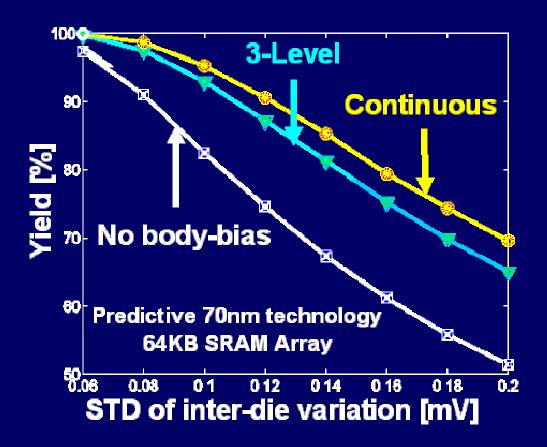

### Yield Enhancement using Self-Repair

Self-Repairing SRAM using body-bias can significantly improve design yield

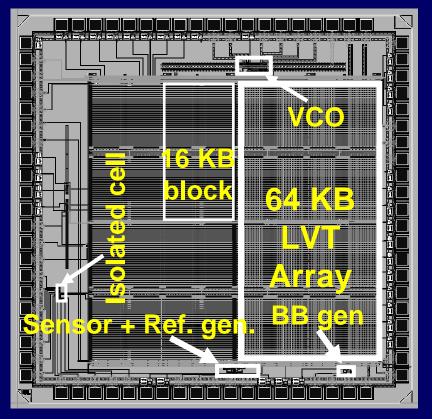

#### **Test-Chip of Self-Repairing SRAM**

Technology: IBM 0.13 μm

128KB SRAM

**Dual-Vt Triple-well tech.**

Number of Trans: ~ 7 million

Die size: 16mm2

**VLSI CKT Symp. 2006, ITC 2005**

Simulation results for 1MB array designed in IBM 0.13µm

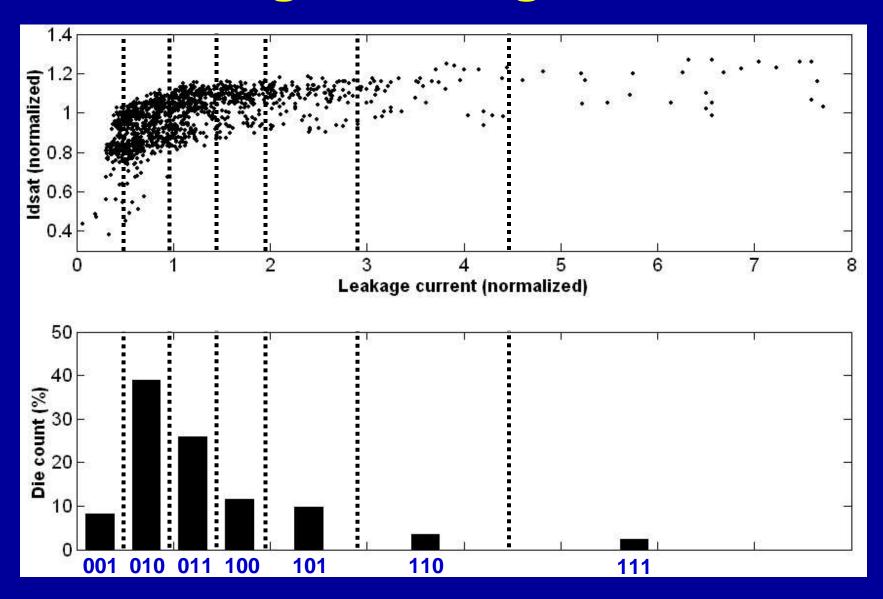

#### **Continuous vs Quantized Body Bias**

Quantized (3 Level: FBB, ZBB, RBB) body bias scheme is a cost effective solution with good yield enhancement possibility

Process Tolerance: Register Files

Kim et. al. VLSI Circuit Symposium 2004

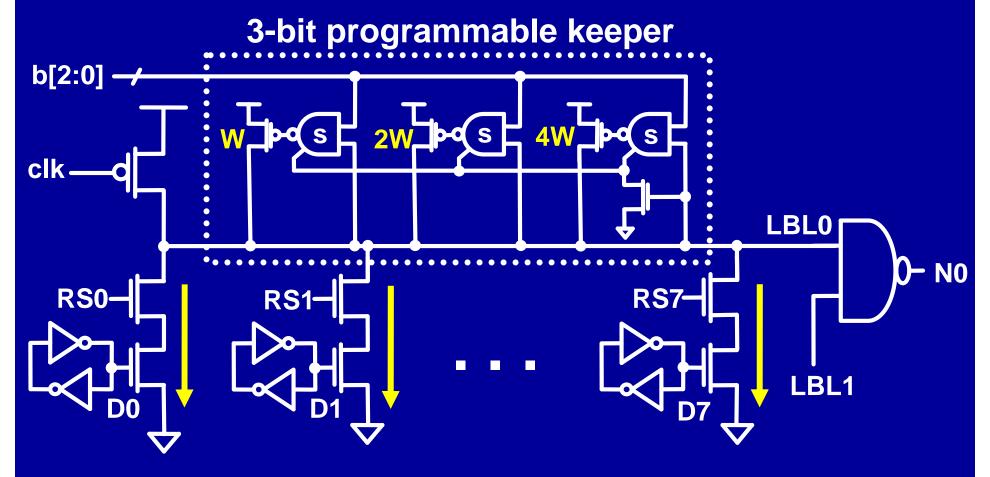

# Process Compensating Dynamic Circuit Technology

Conventional Static Keeper

Keeper upsizing degrades average performance

# Process Compensating Dynamic Circuit Technology

C. Kim et al., VLSI Circuits Symp. '03

Opportunistic speedup via keeper downsizing

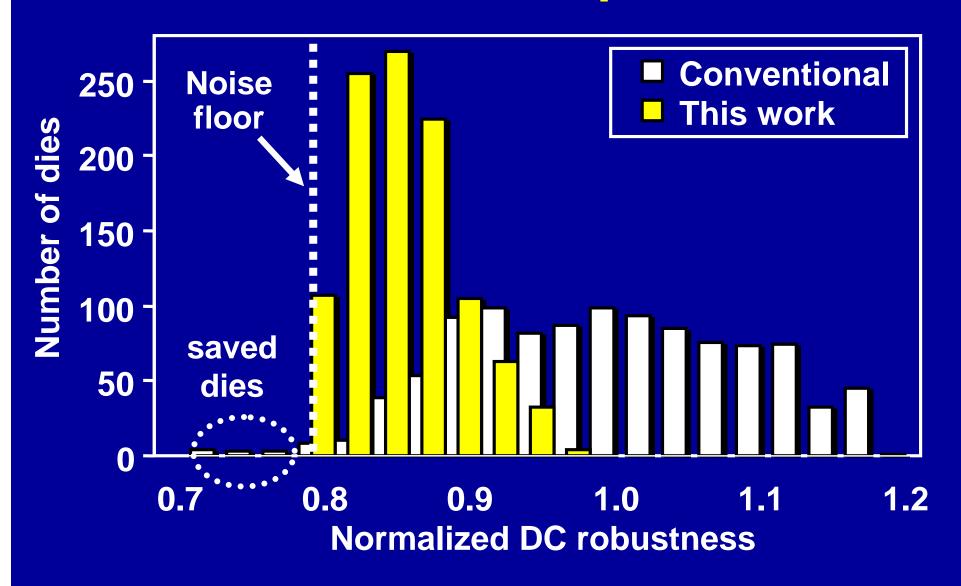

### Robustness Squeeze

5X reduction in robustness failing dies

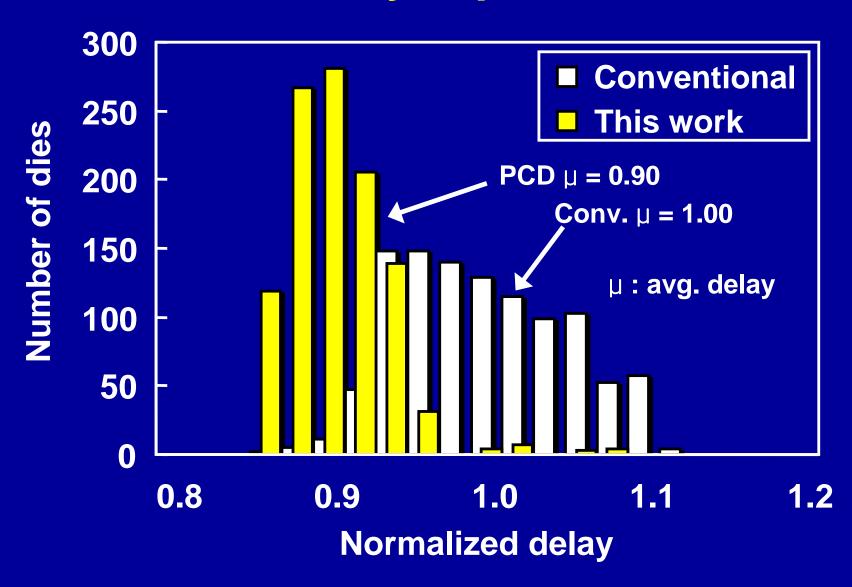

#### **Delay Squeeze**

10% opportunistic speedup

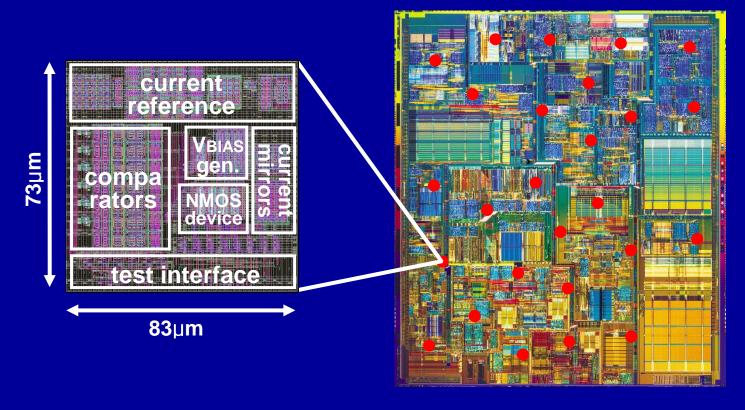

# On-Die Leakage Sensor For Measuring Process Variation

C. Kim et al., VLSI Circuits Symp. '04

High leakage sensing gain – 90nm dual-Vt,

Vdd=1.2V, 7 level resolution, 0.66 mW @80C<sup>o</sup>

# **Leakage Binning Results**

**Output codes from leakage sensor**

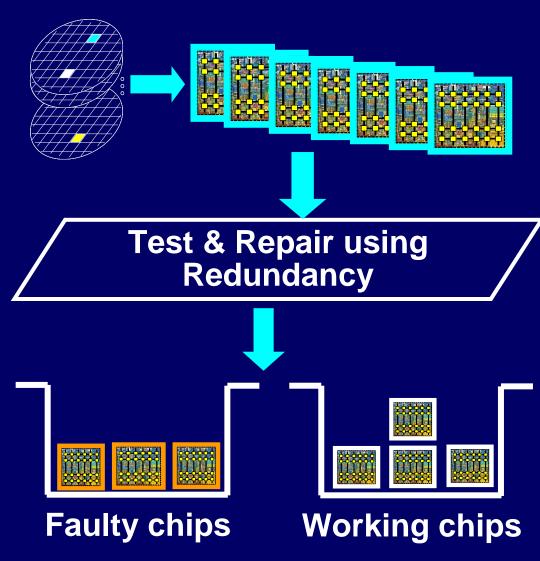

#### **Self-Contained Process Compensation**

Fab

Wafer test

**Process detection**

Leakage measurement

On-die leakage sensor

Program

PCD

using

fuses

Customer

Package test

**Burn** in

**Assembly**

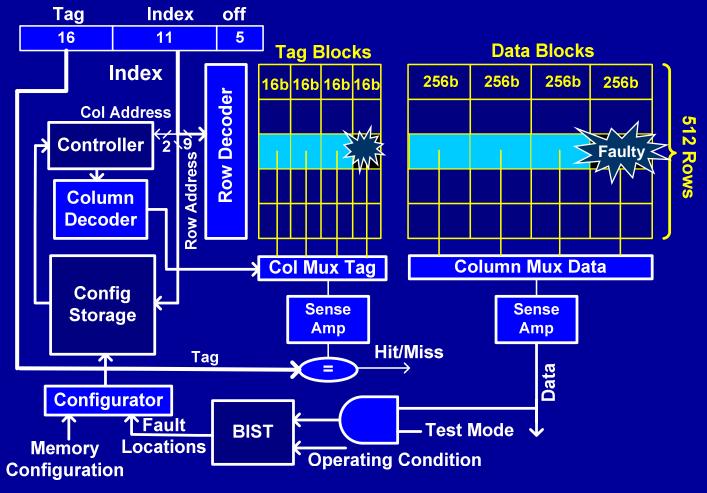

### Self-Repair: Architecture Level

Agarawal, Roy TVLSI 2005

#### **Fault-Tolerant Cache Architecture**

- BIST detects the faulty blocks

- Config Storage stores the fault information Idea is to resize the cache to avoid faulty blocks during regular operation

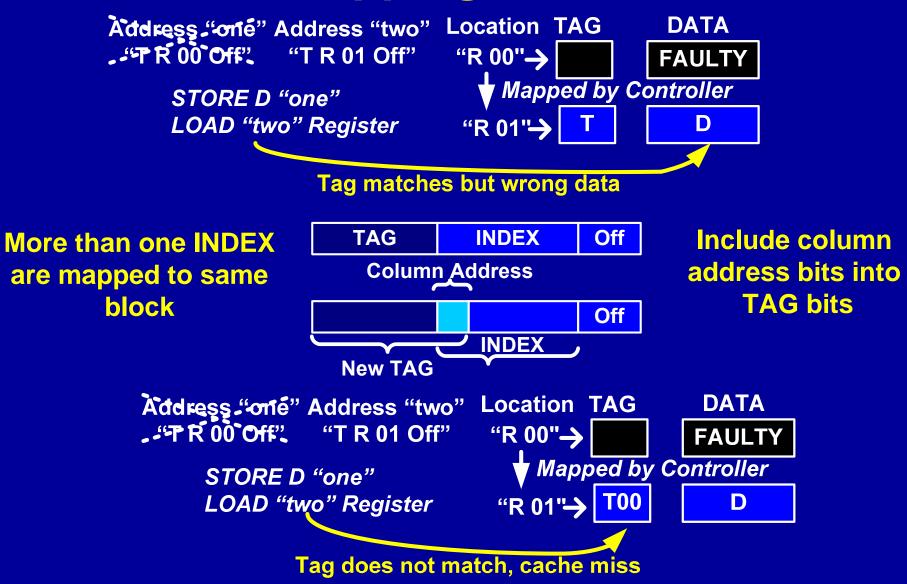

#### **Mapping Issue**

Resizing is transparent to processor → same memory address

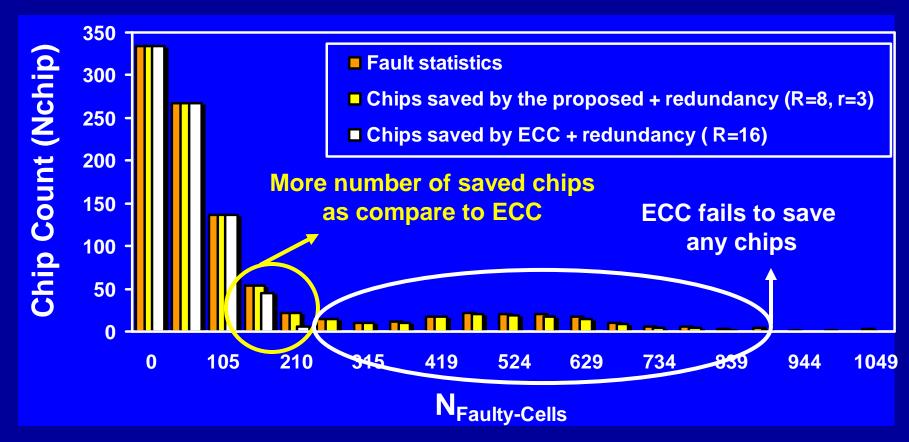

#### **Fault Tolerant Capability**

- Proposed architecture can handle more number of faulty cells than ECC, as high as 890 faulty cells

- Saves more number of chips than ECC for a given N<sub>Faulty-Cells</sub>

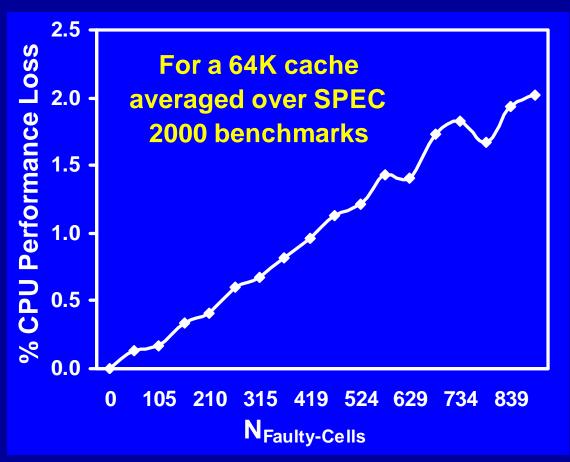

#### **CPU Performance Loss**

- Increase in miss rate due to downsizing of cache

- Average CPU performance loss over all SPEC 2000 benchmarks for a cache with 890 faulty cells is ~ 2%

# Logic: Process Tolerance

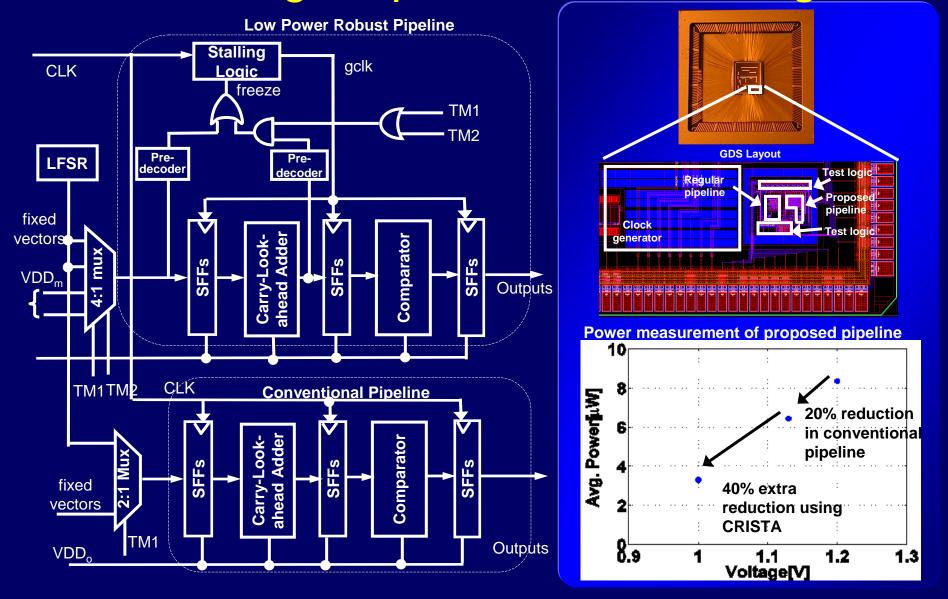

## Logic: A New Paradigm for Low-Voltage, Variation Tolerant Circuit Synthesis Using Critical Path Isolation (CRISTA)

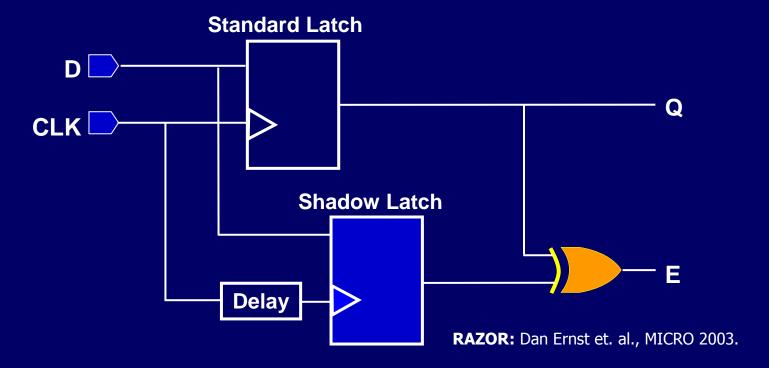

#### Razor Approach

- Post-Silicon technique for dynamic supply scaling and timing error detection/correction

- Error correction overhead is 1% for a 10% error rate

# Vdd Scaling and Process Tolerance: Conventional Solutions

- Low power:

- Reduce the supply voltage

- Error rate increases

- Dual-Vt/dual-VDD assignment

- Number of critical paths increases

- Robustness:

- Increase supply voltage

- Power dissipation increases

- Upsize the gates

- Switching capacitance increases

Low power and robustness: conflicting requirements

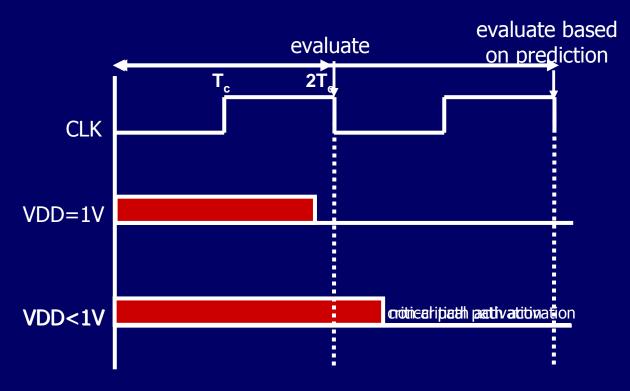

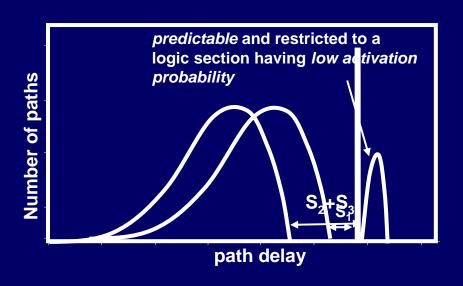

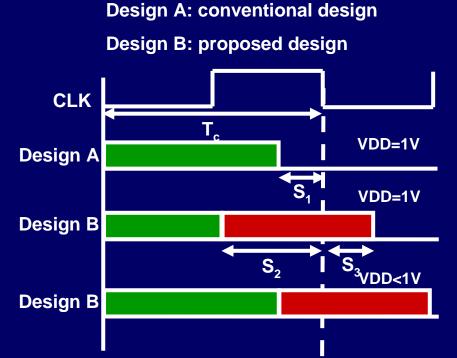

#### **CRISTA:** Basic Idea

- Important points:

- Scale down the supply while making delay failures predictable

- Avoid the failures by adaptive clock stretching

- Ensure that critical paths are activated rarely

#### Design Considerations for CRISTA

- Few predictable critical paths

- Low activation probability of critical paths

- Slack between critical and non-critical paths under variations

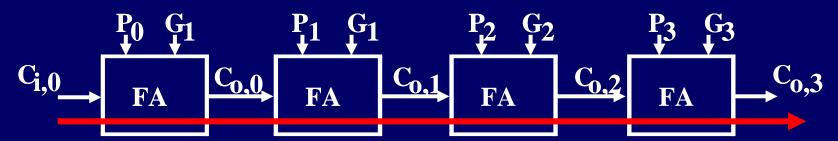

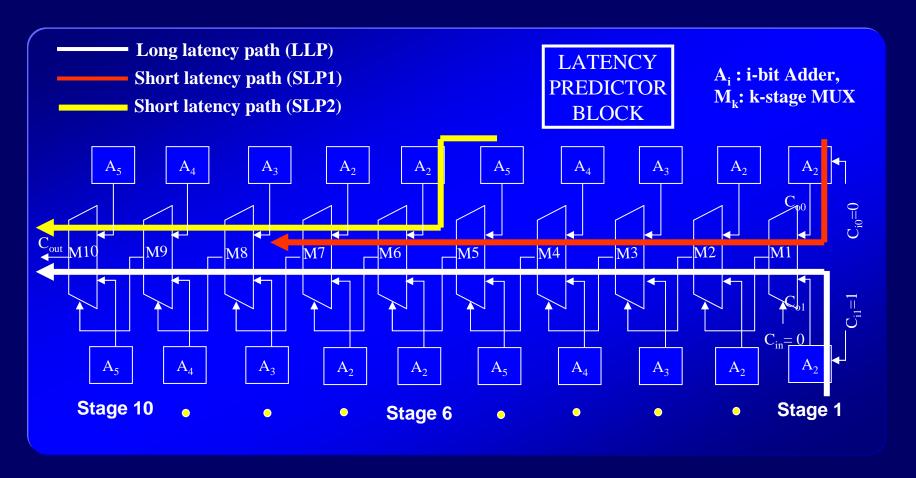

#### Case Study: Adder

- Interesting features:

- Single critical path (activated by P<sub>0</sub>P<sub>1</sub>P<sub>2</sub>P<sub>3</sub>=1 & C<sub>i,0</sub>=1)

- Low activation probability of critical path

$$VDD = 1V$$

,  $TCLK = 260ps$

VDD = 0.8V, TCLK = 260ps

Crit. path delay=260ps longest non-crit. path delay=165ps P = 13uW (1-cycle) Crit. path delay=330ps longest non-crit. path delay=260ps P = 7.4uW (rare 2-cycles, decoder)

44% power saving by reducing voltage and, operating critical path at 2-cycle and other paths at 1-cycle

Can we apply same technique to any random logic?

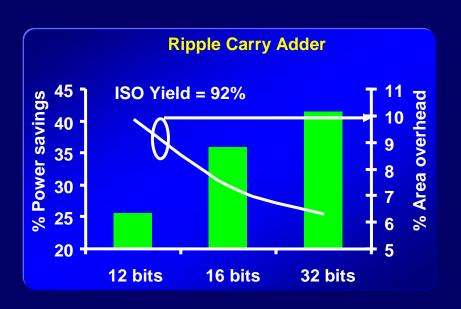

#### Carry Select Adder

~20% power saving with ~6% area overhead

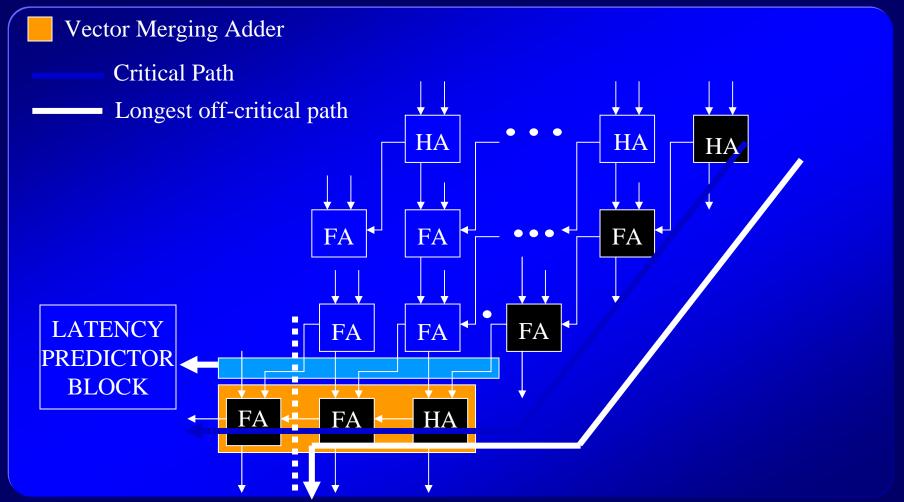

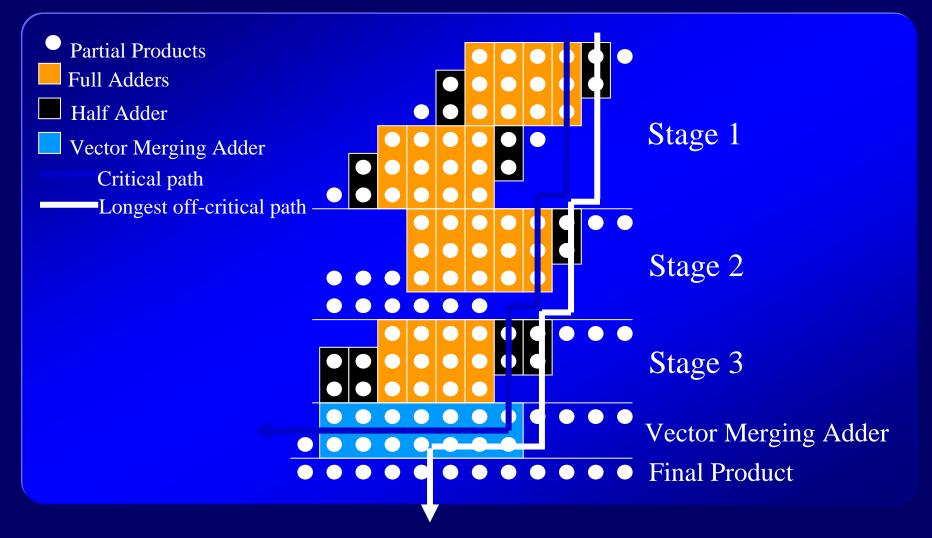

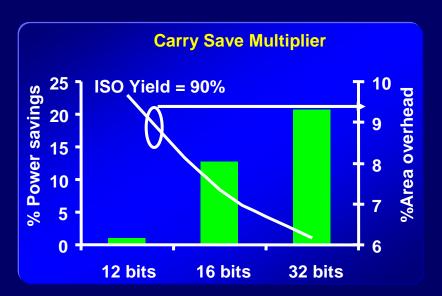

#### **Carry Save Multiplier**

25% power saving with ~5% area overhead

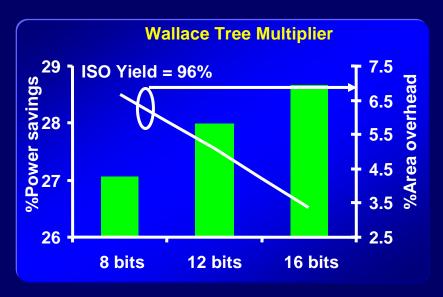

#### Wallace Tree Multiplier

29% power saving with ~4% area overhead

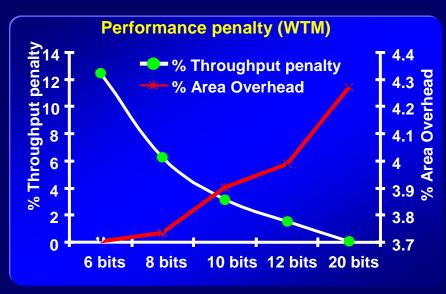

#### Simulation Results

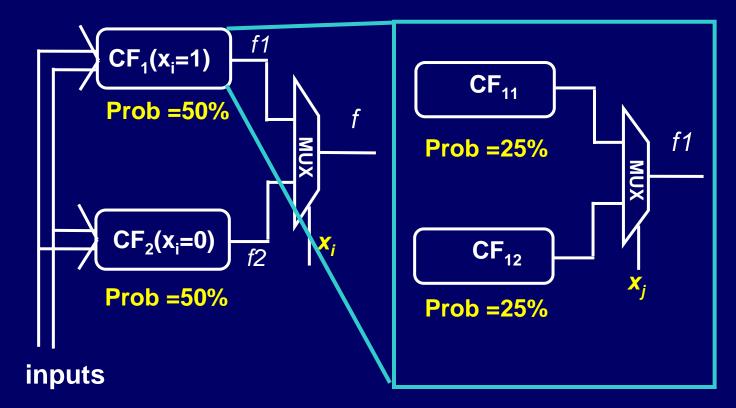

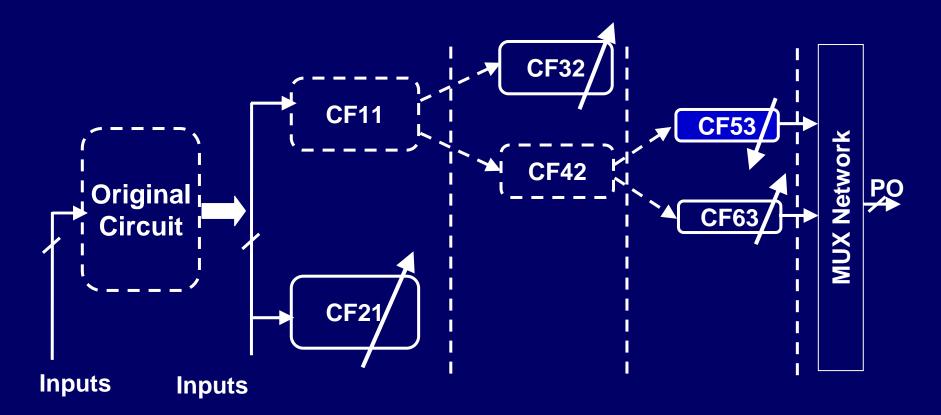

#### Random Logic: Shannon's Expansion

$$f(x_1,...,x_i,...,x_n) = x_i \bullet f(x_1,...,x_i = 1,...,x_n) + x_i' \bullet f(x_1,...,x_i = 0,...,x_n)$$

$$= x_i \bullet CF_1 + x_i' \bullet CF_2$$

$$CF_1 = f(x_1,...,x_i = 1,...,x_n); \quad CF_2 = f(x_1,...,x_i = 0,...,x_n)$$

Activation probability of cofactors can be reduced How to choose *Control Variable*?

#### Further Isolation and Slack Creation by Sizing

- Slack creation strategy

- Lagrangian Relaxation based sizing (B.C. Paul et. al., DAC 2004) is used

- Non-critical paths are selectively made faster

- Critical paths are slightly slowed down

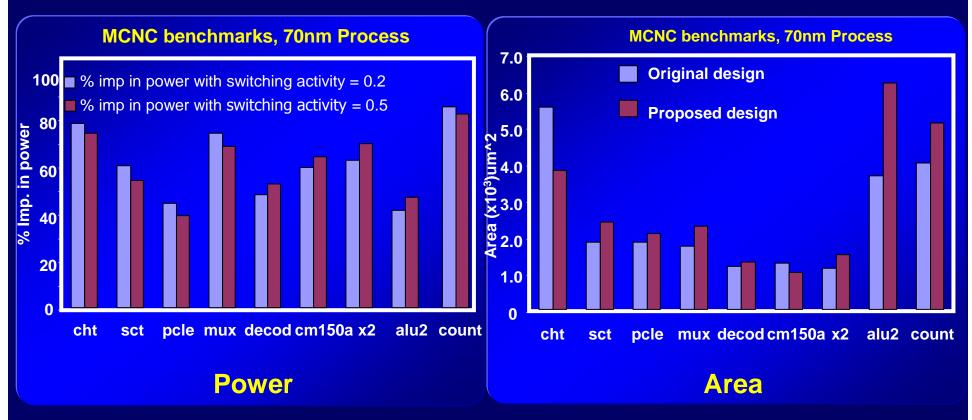

#### Simulation Results

- Average power saving = ~50%

- Average area overhead = 18%

- Avg performance penalty=5.9% (with 4 control variables) for signal prob=0.5

Two-Stage Pipeline with Test Logic

~40% power saving with ~13% performance penalty

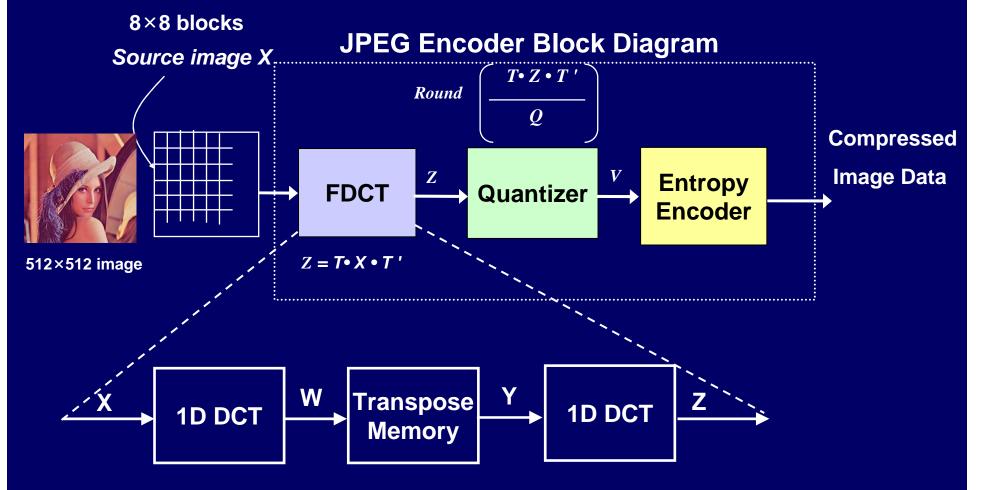

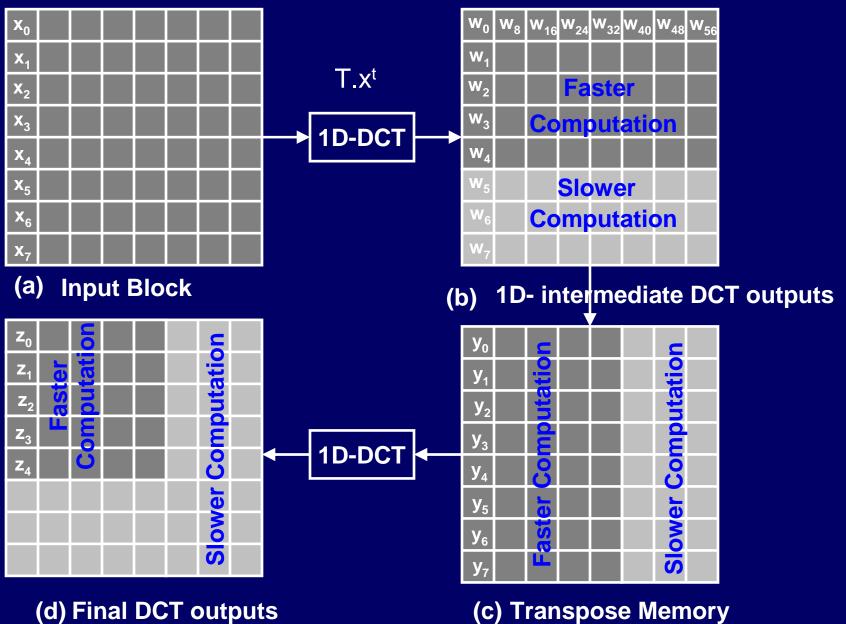

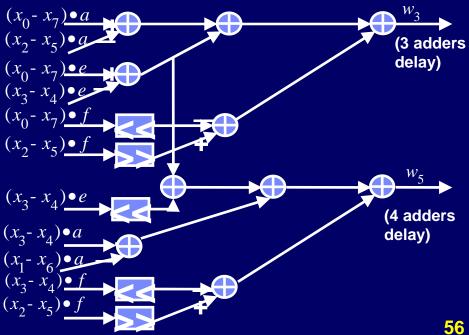

## VDD Scaling, Process Variation, and Quality Trade-off: DCT

#### Basic Idea

- All computations are "not equally important" for determining outputs

- Identify important and unimportant computations based on output "sensitivity"

- Compute important computations with "higher priority"

- Delay errors due to variations/ Vdd scaling "affect only" non-important computations

- "Gradual degradation" in output with voltage scaling and process variations

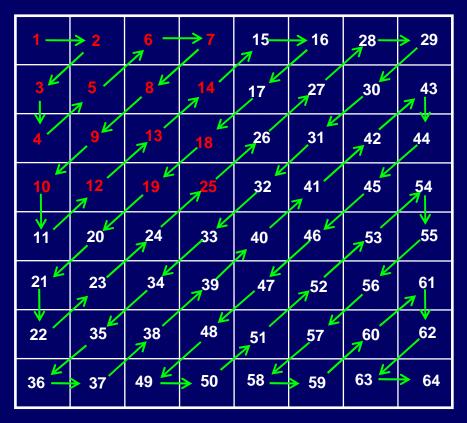

#### **DCT Based Image Compression Process**

- DCT is used in current international image/video coding standards

- JPEG, MPEG, H.261, H.263

#### **Energy Distribution of a 2D-DCT Output**

High energy components (important outputs 75% energy)

Low energy components (less important outputs)

Can important components be computed with higher priority?

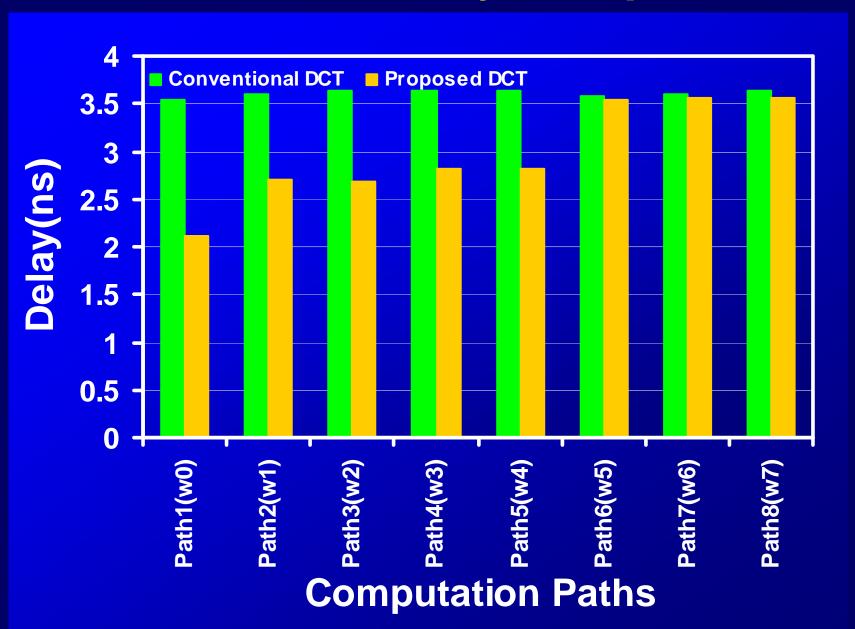

#### **Design Methodology**

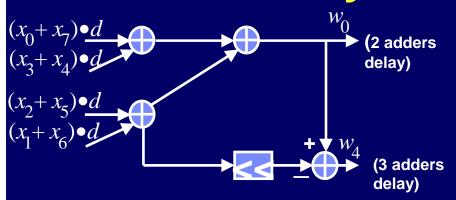

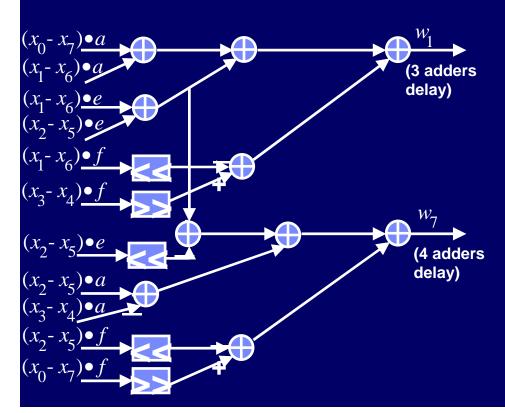

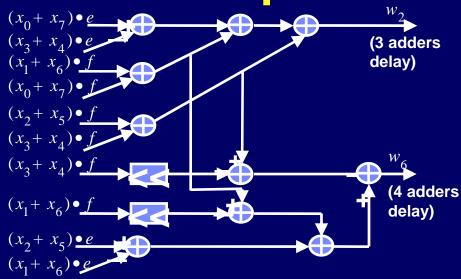

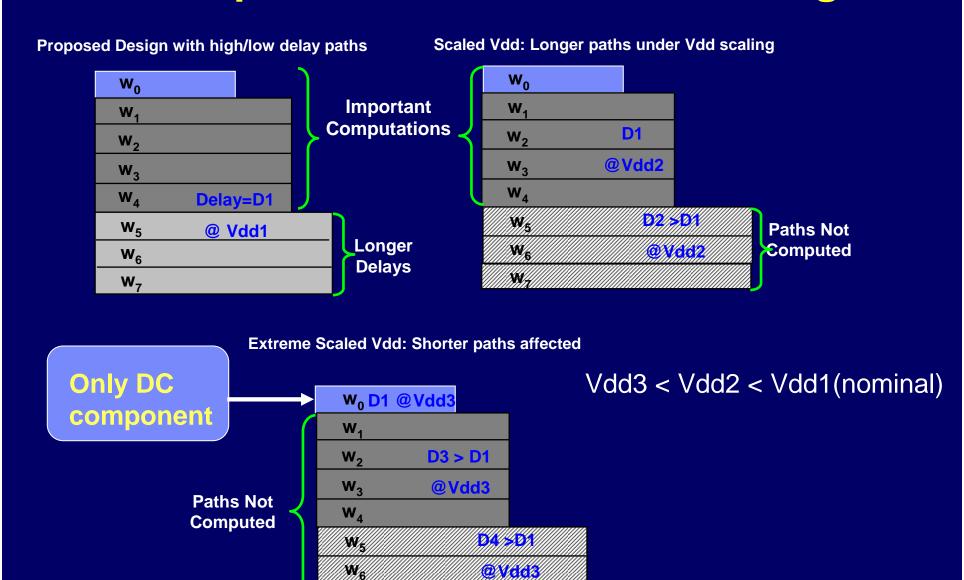

#### Path Delays for 1D-DCT outputs

#### **Proposed DCT under Vdd scaling**

M/

#### **1D-DCT Path Delay Comparisons**

#### **Effect of Vdd Scaling**

**Different Architectures at Nominal Voltage**

|       | Convention al WTM DCT | CSHM DCT<br>(2 alphabet) | Proposed DCT |

|-------|-----------------------|--------------------------|--------------|

| 1.0 V |                       |                          |              |

| 0.9 V | FAILS                 | FAILS                    |              |

| 0.8 V | FAILS                 | FAILS                    |              |

| 1.0V       | CSHM DCT<br>(2 alphabets) | DCT<br>with WTM | Proposed<br>DCT |

|------------|---------------------------|-----------------|-----------------|

| Power (mW) | 25.1                      | 29.8            | 26              |

| Delay (ns) | 3.2                       | 3.64            | 3.57            |

| Area (um²) | 80490                     | 108738          | 90337           |

| PSNR (dB)  | 21.97                     | 33.23           | 33.22           |

#### **Proposed Architecture at Reduced Voltage**

|            | Proposed DCT<br>Vdd=0.9V | Proposed DCT<br>Vdd=0.8V |

|------------|--------------------------|--------------------------|

| Power (mW) | 17.53(41.2%)             | 11.09(62.8%)             |

| PSNR (dB)  | 29                       | 23.41                    |

- Graceful degradation of proposed DCT architecture under Vdd scaling (Vdd can be scaled to 0.75V)

- Conventional architectures <u>fails</u>

## **Temporal Degradation: NBTI**

Kang, Roy, et. al. – TCAD, DAC-07

# Temporal Reliability Issues in CMOS Technology

- HCI Hot Carrier Injection

- NBTI Negative Bias Temperature Instability

- ▶ Increase in V<sub>T</sub> of PMOS with time

- > The dominant reliability factors in scaled tech.

- TDDB, etc.

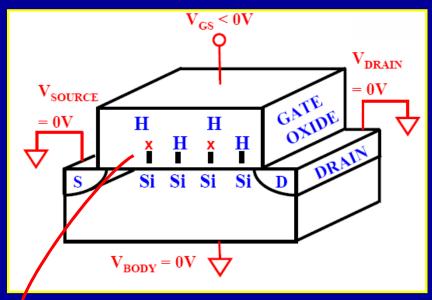

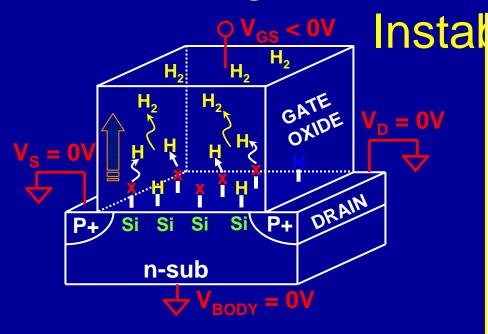

#### **NBTI: Negative Bias Temperature Instability**

Interface trap generation due to Si-H bond breaking

- Interface trap (N<sub>IT</sub>) generation at the channel interface due to the Si-H bond breaking, when negative gate bias is applied

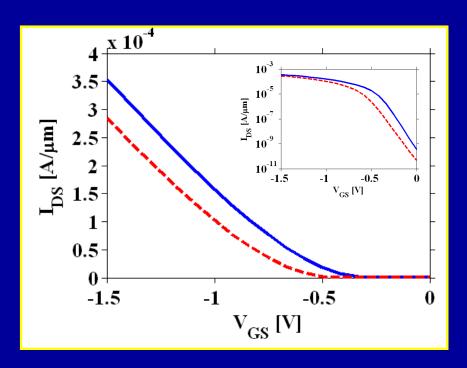

- With time, V<sub>T</sub> increases, subthreshold slope (S) increases, mobility degrades,

- Drive current (I<sub>DS</sub>) reduces and affect the PMOS speed

- Overall reduces the lifetime of PMOS

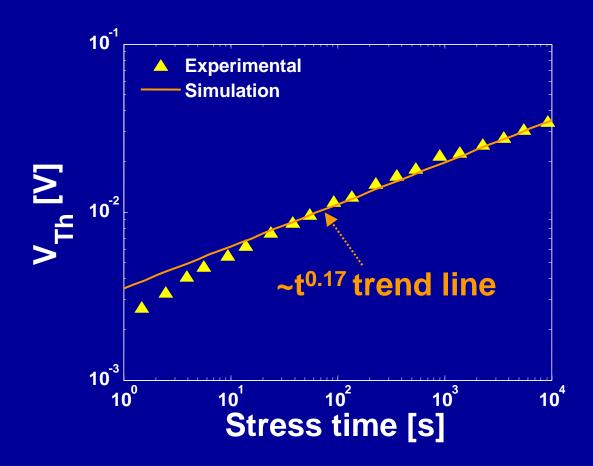

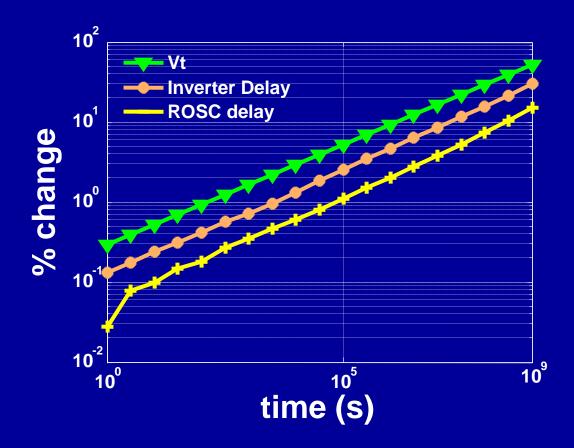

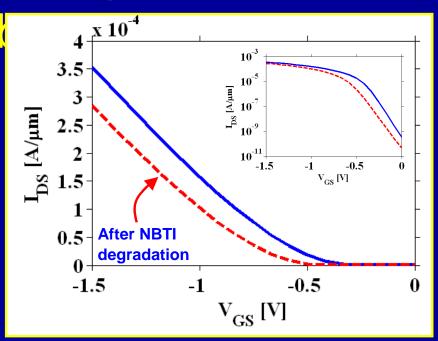

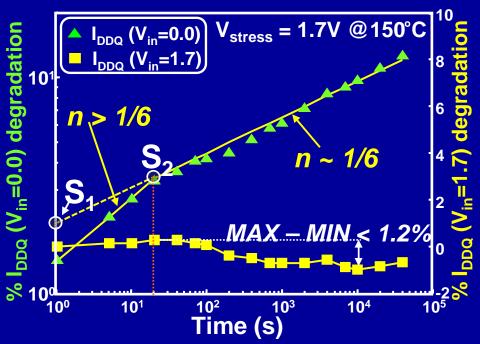

## **NBTI: Experimental Data**

- PMOS V<sub>T</sub> degrades as a power of time due to NBTI

- Fixed exponent of 1/6 matches the simulation data\*

#### Power-law V<sub>T</sub> degradation Model

NBTI degrades in time of exponent 1/6

#### **Mobility degradation factor**

- Mobility degradation due to NBTI is expressed in an additional V<sub>T</sub> shift, noted as m

- Overall temporal V<sub>T</sub> shift model is expressed as,

$$\Delta V_T = (1+m) \frac{q\chi \sqrt{E_{ox}} e^{\left(\frac{E_{ox}}{E_0}\right)} \cdot t^{0.25}}{C_{ox}}$$

# Impact of NBTI on circuit performance

#### **Circuit Performance Degradation**

- Performance (delay) degradation also follows the power trend with same 0.17 exponent

- In CMOS logic, only the rising (L2H) delay's are affected

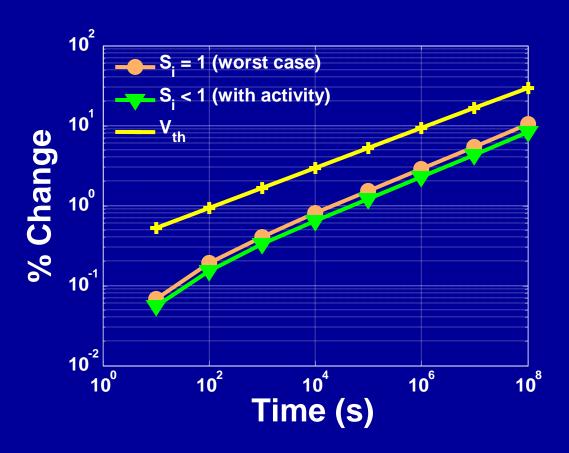

#### Circuit Performance degradation cont.

- Delay degradation in ISCAS c432

- Activity factor (switching activity) does not affect much on the delay degradation

- > In reality, activity factor's are balanced in the normal operations

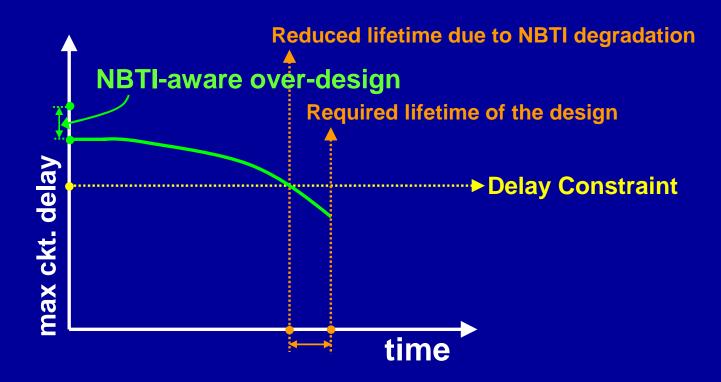

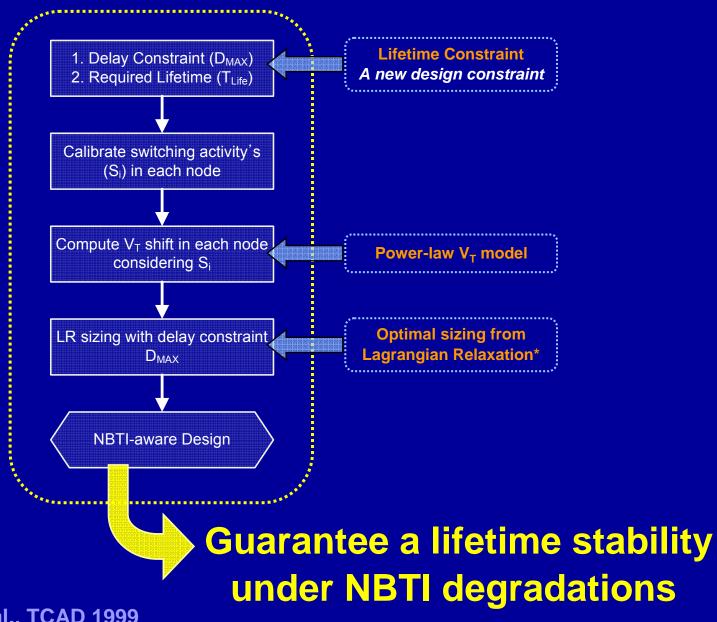

# Design method considering the NBTI degradation

#### **NBTI-aware design method**

- Over-design is required to guarantee a lifetime stability of the circuit

- LR sizing is used to optimize the circuit

- ➢ Size the circuit considering the worst-case V<sub>T</sub> degradation over the lifetime

## LR Sizing considering NBTI

#### Simulation results

#### 1. Delay degradation in ISCAS85 benchmark circuits after 10 years

| Circuit | No. of | Nominal    | % delay degrad. (10 yrs) |                    |

|---------|--------|------------|--------------------------|--------------------|

|         | Trans. | delay (ps) | S <sub>i</sub> = 1       | S <sub>i</sub> < 1 |

| c432    | 590    | 525        | 8.90                     | 7.32               |

| c499    | 1816   | 368        | 9.20                     | 8.06               |

| c1908   | 1582   | 513.5      | 9.18                     | 8.53               |

| c3540   | 3638   | 597.3      | 9.00                     | 7.86               |

| c74181  | 372    | 194.6      | 9.89                     | 8.68               |

| c74182  | 92     | 77.2       | 10.35                    | 9.63               |

| c74283  | 188    | 131.9      | 7.90                     | 6.83               |

| c74L85  | 148    | 115.1      | 9.50                     | 7.60               |

<sup>\*</sup> All benchmarks are synthesized in BPTM 70nm technology

#### Simulation results cont.

#### 2. Area overhead in NBTI-aware sizing

| Circuit | Nominal    |        | % Area overhead    |                    |

|---------|------------|--------|--------------------|--------------------|

|         | delay (ps) |        | S <sub>i</sub> = 1 | S <sub>i</sub> < 1 |

| c432    | 385        | 196.7  | 14.8               | 13.6               |

| c499    | 340        | 581.47 | 7.82               | 6.71               |

| c1908   | 470        | 489.67 | 7.13               | 6.68               |

| c3540   | 500        | 1146.5 | 3.44               | 3.31               |

| c74181  | 180        | 111.1  | 9.45               | 9.0                |

| c74182  | 80         | 31.1   | 11.3               | 11.2               |

| c74283  | 125        | 66.71  | 10.0               | 10.0               |

| c74L85  | 120        | 42.59  | 5.85               | 5.8                |

<sup>\*</sup> All benchmarks are synthesized in BPTM 70nm technology

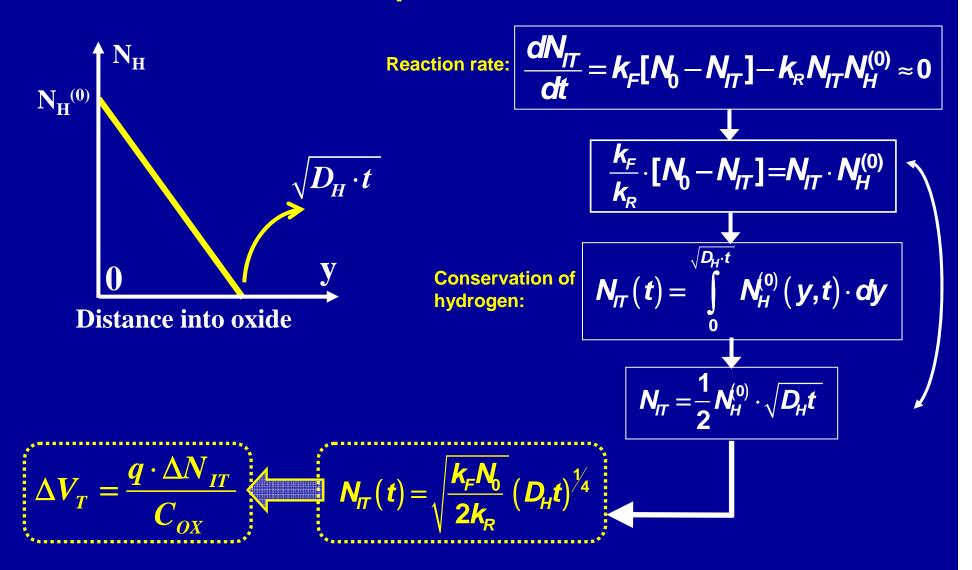

#### Negative Bias Temperature

- PMOS specific Aging Effect

- Generation of (+) traps

- Reaction-Diffusion (RD) model\*

- Time exponent ~ 1/6

$$N_{IT}(t) = \sqrt{\frac{k_F N_0}{2k_R}} \left(D_H t\right)^{\frac{1}{6}}$$

$$\Delta V_T = \frac{q \cdot \Delta N_{IT}}{C_{OX}}$$

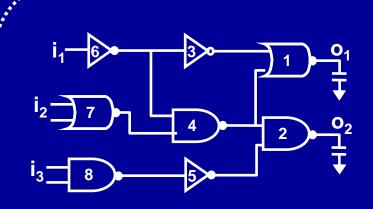

#### **NBTI in Digital Circuits**

#### **Logic Circuits**

- f<sub>MAX</sub> decreases↓

- Timing failure with time

- Static Noise Margin (SNM)↓

- Read & Write Stability

- Parametric Yield↓

Temporal V<sub>Th</sub> increase in PMOS affects critical performance factors of digital VLSI circuits

NBTI: Random Logic Circuits

Delay Degrad. STD cells

| Logic<br>Cell | fanin | Delay (ps) |         | . (0() |

|---------------|-------|------------|---------|--------|

|               |       | t=0        | 3 years | Δ (%)  |

| INV           | 1     | 13.77      | 16.77   | 21.8   |

| NAND          | 2     | 16.86      | 19.88   | 17.9   |

| NAND          | 3     | 19.57      | 22.45   | 14.8   |

| NOR           | 2     | 17.26      | 21.89   | 26.8   |

| NOR           | 3     | 23.80      | 30.19   | 26.9   |

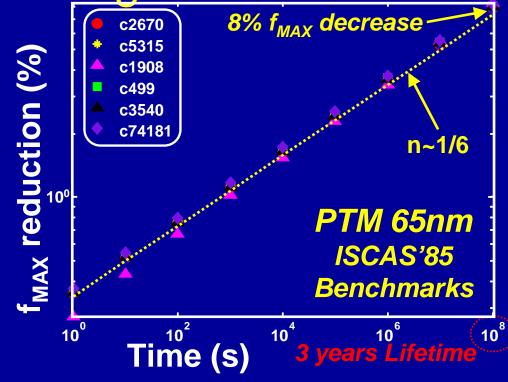

- ISCAS'85 Benchmark Circuits, PTM 65nm

- Gate delay: analytical delay model considering NBTI

- Circuit delay: NBTI-aware Static Timing Analysis (STA)

- Circuit f<sub>MAX</sub> → time exponent n ~ 1/6

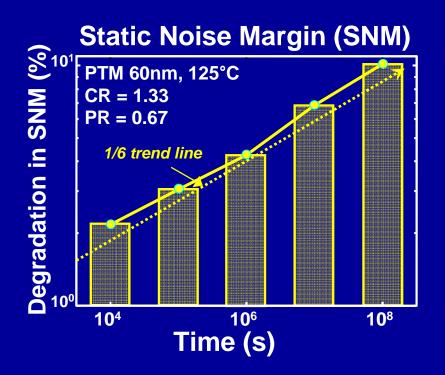

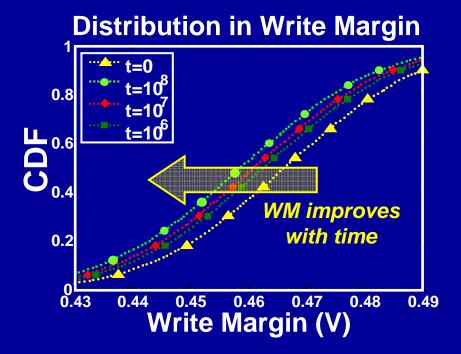

#### **NBTI: 6T SRAM Cell**

- □ SNM degrades by more than 10% in 3 years

- □ % SNM Degradation → time exponent n ~ 1/6

- **WM improves with time under NBTI**

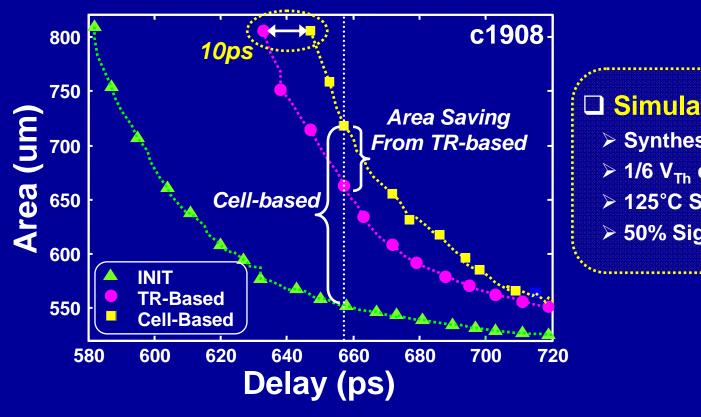

#### Design for Reliability under NBTI

#### □ Simulation Setup

- > Synthesized in PTM 65nm

- > 1/6 V<sub>Th</sub> degradation model

- > 125°C Stress temperature

- > 50% Signal Probability at Pl's

- ☐ Gate Sizing applied to guarantee lifetime functionality of design

- □ 11.7% overhead for Cell-based sizing

- □ 6.13% overhead for TR-based sizing

- > 45% improvement in area overhead

- > Runtime complexity for TR-based sizing is identical to that of Cell-based sizing

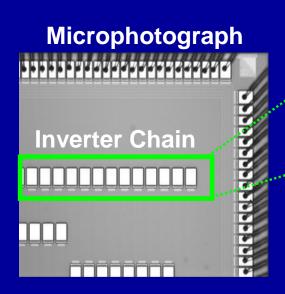

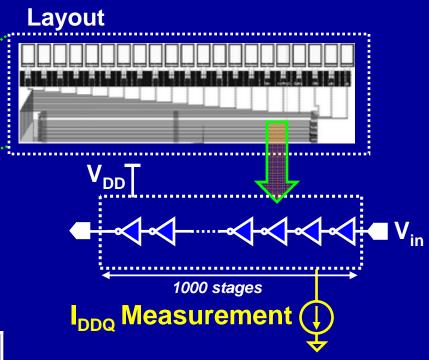

#### I<sub>DDQ</sub> based NBTI Characterization

| Technology | CMOS 130nm           |

|------------|----------------------|

| Die Size   | 20 (mm <sup>2)</sup> |

| I/O Pin    | 209                  |

| $T_{ox}$   | 1.6 (nm)             |

| $V_{DD}$   | 1.2 (V)              |

- Test Circuit Fabricated

- 1000 stage INV chain

- DC Stress signal @V<sub>in</sub>

- I<sub>DDQ</sub> measurement @ GND

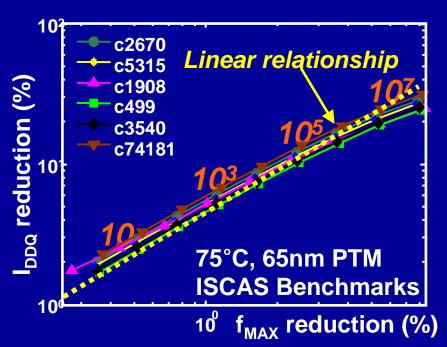

## Correlation between I<sub>DDQ</sub> & f<sub>MAX</sub>

- Clear signature of NBTI

- Correlation between I<sub>DDQ</sub> and f<sub>MAX</sub> can be used to predict circuit performance degradation under NBTI

I<sub>DDQ</sub> degradation → n~1/6 during

$$\begin{split} R_{leak} &= \frac{\Delta I_{leak}(t)}{I_{leak}(0)} \propto t^{1/6} \propto \frac{\Delta f_{MAX}(t)}{f_{MAX}(0)} = R_{freq} \\ R_{freq} &= K \times R_{leak} \quad (K \text{ :constant}) \end{split}$$

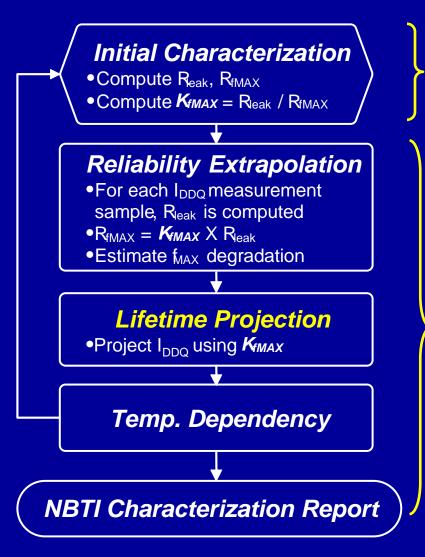

#### I<sub>DDQ</sub> based Characterization Technique

Design phase

# Post-silicon phase

- Circuit-level NBTI Reliability

Characterization

- I<sub>DDQ</sub> test is used

- Expensive f<sub>MAX</sub> testing is avoided (or minimized)

- Accurate circuit level performance degradation can be predicted

- IC specific burn-in to qualify the target produce

- Efficient way of field monitoring: dynamic local signature of produce usage

- Possible usage in other reliability sources: HCI

#### Conclusions

- Process Variation and Process

Tolerance is becoming important

- There is a need to optimize designs considering power/performance/yield