# Deep Sub-micron Test: High Leakage Current and Its Impact on Test; Cross-talk Noise

Kaushik Roy

Electrical & Computer Engineering

Purdue University

### Impact of Leakage on IC Testing?

#### **Our Focus**

- Higher intrinsic leakage challenges current based test techniques

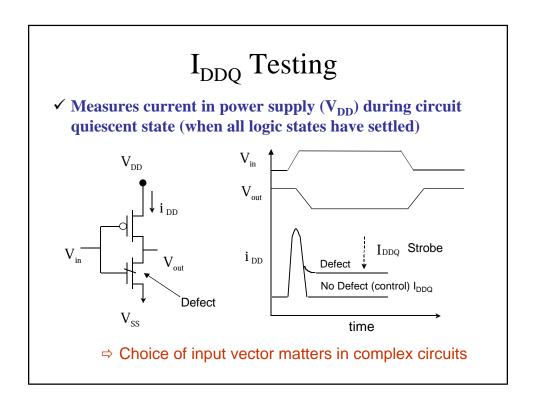

- I<sub>DDQ</sub> test method well established and widely accepted for defects and is necessary

- I<sub>DDO</sub> testability issue sensitivity?

- Novel testing solutions

#### **Problem Statement**

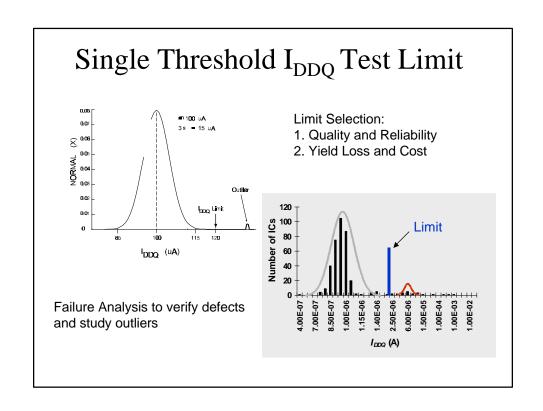

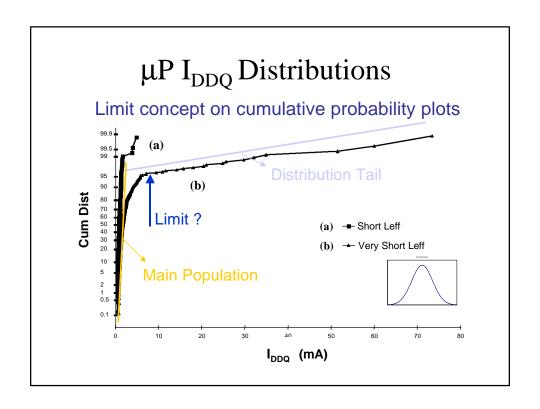

- Can I<sub>DDQ</sub> and current based test methods be effective and survive the prohibitive increase in intrinsic leakage posed by technology scaling?

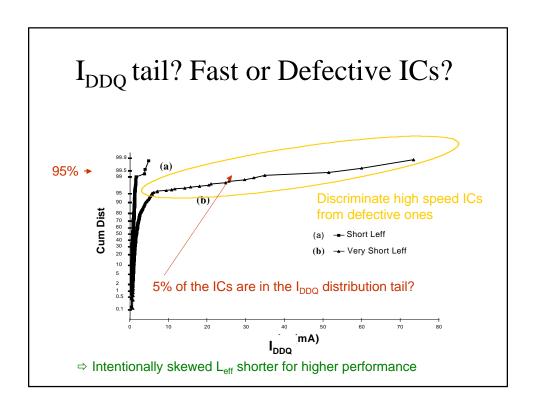

- How do we discriminate high speed leaky ICs from defective ones?

### Gate Oxide Defect & I<sub>DDQ</sub>

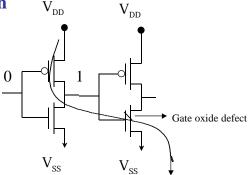

- ✓ I<sub>DDO</sub> most effective in detecting defects

- ✓ Example: NMOS gate oxide defect creating a  $V_{DD}$  to  $V_{SS}$  leakage path  $V_{DD}$   $V_{-1}$

⇒ Circuits become more susceptible to defects with scaling

### State-of-the-art in Current Testing

- Transient Current Testing [1,2]

- Current Signatures and Ratios [3,4]

- Delta I<sub>DDO</sub> [5]

- Divide and conquer techniques [6,7]

- Forcing stacked transistors by input vector selection [8]

- Not sufficient to address the problem

- Our solution not in conflict with above

#### References:

- [1] M. Sachdev, et al., "Defect Detection with Transient Current Testing and its Potential for Deep Submicron ICs," *Int. Test Conf.*, pp. 204-213, Oct. 1999.

- [2] E.I. Cole Jr., et al., "Transient Power Supply Voltage (v<sub>DDt</sub>) Analysis for Detecting IC Defects," *Int. Test Conf.*, pp. 23-31, Nov. 1997.

- [3] A. E. Gattiker et al., "Current Signatures," VLSI Test Symposium, pp. 112-117, 1996.

- [4] P. Maxwell, et al., "Current Ratios: A Self-Scaling Technique for Production IDDQ Testing," Proc. of International Test Conference, pp. 738-746, Oct. 1999.

- [5] C. Thibeault, et al., "Diagnosis Method Based on Delta IDDQ Probabilistic Signatures: Experimental Results," *Int. Test Conf.*, pp. 1019-1026, 1998.

- [6] K. Wallquist, "Achieving IDDQ/ISSQ Production Testing with Quic-Mon," IEEE Design and Test of Computers, Fall 1995.

- [7] W. Maly, et al., "Design of ICs Applying Built-in Current Testing," J. of Electronic Testing: Theory and Applications, pp. 111-120, Dec. 1992.

- [8] Y. Ye, et al., "A New Technique for Standby Leakage Reduction in High-Performance Circuits," *Symp. on VLSI Ckts*, p. 40, June 1998.

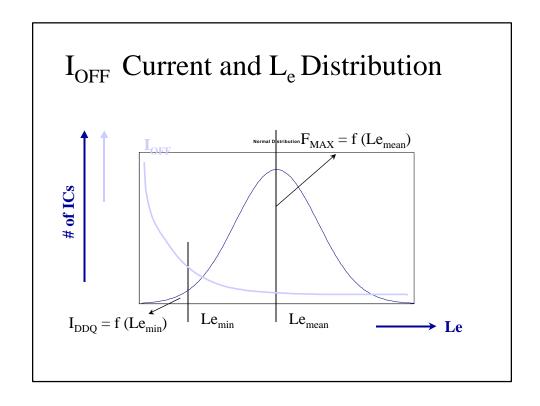

# Parameters Influencing I<sub>OFF</sub>, I<sub>DDO</sub> & Standby Power

- Substrate (Body) Bias

- Temperature

- Lowering Power Supply Voltage

- Combined Effects

### I<sub>OFF</sub> / Leakage Reductions

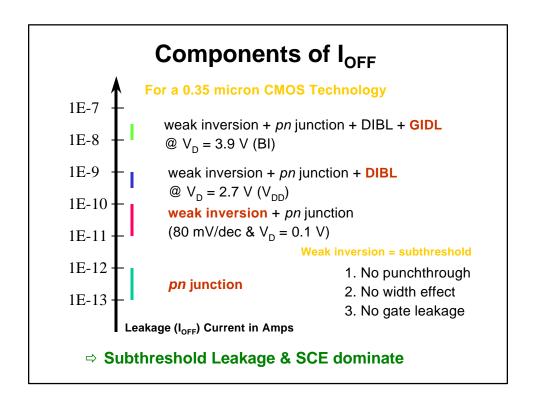

For a 0.35 micron CMOS Technology

- Temperature

- Factor of ~ 350 from room to -50°C

- ullet Substrate backbiasing (RBB)  $V_{BS}$

- Factor of  $\sim 3000$  at  $\sim \mid 2 \mid V$

- Lowered V<sub>DD</sub>

- Factor of  $\sim 10$  from 2.7 V to 1.5 V

- Multiple V<sub>T</sub>

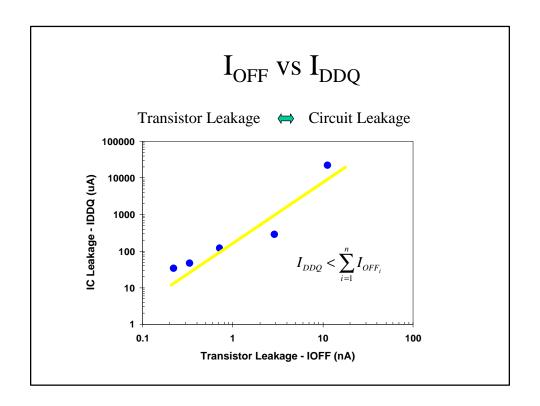

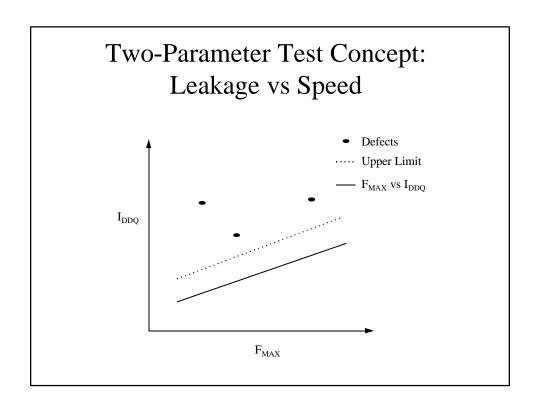

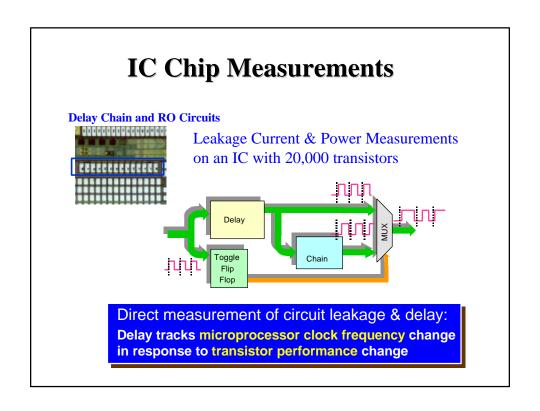

### Two parameter Test Solution

- Scaling

- Functional and Delay Fault Testing

- I<sub>DDQ</sub>

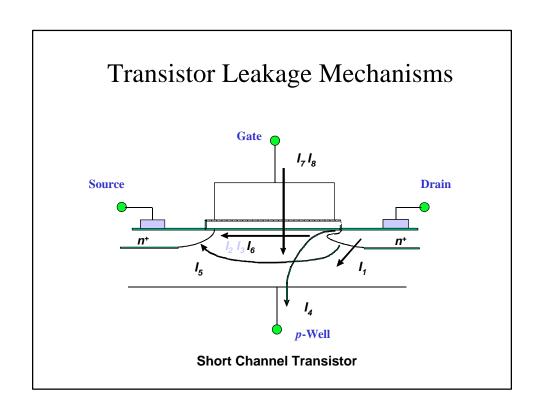

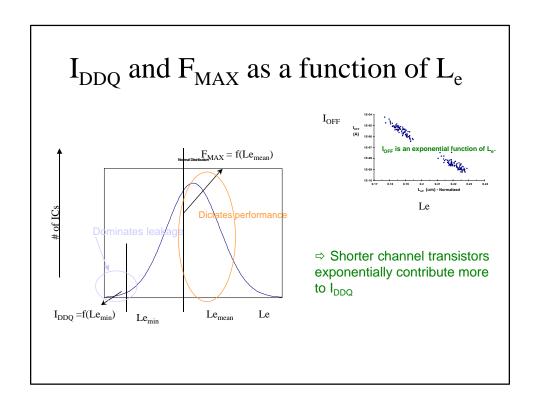

- Components of transistor leakage

- Leakage reduction techniques

- - Two-parameter test solution

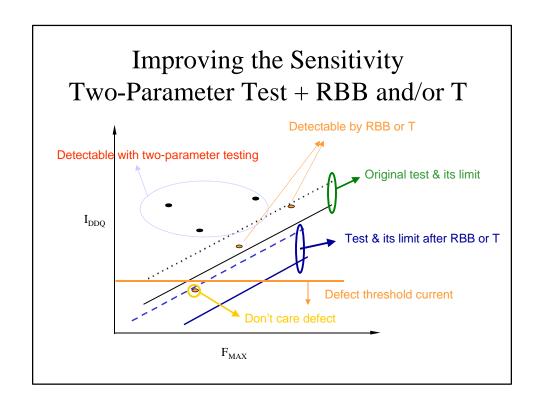

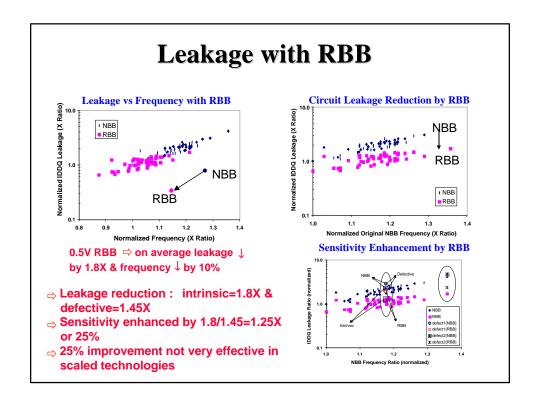

- Sensitivity enhancement by RBB

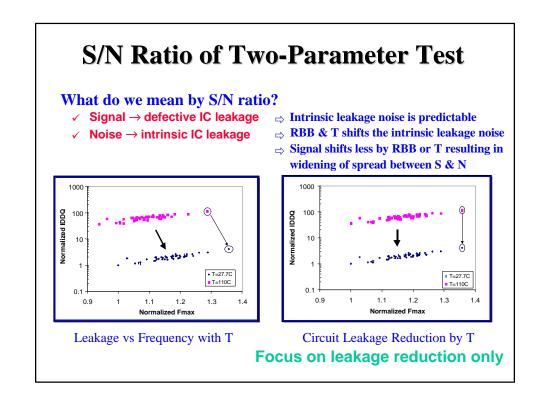

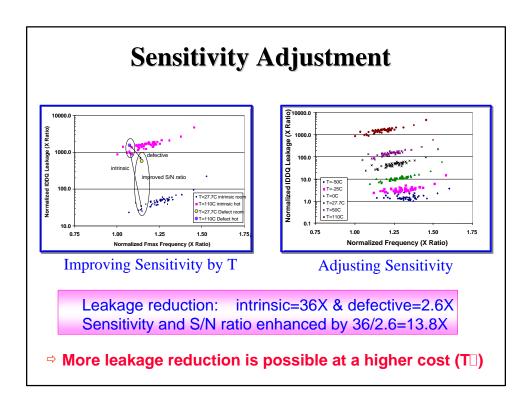

- Sensitivity enhancement by Temperature

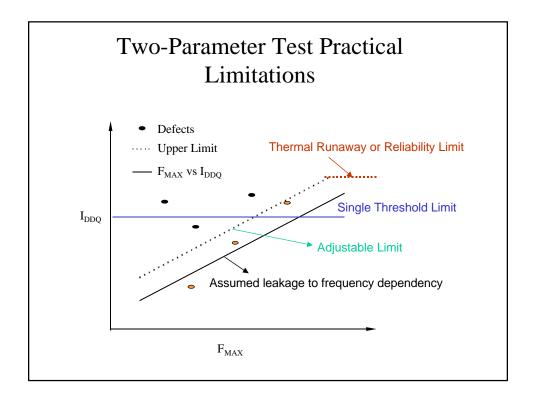

### Two-Parameter Test: Decision Table & Adjustable Limit

| Table 6.1. IC decision matrix for $I_{DDQ}$ |                             |                |

|---------------------------------------------|-----------------------------|----------------|

| and F <sub>MAX</sub> testing.               |                             |                |

| $I_{DDQ}$                                   | $\mathbf{F}_{\mathbf{MAX}}$ | Decision on IC |

| Н                                           | Н                           | Good - Fast    |

| Н                                           | L                           | Defect         |

| L                                           | Н                           | Unlikely       |

| L                                           | L                           | Good - Slow    |

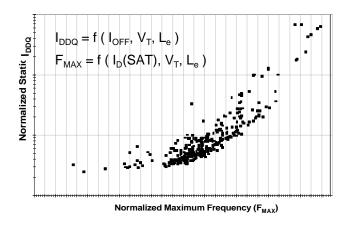

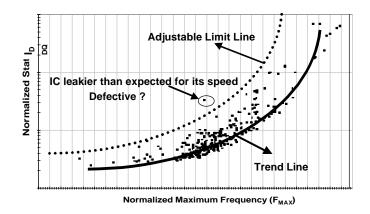

## $\mu P$ Circuit $I_{DDQ}$ vs $F_{MAX}$

- ⇒ Empirical relationship derived from existing test methods

- ⇒ Data include die-to-die parameter variation

### Adjustable Limit for $I_{DDQ}$ vs $F_{MAX}$

⇒ Limit may be established by currently available statistical methods

# Addressing issues raised by the problem statement

- High intrinsic leakage

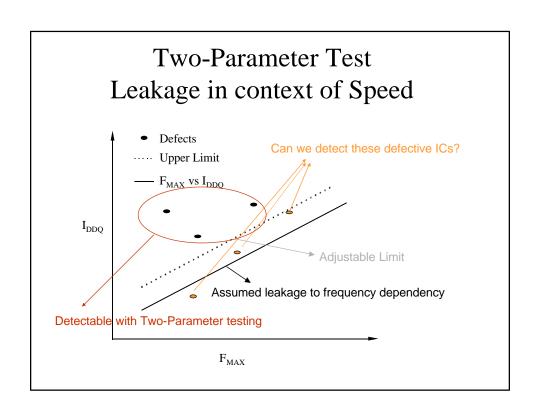

- Our solution places  $I_{DDQ}$  in context of  $F_{MAX}$

- ${\color{blue} \bullet}$  High  $I_{DDQ}$  leakage not an issue in itself

- High leakage at high speed is OK

- lacksquare  $I_{DDQ}$  effectiveness and sensitivity

- $\ \ \$  Two-parameter test extends  $I_{DDQ}$  effectiveness

- More on improving sensitivity by RBB

- Discriminates high speed leaky ICs from defective ones

# How does our solution compare to state-of-the-art in $I_{DDO}$ testing?

- No extra cost, no new hardware or instrumentation, uses established tests

- It complements the existing methods such as lowering V<sub>DD</sub>, lowering temperature, and increasing V<sub>T</sub> by RBB or multiple V<sub>T</sub>

### **Issues in DSM Era**

- Signal integrity

- DSM defects

- capacitive and inductive coupling

- voltage drop charge share

- power supply noise

- functional/delay faults

- New DSM fault models should support

- test generation

- self-test capability

- IDDQ testabilty

- Diagnosis

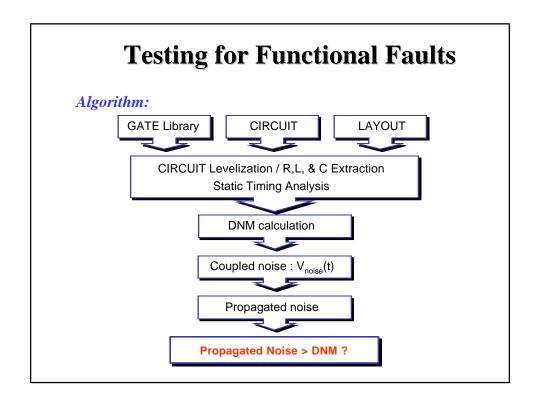

# High Speed Circuit Testing for Cross-Talk Defects

- Crosstalk -- One of the major noise injection mechanisms in DSM circuits

- Determine nodes that are susceptible to these faults in high-speed circuits.

- Helps to generate the test pattern.

- Provide guidelines to design noise tolerant circuits

#### **Noise Sources in DSM Circuits**

- Cross-talk coupling

- Power supply noise

- Charge redistribution

### Why Noise Modeling?

- To determine the circuit immunity to noise.

- Helps in designing noise tolerant circuit.

- Reduces the number of nodes to be tested.

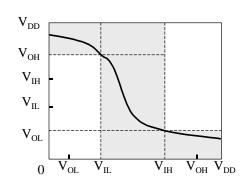

### Static Noise Margin

$$\mathbf{NM_{L}} = |\mathbf{V_{IL}} - \mathbf{V_{OL}}|$$

$\mathbf{NM_{H}} = |\mathbf{V_{OH}} - \mathbf{V_{IH}}|$

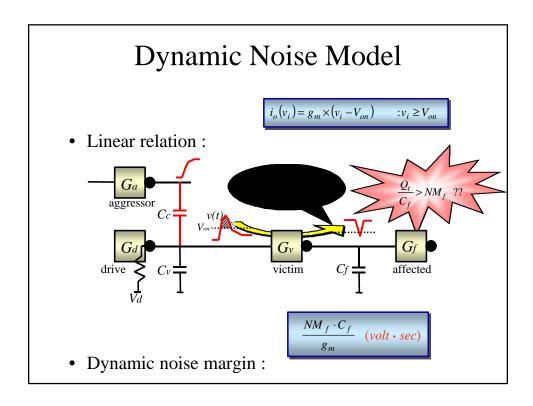

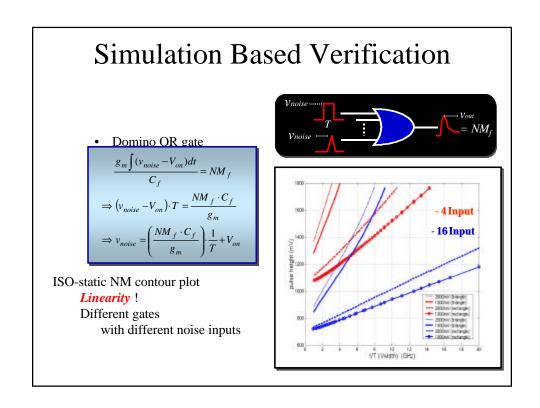

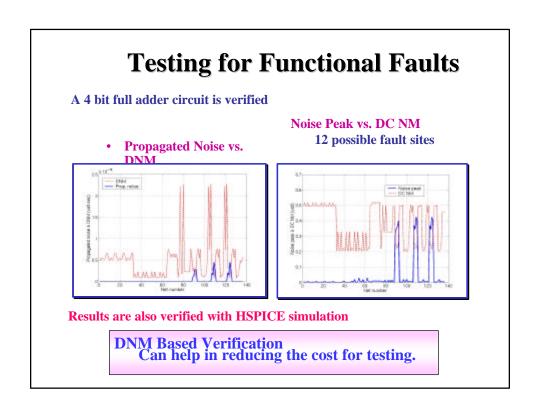

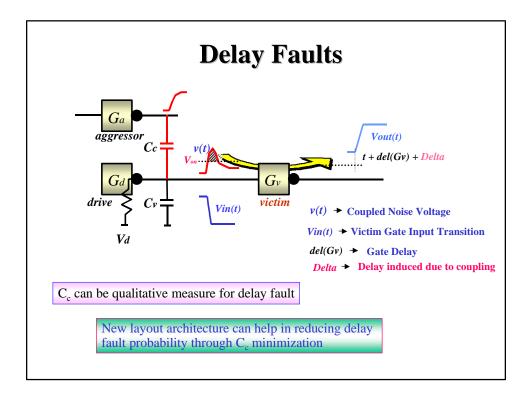

### Requirement of New Technique

New technique for testing of high-speed DSM monotonic logic circuits

**Dynamic Noise Modeling**

Static NM - not sufficient

Dynamic NM - new metric to check functional violation

Detection of functional/delay faults in a circuit

Estimate propagated noise at a victim node

Comparison with dynamic noise margin

Analysis of noise immunities of high speed circuits

# High Speed Circuit Testing for Cross-Talk Defects

- Crosstalk -- One of the major noise injection mechanisms in DSM circuits

- Determine nodes that are susceptible to these faults in high-speed circuits.

- Helps to generate the test pattern.

- Provide guidelines to design noise tolerant circuits

#### **Conclusions**

- Two-Parameter test with speed-adjusted leakage limit has a better S/N ratio

- It discriminates high speed leaky ICs from defective ones

- Reverse Body Bias (RBB) enhances the test sensitivity (S/N ratio) modestly

- Temperature improves the sensitivity by more than an order of magnitude (14X)

### Conclusions

- Cross-talks faults are becoming increasing important for high-speed DSM circuits

- There is a need for good test and verification methodology for cross-talk defects