# Leakage Tolerant Circuits, Sub-threshold Logic

Kaushik Roy

Electrical & Computer Engineering

Purdue University

## Outline

- High Performance and Low-Power Circuits

- Leakage control (CAD and circuit techniques)

- Stacked CMOS with Gated-Vdd (Application: DRIcache)

- Multiple VT

- Dynamic VT

- Circuit techniques:

- MTCMOS, VTCMOS, DTMOS, SCCMOS, etc.

- SOI implementation

- Ultra low voltage digital sub-threshold logic

- Medical applications, bursty versus non-bursty mode

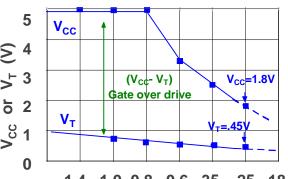

### Constant Voltage vs Field Scaling

- Recently: constant e-field scaling, aka voltage scaling

- $V_{CC} \rightarrow 1V$

- V<sub>CC</sub> & modest V<sub>T</sub> scaling

- Loss in gate overdrive (V<sub>CC</sub>-V<sub>T</sub>)

1.4 1.0 0.8 0.6 .35 .25 .18 Technology Generation (μm)

$\ \square$  Voltage scaling is good for controlling IC's active power, but it requires aggressive  $V_T$  scaling for high performance  $\ _3$

## Delay

$$\boldsymbol{t}_{d} = \frac{C_{L}V_{DD}}{I_{D}}$$

$$\boldsymbol{t}_{d} = \frac{C_{L}}{(\frac{W}{2L})\boldsymbol{m}C_{ax}V_{DD}(1-\frac{V_{T}}{V_{DD}})^{2}}$$

$$\boldsymbol{t}_{d} = \frac{C_{L}}{WC_{ax}\boldsymbol{u}_{SAT}(1-\frac{V_{T}}{V_{DD}})}$$

Short Channel MOSFET

$$t = \frac{CL^{0.5}T_{ox}^{0.5}}{V_{DD}^{0.3}(0.9 - V_{DD}^{1.3})^{1.3}} (\frac{1}{W_n} + \frac{2.2}{W_p})$$

[1]

[1] C. Hu, "Low Power Design Methodologies," Kluwer Academic Publishers, p. 25.

Performance significantly degrades when  $V_{\text{DD}}$  approaches  $3V_{\text{T}}$ .

ļ

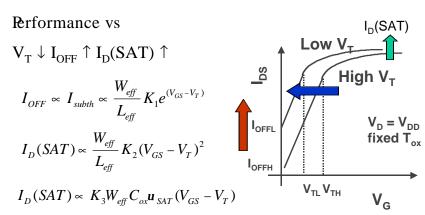

## V<sub>T</sub> Scaling: V<sub>T</sub> and I<sub>OFF</sub> Trade-off

$\Rightarrow$  As  $V_T$  decreases, sub-threshold leakage increases

⇒ is a barrier to voltage scaling

5

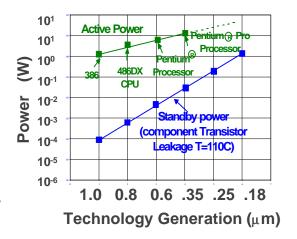

## **Barriers to Voltage Scaling**

- Leakage power

- Short-channel effects

- Soft error

- Special circuit functionality

6

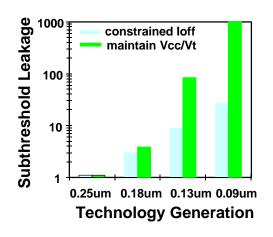

## Why Excessive Leakage an Issue?

- Leakage component to active power becomes significant % of total power

- Approaching ~10% in 0.18 μm technology

- Acceptable limit less than ~10%, implies serious challenge in  $V_{\rm T}$  scaling!

7

## Low-Vdd Low-Vt Design

- Stacked CMOS

- Dual-threshold CMOS

- Dynamic-threshold CMOS

Leakage control techniques

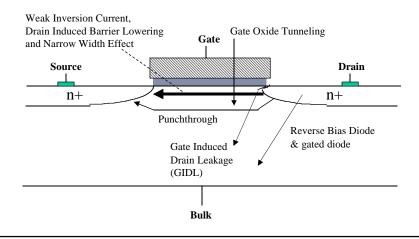

# Sources of Leakage

• From Keshavarzi, Roy, & Hawkins (ITC 1997)

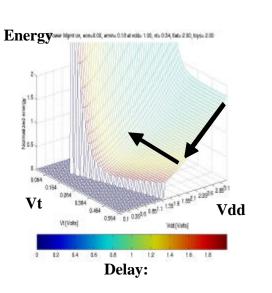

## Motivation

- Reduce Vdd

- Switching energy  $\alpha Vdd^2$

- Increase delay

#### Reduce Vt

- Decrease delay

- $\begin{array}{ccc} \ Leakage & energy \\ \alpha \ e^{(-Vt)} \end{array}$

- Leakage Control permits

- lower voltage

- lower Vt

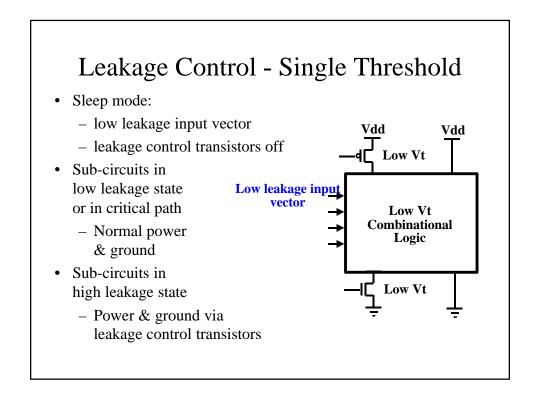

## Leakage Control

- Needed most when circuit is idle

- inputs latched & clocking removed

- supply voltage is still applied

- Can exploit input dependence

- turn off stacks of transistors

- intrinsic self-reverse biasing

- Multiple V, useful

- High V<sub>th</sub>: suppress sub-threshold leakage

- Low V<sub>th</sub>: achieve high performance

## Leakage Control using Self Reverse Bias

- Subthreshold current dominant in sub-µ

- this is the component we concentrate on

- Drain induced barrier lowering (DIBL) and body effect modeled as V<sub>t</sub> shift

- Gate induced drain leakage (GIDL) and gate oxide tunneling may be problem in future

- · Subthreshold current model based on BSIM

- body effect linear for small V<sub>S</sub>

$$I \text{ subth } = A \times e^{\frac{-1}{h u_T} (V_G - V_S - V_{TH \ 0} - g'V_S + h V_{DS})} \times \begin{pmatrix} \frac{-V_{DS}}{u_T} \\ 1 - e \end{pmatrix}$$

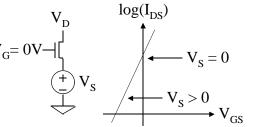

## Self-reverse bias

- Primary effect:

- $-\ V_{GS}\!<\!0$

- move down subthreshold slope

- Secondary effects:

- Drain InducedBarrier Lowering

- Body effect

$$V_{DS} \downarrow \Rightarrow V_{T} \uparrow$$

$$V_{S} \uparrow \Rightarrow V_{T} \uparrow$$

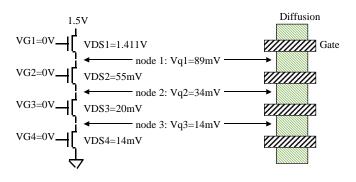

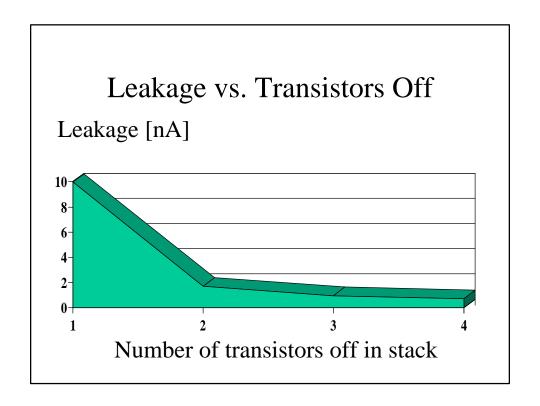

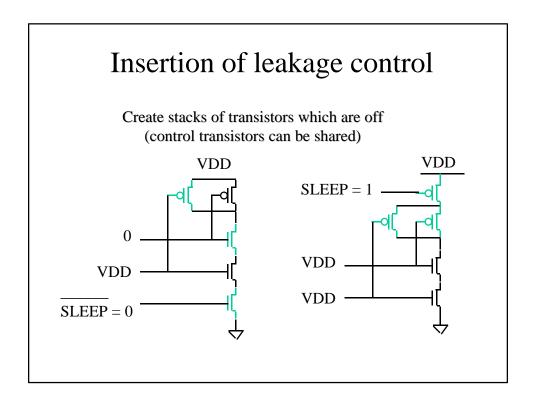

# "Stacking Effect"

ullet Intrinsic self-reverse biasing of  $V_{GS}$  in stack

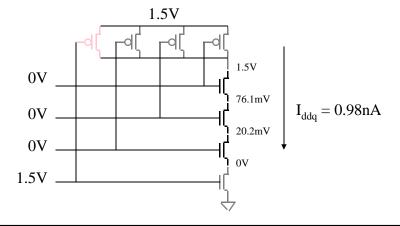

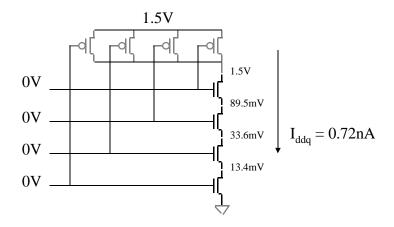

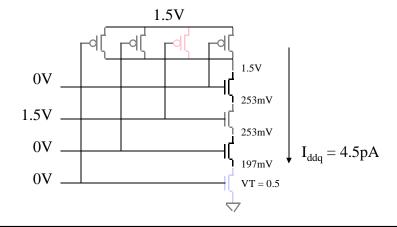

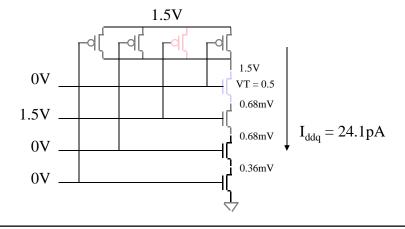

• Consider 4 input NAND  $(V_{DD} = 1.5V, V_T = 0.25V)$

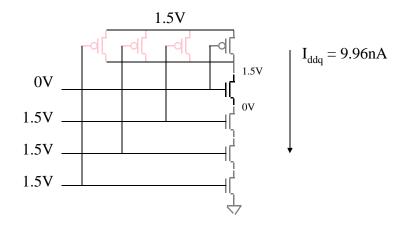

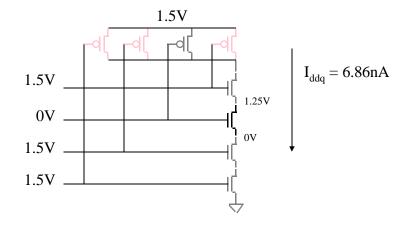

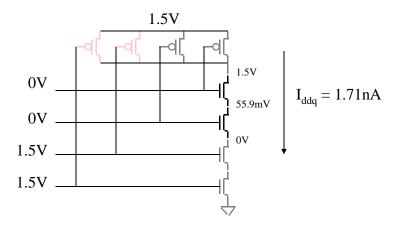

# Input dependence of leakage

• Consider 4 input NAND  $(V_{DD} = 1.5V, V_T = 0.25V)$

# Input dependence of leakage

• Consider 4 input NAND  $(V_{DD} = 1.5V, V_T = 0.25V)$

# Input dependence of leakage

## Model of stacking

- In a simple transistor stack

- ignore transistors which are ON

- calculate V<sub>DS</sub> of each transistor

- use  $I_{\text{subth}}$  equation to calculate leakage

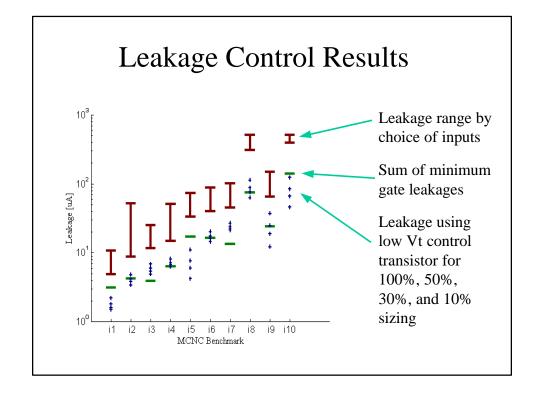

## Selection of Standby Mode Inputs

- At gate level

- evaluate all possible inputs

- for each input vector

- replace ON transistors by shorts

- decompose remaining circuit into disjoint leakage paths

- apply stack leakage model to each path

- For more complex circuits

- build look-up table for each sub-circuit

- use ATPG or GA approach to select minimum leakage input vectors

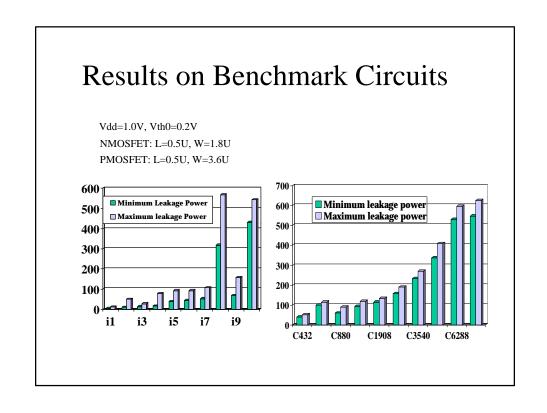

# Results

| Circuit & Input vector | Model<br>Iddq<br>[nA] | HSPICE<br>Iddq<br>[nA] | Comments |

|------------------------|-----------------------|------------------------|----------|

| 4 input NAND           |                       |                        |          |

| ABCD=0000              | 0.72                  | 0.60                   | Best     |

| ABCD=1111              | 23.2                  | 24.1                   | Worst    |

| 3 input NOR            |                       |                        |          |

| ABC=111                | 0.13                  | 0.13                   | Best     |

| ABC=000                | 29.9                  | 29.5                   | Worst    |

| Full Adder             |                       |                        |          |

| A,B,Ci=111             | 7.5                   | 7.8                    | Best     |

| A,B,Ci=001             | 56.0                  | 62.3                   | Worst    |

| 4 bit ripple Add       |                       |                        |          |

| A=B=0000, Ci=0         | 102.6                 | 91.3                   | Best     |

| A=B=1111, Ci=1         | 102.6                 | 94.0                   | Best     |

| A=B=0101, Ci=1         | 258.9                 | 282.9                  | Worst    |

# Results

| Circuit & Input vector    | Model<br>Iddq<br>[nA] | HSPICE<br>Iddq<br>[nA] | Comments          |

|---------------------------|-----------------------|------------------------|-------------------|

| 8 Bit Carry Select        |                       |                        | Uses 4 bit stages |

| A=B=11111111,Ci=1         | 259.0                 | 246.2                  | Best              |

| A=B=01010101,Ci=1         | 690.4                 | 759.6                  | Worst             |

| 4 Bit Manchester Carry Ch | ain                   |                        | Dynamic           |

| All Gi, Pi=1, CLK=1       | 16.8                  | 13.5                   | Best              |

| All Gi, Pi=0, CLK=0       | 15.6                  | 15.9                   | Best              |

| All Gi, Pi=1, CLK=0       | 49.7                  | 55.3                   | Worst             |

| 4 Bit MCC based Adder     |                       |                        |                   |

| CLK=1, others=1           | 154.4                 | 126.6                  | Best              |

| CLK=0, others=0           | 144.4                 | 134.4                  | Best              |

| CLK=0, others=1           | 198.8                 | 190.4                  | Worst             |

## Application: ICALP

- Integrated Circuit/Architecture Approach to Low Power application of trans. stacking

- Leakage power (DRI cache) using transistor stacking (gated-Vdd) and simple hardware monitors

- Dynamic power (L1 & L2 caches)

## ICALP: An Integrated Approach

- Use both circuit & architecture techniques

- aggressive low power circuit techniques

- architecture techniques to configure hardware

- Customize hardware to fit app demand

- e.g., caches, functional units, etc.

- simple hardware monitors

- compiler estimates

- Use circuit to reconfigure hardware

## **ICALP** Goals

- Minimize both leakage and dynamic power

- Redefine architecture from power perspective

- both architectural & compiler techniques

- propose & evaluate power-aware systems

- e.g., our design for a power-aware I-Cache

- Develop the first integrated evaluator

- cycle-driven performance estimator

- accurate power estimators

## Power Management Trigger

- ICALP ISA

- augment ISA with power mgt instructions

- Compiler + ICALP ISA

- e.g., loop size => required I-cache size

- e.g., estimate ILP => required issue width

- Simple hardware monitors

- e.g., monitor miss rate and compare to threshold

## ICALP I-Cache: An Example

- RAM cells large fraction of #transistors

- Potentially large fraction of leakage

- Illustrate usage of Gated-Vdd

- Integrate circuit/architecture schemes

## **DRI-Cache:** Overview

Dynamically Resizable I-Cache (DRI-Cache)

- Monitor dynamic miss rate

- Upsize if miss rate > threshold

- Downsize if miss rate < threshold

- Turn-off power to unused cache blocks

using Gated-Vdd

- Simple hardware implementation

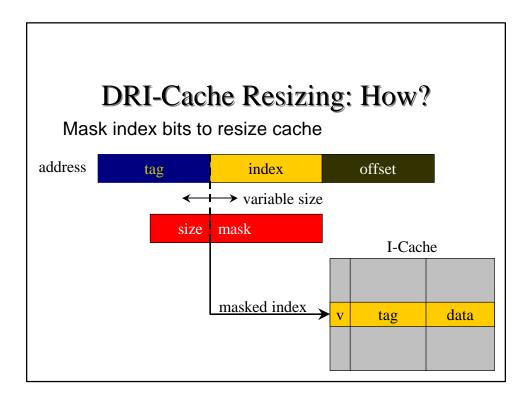

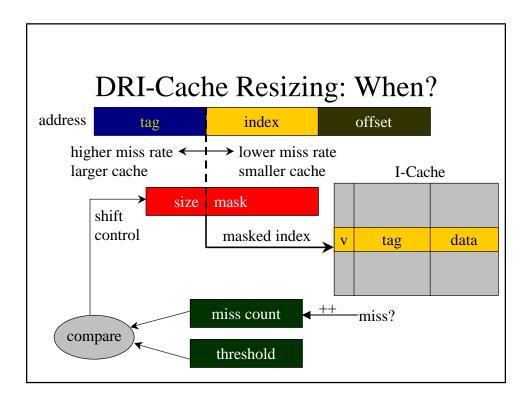

## DRI-Cache Resizing: When?

#### Monitor miss rate for an interval

• Hardware register tracks miss rate

#### At end of interval

- Compare with threshold

- Shift size mask right if lower miss rate

- Shift size mask left if higher miss rate

## DRI-Cache: Architectural Issues

Resizing may cause aliasing

As many tag bits as minimum size

- Larger tag RAM

- Slower tag compares

Size mask in address path

• May affect access time

Extending to D-Cache has problems

• Dirty data needs to be written back

# DRI-Cache: Layout Issues

Extra transistor for Vdd or Gnd

- Less than 3% area increase

- Amortize over one/many cache blocks

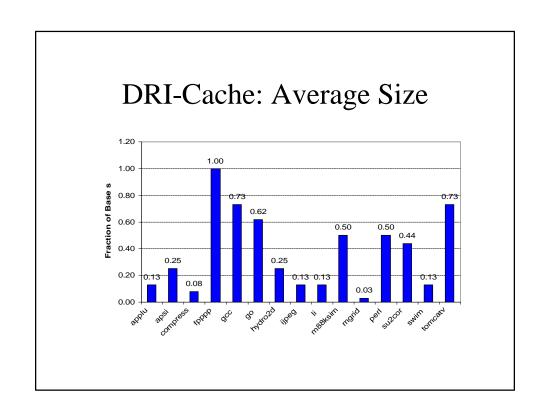

## DRI-Cache: Preliminary Results

#### Simulation Parameters

- Simplescalar simulator

- SPEC95 benchmarks

- 2-way, 64K L1 I- and D-Cache

- 4-way, out-of-order issue

- Sense interval : 256K I-Cache accesses

- Threshold set to base case miss rate

- Measure size estimate power

## **DRI-Cache: Conclusions**

#### DRI-Cache results are encouraging

- Within 3% of base performance on average

- size reduction by 11% 96%

- Relatively simple hardware

#### Actual power reduction

- Using spice simulations on our layout

- average static power reduction of 62%

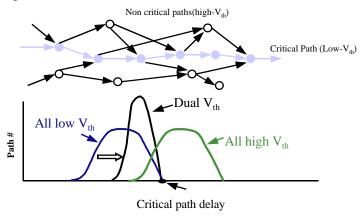

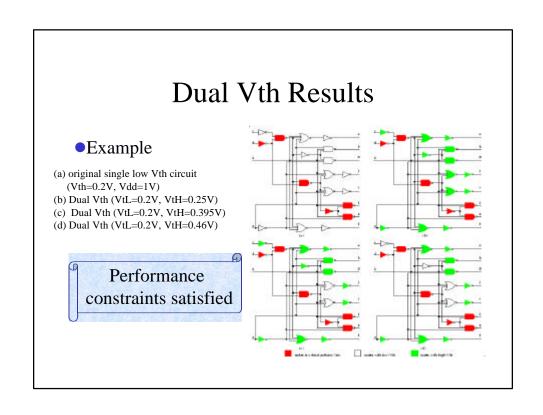

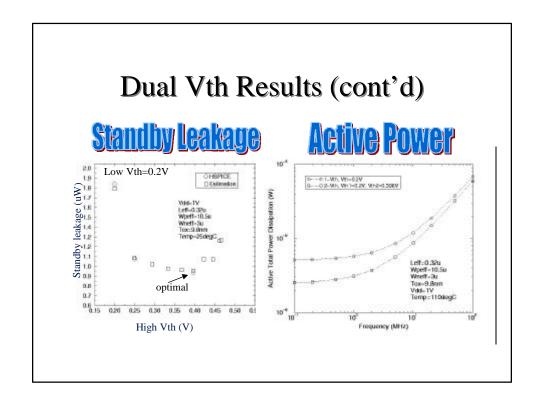

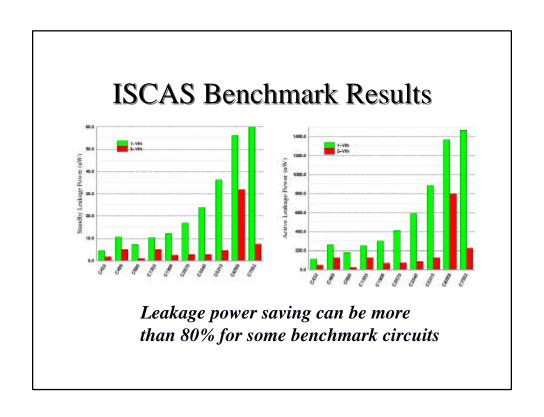

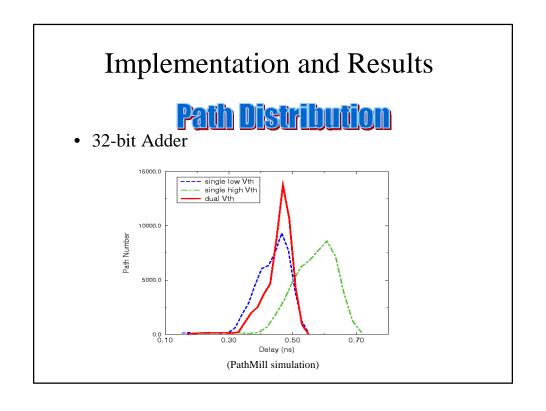

### **Dual Threshold CMOS**

- Low-V<sub>th</sub> transistors in critical path for high performance

- Some high-V<sub>th</sub> transistors in non-critical paths to reduce leakage

# Dual Threshold CMOS (cont'd)

• Due to the complexity of a circuit, not all the transistors in non-critical paths can be assigned a high-V<sub>th</sub>, otherwise, the critical path may change.

$\bullet$  How to selectively assign dual  $V_{\text{th}}$  to achieve the best leakage saving under performance constraints?

## Leakage of 32-bit Adder

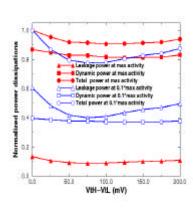

$\hbox{ Mixed-$V_{th}$ design technique can provide 20\% more leakage savings than gate-level dual-$V_{th}$ technique }$

## Total Power of 32-bit Adder

- Total power can be reduced by 9% for high activity

- Total power can be reduced by 22% at low activity

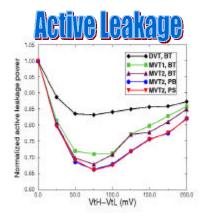

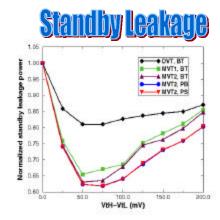

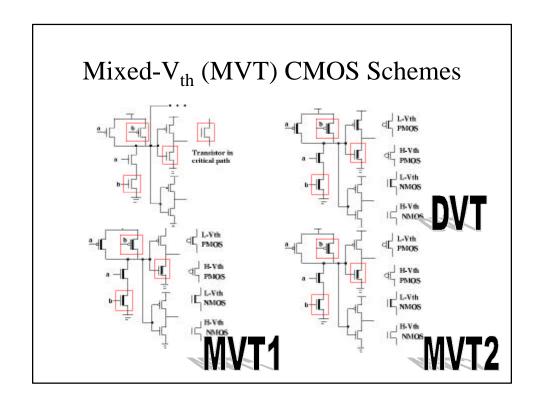

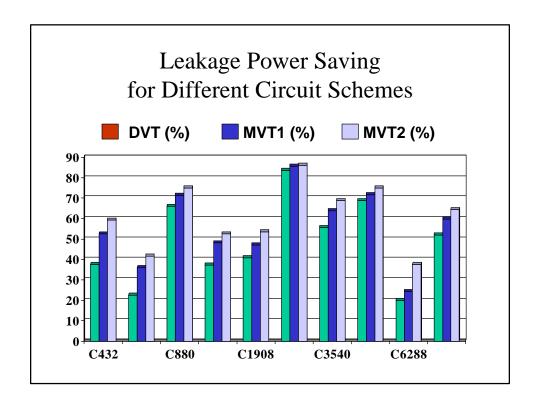

# Mixed-V<sub>th</sub> (MVT) CMOS Schemes

- Mixed-V<sub>th</sub> (MVT) CMOS Schemes

- Scheme I (MVT1)

- There is no mixed  $\boldsymbol{V}_{\text{th}}$  in p pull-up or n pull-down trees.

- Scheme II (MVT2)

- Mixed- $V_{\rm th}$  is allowed anywhere except for the series connected transistors.

• Due to the process variation, the worst case corner should be used in the analysis.

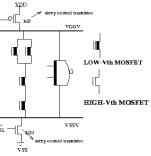

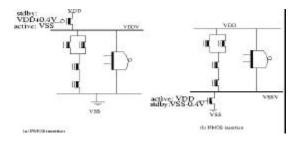

## **MTCMOS**

- Multi-Threshold CMOS (From S. Mutoh, etc. JSSC 1995)

- In active mode:

- SL=0, MP and MN are "on VDDV and VSSV almost function as VDD and VSS.

- In standby mode:

- SL=1, MP and MN are "off leakage is suppressed.

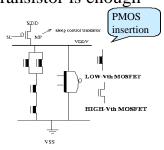

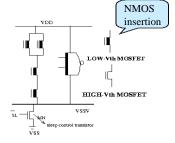

## MTCMOS (cont'd)

• Only one type of high-Vth sleep control transistor is enough

• NMOS size smaller

NMOS insertion is preferable

## MTCMOS (cont'd)

- Advantage:

- Effective for standby leakage reduction

- Easily implemented based on existing circuits

- 1-V MTCMOS DSP chip for mobile phone application (1996)

- Disadvantage:

- Increase area and delay

- If data retention is required in standby mode, an extra high-V<sub>th</sub> memory circuit is needed

## **SCCMOS**

- Super Cut-off CMOS (From H. Kawaguchi, ISSCC, 1998)

- Single-low-V<sub>th</sub> circuit

- Low- $V_{th}$  sleep control transistor with smaller size

- Minimal  $V_{dd}$  is lower than that of MTCMOS

- A gate bias generator is required

## **VTCMOS**

- Variable Threshold CMOS (from T. Kuroda, ISSCC, 1996)

- In active mode:

- Zero or slightly forward body bia for high speed

- In standby mode:

- Deep reverse body bias for low leakage

- Triple well technology required

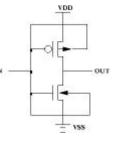

## **DTMOS**

- Dynamic Threshold CMOS

- from F. Assaderaghi, IEDM, 1994

- Vth altered dynamically to suit the operation state of the circuit

- Vdd<0.6V

- Triple well required for BULK silicon technology

- DTMOS in partially-depleted SOI

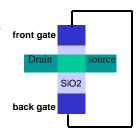

## **DGDT SOI CMOS**

- Double Gate Dynamic Threshold SOI CMOS

from L.Wei, Z. Chen, K.Roy, IEEE SOI Conf., 1997

- Asymmetrical double gate fully-depleted SOI MOSFET

- Front gate: conducting gate Back gate: controlling gate

## Conclusions

- Efficient leakage control technique required to maintain high performance in future designs

- For some niche applications (where performance is of secondary concern) ultra low power sub-threshold digital circuits can be used

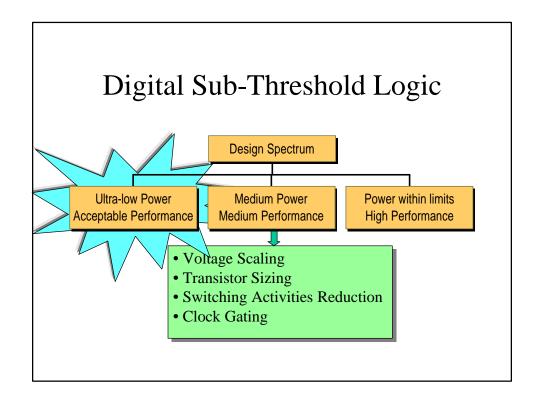

## Digital Sub-threshold Logic

- Operate in sub-threshold region  $(V_{gs} < V_{th})$

- Uses leakage current as the operating switching current

- Suitable for ultra-low power applications where performance is of secondary importance

- Utilizes sub-threshold characteristics of MOS transistors

# **Application Areas**

• Primary requirement: *Ultra-low Power*

• Bursty applications

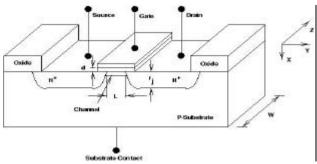

# Sub-threshold Characteristics of MOS Transistor

$$I_{ds} = \mathbf{m}_{eff} C_{ox} \frac{W}{L} (m-1) \left(\frac{kT}{q}\right)^{2} e^{\frac{(V_g - V_{th})}{mkT/q}} \left(1 - e^{-\frac{V_{ds}}{kT/q}}\right)$$

# Sub-threshold Characteristics of MOS Transistor

$$I_{ds} = \mathbf{m}_{eff} C_{ox} \frac{W}{L} (m-1) \left(\frac{kT}{q}\right)^{2} e^{\frac{\left(V_{g} - V_{th}\right)}{mkT/q}} \left(1 - e^{-\frac{V_{ds}}{kT/q}}\right)$$

- *m* is body-effect coefficient i.e.  $m = 1 + \frac{C_{depl}}{C_{ox}} = 1 + \frac{3t_{ox}}{W_{depl}}$

- $C_{depl}$  is bulk depletion capacitance i.e $C_{depl} = \frac{\mathbf{e}_{Si}}{W_{depl}}$

- $C_{ox}$  is oxide capacitance per unit area i.e.  $C_{ox} = \frac{e_{ox}}{t_{ox}}$

# Sub-threshold Characteristics of MOS Transistor

$$I_{ds} = \mathbf{m}_{eff} C_{ox} \frac{W}{L} (m-1) \left(\frac{kT}{q}\right)^2 e^{\frac{(V_g - V_{th})}{mkT/q}} \left(1 - e^{-\frac{V_{ds}}{kT/q}}\right)$$

$$I_{ds} \propto e^{V_{gs}}$$

$$g_m \equiv \frac{\partial I_{ds}}{\partial V_{gs}} |_{V_{ds} = const}$$

## Threshold Voltage

$$V_{th} = V_{fb} + 2\mathbf{y}_{b} + \frac{\sqrt{2\mathbf{e}_{Si}qN_{A}(2\mathbf{y}_{b} - V_{sb})}}{C_{ox}}$$

$$\Delta V_{th} = V_{th}(V_{sb}) - V_{th}(V_{sb} = 0) = \frac{\sqrt{2\mathbf{e}_{Si}qN_{A}}}{C_{ox}} \left(\sqrt{2\mathbf{y}_{b} - V_{sb}} - \sqrt{2\mathbf{y}_{b}}\right)$$

$$= a\mathbf{b} \left(\sqrt{\frac{2\mathbf{y}_{b} - V_{sb}}{\mathbf{b}}} - \sqrt{\frac{2\mathbf{y}_{b}}{\mathbf{b}}}\right) \quad \bullet V_{fb} \text{ is the flat-band voltage}$$

$$\bullet \mathbf{y}_{b} = V_{fermi} - V_{intrinsic of bulk Si}$$

$$\bullet \mathbf{e}_{Si} \text{ is the permittivity of Silicon}$$

$$\bullet C_{ox} = \mathbf{e}_{ox}/t_{ox} \text{ i.e. oxide capacitance/unit area}$$

$$\bullet \mathbf{b} = \mathrm{kT/q} \text{ i.e. thermal voltage}$$

$$\bullet L_{D} = (\mathbf{b}\mathbf{e}_{Si}/(qN_{A}))^{1/2} \text{ i.e. extrinsic Debye length}$$

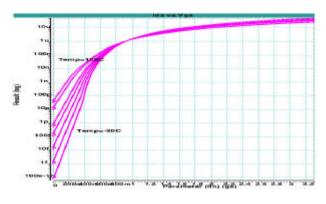

# Temperature Effect on V<sub>th</sub>

$$V_{th} = V_{fb} + 2\mathbf{y}_{b} + \frac{\sqrt{2\mathbf{e}_{Si}qN_{A}(2\mathbf{y}_{b} - V_{sb})}}{C_{ox}}$$

$$\frac{dV_{th}}{dT} = \frac{d\mathbf{y}_{b}}{dT} \left( 2 + \frac{1}{C_{ox}} \sqrt{\frac{\mathbf{e}_{Si}qN_{A}}{\mathbf{y}_{b}}} \right)$$

$$\frac{d\mathbf{y}_{b}}{dT} = \pm \frac{1}{T} \left( \frac{E_{g}(T=0)}{2q} - |\mathbf{y}_{b}(T)| \right)$$

$E_g$  is the band-gap energy

## Sub-threshold Slope (S)

Gate voltage swing needed to change the drain current by one decade

$$S = \frac{dV_{gs}}{d(\ln I_{ds})} \ln 10 = \mathbf{b} \frac{d \binom{V_{gs}}{\mathbf{b}}}{d(\ln I_{ds})} \ln 10 = \mathbf{b} \left[ 1 + \frac{C_{depl}}{C_{ox}} \right] \left[ 1 - \left( \frac{2}{a^2} \right) \left( \frac{C_{depl}}{C_{ox}} \right)^2 \right] \ln 10$$

For  $a \gg \left( \frac{C_{depl}}{C_{ox}} \right)$ :  $S \approx \frac{kT}{q} \left[ 1 + \frac{C_{depl}}{C_{ox}} \right] \ln 10$

$C_{depl}$  is the depletion layer capacitance

# Temperature Variation

$$I_{ds} = \mathbf{m}_{eff} C_{ox} \frac{W}{L} (m-1) \left(\frac{kT}{q}\right)^{2} e^{\frac{\left(V_{g} - V_{th}\right)}{mkT/q}} \left(1 - e^{-\frac{V_{ds}}{kT/q}}\right)$$

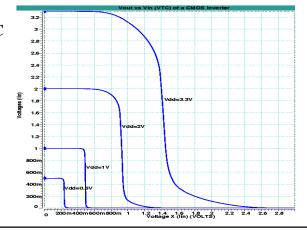

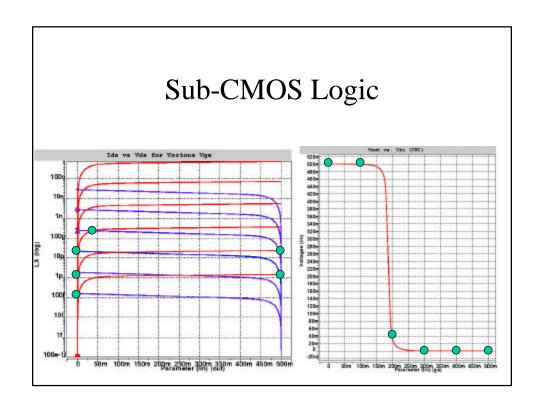

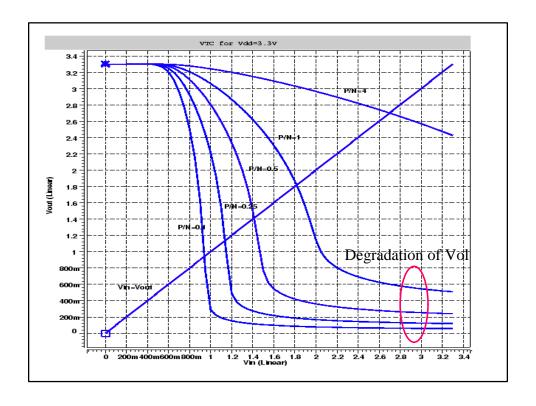

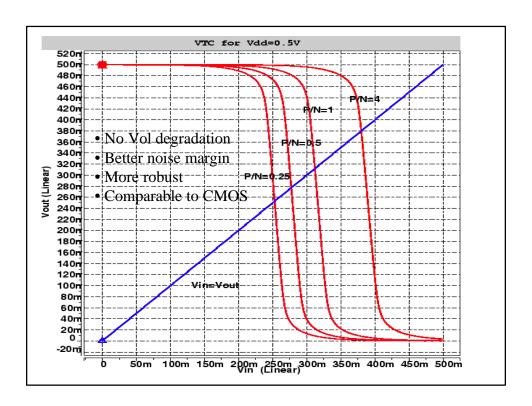

# Sub-threshold Static Logic: Sub-CMOS Logic

- CMOS logic operates in sub-threshold region

- $\bullet \quad V_{dd} < V_{th}$

- Near ideal VTC

- High gain

- High g<sub>m</sub>

- Better NM

## **Simulation Results**

- Logic Gates (SPICE using 0.35m process)

- 8x8 Carry-Save Array Multiplier (0.35um)

| Inversion | Power(W) | Delay(s) | PDP(J)    |

|-----------|----------|----------|-----------|

| Strong    | 9.27e-3  | 1.883e-9 | 17.46e-12 |

| Weak      | 30.1e-9  | 21.38e-6 | 0.644e-12 |

377.4um x 279.1um

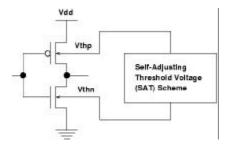

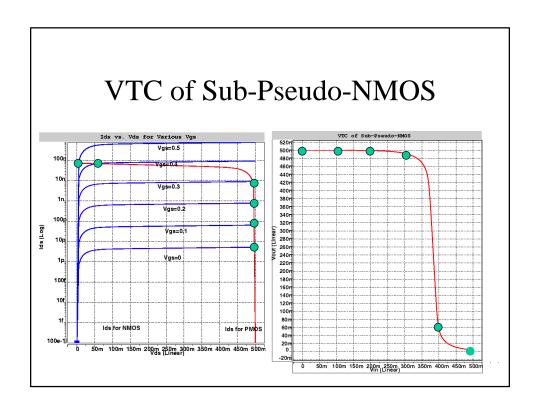

# Robust Sub-Static Logic: Sub-VT-CMOS logic

- Negative feedback principle:

- Monitors any change in leakage current (due to process and temperature variations)

- Stabilizes the circuit by applying appropriate substrate bias

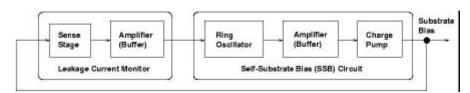

## Sub-VT-CMOS Logic

Two components of stabilization scheme:

- Leakage Current Monitor (LCM):

- Leakage current sensor

- Activates/De-activates the SSB circuit

- Self-Substrate Bias (SSB) circuit:

- Uses charge-pump to accumulate charge

- Applies bias to the substrate

## Simulation Results

- 8x8 carry-save array multipliers

- TSMC 0.35um process technology

- 50kHz with Vdd=0.5V and temp=55°C

|                 | Area(um <sup>2</sup> ) | Power(uW) |

|-----------------|------------------------|-----------|

| CMOS            | 228.6x10 <sup>3</sup>  | 11.59     |

| Sub-CMOS        | $228.6x10^3$           | 0.163     |

| Sub-Pseudo-NMOS | $210.9x10^3$           | 1.056     |

| Sub-True-NMOS   | 202.7x10 <sup>3</sup>  | 1.497     |

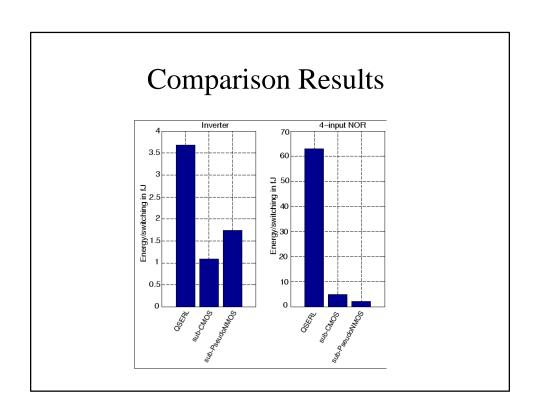

# Comparison with other known ultra-low power logic: Energy-Recovery Logic

- To validate the power saving effectiveness of sub-threshold logic

- QSERL (Quasi-Static Energy-Recovery Logic): close resemblance to CMOS logic

- Sinusoidal power supply generator is assumed to have 100% efficiency (In practice, only 80-90% efficiency is achieved)

- Use ideal Schottky diodes instead of diode-connected, low Vth MOS transistors (leaky transistors make it difficult for QSERL to hold the output voltage properly during long hold time)

## Conclusions

- Digital sub-threshold logic is used to satisfy the ultra-low power requirement

- Sub-threshold logic is readily implemented and derived from the traditional existing circuits by lowering the  $V_{dd}$  to be less than  $V_{th}$

- Improved characteristics including higher gain, better noise margin, and more energy efficient

- Ratio-ed logic (Pseudo/True-NMOS) is comparable to CMOS logic in sub-threshold logic in terms of robustness, noise margin and power consumption

- Sub-dynamic logic is faster, smaller and has better noise margin than sub-CMOS

- Sub-threshold logic is easier to design and more efficient as compared to other known ultra-low power logic, such as energy-recovery logic