# Swing-Restored Pass Gate Logic (SRPL)

- Low stand-by power

- High design margin, process tolerance

- Less delay via sense-amp action

## Push-Pull Pass Transistor Logic (PPL)

- Push-Pull action, no need for re-buffering

- Low power

- PFET drive dependence

- High performance, skew transitions in a particular direction

- Good dynamic noise immunity

- Static circuit testability

- Cumbersome monotonic stage operation

- Complex clocking

- Capability of inverting functions

- Reduced chip clock overhead

- Extreme process sensitivity

- Timing complexity

- Additional clk propagated with logic

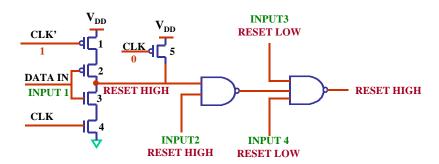

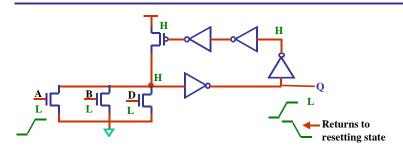

## Self Resetting Domino (SR CMOS)

- Own appropriate clocking

- Very high speed

- Reduced clock over-head

- Low noise immunity

- High process sensitivity

- Additional device count

- Difficult to time

### Latched Domino Structure

- Merging of a latch with the load devices of a dynamic logic element

- Result is fully latched

- Need for O/P buffer eliminated

- Tree does not need to complete its transition

- Sense amplification and additional noise immunity adds design reliability

# Enable/Disable CMOS Differential Logic (ECDL)

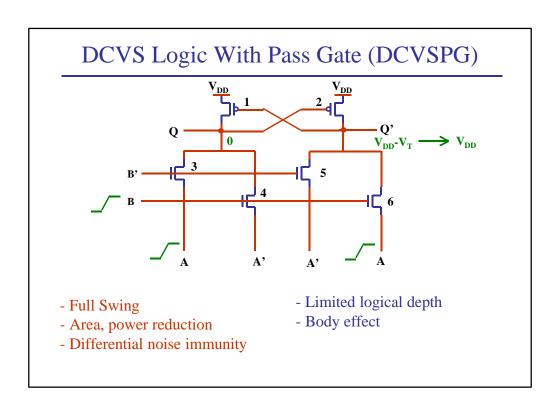

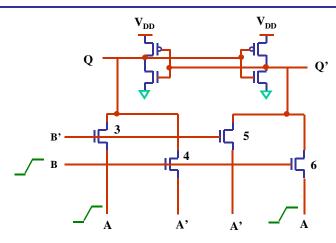

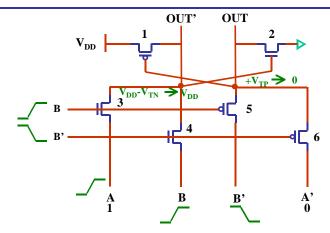

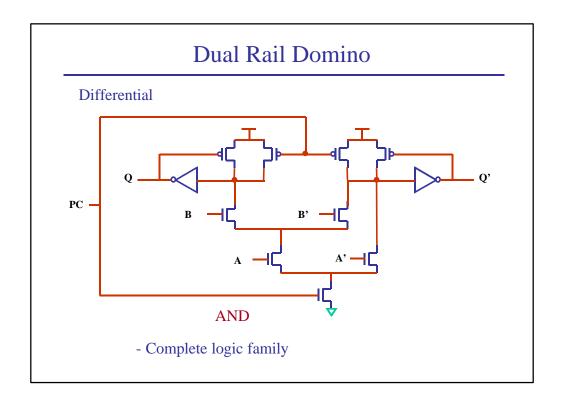

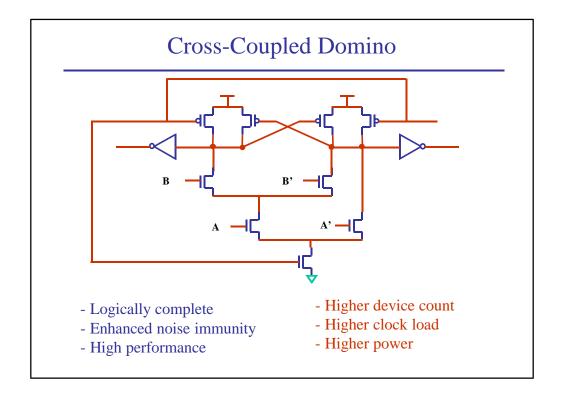

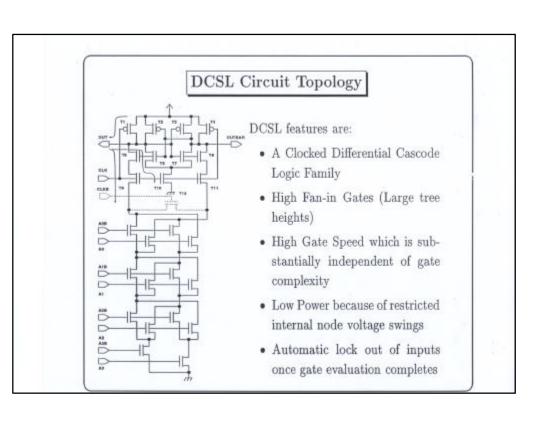

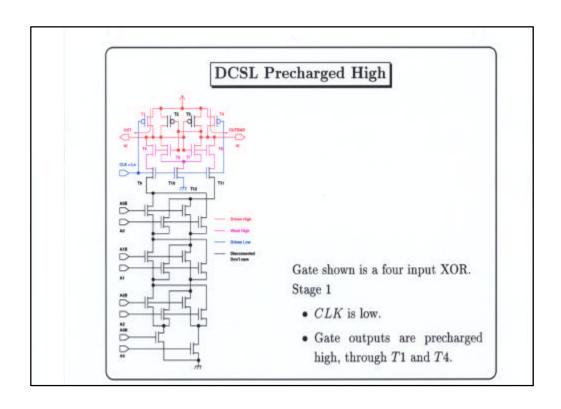

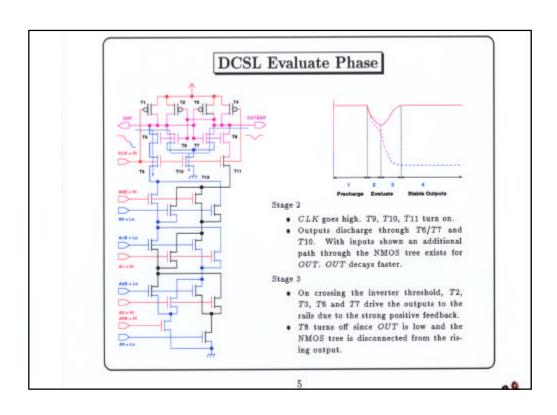

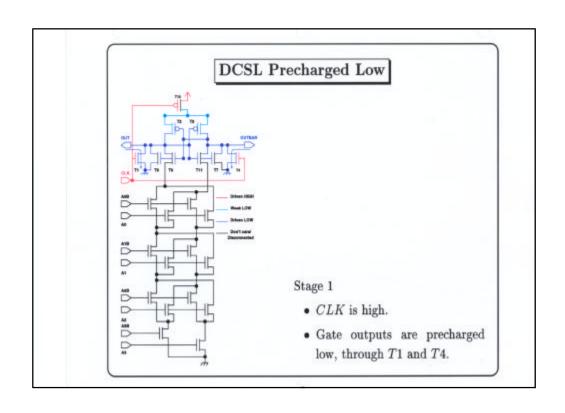

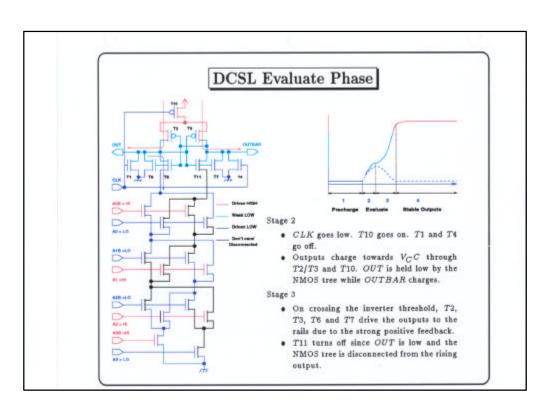

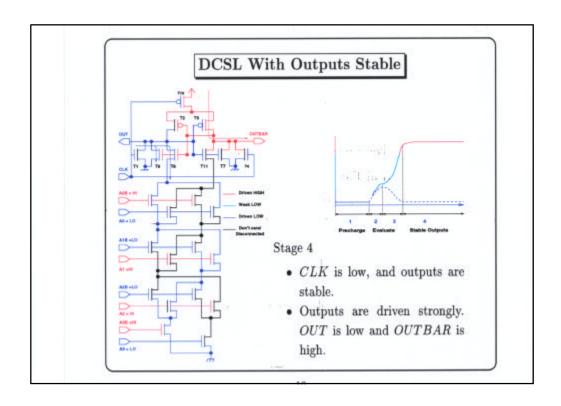

### DCSL Features

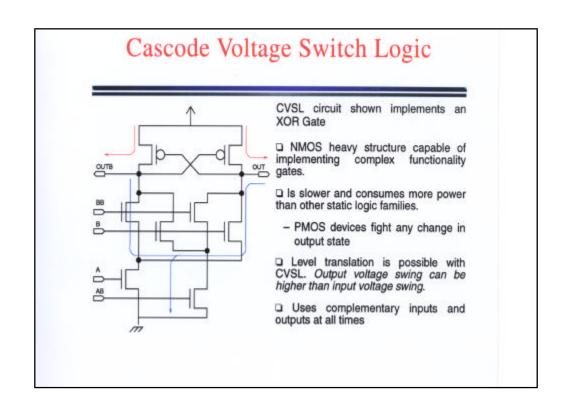

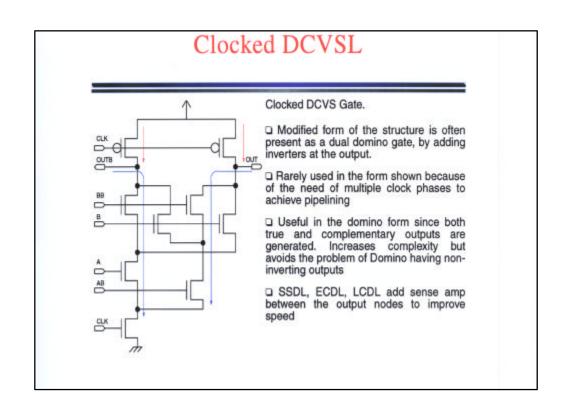

- Clocked Differential Cascode Voltage Switch Logic style

- Differential NMOS tree gives gate functionality.

- Capable of implementing High fan-in gates with low delay

- Gates having fanin between 6 to 18 perform better than comparable domino gates.

- High Complexity gates

- Allows a reduction in logic depth and number of output nodes (not possible in every case)

## DCSL Features (contd.)

- Efficient implementation of XOR based circuits.

- Arithmetic circuits with lots of XORs benefit the most.

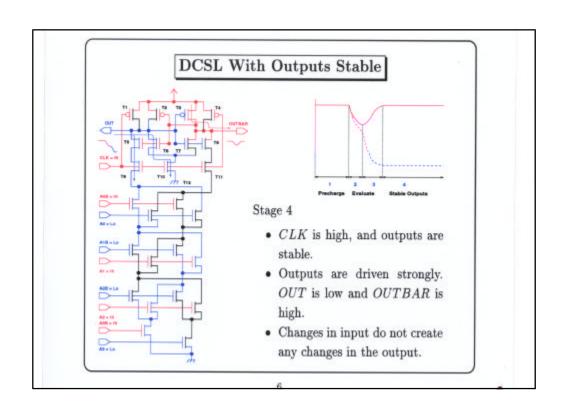

- Achieves low power without sacrificing speed by restricting the voltage swing of internal nodes

- Internal voltage swings are of the order of 0.4volts in a 5volt CMOS process.

- Automatic lock out of inputs once gate evaluation is complete

- Functionally identical to a latch followed by a combinatorial gate

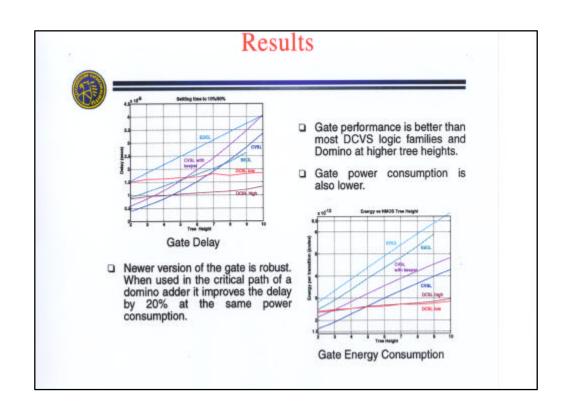

#### Results

A comparison of DCSL with similar logic families has been carried out.

- An XOR tree similar to that shown previously is used.

- Comparison is with respect to circuit in the absence of T9 and T11. Circuits compared are

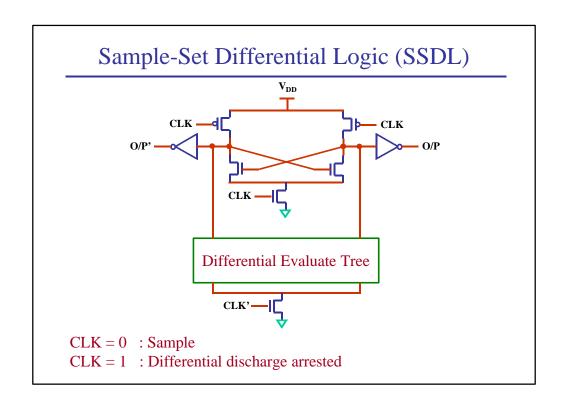

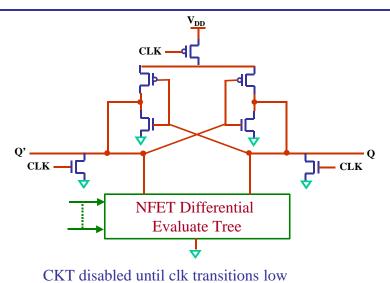

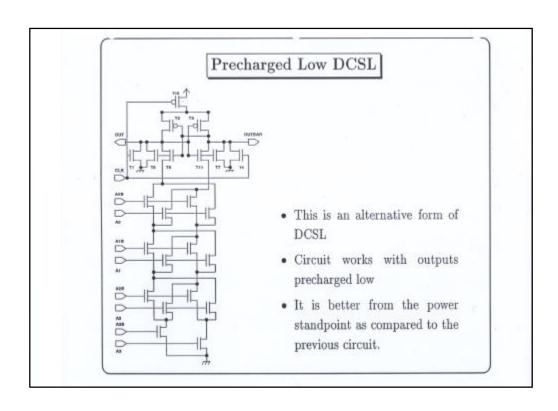

- DCSL precharged high is similar to "Sample Set Differential Logic" SSDL.

- DCSL precharged low is similar to "Enable Disable Cascode Logic" EDCL.

- Clocked DCVS with and without a "keeper" P transistor.

$$\frac{a}{n} \bigvee_{i} \bigvee_{j} \bigvee_{j} \bigvee_{i} \bigvee_{j} \bigvee_{j} \bigvee_{i} \bigvee_{j} \bigvee_$$

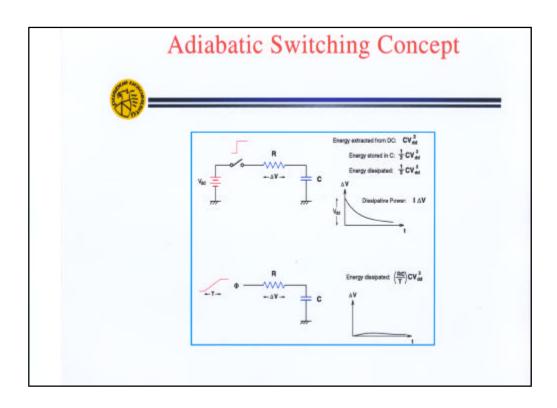

$$\Phi = \begin{cases} 0 & t < 0 \\ \left(\frac{V_{td}}{T}\right)t & 0 \le t < T \\ V_{td} & t \ge T \end{cases}$$

The solution of the above equation is given by

$$V_c = \begin{cases} 0 & t < 0 \\ \Phi - \left(\frac{RC}{T}\right)V_{dd}(1 - e^{-t/RC}), & 0 \le t < T \\ \Phi - \left(\frac{RC}{T}\right)V_{dd}(1 - e^{-t/RC})e^{-(t-t)/RC} & t \ge T \end{cases}$$

(7.2)

The energy dissipation in the above charging process can be calculated as follows:

$$E_{lower} = \int_{0}^{\infty} iV_{N} dt = \int_{0}^{T} iV_{N} dt + \int_{T}^{\infty} iV_{N} dt$$

(7.3)

The first term of Eq. (7.4) can be written as

$$\begin{split} \int_{0}^{T} (\mathcal{V}_{R} \, dt &= \int_{0}^{T} \frac{\left(\Phi - \mathcal{V}_{c}\right)^{2}}{R} \, dt \\ &= \int_{0}^{T} \frac{\left[\left(V_{dd}/T\right)RC\left(1 - e^{-\varepsilon/RC}\right)\right]^{2}}{R \, dt} \\ &= \frac{R^{2}C^{2}}{T^{2}} C \mathcal{V}_{cd}^{2} \int_{0}^{T/RC} \left(1 - e^{-\varepsilon/RC}\right)^{2} d\left(\frac{1}{RC}\right) \\ &= \left(\frac{RC}{T}\right) C \mathcal{V}_{cd}^{2} \left[1 - \frac{3}{2}\left(\frac{RC}{T}\right) + 2\left(\frac{RC}{T}\right)e^{-T/RC} - \frac{1}{2}\left(\frac{RC}{T}\right)e^{-2T/RC}\right] \end{split}$$

And the second term can be written as

$$\begin{split} \int_{T}^{a} i V_{B} \, dt &= \int_{T}^{a} \frac{(\Phi - V_{f})^{2}}{R} \, dt \\ &= \frac{RC}{T^{2}} C V_{df}^{2} \left(1 - e^{-T f BC}\right)^{2} \int_{T}^{a} e^{-2k T - T 3 f BC} \, dt \\ &= \left(\frac{RC}{T}\right)^{2} C V_{df}^{2} \left[\frac{1}{2} \left(1 - e^{-T f BC}\right)^{2}\right] \end{split}$$

Finally we have

$$E_{boost} = \left(\frac{RC}{T}\right)CV_{eld}^T\left(1 - \frac{RC}{T} + \frac{RC}{T}e^{-T/RC}\right) \qquad (7.4)$$

Let us consider the two extreme cases. When  $T \gg R0$

$$E_{bwir} = \left(\frac{RC}{T}\right)CV_{id}^{\gamma}$$

(7.5)

and when  $T \ll RC$

$$\mathcal{E}_{\text{berne}} = \left(\frac{RC}{T}\right)C\mathcal{V}_{dd}^{2}\left\{1 - \frac{RC}{T} + \frac{RC}{T}\left[1 - \frac{T}{RC} + \frac{1}{2}\left(\frac{T}{RC}\right)^{2}\right]\right\}$$

$$= \frac{1}{2}C\mathcal{V}_{dd}^{2}$$

(7.6)