#### **GPU Teaching Kit**

**Accelerated Computing**

### Module 4.4 - Memory and Data Locality

### Objective

- To learn to write a tiled matrix-multiplication kernel

- Loading and using tiles for matrix multiplication

- Barrier synchronization, shared memory

- Resource Considerations

- Assume that Width is a multiple of tile size for simplicity

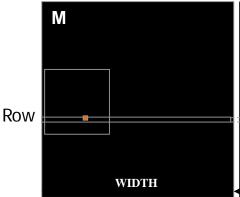

# Loading Input Tile 0 of M (Phase 0)

Have each thread load an M element and an N element at the same relative position as its P element.

3

# Loading Input Tile 0 of N (Phase 0)

Have each thread load an M element and an N element at the same relative position as its P element.

```

int Row = by * blockDim.y + ty;

int Col = bx * blockDim.x + tx;

2D indexing for accessing Tile 0:

M[Row][tx]

N[ty][Col]

```

M Row WIDTH

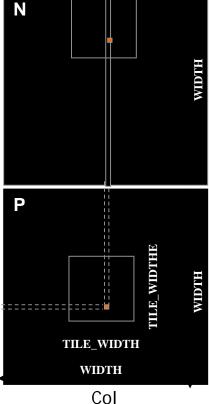

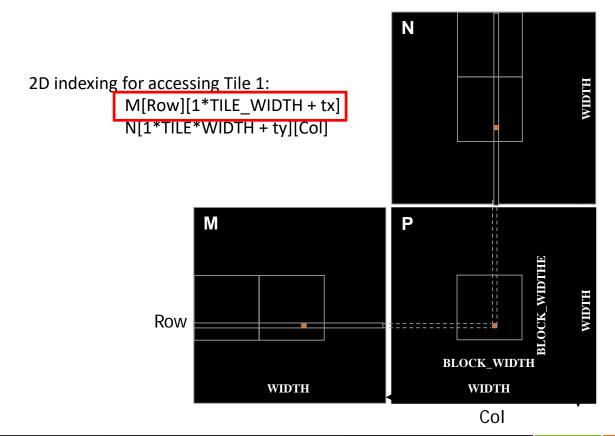

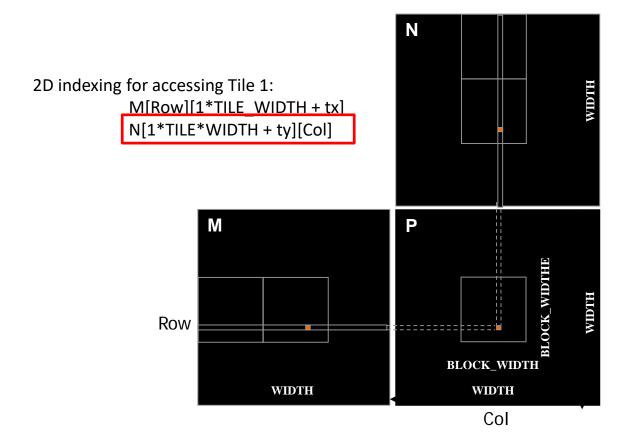

## Loading Input Tile 1 of M (Phase 1)

# Loading Input Tile 1 of N (Phase 1)

### M and N are dynamically allocated - use 1D indexing

- M[Row][p\*TILE\_WIDTH+tx]

M[Row\*Width + p\*TILE\_WIDTH + tx]

- N[p\*TILE\_WIDTH+ty][Col]

N[(p\*TILE\_WIDTH+ty)\*Width + Col]

where p is the sequence number of the current phase

```

global void MatrixMulKernel(float* M, float* N, float* P, Int Width)

shared float ds M[TILE WIDTH];

shared float ds N[TILE WIDTH][TILE WIDTH];

int bx = blockIdx.x; int by = blockIdx.v;

int tx = threadIdx.x; int ty = threadIdx.y;

int Row = by * blockDim.y + ty;

int Col = bx * blockDim.x + tx;

float Pvalue = 0;

// Loop over the M and N tiles required to compute the P element

for (int p = 0; p < n/TILE_WIDTH; ++p) {</pre>

// Collaborative loading of M and N tiles into shared memory

ds_M[ty][tx] = M[Row*Width + p*TILE_WIDTH+tx];

ds N[ty][tx] = N[(t*TILE WIDTH+ty)*Width + Col];

syncthreads();

for (int i = 0; i < TILE_WIDTH; ++i)Pvalue += ds_M[ty][i] * ds_N[i][tx];

synchthreads();

P[Row*Width+Col] = Pvalue;

```

```

global void MatrixMulKernel(float* M, float* N, float* P, Int Width)

__shared__ float ds_M[TILE_WIDTH][TILE_WIDTH];

shared float ds N[TILE WIDTH][TILE WIDTH];

int bx = blockIdx.x; int by = blockIdx.v;

int tx = threadIdx.x; int ty = threadIdx.y;

int Row = by * blockDim.y + ty;

int Col = bx * blockDim.x + tx;

float Pvalue = 0;

// Loop over the M and N tiles required to compute the P element

for (int p = 0; p < n/TILE_WIDTH; ++p) {</pre>

// Collaborative loading of M and N tiles into shared memory

ds M[ty][tx] = M[Row*Width + p*TILE_WIDTH+tx];

ds N[ty][tx] = N[(t*TILE WIDTH+ty)*Width + Col];

__syncthreads();

for (int i = 0; i < TILE_WIDTH; ++i)Pvalue += ds_M[ty][i] * ds_N[i][tx];

synchthreads();

P[Row*Width+Col] = Pvalue;

```

```

global void MatrixMulKernel(float* M, float* N, float* P, Int Width)

__shared__ float ds_M[TILE_WIDTH][TILE_WIDTH];

shared float ds N[TILE WIDTH][TILE WIDTH];

int bx = blockIdx.x; int by = blockIdx.v;

int tx = threadIdx.x; int ty = threadIdx.y;

int Row = by * blockDim.y + ty;

int Col = bx * blockDim.x + tx;

float Pvalue = 0;

// Loop over the M and N tiles required to compute the P element

for (int p = 0; p < n/TILE_WIDTH; ++p) {</pre>

// Collaborative loading of M and N tiles into shared memory

ds M[ty][tx] = M[Row*Width + p*TILE_WIDTH+tx];

ds N[ty][tx] = N[(t*TILE WIDTH+ty)*Width + Col];

__syncthreads();

for (int i = 0; i < TILE_WIDTH; ++i)Pvalue += ds_M[ty][i] * ds_N[i][tx];

synchthreads();

P[Row*Width+Col] = Pvalue;

```

### Tile (Thread Block) Size Considerations

- Each thread block should have many threads

- TILE\_WIDTH of 16 gives 16\*16 = 256 threads

- TILE\_WIDTH of 32 gives 32\*32 = 1024 threads

- For 16, in each phase, each block performs 2\*256 = 512 float loads from global memory for 256 \* (2\*16) = 8,192 mul/add operations. (16 floating-point operations for each memory load)

- For 32, in each phase, each block performs 2\*1024 = 2048 float loads from global memory for 1024 \* (2\*32) = 65,536 mul/add operations. (32 floating-point operation for each memory load)

### **Shared Memory and Threading**

- For an SM with 16KB shared memory

- Shared memory size is implementation dependent!

- For TILE\_WIDTH = 16, each thread block uses 2\*256\*4B = 2KB of shared memory.

- For 16KB shared memory, one can potentially have up to 8 thread blocks executing

- This allows up to 8\*512 = 4,096 pending loads. (2 per thread, 256 threads per block)

- The next TILE\_WIDTH 32 would lead to 2\*32\*32\*4 Byte= 8K Byte shared memory usage per thread block, allowing 2 thread blocks active at the same time

- However, in a GPU where the thread count is limited to 1536 threads per SM, the number of blocks per SM is reduced to one!

- Each \_\_syncthread() can reduce the number of active threads for a block

- More thread blocks can be advantageous

### **GPU Teaching Kit**

Accelerated Computing

The GPU Teaching Kit is licensed by NVIDIA and the University of Illinois under the <u>Creative Commons Attribution-NonCommercial 4.0 International License.</u>