# RF-PSF: A CNN-Based Process Distinction Method Using Inadvertent RF Signatures

Md Faizul Bari, Member, IEEE, Baibhab Chatterjee, Member, IEEE, Lucas Duncan, Member, IEEE, and Shreyas Sen, Senior Member, IEEE

Abstract-Stochastic variation of process parameters within a die and technology-limitation-driven variation from die-to-die give rise to unique distribution patterns for manufacturing process parameters. These patterns work as a process signature that is transferred from the device level to the system level through electrical circuits and can be used to make a distinction among the processes. In this work, we propose an in-situ manufacturing process technology distinction method, 'Radio Frequency Process Specific Functions (RF-PSF)', that uses process-specific inherent properties of an IC manifested in the transmitted radio frequency signal. Among many desirable testing criteria, RF-PSF addresses the question of fabrication with the intended process technology. This information plays an important role in modern zero-trust architecture and IC clone detection, a counterfeiting method where the IC is manufactured using a different process. An RF transmitter with RF-DAC power amplifier for QPSK modulation has been designed and simulated in 14 nm, 22 nm, and 65 nm processes for 5 process corners (TT, FF, FS, SF, and SS) in Cadence. The simulated data have been processed in MATLAB. A Multilayer Perceptron (MLP), trained with the constellation data, provides an average accuracy of  $\sim 90\%$  for process distinction. Realizing that (i) a higher order modulation will have even more process information and (ii) we can harness the Convolutional Neural Network's (CNN) improved capability on pattern recognition, we can feed image-like constellation plots to a CNN to get better and consistent performance. Using the baseband constellations for 64-QAM modulated data as images, we have achieved  $\sim 100\%$  accuracy with commonly used, pretrained CNN models (ResNet18, ResNet50, and GoogleNet) through transfer learning. The separation among 5 process corners within a process, termed intra-process variation, is also analyzed. The effect of baseband sampling rate and ADC resolution, two practical limitations in RF systems, have been explored. An extensive study has been performed on the effect of a key design parameter at the RF circuit level i.e. W/L or aspect ratio, leading to design insights, proper CNN selection, and some control parameters. This work establishes RF-PSF as a zero-power, zero-area overhead, in-situ process distinction method.

*Index Terms*—radio frequency, CNN, transfer learning, zeropower, zero-trust, manufacturing process, counterfeit IC

# I. INTRODUCTION

# A. Harnessing Process Variation in Radio Frequency Machine Learning Systems

**P**ROCESS parameters of a particular process technology drift significantly from their intended values due to the inherently stochastic nature of the processes and the limitations in process control. Variation of process parameters in the IC fabrication process is classified into two classes: (1) *local variation* or within die variation (fluctuation of the process parameters within a chip) and (2) *global variation* that includes die-to-die variation, wafer-to-wafer variation, and lot-to-lot

1

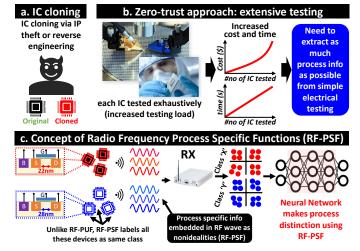

Fig. 1. (a) IC counterfeiting (e.g., IC cloning) poses a big threat to the whole semiconductor industry. To counter it, (b) zero-trust architecture can be a viable solution where there is no predefined trust and all the ICs are tested extensively. However, this approach increases testing costs and time, so it is desirable to extract as much information as possible from the simple electrical signal. (c) Process dependent system-level nonidealities are termed 'process specific functions' and work as the process identity that can be used to distinguish among processes at the system level. Here devices from 22 nm and 28 nm processes are considered (unlike RF-PUF which distinguishes devices of the same process, RF-PSF considers devices of the same process information that can be picked up by a neural network at the receiver end to distinguish between these two processes.

variation. Local variation stems from the inherent randomness associated with any semiconductor manufacturing process, e.g. random variation in doping density, edge roughness variation created randomly during lithography, random variation of the grain orientation in the metal gate or polysilicon leading to the work function variation, random distribution of dangling bonds and their capture of carriers, etc [1]–[3]. Unlike local variation, the root of global variation lies in the limitation of process technology and process control, e.g. oxide thickness variation during deposition, etching, or polishing [2], [4], [5].

Random local variation creates differences among devices of the same class, i.e., within-chip variation creates a *unique device signature* for a particular device pertaining to a device class. This signature is manifested as various system-level nonidealities in the transmitted signal. For example, the 'n' number of ZigBee devices fabricated using the same process technology in the same fab house will have slightly different nonidealities in their transmitted signal due to their unique device identity derived mostly from process variation. A

© 2023 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

This article has been accepted for publication in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. This is the author's version which has not been fully edi content may change prior to final publication. Citation information: DOI 10.1109/TCAD.2023.3266370

receiver with an in-situ machine-learning system can extract the embedded 'device signature' from the received wave to uniquely identify the device. This is the basis of *Radio Frequency Physical Unclonable Function or RF-PUF* [6]–[8] which is used for RF fingerprinting.

#### B. Proposed Radio Frequency Process Specific Functions

The deviation of output due to process technology is perceived as process-dependent nonidealities. In effect, process parameters and their distributions due to random local and process limitation-based global variations form a unique signature of a process. This signature can be thought of as a unique function, which we define as Process Specific Function (PSF). For radio frequency integrated circuits (RF IC), these functions are expressed in the transmitted RF signal which we call RF-PSF, and can be used to make a distinction among different process technologies. This is process identity instead of device identity, which separates it from the idea of RF-PUF. To elaborate the difference even further, devices fabricated using the same process technology are labeled as the same class by RF-PSF, whereas they are uniquely identified by RF-PUF. In other words, RF-PUF utilizes intra-process variation whereas RF-PSF utilizes inter-process variation.

This concept of the *in-situ process distinction method* is explained in fig. 1(c). Red and blue devices are fabricated using a 22 nm process and 28 nm process respectively. Red devices are labeled as class 'X' and blue devices are labeled as class 'Y' (RF-PUF would consider each device as a separate class, but RF-PSF considers them as same class as long as they are fabricated using the same process technology). Since the distributions of process parameter variations are different between the processes, the transmitted electromagnetic signal will contain different process-dependent nonidealities (RF-PSF) embedded in it. A receiver (RX) captures waves from both classes and processes them. The constellation diagram at the RX end will contain the signatures associated with the processes and a neural network trained with the constellation data can make a distinction between 22 nm and 28 nm processes.

The impact of both types of variations on output is not the same. This is explained with a nice thought experiment involving matched transistors of a differential pair in [1]. If the local variation is much less compared to the global variation, the differential pair will still be matched and the common mode gain will not change. However, if the local variation is very high, the transistors within a chip will no longer match and the designer will have to think of a way to adjust the common mode gain. So, the same circuit is behaving differently based on the process variation pattern which in turn depends on the process technology. We can think of it as the circuit is mapping process technology-related information from the device level to the system level. If the same circuit is implemented in different process technologies, the response of the same circuit at the system level will be slightly different as we have established that different process variation impacts the circuit performance differently.

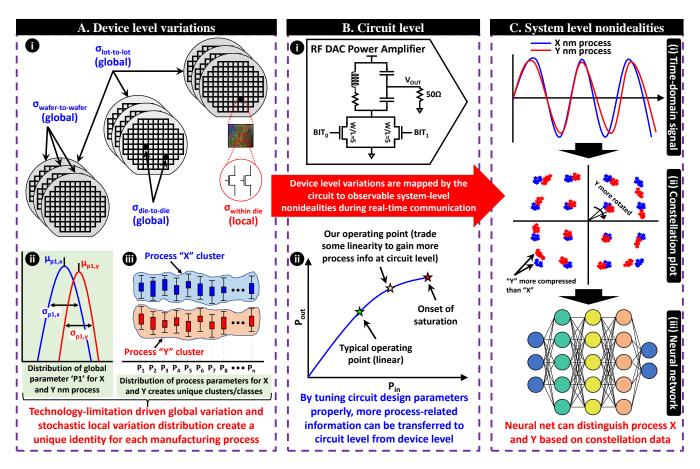

Fig. 2 shows how the device-level process information is transferred to the system level by properly designed circuits.

Fig. 2(a)(i) shows different types of process variation at the device level. In Fig. 2(a)(ii), the distribution of a hypothetical process parameter 'P1' has been shown for both X nm and Y nm processes. The distribution of hundreds of similar process parameters creates a unique cluster/group/class for each process as shown in Fig. 2(a)(iii). RF-PSF distinguishes these clusters (processes). Fig. 2(b) shows that this information is passed to the circuit from the device level. While a circuit designer tries to suppress most process-related information (to avoid process-driven nonidealities at the output), some information still passes. The amount of information can be increased even further by adjusting the operating points of the circuit. Hence, we propose two modes of operation:

- Communication mode: where the operating condition of the circuit is optimized for regular communication and maps less process-specific nonidealities at the system level. RF-PSF will provide less accuracy in this mode, but it will not interfere with regular operation and can make process distinctions on the go.

- 2) Test mode: where the operating condition of the circuit is pushed towards the limits where process-dependent nonidealities become maximum. The RF IC can be operated in this mode just to check process information for a brief time, and then switched back to regular communication.

As an example, we consider a power amplifier (PA) circuit which is the heart of any RF transmitter. The operating point can be shifted slightly towards saturation without hampering its performance too much. This is our communication mode where we get some process information but the regular performance remains primarily similar. The yellow point in fig. 2(b)(ii) shows this operating point. Now we can push the operating point to the edge of saturation which will increase nonideality at the output. However, that nonideality (phase noise, compression, etc.) is dependent on process parameters and contains significant process information. This is test mode and is shown as the red point in fig. 2(b)(ii). Significant process information is transferred to the system-level output as shown in fig. 2(c). Here, both the time domain signal and consequent constellation diagram contain significant processdependent nonideality. A neural network can be trained using this information which can intelligently distinguish between processes X and Y.

#### C. Motivation: Zero-Trust Architecture

Now that the concept of *RF-PSF* has been established as an *in-situ process distinction method*, the question arises as to why we need to extract manufacturing process information from the IC itself which the vendor already provides. The answer lies in 'IC counterfeiting'. Counterfeiting electronic components is a rising threat to the semiconductor supply chain. In 2011, IHS has reported a \$169B annual risk due to counterfeiting, with an annual growth of 25%. This is termed a "ticking bomb" for the semiconductor industry. IC counterfeiting involves recycling and remarking, overproduction, cloning, out-of-the-spec production, tampering, faking documentation, This article has been accepted for publication in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. This is the author's version which has not been fully edi content may change prior to final publication. Citation information: DOI 10.1109/TCAD.2023.3266370

3

JOURNAL OF LATEX CLASS FILES, VOL. X, NO. X, APRIL 2023

Fig. 2. (a)(i) Random fluctuation of process parameters leads to local variation (within die) whereas process technology limitation gives rise to global variation (die-to-die of a wafer, wafer-to-wafer of a lot, and lot-to-lot). (ii) Distribution of process parameter P1 that can distinguish two processes in the non-overlapping portion. (iii) Distribution of n process parameters creates unique clusters for both 'X' and 'Y' *nm* processes. (b) The unique signature of a process is transferred to the circuit level. A proper circuit design can harness more of this signature and reflect it as system-level output. Here, a power amplifier operating point is adjusted with a certain back-off to trade some nonlinearity for process information. (c) The process signature manifests itself as system-level nonidealities which can be seen in both (i) time-domain signal and (ii) constellation plot. A neural network can be trained with this information which can then make a distinction between process X.

etc. In the battle against IC counterfeiting, 'zero-trust' architecture [9] poses itself as a promising solution. It is a unique environment where there is no predefined trust and everyone is treated as a potential threat and access to information and resources is granted only when they get verified. The term 'zero-trust' got popular in early 2020 due to the rise of cyber threats as most of the employees had to work from home and were no longer in the security bubble of the workplace. 'zerotrust' concept can be applied to the semiconductor supply chain, which is vulnerable as the design is usually performed in one country but fabrication and assembly are done offshore. There are many points of vulnerability in the whole supply chain even for large manufacturers. A senate hearing in the US shows that 15% of the spare and replacement parts purchased by the Pentagon are counterfeited in some ways [10]. In a zerotrust environment, even the ICs from an authorized vendor are tested extensively before utilization, leaving no space for a breach of trust (as there is none by default!).

But the zero-trust approach increases test load tremendously as shown in fig. 1(b). Traditional counterfeiting detection methods require both physical inspection (X-Ray imaging, Scanning Acoustic Microscopy or SAM, Scanning Electron

Microscopy or SEM, optical inspection, Raman spectroscopy, Ion Chromatography or IO, etc.) and electrical testing (DC/AC characteristics test, fault test, etc.). While these methods are efficient, they put significant time and cost overhead and most of the methods are intrusive. This is especially problematic in the zero-trust approach where the testing load is much heavier. So, it is desirable to extract some of the manufacturing information noninvasively from the electrical signal of the ICs. RF-PSF is an attractive choice here as it can provide manufacturing process information in a non-invasive manner without any additional area and power overhead (as it needs no additional block in the transmitter) with trivial time, cost, and effort. But how to use process information to detect counterfeited IC? One particular counterfeiting method, IC cloning, involves IC fabrication using a different process than it was originally intended. RF-PSF can be used here to determine whether the IC was fabricated in the authorized manufacturing facility using the intended process technology. RF-PSF itself doesn't detect IC cloning, rather it makes a distinction among different process technology. That information is an important part of cloning detection.

In this work, we have designed and simulated a simple

This article has been accepted for publication in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. This is the author's version which has not been fully edi content may change prior to final publication. Citation information: DOI 10.1109/TCAD.2023.3266370

JOURNAL OF LATEX CLASS FILES, VOL. X, NO. X, APRIL 2023

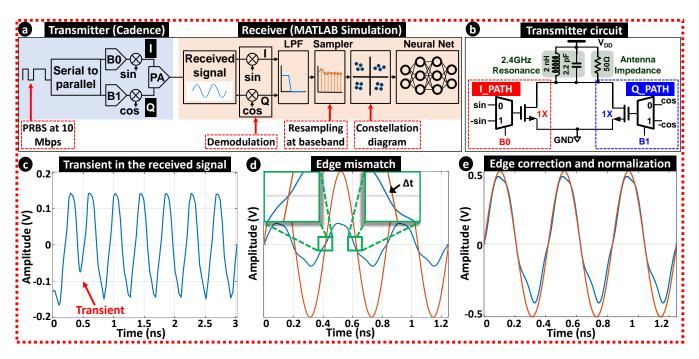

Fig. 3. (a) Simulation block diagram. The transmitter is simulated in Cadence where PRBS data are transmitted using QPSK modulation. The receiver is simulated in MATLAB where the RF signal is processed. (b) Transmitter circuit diagram. (c) The initial transient in the received signal shows irregularity in the wave. Although the transient contains some process information, it has been discarded for steady-state operation. (d) Due to DC offset, the falling edge of the signal doesn't match (right inset) when the rising edge is matched (left inset) with the reference clock. This can lead to a constant time difference  $\Delta t$  (hence, a constant phase difference  $\omega \Delta t$ ) erroneously. (e) Edge corrected (50% duty cycle) and normalized wave with a reference clock (sine).

RF transmitter with an RF DAC power amplifier in 3 different process technologies: 14 nm (GlobalFoundries), 22 nm (GlobalFoundries), and 65 nm (TSMC) for QPSK and 64-QAM modulation. Again, for specific process technology, simulation is performed for 5 process corners, namely: TT (typical-typical), FF (fast-fast), FS (fast-slow), SF (slow-fast), and SS (slow-slow). The transmitter is simulated in Cadence and the output RF signal is processed in a receiver designed in MATLAB. A deep learning block, initially a multilayer perceptron or neural network (NN) and later a convolutional neural network (CNN), is added at the end of the receiver chain. This block is trained with the I-Q data from the RF receiver which can then infer the variation among the processes and their corners. The variation within a specific process due to process corners is referred to as intra-process variation and the variation among different process technology, irrespective of process corners, is defined as an inter-process variation.

Simulation results show that process distinction accuracy among the 3 aforementioned processes is ~ 90% on average using QPSK modulation and NN, with a best-case accuracy of 99% and worst-case accuracy of > 80%. Using higher order modulation (64-QAM) and CNN (specifically CNN with DAG architectures, as will be explained in section VI-C), 100% accuracy can be achieved. A detailed analysis has been performed on intra-process variation as well. In a real RF receiver, the sampling rate is limited due to the requirement for faster circuits and the ADCs have a finite resolution. The effect of the sampling rate in the baseband and the ADC resolution (quantization) has been explored in detail. A circuit design parameter, aspect ratio or W/L, has been varied and the whole study has been performed again for different W/L to gain more insight into how the process information is being transferred from the device level to the system level. This analysis and resulting constellation plots not only help us understand RF-PSF better but also aids in selecting the proper deep-learning method as well as offer some design control knobs that can be used to put the IC in test mode or normal operation mode (hence eliminating the performance trade-off in normal operation).

4

#### D. Our Contribution

1) In this work, for the first time, manufacturing processspecific properties or functions, manifested in the transmitted RF signal, are used to make a distinction among different process technologies. Using simulation data of an RF transmitter with QPSK modulation in 14 nm, 22 nm, and 65 nm processes, it has been shown that  $\sim 90\%$  accuracy can be achieved on average using a neural network with raw data, with a best-case accuracy of 99%.

2) Intra-process and inter-process variations are scrutinized in terms of time-domain signal, constellation diagram, and neural network performance using data from 5 different process corners (TT, FF, FS, SF, and SS) and 3 different process technologies.

3) The effect of two practical circuit limitations: baseband sampling rate and ADC resolution, has been addressed and their impact on detection accuracy has been analyzed.

4) Higher-order modulation (i.e. 64-QAM) has been used with RF-DAC PA structure that provides significantly more RF nonidealities. It is exploited to form a robust feature set.

5) The effect of a key design parameter, aspect ratio or W/L, has been explored in detail. The effect is discussed in terms of constellation plots. Using data from varying W/L along with some commonly used CNN architecture,  $\sim 100\%$  process distinction accuracy has been achieved.

# E. Organization of the Paper

The rest of the paper is structured as follows: Section II briefly discusses relevant works. Section III discusses the simulation methodology and data processing steps in detail. In section IV, we show the intra and inter-process distinction in time domain signal and constellation data and how that translates to NN accuracy. We also explore the effects of baseband sampling rate and ADC resolution. The conference paper version of this work [11] covers up to this point. The rest of the sections discuss additional works that improve process distinction accuracy from  $\sim 90\%$  all the way up to  $\sim 100\%$ .

Section V explains how we have used process-dependent distortion in higher order constellation to harness more process-specific information. The new PA (same RF-DAC architecture, modified for higher order modulation) structure has been explained with detailed parameter calculations and performance has been evaluated. In section VI, we have explored a circuit parameter, i.e. aspect ratio or W/L, which helps map the process information better at the system level. Using image-like constellations for different W/L in commonly used CNN structures, we have reached our targeted  $\sim 100\%$  accuracy. We have also explored the effect of environmental noise on RF-PSF performance. Finally, we conclude this work with a summary in section VII.

# II. RELATED WORKS

Due to the significant effect on circuit and system performance, manufacturing process variation has been studied extensively over decades [12]-[21]. With the scaling of feature size, the importance of process parameters and their impact is even more crucial now for modern processes [22]-[24]. The modeling and statistical distribution of process parameters have evolved vastly [25]-[27] with device scaling which paves the way for mapping a particular manufacturing process technology to extract process-specific signatures at the system level. Even for a particular feature size, process parameters and their distribution vary significantly from one fab house to another. This provides an opportunity to exploit the processdependent signature present in the transmitted electromagnetic signal of an RF transmitter in order to extract process information at the system level. This information can be used in sensitive and critical applications.

Sensitive networks face a wide attack surface which forced the defense agencies to adopt a "zero-trust" architecture [9]-[28]. Borrowing that concept to the semiconductor supply chain raises the issue of time and cost overhead for additional testing and requires low-power, cost-effective, time-saving methods. Among many specifications, process-related information can be found through the process-specific functions in the RF signal. As a byproduct, manufacturing process information is an important part of cloning (a counterfeiting method) detection as well [29], which requires time-consuming, costly physical and electrical tests [30]- [31]. Considering the heavy damages caused by counterfeiting, its detection and prevention have been a major research domain for decades. According to a review, counterfeits cost the industry more than \$100Bper year back in 2007 [32]. In 2010, the U.S. Department of Commerce released an assessment of counterfeit electronics on the defense industrial base (sponsored by the US Navy). The assessment shows an increase of 141% in counterfeit cases over four years [33]. The same assessment mentions that the US Government Accountability Office (GAO) had concluded that counterfeit electronics being sold as militarygrade were readily accessible for purchase via online vendors and the US military was vulnerable to counterfeit ICs via the Department of Defense (DoD) supply chain. A police raid on a suspected counterfeiter in China's Guangdong province found fake computer parts worth US \$1.2 million, which is enough to make computer servers and a lot of personal PCs [34].

5

### III. SIMULATION METHOD AND DATA PROCESSING

# A. Simulation Method

The transmitter (TX) is simulated in Cadence and the receiver (RX) is designed in MATLAB as shown in fig. 3(a). A 7-bit pseudo-random bit sequence (PRBS) is used to generate random bits at the rate of 10 Mbps. The serial bit stream is converted to 2-parallel streams (marked B0 and B1) which were modulated using a sine and a cosine carrier of 2.4 GHz to provide a QPSK modulated output signal. A low-power PA with  $50\,\Omega$  antenna impedance is used at the end of the transmitter chain which resonates at 2.4 GHz to produce the final RF output signal (shown in fig. 3(b)). The transient analysis is performed for a duration of 15 µs for five different process corners, namely: TT (typical-typical), FF (fast-fast), FS (fast-slow), SF (slow-fast), and SS. The simulation is done in 3 different process technologies, namely 65 nm technology (TSMC), 22 nm technology (GlobalFoundries), and 14 nm technology (GlobalFoundries). Collected data are then processed in MATLAB.

# B. Discarding Initial Transients to Focus on Steady State Signature

Fig. 3(c) shows that the received signal has initial transients that lead to phase irregularity and shape distortion. Simulated results benefit from initial transients that are significantly affected by the process variation but may not be available in real time. To analyze the steady-state operation and make RF-PSF more realistic, we discard the initial transients. For this purpose, initial 1  $\mu$ s is discarded from the 15  $\mu$ s data.

#### C. Edge Matching for DC Offset Correction

Shifting the wave along the time axis matches the rising edge of it with the reference clock, but the falling edge doesn't match as shown in the insets of fig. 3(d). This is because the output RF wave contains a certain DC offset. In this step, that offset is removed to make it a wave of 50% duty cycle.

JOURNAL OF LATEX CLASS FILES, VOL. X, NO. X, APRIL 2023

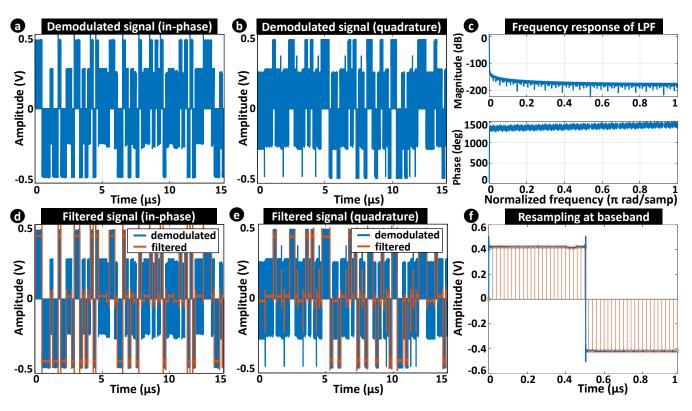

Fig. 4. (a) The received signal is multiplied by a sine wave to produce the in-phase demodulated signal. (b) The received signal is multiplied by a cosine wave to produce the quadrature-demodulated signal. (c) Frequency response of the designed low-pass filter (LPF). (d) In-phase filtered signal (the filtered envelope shown on top of the demodulated wave). (e) Quadrature filtered signal (the filtered envelope shown on top of the demodulated wave). (f) Resampling of the filtered wave at baseband. All the figures are produced for 65 nm technology with TT corner, sampling rate = 100 MHz, ADC resolution = 64 bit.

# D. Normalization to Avoid Process-independent Amplitude Variation

Different process technology has different supply voltage for optimum operation (For both 14 nm and 22 nm it's 0.8 V, for 65 nm it's 1 V). This difference in supply voltage already creates a difference between the processes based on signal amplitude. Since it is not a process-specific function, the RF signal is normalized to bring it in the range of 1 V. Fig. 3(e) shows the edge-matched and normalized wave with a reference sine clock.

#### E. Demodulation

Two reference clocks of  $90^{\circ}$  phase-difference (sine and cosine) and 2.4 GHz frequency are generated in MATLAB. The edge-matched and normalized RF signal is multiplied with the sine wave to produce the I-channel (in-phase channel) and with the cosine wave to produce the Q-channel (quadrature channel). Fig. 4(a) and fig. 4(b) show the I and Q channel respectively.

# F. Filtering

Fig. 4(c) shows the frequency response of a low-pass filter (LPF) that is designed using Hamming window. This is used to filter out the high-frequency RF components from the demodulated signal. Fig. 4(d) and fig. 4(e) show the filtered signals (envelopes) on top of the demodulated signals.

#### G. Resampling at Baseband

Fig. 4(f) shows the resampling of the filtered, baseband signal. The initial sampling rate of the received signal was high as it was in the high-frequency RF domain. The sampling rate is made even higher when it is interpolated. During the conversion from analog to digital domain, such a high sampling rate cannot be maintained. So, the filtered signal is sampled to convert it to a sampling rate of 100 MHz (10 times the original data rate). Later in subsection IV-A3, the effect of different sampling rates is explored in detail. The resampled I and Q channel data are plotted in the constellation diagram.

#### H. Neural Network

The resampled data are also used to train an artificial neural network. The raw I-Q samples in each quadrant are taken as features (2 I-Q points  $\times$  4 quadrants = 8 features). The feature set is divided into 70%, 15%, and 15% ratios for train, validation, and test purposes.

# IV. PROCESS DISTINCTION FOR QPSK

#### A. Intra-process Variation

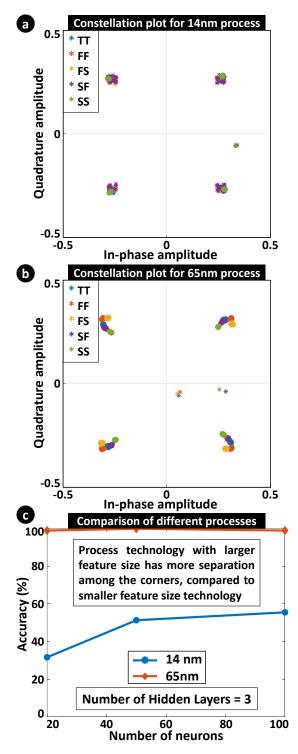

1) Comparison in Constellation Diagram: Fig. 5(a) and (b) shows the constellation plot for TT, FF, FS, SF, and SS corners of 14 nm and 65 nm respectively. It is observed that the larger feature-size process technology (65 nm) has a much larger variation. This is because larger feature-size technology has more delay and the percent variation of the delay for a fixed

Fig. 5. (a) Comparison of process corners of 14 nm process in the constellation diagram. (b) Comparison of process corners of 65 nm process in the constellation diagram. (c) Accuracy of process corner detection for both 14 nm and 65 nm processes. Sampling rate = 100 MHz, resolution = 64 bit.

data rate is higher. That's why the process corners show more variation for 65 nm compared to 14 nm.

2) Detection Accuracy: A simple NN with 3 hidden layers and a varying number of neurons per layer is trained with 5 target classes (each corner is considered a separate target class). Fig. 5(c) shows the intra-process detection accuracy

7

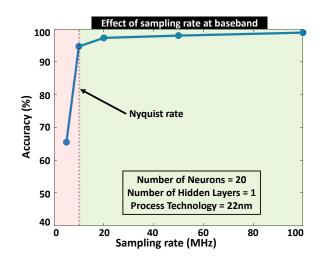

Fig. 6. Effect of different sampling rates at baseband. Below the Nyquist rate (light red region), the accuracy drops significantly. However, at or above the Nyquist rate (light green region), the accuracy remains high.

Fig. 7. Effect of quantization (ADC resolution) on detection accuracy. It is found that the accuracy remains almost unchanged even for 8 bit resolution.

for 14 nm and 65 nm process technology. The accuracy is very low for a smaller feature-size process like 14 nm but high for a larger feature-size process like 65 nm. This is expected from the constellation diagram as it is already observed that the 14 nm has less variation among corners compared to 65 nm.

3) Effect of Sampling Rate: Fig. 6 shows the effect of the sampling rate at the baseband. The original data rate is 10 Mbps, which reduces to 5 Mbps for each bitstream due to serial-to-parallel conversion. So, the Nyquist rate is 10 MHz. It can be seen that below the Nyquist rate, the accuracy drops significantly due to loss of information. However, at or above the Nyquist rate, the accuracy remains high.

4) Effect of Quantization: While processing in MATLAB, the data have 64 bit resolution by default. However, in actual ADC, it can be 8, 16, or 32 bits. So, it is important to see if our results hold for low resolution. Fig. 7 shows that even at 8 bit, accuracy remains almost unchanged. So, practical ADC resolution has a trivial impact on our results as long as it is  $\geq 8$  bits.

JOURNAL OF LATEX CLASS FILES, VOL. X, NO. X, APRIL 2023

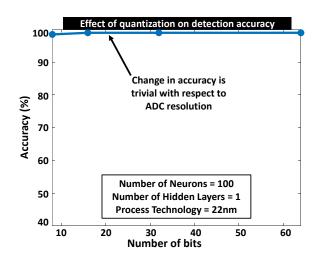

Fig. 8. (a) Comparison of the time domain received signal for 14 nm, 22 nm, and 65 nm processes (FF corner for each process). (b) Comparison of 3 processes in the constellation plot (5 corners from each process are plotted as one). (c) Detection accuracy of inter-process variation for different NN configurations. Sampling rate = 100 MHz, resolution = 64 bit.

# B. Inter-Process Variation

1) Comparison of the Received Signal: Fig. 8(a) shows the received signal in the time domain for all 3 processes (only FF corner is shown). A reference sine clock is also plotted for comparison. It is observed that the time domain signals can be distinguished based on amplitude and signal distortion.

2) Comparison in Constellation Diagram: Fig. 8(b) compares 3 process technology in terms of a constellation diagram. Here, all 5 process corner data are plotted as one combined group. It can be observed from the plot that, the 3 processes form distinct regions with some overlapping.

3) Detection Accuracy: Simple NN with a different number of hidden layers and neurons in each layer are trained with the constellation data. Fig. 8(c) shows the detection accuracy of 3 processes for different NN configurations. It can be observed that the accuracy is always > 80% and can reach up to 99%. But on average, it remains  $\sim 90\%$ .

# V. EFFICIENT PROCESS DISTINCTION USING HIGHER Order Modulation – 16 and 64-QAM

# A. Motivation

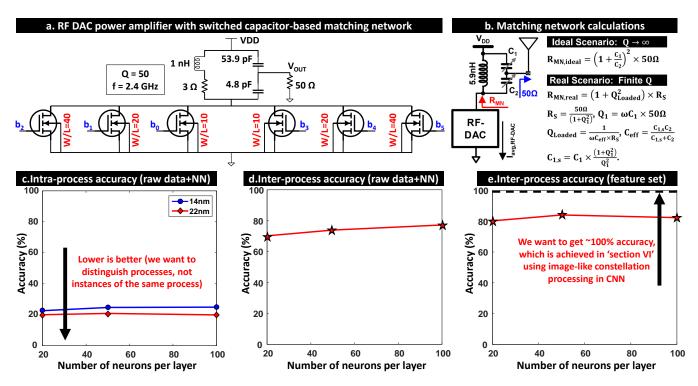

For higher-order modulation (16-QAM, 64-QAM, etc.), the outer constellation points suffer from phase noise or distortion due to power amplifier (PA) nonlinearity. This is dependent on the PA and in turn, depends on the process as well. This distortion or compression at higher order modulation can be exploited for process distinction as this is a function of the process. Hence, we switch to 64-QAM from QPSK. To that end, the same digital-friendly RF-DAC power amplifier has been used with switched capacitor-based matching network [35] and modified for higher-order modulation.

# B. Reconfigurable RF-DAC PA with Tapped Capacitor-based Matching Network

Figure 9(a) shows the reconfigurable power amplifier designed using RF-DAC architecture for 64-QAM, 16-QAM, QPSK, and OOK modulation (setting  $b_2$  and  $b_5$  signals to zero converts it to 16-QAM; setting  $b_2$ ,  $b_1$ ,  $b_4$  and  $b_5$  signals to zero converts it to QPSK; setting  $b_2$ ,  $b_1$ ,  $b_3$ ,  $b_4$  and  $b_5$  signals to zero converts it to OOK). It's a reconfigurable inverse class-D PA that eliminates the requirement of separate I and Q path DACs and Mixers. Further details on the design can be found in [35], [36]. The formulas for the switched capacitor matching network are shown in fig 9(b). We are designing the PA for a carrier frequency of 2.4 GHz. Here, an inductor of 1 nH with Q = 50 is taken. The calculation of other parameters is shown below:

$$\begin{split} f &= \frac{1}{2\pi\sqrt{LC_{eff}}} \\ \text{Hence, } C_{eff} = 4.4\,\text{pF} \\ \text{Now, } R_{MN} &= (1+50^2)\times 3 \\ \text{Or, Now, } R_{MN} = 7503 \\ \text{Again, } (1+\frac{C_1}{C_2})^2 &= \frac{R_{MN}}{50} \\ \text{Or, } C_1 &= 11.25C_2 \\ \text{Finally, } C_{eff} &= \frac{C_1C_2}{C_1+C_2} \\ \end{split}$$

Which leads to,  $C_1 = 53.9\,\text{pF}, C_2 = 4.8\,\text{pF}$

# C. Performance

1) Accuracy with Raw Constellation Data: Figure 9(c) shows the accuracy plot for intra-process variation. This accuracy is lower meaning less variation among corners which

JOURNAL OF LATEX CLASS FILES, VOL. X, NO. X, APRIL 2023

Fig. 9. (a) RF-DAC power amplifier with a matching network implemented using a switched capacitor. It's an inverse class-D PA that doesn't need a separate I and Q-path for DACs and mixers. (b) Formulas for matching network parameter calculation. (c) Intra-process detection performance using raw data fed to a NN. This accuracy is low, which is good for us. (d) Inter-process detection performance using raw data fed to a NN. Accuracy goes up to 80%, which is lower than expected. (e) Inter-process detection performance using a robust feature set along with a NN. The accuracy improves slightly, up to 85%, but there is still room for improvement.

is desired. However, figure 9(d) shows the accuracy plot for inter-process variation which is also in the range of 70 - 80% (low) that is not desired. It is apparent that the NN with raw constellation data is not good enough and we need to switch to some other method. To that end, we perform intuitive feature engineering to form a robust feature set.

2) Accuracy with Engineered Feature Set: We formulate 6 features based on intuition.

- $r_i$  and  $\theta_i$  are first two features where  $r_i$  = mean of radial distances of the data points for position i=1,2,...,64 and  $\theta_i$  = mean of angles of the data points for position i=1,2,...,64

- $\sigma_{ri}$  and  $\sigma_{\theta i}$  are the variances of  $r_i$  and  $\theta_i$ , and are used as two other features.

- EVM or Error vector magnitude  $((r_{mean} r_{ideal})/r_{ideal})$  for r and  $\theta$  are used as two other features.

In total 6 features for 64 positions form a 64x6 feature matrix. This matrix was fed into the NN for detecting accuracy. Figure 9(e) shows the accuracy of inter-process variation detection. The performance has improved. Previously, it was 70 - 80%, now it is 80 - 85%. However, there is still room for improvement. At this point, we want to look at the design parameters and gain insight from there to improve process detectability.

# VI. DESIGN PARAMETER EXPLORATION - W/L RATIO

# A. Simulation by Varying W/L

We switched to higher-order modulation to exploit the phase noise or compression. Since the W/L ratio controls current

flow and hence gain in the PA (as a result, the amount of distortion as well), we want to investigate it. For this work, each simulation is done for 4 different W/L ratios: 10, 20, 30, and 40. W is changed by changing the number of fingers. This has two advantages: (i) Since our PA structure uses parallel NMOS, finger number can be used as a control knob (controlled by gate voltage) for switching to different W/L at different modes of operation (test mode where the circuit is optimized for test or mission mode where the regular operation is done through the transmitter and RF-PSF is a byproduct) (ii) Processes have a different implementation, e.g. 14nm is FinFET. The width can be controlled by using the Fin number as well. To keep consistency among the processes, changing the number of fingers is the best approach.

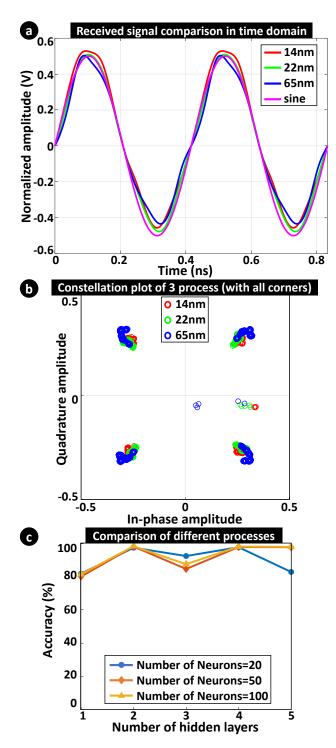

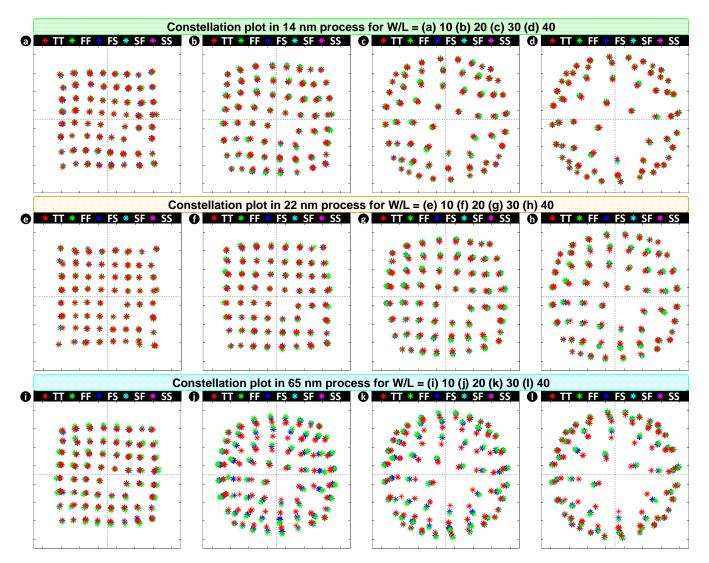

#### B. Constellation Plot Comparison

Fig. 10(a), (b), and (c) show the constellation plots for different W/L in 14nm, 22nm, and 65nm processes respectively (in each plot, all 5 process corners are plotted). Some interesting observations can be made from the comparison of the constellation plots. Firstly, if intra-process constellation plots are compared, it can be seen that compression or phase noise increases with increasing W/L, which is expected as higher W/L pushes the signal more toward the nonlinear region of the power amplifier. Secondly, if the inter-process comparison is made, it can be noticed that each process shows a different rate of change with W/L. For example, if W/L=20 is considered for each process, 14 nm shows slight compression, 22 nm shows trivial compression, and 65 nm shows strong

Fig. 10. Constellation plot for different W/L ratios for 14nm (Fig a-d), 22nm (Fig e-h), and 65nm (Fig i-l) processes. All 5 process corners are plotted in each figure.

compression. Finally, at high W/L, the compression is so high that the constellation plot becomes almost circular. At that point, regular data communication is not possible as that will cause high bit errors, but it can be used in the testing mode where the transmitted signal is being captured and analyzed only for testing purposes, not communication.

# C. Using CNN for Constellation Pattern

Since the constellation plots of the processes can be distinguished by visual inspection or from the images, we resort to an unorthodox approach of using convolutional neural networks (CNN) to classify the constellation plots. CNNs are quite good at finding patterns in images and are widely used for image classification [37]. Here, the legends and texts are removed from the constellation plots and used for training and testing.

We have used the *transfer learning* approach [38], [39], where some popular pretrained networks are taken and slightly modified to our needs. Here, both series and DAG (Directed Acyclic Graph) networks are used. The networks that have

been employed for training and testing purposes are VGG16 (16 layers deep series net), AlexNet (8 layers deep series net), ResNet18 (18 layers deep DAG), GoogleNet (22 layers deep DAG), and ResNet50 (50 layers deep DAG) [40]–[43]. The constellation images are augmented to match the input size requirement of each network and the final fully connected layer has been modified to provide 3 output classes. For training purposes, the stochastic gradient descent momentum (SGDM) method is used with a learning rate of 0.001 and batch size of 8. Images for W/L ratios of 30 and 40 were taken (constellations with the most compression and phase noise) as input data and they were divided into 2 datasets with an 80% - 20% ratio for training and testing purposes.

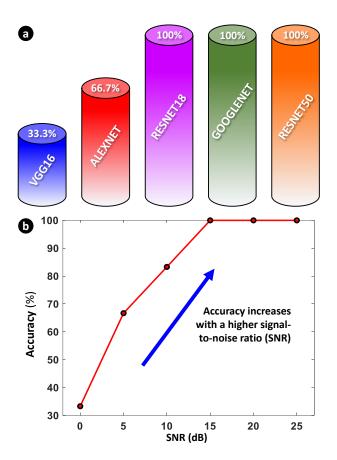

#### D. Performance Comparison using CNN

Fig. 11(a) shows the accuracy plot for each CNN. While the accuracy for simple series networks (AlexNet and VGG16) is not up to the mark, all the DAG networks provide 100% accuracy. This turns our visual analysis into a good quantitative performance result.

Fig. 11. (a) Performance comparison plot of a few popular CNNs (VGG16, AlexNet, ResNet18, GoogleNet, and ResNet50) trained and tested with constellation plots for different W/L. (b) Effect of environmental noise on RF-PSF performance. Low SNR causes low accuracy which quickly increases with improving SNR.

#### E. Effect of Noise on Accuracy

RF-PSF exploits process-dependent system-level nonidealities. However, environmental noise also generates system-level nonidealities which are process independent and random in nature. So far we have considered the ideal channel, however, the effect of environmental noise needs to be explored. For that purpose, White Gaussian Noise (WGN) has been added to the transmitted wave at different SNR levels. These signals have been processed just like before to test accuracy. For testing purposes, we have used GoogLeNet. Fig. 11(b) shows that the accuracy is low for 0 dB SNR. However, the accuracy improves quickly as the SNR improves and reaches 100% at 15 dB and beyond.

#### F. Future Works

The ultimate goal of RF-PSF is to distinguish between the two process technology of the same node from different fabrication houses (e.g. 22 nm Intel vs 22 nm GlobalFoundries). Due to the unavailability of two such nodes to us, we cannot pursue this goal at the moment and have kept it as a future work. Also, this work proves the concept of RF-PSF with simulation data. However, experimental validation is needed. Since RF-PSF is similar to RF-PUF (RF-PSF is process identity whereas RF-PUF is device identity), PSF properties (like PUF properties [6], [44]) need to be explored using experimental data. This is also kept as a future work.

#### VII. CONCLUSION

In this work, a novel process distinction method, RF-PSF, has been proposed and proved using simulation data. Process-dependent properties embedded in the transmitted RF wave have been used to make a distinction among 3 different process technologies: 14 nm (GlobalFoundries), 22 nm (GlobalFoundries), and 65 nm (TSMC). Using simulated data from Cadence and processing it in MATLAB, it has been shown that, for inter-process variation, 100% accuracy can be achieved using a DAG CNN fed with constellation data, whereas  $\sim 90\%$  accuracy can be achieved using multilayer perceptrons or artificial neural networks with raw data. An extensive study has been performed on intra-process variation using data for 5 process corners of each process technology and a comparison has been made in terms of the constellation and intra-process variation detection accuracy. A practical RF receiver is limited in terms of baseband sampling rate and ADC resolution. The effect of these two parameters along with the effect of environmental noise has been explored in detail. To conclude, the analysis of the time domain signals and constellation plot, along with performance evaluation using I-Q data in neural networks proves the existence of PSF in the RF domain which can be utilized as a zero-power overhead process distinction method.

#### ACKNOWLEDGMENT

This work was jointly supported by Air Force Research Laboratory (AFRL) via Centauri (now KBR) under the project 'RF-PSF' and National Science Foundation (NSF) under the 'SaTC Eager: Machine-Learning based Side-Channel Attack and Hardware Countermeasures' grant (grant no: 1935534).

#### REFERENCES

- S. Dongaonkar, S. P. Mudanai and M. D. Giles, "From Process Corners to Statistical Circuit Design Methodology: Opportunities and Challenges," in IEEE Transactions on Electron Devices, vol. 66, no. 1, pp. 19-27, Jan. 2019, doi: 10.1109/TED.2018.2860929.

- [2] K. J. Kuhn et al., "Process Technology Variation," in IEEE Transactions on Electron Devices, vol. 58, no. 8, pp. 2197-2208, Aug. 2011, doi: 10.1109/TED.2011.2121913.

- [3] A. Asenov and B. Cheng, "Modeling and simulation of statistical variability in nanometer CMOS technologies," Analog circuit design, Springer, Dordrecht, 2011. 17-33.

- [4] M. Orshansky, L. Milor and Chenming Hu, "Characterization of spatial intrafield gate CD variability, its impact on circuit performance, and spatial mask-level correction," in IEEE Transactions on Semiconductor Manufacturing, vol. 17, no. 1, pp. 2-11, Feb. 2004, doi: 10.1109/TSM.2003.822735.

- [5] L. -T. Pang and B. Nikolic, "Measurements and Analysis of Process Variability in 90 nm CMOS," in IEEE Journal of Solid-State Circuits, vol. 44, no. 5, pp. 1655-1663, May 2009, doi: 10.1109/JSSC.2009.2015789.

- [6] M. F. Bari, P. Agrawal, B. Chatterjee, and S. Sen, "Statistical Analysis Based Feature Selection Enhanced RF-PUF With >99.8% Accuracy on Unmodified Commodity Transmitters for IoT Physical Security," Frontiers in Electronics, vol. 3, Apr. 2022, doi: 10.3389/felec.2022.856284.

- [7] B. Chatterjee, D. Das, S. Maity and S. Sen, "RF-PUF: Enhancing IoT Security Through Authentication of Wireless Nodes Using In-Situ Machine Learning," in IEEE Internet of Things Journal, vol. 6, no. 1, pp. 388-398, Feb. 2019, doi: 10.1109/JIOT.2018.2849324.

- [8] M. F. Bari, B. Chatterjee, K. Sivanesan, L. L. Yang and S. Sen, "High Accuracy RF-PUF for EM Security through Physical Feature Assistance using Public Wi-Fi Dataset," 2021 IEEE MTT-S International Microwave Symposium (IMS), 2021, pp. 108-111, doi: 10.1109/IMS19712.2021.9574917.

- [9] "COVID-Related Telework Accelerates DISA's Zero-Trust Adoption," Dec. 1, 2020. Accessed on: Nov. 11, 2022. [Online]. Available: https://www.defense.gov/Explore/News/Article/Article/2431541/covidrelated-telework-accelerates-disas-zero-trust-adoption/

- [10] "THE COMMITTEE'S INVESTIGATION INTO COUNTERFEIT ELECTRONIC PARTS IN THE DEPARTMENT OF DEFENSE SUPPLY CHAIN," Nov. 8, 2011. Accessed on: Nov. 11, 2022. [Online]. Available: https://www.govinfo.gov/content/pkg/CHRG-112shrg72702/html/CHRG-112shrg72702.htm

- [11] M. F. Bari, B. Chatterjee, L. Duncan and S. Sen, "RF-PSF: Zero-Trust Radio Frequency Process Specific Functions as Process Distinction Method," 2022 IEEE/MTT-S International Microwave Symposium - IMS 2022, 2022, pp. 599-602, doi: 10.1109/IMS37962.2022.9865379.

- [12] W. Shockley, "Problems related to pn junctions in silicon." Czechoslovak Journal of Physics 11.2 (1961): 81-121.

- [13] J. Logan, "Statistical circuit design: Characterization and modeling for statistical design," Bell System Technical Journal 50.4 (1971): 1105-1147.

- [14] J. -B. Shyu, G. C. Temes and K. Yao, "Random errors in MOS capacitors," in IEEE Journal of Solid-State Circuits, vol. 17, no. 6, pp. 1070-1076, Dec. 1982, doi: 10.1109/JSSC.1982.1051862.

- [15] M. J. M. Pelgrom, A. C. J. Duinmaijer and A. P. G. Welbers, "Matching properties of MOS transistors," in IEEE Journal of Solid-State Circuits, vol. 24, no. 5, pp. 1433-1439, Oct. 1989, doi: 10.1109/JSSC.1989.572629.

- [16] A. N. Lokanathan and J. B. Brockman, "Efficient worst case analysis of integrated circuits," Proceedings of the IEEE 1995 Custom Integrated Circuits Conference, 1995, pp. 237-240, doi: 10.1109/CICC.1995.518176.

- [17] S. G. Duvall, "Statistical circuit modeling and optimization." 2000 5th International Workshop on Statistical Metrology (Cat. No. 00TH8489. IEEE, 2000.

- [18] S. Reda and S. R. Nassif, "Analyzing the impact of process variations on parametric measurements: Novel models and applications," 2009 Design, Automation & Test in Europe Conference & Exhibition, 2009, pp. 375-380, doi: 10.1109/DATE.2009.5090692.

- [19] H. F. Haneef, A. M. Zeidell and O. D. Jurchescu, "Charge carrier traps in organic semiconductors: a review on the underlying physics and impact on electronic devices," Journal of Materials Chemistry C 8.3 (2020): 759-787.

- [20] V. M. van Santen, J. Martin-Martinez, H. Amrouch, M. M. Nafria and J. Henkel, "Reliability in Super- and Near-Threshold Computing: A Unified Model of RTN, BTI, and PV," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 65, no. 1, pp. 293-306, Jan. 2018, doi: 10.1109/TCSI.2017.2717790.

- [21] A. D. J. De Meux, G. Pourtois, J. Genoe and P. Heremans, "Defects in amorphous semiconductors: the case of amorphous indium gallium zinc oxide," Physical Review Applied 9.5 (2018): 054039.

- [22] D. J. Frank, R. H. Dennard, E. Nowak, P. M. Solomon, Y. Taur and H. P. Wong, "Device scaling limits of Si MOSFETs and their application dependencies," in Proceedings of the IEEE, vol. 89, no. 3, pp. 259-288, March 2001, doi: 10.1109/5.915374.

- [23] R. Clark et al., "Perspective: New process technologies required for future devices and scaling." APL Materials 6.5 (2018): 058203.

- [24] Kwyro Lee et al., "The impact of semiconductor technology scaling on CMOS RF and digital circuits for wireless application," in IEEE Transactions on Electron Devices, vol. 52, no. 7, pp. 1415-1422, July 2005, doi: 10.1109/TED.2005.850632.

- [25] K. Takeuchi and M. Hane, "Statistical Compact Model Parameter Extraction by Direct Fitting to Variations," in IEEE Transactions on Electron Devices, vol. 55, no. 6, pp. 1487-1493, June 2008, doi: 10.1109/TED.2008.922491.

- [26] X. Wang et al., "FinFET Centric Variability-Aware Compact Model Extraction and Generation Technology Supporting DTCO," in IEEE Transactions on Electron Devices, vol. 62, no. 10, pp. 3139-3146, Oct. 2015, doi: 10.1109/TED.2015.2463073.

- [27] K. Ni, W. Chakraborty, J. Smith, B. Grisafe and S. Datta, "Fundamental Understanding and Control of Device-to-Device Variation in Deeply Scaled Ferroelectric FETs," 2019 Symposium on VLSI Technology, 2019, pp. T40-T41, doi: 10.23919/VLSIT.2019.8776497.

- [28] J. Barnett, "Air Force pushing 'mission-critical' applications to zero trust," Jan. 12, 2021. Accessed on: Nov. 11, 2022. [Online]. Available: https://www.fedscoop.com/air-force-zero-trust-missioncritical-frank-konieczny/

- [29] M. Pecht, "The counterfeit electronics problem," Open Journal of Social Sciences 1, no. 07 (2013): 12.

- [30] S. Bhanu, D. Das and M. Pecht. "Screening for counterfeit electronic parts," Journal of Materials Science: Materials in Electronics 22, no. 10 (2011): 1511-1522.

- [31] K. P. Pfeuffer et al., "Detection of counterfeit electronic components through ambient mass spectrometry and chemometrics," Analyst 139, no. 18 (2014): 4505-4511.

- [32] R. K. Lowry, "Counterfeit electronic components-an overview," in Military, Aerospace, Spaceborne and Homeland Security Workshop (MASH). 2007.

- [33] Z. A. Collier, S. Walters, D. DiMase, J. M. Keisler and I. Linkov. "A semi-quantitative risk assessment standard for counterfeit electronics detection," SAE International Journal of Aerospace 7, no. 2014-01-9002 (2014): 171-181.

- [34] M. Pecht and S. Tiku, "Bogus: electronic manufacturing and consumers confront a rising tide of counterfeit electronics," in IEEE Spectrum, vol. 43, no. 5, pp. 37-46, May 2006, doi: 10.1109/MSPEC.2006.1628506.

- [35] B. Chatterjee and S. Sen, "A 41.5 pJ/b, 2.4GHz Digital-Friendly Orthogonally Tunable Transceiver SoC with 3-decades of Energy-Performance Scalability," 2020 IEEE Custom Integrated Circuits Conference (CICC), 2020, pp. 1-5, doi: 10.1109/CICC48029.2020.9075915.

- [36] N. Cao et al., "A 65 nm Wireless Image SoC Supporting On-Chip DNN Optimization and Real-Time Computation-Communication Trade-Off via Actor-Critical Neuro-Controller," in IEEE Journal of Solid-State Circuits, vol. 57, no. 8, pp. 2545-2559, Aug. 2022, doi: 10.1109/JSSC.2022.3159473.

- [37] J. Wang et al., "CNN-RNN: A unified framework for multi-label image classification," proceedings of the IEEE conference on computer vision and pattern recognition. 2016.

- [38] S. J. Pan and Q. Yang, "A Survey on Transfer Learning," in IEEE Transactions on Knowledge and Data Engineering, vol. 22, no. 10, pp. 1345-1359, Oct. 2010, doi: 10.1109/TKDE.2009.191.

- [39] L. Torrey and J. Shavlik, "Transfer learning," handbook of research on machine learning applications and trends: algorithms, methods, and techniques. IGI global, 2010. 242-264.

- [40] K. Simonyan, and A. Zisserman, "Very deep convolutional networks for large-scale image recognition," arXiv preprint arXiv:1409.1556 (2014).

- [41] A. Krizhevsky, I. Sutskever and G. E. Hinton, "Imagenet classification with deep convolutional neural networks," Advances in neural information processing systems 25 (2012): 1097-1105.

- [42] C. Szegedy et al., "Going deeper with convolutions," proceedings of the IEEE conference on computer vision and pattern recognition. 2015.

- [43] K. He, X. Zhang, S. Ren, J. Sun, "Deep residual learning for image recognition," Proceedings of the IEEE conference on computer vision and pattern recognition. 2016.

- [44] V. Sehwag and T. Saha, "TV-PUF: A Fast Lightweight Analog Physical Unclonable Function," 2016 IEEE International Symposium on Nanoelectronic and Information Systems (iNIS), Gwalior, India, 2016, pp. 182-186, doi: 10.1109/iNIS.2016.049.

**Md Faizul Bari** is currently pursuing his Ph.D. in Electrical Engineering at Purdue University, West Lafayette, IN, USA. His research interests include wireless security, hardware security, radio frequency machine learning systems, etc. He completed his B.Sc.Engg. in Electrical and Electronic Engineering from Bangladesh University of Engineering and Technology, Dhaka, in 2017 and completed his M.Sc.Engg. from the same department in 2020. He worked as a Design Engineer at Neural Semiconductor Limited, Dhaka, Bangladesh for more than a year.

Later, he joined the University of Asia Pacific, Dhaka as a lecturer and worked there for almost a year before coming to the USA to pursue his doctoral study. He completed a successful summer internship in 2020 at Intel Labs. He received Deans' List Award and University Merit Scholarship from his alma mater during his undergrad. He is also a recipient of the Computer and Information Systems Fellowship (CISE) from Purdue University in 2019 and the Magoon Award for Excellence in Teaching in 2020.

JOURNAL OF LATEX CLASS FILES, VOL. X, NO. X, APRIL 2023

**Baibhab Chatterjee** (S'17, M'22) received his Ph.D. from the Elmore Family School of Electrical Engineering, Purdue University, West Lafayette, IN, USA in 2022. He is currently an Assistant Professor in the department of ECE, University of Florida, Gainesville, FL, USA. His industry experience includes two years as a Digital Design Engineer/Senior Digital Design Engineer with Intel, Bengaluru, India, and one year as a Research and Development Engineer with Tejas Networks, Bengaluru, India. He was a Quantum Hardware Design Intern with IBM

T.J. Watson Research Center, NY, USA during 2020-2021, where he worked on ultra-low power quantum receiver front-ends.

Dr. Chatterjee received the University Gold Medal from NIT, Durgapur, India, in 2011, the Institute Silver Medal from IIT Bombay in 2015, the Andrews Fellowship at Purdue University during 2017-2019, the HOST 2018 Best Student Poster Award (3rd), the CICC 2019 Best Paper Award (overall), the RFIC/IMS 2020 3MT Award (audience choice) and the Bilsland Dissertation Fellowship at Purdue University during 2021-2022. His research interests include low-power analog, RF, and mixed-signal circuit design for next-generation biomedical and quantum applications.

Lucas Duncan is the Chief Science Officer of Niobium Microsystems. He received his B.S., M.S., and Ph.D. degrees in electrical and computer engineering from the Ohio State University in 2009, 2012, and 2017, respectively. Dr. Duncan has over a decade of experience in the research and development of advanced integrated circuit designs spanning analog, RF, mixed-signal, and digital design domains. His research interests include high-performance mixedsignal circuits for direct-RF transceivers, digital beamforming, and hardware security.

Shreyas Sen is an Elmore Associate Professor of ECE & BME, Purdue University and received his Ph.D. degree from ECE, Georgia Tech. Dr. Sen has over 5 years of industry research experience in Intel Labs, Qualcomm and Rambus. His current research interests span mixed-signal circuits/systems and electromagnetics for the Internet of Things (IoT), Biomedical, and Security. He has authored/coauthored 3 book chapters, over 175 journal and conference papers and has 15 patents granted/pending. Dr.Sen serves as the Director of the Center for

Internet of Bodies( C-IoB). Dr. Sen is the inventor of the Electro-Quasistatic Human Body Communication(EQS-HBC), or Body as a Wire technology, for which, he is the recipient of the MIT Technology Review top-10 Indian Inventor Worldwide under 35 (MIT TR35 India) Award. His work has been covered by 250+ news releases worldwide, invited appearance on TEDx Indianapolis, Indian National Television CNBC TV18 Young Turks Program, NPR subsidiary Lakeshore Public Radio and the CyberWire podcast. Dr. Sen is a recipient of the NSF CAREER Award 2020, AFOSR Young Investigator Award 2016, NSF CISE CRII Award 2017, Intel Outstanding Researcher Award 2020, Google Faculty Research Award 2017, Purdue CoE Early Career Research Award 2021, Intel Labs Quality Award 2012 for industrywide impact on USB-C type, Intel Ph.D. Fellowship 2010, IEEE Microwave Fellowship 2008, GSRC Margarida Jacome Best Research Award 2007, and nine best paper awards including IEEE CICC 2019, 2021 and in IEEE HOST 2017-2020, for four consecutive years. Dr. Sen's work was chosen as one of the top-10 papers in the Hardware Security field (TopPicks 2019). He serves/has served as an Associate Editor for IEEE Solid States Circuits Letters(SSC-L), Frontiers in Electronics, IEEE Design & Test, Executive Committee member of IEEE Central Indiana Section and Technical Program Committee member of DAC, CICC, IMS, DATE, ISLPED, ICCAD, ITC, VLSI Design, among others. Dr. Sen is a Senior Member of IEEE.