IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES

# Sub-1-ms Instinctual Interference Adaptive GaN LNA Front End With Power and Linearity Tuning

Jie Yang<sup>®</sup>, Graduate Student Member, IEEE, Baibhab Chatterjee<sup>®</sup>, Member, IEEE,

Mohammad Abu Khater<sup>10</sup>, Senior Member, IEEE, Mattias Thorsell<sup>10</sup>, Member, IEEE,

Sten E. Gunnarsson<sup>10</sup>, Senior Member, IEEE, Tero Kiuru, Brian Edward, and Shreyas Sen<sup>10</sup>, Senior Member, IEEE

Abstract-One of the major challenges in communication, radar, and electronic warfare receivers arises from nearby device interference. This article presents a 2-6-GHz gallium-nitride (GaN) low-noise amplifier (LNA) front end with onboard sensing, processing, and feedback utilizing microcontroller-based controls to achieve adaptation to a variety of interference scenarios through power and linearity regulations. The utilization of GaN LNA provides high-power handling capability (30 dBm) and high linearity (OIP3 = 30 dBm) for radar and EW applications. The system permits an LNA power consumption to tune from 500 mW to 2 W (4× increase) in order to adjust the linearity from  $P_{1 \text{ dB,IN}} = -10.5$  to 0.5 dBm (>10× increase). Across the tuning range, the noise figure increases by approximately 0.4 dB. Feedback control methods are presented with backgrounds from control theory. The rest of the controls consume  $\leq 10\%$ (100 mW) of nominal LNA power (1 W) to achieve an adaptation time <1 ms.

*Index Terms*—Adaptive control, front end, gallium-nitride (GaN) low-noise amplifier (LNA), interference robust.

#### I. INTRODUCTION

WITH continuous advances in communication, radar, and electronic warfare (EW) technologies, the receivers (Rx) are becoming more susceptible to nearby interferences. Unlike the intentional jamming that deliberately saturates the Rx system to produce an unusable signal, unintentional interferences are more prevalent, such as self-interference, and adjacent channel interference and reflection by neighboring devices [2], [3]. To combat unintentional interferences, some of today's Rxs are designed to operate in the worst case condition at the cost of extra power consumption. When the radar and EW Rxs are implemented in large arrays, the extra power consumption can quickly add up and may require extra cooling. The increasing interferences caused extra power

Manuscript received 15 February 2023; accepted 19 February 2023. This work was supported in part by SAAB AB, Sweden, and in part by SAAB Inc., USA. This article is an extended version of the MWCL Paper [1]. (*Corresponding author: Jie Yang.*)

Jie Yang, Mohammad Abu Khater, and Shreyas Sen are with the Department of Electrical and Computer Engineering, Purdue University, West Lafayette, IN 47907 USA (e-mail: yang1122@purdue.edu; shreyas@purdue.edu).

Baibhab Chatterjee is with the Department of Electrical and Computer Engineering, University of Florida, Gainesville, FL 32611 USA.

Mattias Thorsell, Sten E. Gunnarsson, and Tero Kiuru are with SAAB AB, 16484 Stockholm, Sweden (e-mail: mattias.thorsell@saabgroup.com).

Brian Edward, Retired, was with SAAB Inc., Orlando, FL 13057 USA. Color versions of one or more figures in this article are available at https://doi.org/10.1109/TMTT.2023.3248957.

Digital Object Identifier 10.1109/TMTT.2023.3248957

consumption calls for an adaptive interference-tolerant lowpower RF Rx system.

1

The first step to the adaptive interference-tolerant low-power RF Rx system especially in the radar and EW Rxs is the ability to sustain a high input level. Gallium-nitride (GaN) low-noise amplifiers (LNAs) have been widely used due to their higher power handling capabilities (>30 dBm) than traditional GaAs or CMOS LNAs (20 dBm). Traditional LNAs usually require the implementation of a limiter in the input path for protection from high input power, while the GaN LNA is able to function standalone [3]. The next step is the ability to adjust the Rx power consumption according to the input power as opposed to continuous operation under worst case conditions. Operation of the Rx system in the low-power mode can significantly reduce the power consumption and the need for cooling when the input is small in a large radar and EW Rx array.

# A. Background of Adaptive Receivers and Related Works

In the effort of achieving a low-power and interference adaptive Rx, some previous works have focused on linearizing mixers using frequency translation by compressing third-order intermodulation product (IM3) [4], [5], [6]; however, if the LNAs are already saturated, linearizing the later stages gains little advantage. Other works contributed to creating ultralow-power LNA using the current reuse and forward body biasing techniques [7], [8], [9], variable-gain LNA [10], [11], [12], an orthogonally tunable LNA where input third-order intercept point (IIP3) and gain can be individually changed through the bias tuning knobs [13], or a combination of low-power and variable-gain LNA [14]. The variable gain and IIP3 in the design of LNA can assist the Rx to become more interference tolerant in terms of both large signal saturation and small signal nonlinearity; however, these works only included circuit-level designs without a complete system design. With the purpose of developing an adaptive Rx, dynamic bias (tuning of the gate and drain voltage) for the optimization of the signal-to-noise and distortion ratio (SNDR) for a GaN LNA is explored in [15]; however, the system-level considerations for the dynamic bias technique were not included.

Banerjee et al. [16] utilized the orthogonally tunable LNA to implement a use-aware adaptive RF transceiver system where different low-power adaptation modes are designed for

0018-9480 © 2023 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

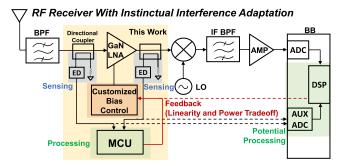

Fig. 1. Block diagram for RF Rx with instinctual interference adaptation.

different throughput requirements but disregard the tuning speed of the Rx. Other implementations of an adaptive RF communication system use error vector magnitude (EVM) and lookup table (LUT) with stored tuning conditions for the LNA and mixer to optimally trade off power and performance [17]. Advancements were made later by considering the process variation of the components with tuning adjustments included in the design process [18]. These contributions provide a thorough design of the Rx system, but most of the results are still simulation-based, and utilization of only the LUT does not provide local feedback for further tuning of the system.

Other adaptive systems with the implementation of COTS, IC, or simulation can be found in [19], [20], [21], [22], [23], [24], [25], [26], and [27].

# **B.** Proposed Solution

This article presents the first building block, a high input tolerant and interference adaptive GaN LNA front end, to an instinctual adaptive Rx. Fig. 1 modifies the traditional RF Rx with the instinctual interference adaptation by incorporating: 1) sensing through the onboard envelope detectors (EDs) as observation points at the input and/or output of the GaN LNA; 2) processing through localized digital processing unit or the auxiliary analog-to-digital converter (ADC) that is already present in baseband (BB); and 3) feedback to the customized GaN LNA bias controls for the best linearity and power performance while maintaining signal integrity. Note that, in this article, the processing is done using an MCU, but it can also be done using the BB DSP and auxiliary ADC. When blockers are present in a traditional Rx system working in nominal conditions, the blockers would saturate the LNA and produce a comparable IM3 to the actual signal, which results in an undecidable LNA output. When blockers are present in the front end with instinctual interference adaptation, the control logic would be able to increase the linearity of the system, which, in turn, increases the IM3 compression at the cost of power consumption. When the signal and interference are both low, the Rx with bias control would be consuming less power for approximately the same signal levels. Note that the need for a better linearity range is present regardless of whether the high power is from the desired signal or the interference as long as the system is able to be brought back to the linearity range.

To have a higher power handling capability and linearity, GaN LNA is utilized. Our prior work [1] involves interference adaptation for an Rx system with incremental adaptation control involving both feedforward and feedback path for the GaN LNA. However, the utilization of bench-top equipment significantly increases the adaptation time and the form factor of the system, which makes the design unsuitable in real life. Yang et al. [1] also lack consideration of the effects of the GaN LNA properties.

This article builds upon the prior work and has the following additional contributions.

- This work implements the first sub-1-ms interference adaptive, instinctual GaN LNA system with a localized in-built intelligence using a microcontroller. The system consumes ≤10% of nominal LNA power to provide a wide tuning range of linearity for about 11 dB and LNA power for 0.5–2 W.

- The control circuitry of GaN LNA has been designed with careful consideration of the high-power effects of GaN LNA and the tradeoff between system adaptation time and device lifetime.

- 3) Background control theory of the system is provided on the limitations for the overall adaptation time (<1 ms), which shows a high correlation with the measurement results. To the best of our knowledge, this is the first control theory introduced for an interference adaptive RF front end system.

- 4) Important tradeoffs are presented between two designs:

a) feedforward + feedback using control theory mentioned in Section IV-E and b) feedback only using:

i) incremental adaptation; ii) LUT; and iii) one-shot + incremental adaptations. The different designs illustrate different timing constraints and complexities for different applications.

This article is organized as follows. Section II provides an overview of the control loops and component characterization. Section III investigates different design considerations, such as the design of directional coupler, high input power effects for a GaN LNA, the gate voltage ( $V_G$ )-based tuning method, and design comparison. Section IV describes the three control methods and the control theory. Section V presents the measurement results. Section VI presents the future directions of this work.

# II. HARDWARE DESCRIPTION AND CHARACTERIZATION

#### A. System Architecture and PCB Designs

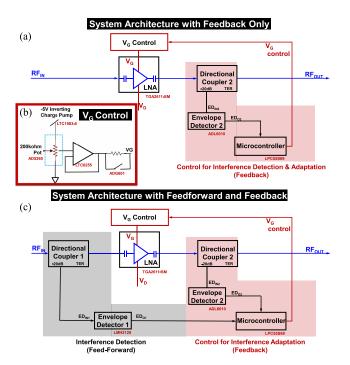

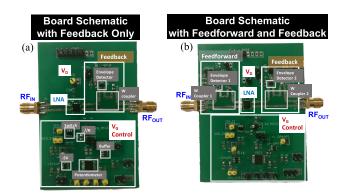

The two-layer PCB utilizes Rogers 4003C material with a thickness of 0.508 mm. The signal lines are carefully matched to 50  $\Omega$ . The system architectures are shown in Fig. 2 with associated board layouts shown in Fig. 3. The commercial off-the-shelf (COTS) parts used on the PCBs are listed in Table I. Figs. 2(a) and 3(a) show the architecture and layout for the feedback-only design where the interference detection and adaptation are performed in the feedback loop that utilizes an ED to sample the output of the LNA. The bias control circuitry for the LNA is shown in Fig. 2(b). Figs. 2(c) and 3(b) show the architecture and layout for the feedback design. The feedforward loop involves the use of envelope detector 1 (ED1) that is higher in sensitivity than envelope

Fig. 2. (a) System architecture with feedback-only controls. (b)  $V_G$  control circuitry. (c) System architecture with feedforward and feedback controls.

Fig. 3. (a) Board schematic with feedback-only controls. (b) Board schematic with feedforward and feedback controls.

detector 2 (ED2) used in the feedback loop while still being able to sustain the maximum input signal limited by the rating of the LNA at 30 dBm (1 W). The difference between the two designs is how the interference will be detected (through the feedforward and feedback path, or directly from the feedback path), which will be discussed more in Section IV.

The directional couplers and the LNA form the front end in the system that will be connected to a mixer and BB stages in a standard RF Rx. For a combined feedforward and feedback system, RF input first passes through the port of the directional coupler 1 to the LNA, while the coupling port enables ED1 to measure the input signal level. Directional couplers are necessary for measurement because of the physical constraints (power handling capability) of the EDs and to avoid a significant power divide from the LNA. If the input signal is high (i.e., a blocker), then ED1 will output a higher dc voltage. The assumption is that high-level input signals are only caused by the interference and not the desired signal;

| COMPONENT SPECIFICATIONS |              |                                                                              |  |  |  |  |  |

|--------------------------|--------------|------------------------------------------------------------------------------|--|--|--|--|--|

| Component                | Part Number  | Specifications                                                               |  |  |  |  |  |

| GaN LNA                  | TGA2611-SM   | 2-6GHz, 1dB NF, 22dB Gain,                                                   |  |  |  |  |  |

|                          | (Qorvo) [28] | -4dBm P <sub>1dB,IN</sub> , 1W nominal power                                 |  |  |  |  |  |

| Envelope                 | LMH2120      | 0.05-6GHz, $7\mu$ s $t_{rise}$ , 2.9mA                                       |  |  |  |  |  |

| Detector 1               | [29]         | $0.032 \text{V-}1.1 \text{V} \qquad \text{V}_{\text{out}}, \qquad 50 \omega$ |  |  |  |  |  |

|                          |              | $P_{IN}$ =-40 $\sim$ 12dBm                                                   |  |  |  |  |  |

| Envelope                 | ADL6010 [30] | 0.5-43.5GHz, $47\mu s$ t <sub>rise</sub> ,                                   |  |  |  |  |  |

| Detector 2               |              | $1.6 \text{mA}, 0.01 \text{V}-3 \text{V} \text{V}_{\text{out}}, 50 \Omega$   |  |  |  |  |  |

|                          |              | $P_{IN}$ =-30~15dBm                                                          |  |  |  |  |  |

| -5V                      | LTC1983-5    | -5V V <sub>out</sub> , 25µA                                                  |  |  |  |  |  |

| Inverting                | [31]         |                                                                              |  |  |  |  |  |

| Charge Pump              |              |                                                                              |  |  |  |  |  |

| Digitally                | AD5260 [32]  | 200k $\Omega$ , dual-supply, 256taps,                                        |  |  |  |  |  |

| Programmed               |              | 4-wire SPI, 0.3mW, $t_{settling}=5\mu s$                                     |  |  |  |  |  |

| Potentiometer            |              |                                                                              |  |  |  |  |  |

| Operational              | LTC6255 [33] | $60\mu$ A, 6MHz GBP, 1.5V/us,                                                |  |  |  |  |  |

| Amplifier                |              | $2.5\mu Vpp e_{ni}$                                                          |  |  |  |  |  |

| Switch                   | ADG601 [34]  | 2.50hm, 1 $\mu$ A, 80ns t <sub>on</sub> , 45ns t <sub>off</sub> ,            |  |  |  |  |  |

|                          |              | N.O., -60dB off isolation                                                    |  |  |  |  |  |

| Micro-                   | LPC55S69     | 16bit ADC, 1MHz f <sub>sample (ADC)</sub> , SPI                              |  |  |  |  |  |

| controller               | [35]         | support, 150MHz f <sub>CLK</sub>                                             |  |  |  |  |  |

TABLE I

thus, high input signal corresponds to a high interference level. ED2 in the feedback path will also be incorporated in the interference detection for a better sensitivity after the LNA gain. The measurement will be processed through the ADC on the microcontroller; if the microcontroller determines the adaptation of the LNA that is needed, tuning control will be initiated. The feedback control adjusts the gate voltage ( $V_G$ ) of the LNA to achieve the high linearity for the LNA, which will be further discussed in Section IV. Note that the drain voltage ( $V_D$ ) of the LNA is not being controlled because the linearity improvement is minimal with changing  $V_D$  for the specific LNA presented; however,  $V_D$  controllability can be considered for future improvements on other LNAs. The difference with a feedback-only system is that the presence of interference will only be detected using ED2 in the feedback loop.

#### B. Characterization of Components

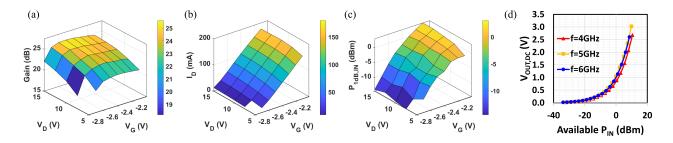

The components used are described in Table I. The LNAs in both the MWCL [1] and this article are the same part number, but there are some chip-to-chip variations such that, with the same  $V_G$ ,  $I_D$  is higher in this article. Note that the characteristics of the GaN LNA are determined more by the current rather than the bias voltage. This is because diodes are important in the GaN LNA modeling, and biasing the diode current with the correct voltage is more important [36]. We decided to continue with the  $V_G$  range of -2.7 to -2.2 V with a higher  $I_D$  due to a worse S11 response at  $V_G < -2.7$  V, as shown in Section V-C. The feedforward and feedback path components are characterized in the 2-6-GHz range. The losses due to the SMA cables are calibrated during the characterization of the RF components and measurements thereafter. RF components are chosen to have an input impedance of 50  $\Omega$ . Fig. 4(a)–(c) represents the behavior of a GaN LNA at 4 GHz. As LNA's  $V_G$  increases from -2.8 to -2.2 V, the gain first increases and saturates at around -2.5 V and then starts to decrease. The

IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES

Fig. 4. Measured performance characterization of the components used: (a) LNA gain versus  $V_D$  and  $V_G$  at 4 GHz (weak function of both  $V_D$  and  $V_G$ ), (b) LNA drain current ( $I_D$ ) versus  $V_D$  and  $V_G$  at 4 GHz (weak function of both  $V_D$  and strong function of  $V_G$ ), (c) LNA input  $P_{1 \text{ dB}}$  ( $P_{1 \text{ dB},\text{IN}}$ ) versus  $V_D$ and  $V_G$  at 4 GHz (weak function of both  $V_D$  and strong function of  $V_G$ ), and (d) dc output voltage of the ED2 at the output of the LNA versus available input power to the ED.

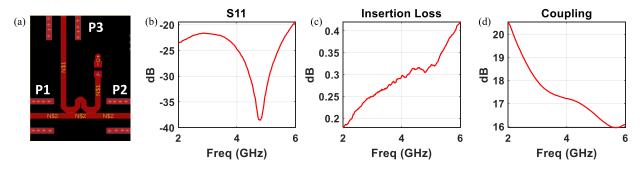

Fig. 5. W-shaped coupler: (a) schematic, (b) S11, return loss, (c) S21, insertion loss, and (d) coupling.

gain also increases with increasing  $V_D$ . Because the change in gain is less than 4 dB (neglecting the -2.8-V V<sub>G</sub> data due to low gain and  $P_{1 \text{ dB,IN}}$ , the adaptation will be between  $V_G = -2.7$  and -2.1 V), the LNA gain is a weak function of both  $V_D$  and  $V_G$ . The supply current  $(I_D)$  increases by more than 100 mA with increasing  $V_G$  while having a small change with increasing  $V_D$ . This makes LNA's  $I_D$  a strong function of  $V_G$  and a weak function of  $V_D$ . The input  $P_{1 \text{ dB}}$  ( $P_{1 \text{ dB,IN}}$ ) of the LNA varies around 16.5 dBm with increasing  $V_G$  but changes minimally with  $V_D$ . This makes the LNA's  $P_{1 \text{ dB,IN}}$  a strong function of  $V_G$  and a weak function of  $V_D$ . Therefore, only  $V_G$  will be changed to achieve linearity, while  $V_D$  is fixed at 10 V. Note that, if the LNA's  $P_{1 \text{ dB,IN}}$  response is both a strong function of  $V_G$  and  $V_D$ , or if the LNA's gain is a strong function of  $V_D$ , both  $V_G$  and  $V_D$  can be implemented in the control loop.

Fig. 4(d) represents the behavior of ED2 at frequencies of 4, 5, and 6 GHz. The voltage output of ED2 increases exponentially with increasing power. ED1 is chosen to be able to detect low-power levels at the input. Other controlling components listed in Table I are generally chosen to be low power, short settling and rising times, and low noise.

# **III. DESIGN CONSIDERATIONS**

# A. Directional Coupler Design

In our prior work [1], we utilized COTS directional coupler components to provide the measurement path; however, even though the components have outstanding specs, the integration of the directional coupler with the PCB board is causing unwanted reflections from the soldering and the abrupt transition from the trace to the component. Consequently, this article takes advantage of the onboard microstrip design for the directional coupler, which avoids extra transition from the board to the component. The coupler is necessary for decreasing the power input to below the power limit of the ED and not to diverge extra power from the signal path for measurement purposes. The microstrip directional coupler schematic is shown in Fig. 5(a) [37]. The measurements for the directional coupler are shown in 5(b)–(d). S11 shows low return loss with measurements below -19 dB over the frequency from 2 to 6 GHz. The insertion loss (S21) increases from 0.18 to 0.42 dB with frequency. The coupling (S31) changes from 20.5 to 16 dB over the bandwidth.

#### B. GaN LNA Considerations for High-Power Input

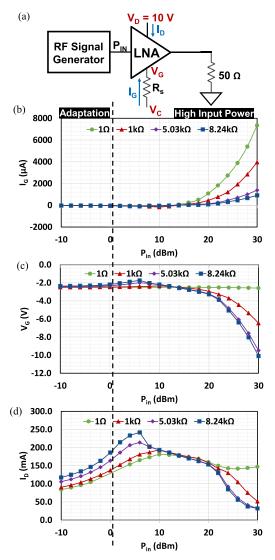

Unlike the typical GaAs LNA's lifetime being limited by the breakdown voltage, GaN LNA is limited by high dc gate current and drain–gate voltage ( $V_{DG}$ ). Characteristics of a GaN LNA with high input power have been investigated in [38]. Similar characteristics have been presented for the LNA used in this article in Fig. 6.

Fig. 6 describes  $I_G$ ,  $V_G$ , and  $I_D$  versus different input powers with different resistor values in series ( $R_S$ ) at the gate bias of the LNA with the setup in Fig. 6(a). The frequency has been set at 2 GHz for the worst case scenario. As shown in the plots in Fig. 6(b)–(d), low-power characteristics are very different than the high-power characteristics. In the low-power region or the adaptation range,  $I_G$  is actually negative causing  $V_G$  to tail up due to  $R_S$ , and with Ohm's law, when  $I_G$  is flowing out of the gate,  $V_G$  is higher than the control voltage ( $V_C$ ). Because of the higher bias in  $V_G$ ,  $I_D$  is also drawing more current. With increasing in  $R_S$ ,  $V_G$  tails up higher,

Fig. 6. 2-GHz LNA at  $V_G = -2.5$  V and  $V_D = 10$  V data with various series resistors at the bias gate node of the LNA for (a) LNA high-power measurement set up, (b)  $I_G$  versus  $P_{\rm IN}$  adjusted for cable loss, (c)  $V_G$  versus  $P_{\rm IN}$ , and (d)  $I_D$  versus  $P_{\rm IN}$ .

and  $I_D$  also reaches a higher point. When the input power transitions to the high-power region,  $I_G$  becomes positive and starts to increase exponentially. As a result of  $I_G$  becoming more positive,  $V_G$  starts to drop off exponentially with  $I_D$  also dropping. With increasing in  $R_S$ ,  $I_G$  increases more gradually which protects the LNA. Even though  $V_G$  drops to about -10-V range, it is not significant to cause the LNA to break down. The typical critical value for  $V_{DG}$  causing degradation in LNA performance is 30 V, where, if  $V_D$  is 10 V (used in this article), the minimum  $V_G$  is -20 V [39].

The characteristics of  $I_G$  with varying  $P_{\rm IN}$  is explained by the Shockley contact at the gate and source of a GaN highelectron-mobility transistor (HEMT). A GaN LNA model can be found in [36]. The Shockley contact is essentially a diode; consequently, at low-power levels, the gate experiences a small leakage current. At high-power levels, the diode is turned on, and  $I_G$  increases exponentially [40].

Another effect of the GaN LNA is the trapping effect on the gain recovery after a pulse of high input signal [3].

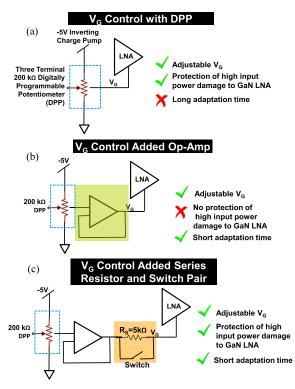

Fig. 7. (a)  $V_G$  controller with only the DPP, (b)  $V_G$  controller with a DPP with a buffer, and (c) current  $V_G$  controller design with buffer, and resistor and switch pair to accommodate both low and high input power to the LNA.

This effect happens much higher than the adaptation range  $(P_{\rm IN} > 25 \text{ dBm})$ ; thus, during the pulse, the system can be tuned at the maximum possible linearity. When the high input signal is removed, the slow gain recovery does not affect the detection that the input signal is now minimal and returns back to the low-power mode.

### C. Bias Control

To protect the GaN LNA against the high input power characteristics and provide reasonable adaptation time, the current design for tuning  $V_G$  of the LNA is proposed in Fig. 7(c). The microcontroller will be configuring the digitally programmable potentiometer (DPP), which is supplied by a -5-V inverting charge pump for the negative  $V_G$  bias. Following the DPP is a buffer and a parallel structure of a resistor and switch for the control of  $I_G$ .

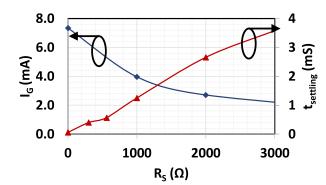

The process for the current design in tuning the  $V_G$  is shown in Fig. 7. Fig. 7(a) considers the case when there is only a DPP connected directly to the gate of the LNA. The drawback of this design is shown in Fig. 8. As  $R_S$  to the gate of the LNA increases, the gate current is suppressed, but the settling time increases. Since the DPP is in the 100-k $\Omega$  range, the high series resistance causes a high RC time constant, which increases the settling time ( $T_S$ ) significantly. The increase in  $T_S$  would, in turn, increase the adaptation time to tens of milliseconds, which is undesirable when one of the goals is to constraint the timing in the millisecond range. To solve the  $T_S$  problem, a buffer is added, as shown in Fig. 7(b), which essentially reduces  $R_S$  to decrease  $T_S$ ; however, as discussed in Section III-B, the reduced  $R_S$  draws more  $I_G$  in high power, which minimizes the device lifetime.

Fig. 8. 2-GHz data at  $V_G = -2.5$  V and  $V_D = 10$  V for the tradeoff of  $I_G$  and settling time versus different series resistor values.

Fig. 9. Conceptual diagram for the gain of the system versus  $P_{\text{IN}}$ . The input signal moves from the nonlinear region to the linear region of the system by increasing  $V_G$  from -2.7 to -2.5 V.

To balance the  $I_G$  and  $T_S$  tradeoff, a parallel resistor–switch pair is added in the current design, as shown in Fig. 7(c). During the low-power and adaptation regions in Fig. 6(a),  $I_G$ is low in the sub-mA region, so the switch can be closed to construct the low-resistance path for tuning  $V_G$  to improve  $T_S$ . After the adaptation, the switch will remain closed to maintain a steady bias condition; on the other hand, if the switch opens to place  $R_S$  in the path,  $V_G$  would increase, as shown in Fig. 7(b), and change the bias condition, which consumes more power. In the high-power region, lower  $I_G$  is more prominent since  $V_G$  is set to -2.1 V directly without the adaptation, so  $T_S$  can be traded for lower  $I_G$  with the switch being open and resistor in series.

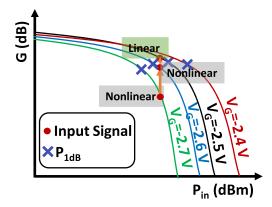

#### D. Linearity Decision Making in Incremental Adaptation

Due to the variable gain behavior of the LNA with changing  $V_G$ , the ED2 measurements at the output of the LNA are also affected. The gain of the LNA first increases with increasing  $V_G$  and then decreases after  $V_G \approx -2.5$  V in Fig. 4(a). Fig. 9 shows that the linear region occurs where the gain of the system remains relatively constant before the 1-dB compression point ( $P_{1 \text{ dB}}$ ), and the nonlinear region occurs where the system is highly compressed beyond  $P_{1 \text{ dB}}$ . Even though the gain varies with increasing  $V_G$ . When a high input signal presents in the

IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES

Fig. 10. 3-GHz data for the output power of the LNA versus  $V_G$  at different input power levels and the  $P_{1 \text{ dB}}$  points signifying the expected  $V_G$  to bring the system back to linearity for each input power. The determining steps show how the threshold applied in the control logic is decided.

system at  $V_G = -2.7$  V, the signal is highly gain compressed, and the system is highly nonlinear. To linearize the system,  $V_G$  increases in 0.1-V increments. When  $V_G$  increases from -2.7 to -2.6 V, the signal becomes less gain compressed, but the system remains nonlinear. To further improve the system linearity,  $V_G$  is increased to -2.5 V. The idea of incrementing  $V_G$  to improve linearity forms the basis of the incremental adaptation in Section IV-A.

Fig. 10 shows  $P_{OUT}$  versus  $V_G$  tuning with respect to different  $P_{IN}$ 's.  $P_{1 dB}$ s are also shown to show that  $V_G < V_{P_{1 dB}}$  results in a nonlinear system. As  $P_{IN}$  increases, the  $V_{P_{1 dB}}$  also increases. As  $V_G$  is tuning, the gain of the LNA increases and then decreases, as shown in Fig. 4(a). Due to the effect of LNA gain with different VG and LNA transitioning from nonlinear to linear, the determining step decreases with  $P_{IN}$  increase. Therefore, to accommodate the difference in determining steps in both high and low  $P_{IN}$  across different frequencies, a lower determining step is chosen as the linearity threshold, which has a drawback of overestimation of  $V_G$  for lower  $P_{IN}$  values. One may suggest that different threshold limits can be used with different  $P_{IN}$  values, but this again creates a case-dependent threshold that may not work in other frequencies.

# IV. CONTROL MECHANISMS FOR ADAPTATION

Figs. 11–13 present three control methods in the feedbackonly configuration.

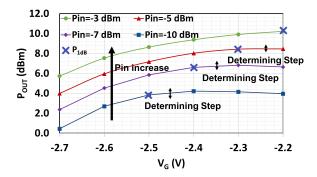

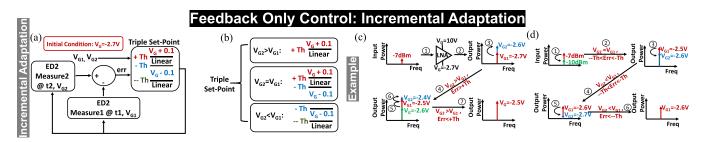

#### A. Incremental Adaptation Control Logic

Fig. 11(a) describes the control method with incremental adaptation. The LNA is initially in the low-power mode, with  $V_G$  being initially set at -2.7 V, and ED2 will perform the initial measurement at time instance 1 (t1) as the reference. When interference reaches the system, another ED2 measurement at time instance 2 (t2) is taken as the current value. The difference (err) between the current and reference of ED2 is compared with a set of thresholds to start the feedback control. The set of thresholds can be regarded as an extended version of bang-bang control as the triple set-point control in Fig. 11(b). The triple set-point has three different conditions: when  $V_{G1}$  at t1 is the same as  $V_{G2}$  at t2, the resulting action

Fig. 11. (a) Incremental adaptation logic for feedback-only control. (b) Triple set-point breakdown for different  $V_G$  cases. (c) Example of the incremental adaptation when a detectable interference presents. (d) Example of the incremental adaptation when interference level decreases.

Fig. 12. (a) LUT logic for feedback-only control. (b) LUT mapping for different  $V_G$ 's and input powers. (c) Example of the LUT adaptation when a detectable interference presents. (d) Example of the LUT adaptation when interference level decreases.

is increment  $V_G$  by 0.1 V if the err is greater than the positive threshold (+Th), decrement  $V_G$  by 0.1 V if the err is less than the negative threshold (-Th), or maintain the same  $V_G$ if the err is between +Th and -Th; when  $V_{G2}$  is greater than  $V_{G1}$  (VG is incrementing), the err is compared only to the +Th such that  $V_G$  increments when err is greater than +Th (gain compression observed) or returns to  $V_{G1}$  when err is less than +Th (linear); and when  $V_{G2}$  is less than  $V_{G1}$  (VG is decrementing), the err is compared with the -Th and a more negative threshold (-Th) such that  $V_G$  decrements to find the optimum  $V_G$  when the err is in between the thresholds (still in the linear region), or returns to  $V_{G1}$  when the err is less than the -Th (gain compression observed). An example of the incremental adaptation is shown in Fig. 11(c). When the interference is detected,  $V_G$  will start incrementing until err is less than the +Th. Another example of when the interference signal changes are shown in 11(d). When the interference level decreases,  $V_G$  also starts to decrement until err is less than -Th. Note that, if the interference level drops a significant amount,  $V_G$  is back to the initial condition instead of stepping down to start the adaptation.

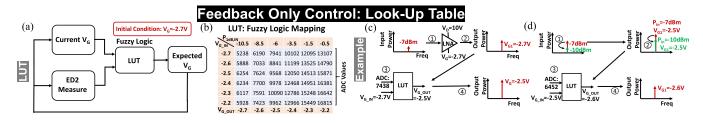

#### B. Lookup Table Control Logic

Fig. 12(a) describes the control method with an LUT. An LUT shown in Fig. 12(b) utilizes the current  $V_G$  value and the ADC measurement (unit:  $10^{-4}$  V) of the ED2 at 3 GHz and then outputs the  $V_G$  value that would bring the LNA back to linearity (high linearity mode). Note that, although not included in the figure, after settling of  $V_G$ , ED2 is constantly monitored so that, if the measurement is within the ADC variation,  $V_G$  stays at the same value; otherwise, the process starts over with another ED2 measurement. The LUT is generated in a way that, for each input power using the  $P_{1 \text{ dB,IN}}$  at each  $V_G$  value and different  $V_G$  settings, ADC measures at the output of ED2. LUT can be associated with a fuzzy logic control that, unlike the triple set-point control to only have four commands, fuzzy logic includes a wider range of  $V_G$  outputs. Each combination input  $V_G$  and ED2 measurement can be treated as an if-else statement in the fuzzy logic and returns a preprogrammed output  $V_G$  [41]. An example of the LUT control is shown in Fig. 12(c). When the interference is detected, ADC measures at ED2 output. With the ADC measurement of 743.8 mV (ADC reads 7438) and the current  $V_G$  value of -2.7 V, the LUT determines that a  $V_G$  value of -2.5 V with a  $P_{1 \text{ dB,IN}}$  of -6 dBm is sufficient to bring the system back to linearity. Another example is shown in Fig. 12(d) in the case of reduced interference level. Again, the ADC measurement and current  $V_G$  values are used to determine that  $V_G$  of -2.6 V with  $P_{1 \text{ dB,IN}}$  of -8.5 dBm is sufficient for linearity.

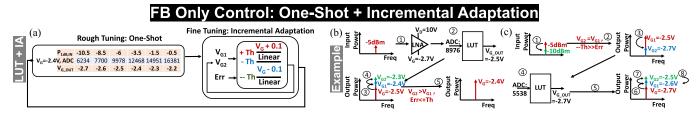

# C. One-Shot + Incremental Adaptation Control Logic

Fig. 13(a) describes the control method with a one-shot for rough tuning and incremental adaptation for fine-tuning. The one-shot is implemented in an LUT style with certain degrees of an underestimate of the output  $V_G$  value to accommodate different frequencies and different  $V_G$  values. The incremental adaption again utilizes the triple set-point control with three thresholds and four regions of action. An example is shown in 13(b), where, when the interference of -5 dBm is detected, one-shot rough tunes  $V_G$  to -2.5 V, and then, the incremental adaptation starts to increment  $V_G$  for fine-tuning. A second example is shown in 13(c), where, when the interference level drops significantly, one-shot tunes  $V_G$  to -2.7 V, and then, incremental adaptation steps up to find the optimum  $V_G$ .

#### D. Comparison of Control Methods

All three methods are intended to control the bias of LNA in order to achieve linearity with a minimum required power consumption from the LNA. LUT has the advantage of being very fast and accurate if the frequency is known so that the specific

Fig. 13. (a) One-shot + incremental adaptation logic for feedback-only control. (b) Example of the one-shot + incremental adaptation when a detectable interference presents. (c) Example of the one-shot + incremental adaptation when the interference level decreases.

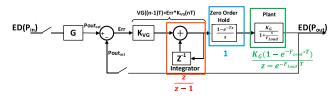

Fig. 14. Second-order dynamic control diagram with discrete time control and continuous time plant.

LUT can be utilized; however, accuracy implies a stringent requirement on the memory space in the microcontroller that multiple LUTs at different frequencies are required. On the other hand, the incremental adaptation only and the one-shot + incremental adaptation methods do not need the frequency information for adaptation as long as the measurement is greater than the interference threshold. However, due to the extra adaptation and the single set linearity threshold, the two methods tend to take longer and are less accurate involving some overestimation of  $V_G$ . A way to incorporate methods is that, when the interference frequency is known, LUT can be used, but, when the frequency is unknown, one-shot + incremental adaptation can be used.

#### E. Control Theory for Optimum Bias

In order to provide a more thorough background on the limitations of the control loop adaptation time, a second-order dynamic system is presented in Fig. 14 following the analysis for digital dropout regulators [42], [43]. The control loop models the feedforward and feedback control method with two degrees of observability at the input and output. The model has the following assumptions.

- 1) Flat gain until the  $P_{1 \text{ dB}}$  point.

- 2) Gain is not a function of  $V_G$  and frequency but linearity.

- 3)  $V_G$  settling (100 kHz) dominates ED bandwidth (40 MHz) and LNA bandwidth.

The goal of the control loop is to minimize the difference between the expected output and the measured output. The expected output is calculated from the measured input and multiplied by a constant LNA gain (G). Both the expected output and the measured output are sampled and subtracted to form an error signal. The error signal multiplies with a proportional constant ( $K_{VG}$ ) to form  $\Delta V_G$  that is added to the previous  $V_G$  through the integrator (z/(z-1)). The sampled  $V_G$  transforms to continuous time through the zeroorder hold. Finally,  $V_G$  supplies to the plant and maps the  $V_G$  to the measured output. The plant consists of a constant gain  $K_G$  and a pole from the  $V_G$  settling time ( $F_{Load}$ ) with a z-domain equation of [( $K_G(1 - e^{(-F_{Load}T_s)}))/(z - e^{(-F_{Load}T_s)})$ ].

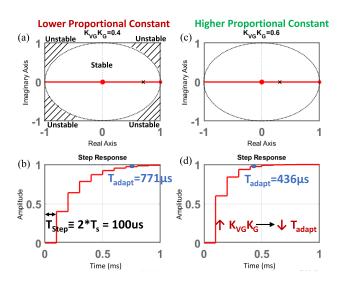

Fig. 15. (a) and (b) Root locus and step response for a lower proportional constant of 0.4. (c) and (d) Root locus and step response for a higher proportional constant of 0.6.

$T_s$  is the ADC sampling period (we will approximate 50  $\mu$ s for a simpler demonstration of calculation). The open-loop gain is

$$G_{\rm OL}(z) = \frac{K_{\rm VG}K_G \left(1 - e^{-F_{\rm Load}T_s}\right)}{z - e^{(-F_{\rm Load}T_s)}} \times \frac{z}{z - 1}.$$

(1)

To maximally match the existing control methods, since each adaptation step requires two samples of measurement to ensure accuracy, which will be explained shortly,  $2 * T_s =$ 100  $\mu$ s with a sampling frequency  $F_s/2 = 10$  kHz is used. With  $F_{\text{Load}} = 100$  kHz,  $F_s < F_{\text{Load}}$ , and  $F_s$  dominants in the settling time. From Fig. 15(a) and (b), the proportional constant is low with  $K_{V_G}K_G = 0.4$ , and the total settling time or the adaptation time is 771  $\mu$ s. From Fig. 15(c) and (d),  $K_{V_G}K_G = 0.6$ , and the total settling time is 436  $\mu$ s. As shown in the step response, because  $T_{\text{Load}} < T_s$ , each step takes  $2 * T_s$ . The different proportional constant can be thought of as the one-shot values in the one-shot + incremental adaptation method; with a higher one-shot value (high  $K_{V_G}K_G$ ), the number of steps to reach a steady state is lower, hence a faster response.

Overall, the adaptation time can be approximated as

$$T_{\text{adapt}} = N * \left(2 * T_s + T_{\text{process}}\right) \tag{2}$$

where

$$T_s > T_{V_G} + T_{\rm LNA} + T_{\rm ED}.$$

(3)

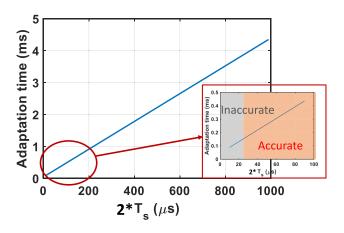

Fig. 16. Adaptation time versus ADC sampling time  $(T_s)$  with  $K_{V_G}K_G = 0.6$  and assuming  $T_{V_G} \approx 10 \ \mu$ s.

In the equations, *N* is the number of steps, which is a function of the proportion constant,  $T_s$  is the ADC sampling time,  $T_{\text{process}}$  is the processing time for the microcontroller to make decisions,  $T_{V_G}$  is the  $V_G$  tuning time,  $T_{\text{LNA}}$  is the propagation time from tuned  $V_G$  to the settling of the LNA, and  $T_{\text{ED}}$  is the propagation time from settled LNA output to settled ED output. Note that the first sample of the ADC contains some of the transient response, which lacks accuracy, so the second sample is taken to be the accurate one to the processing, hence  $2 * T_s$  in (2). In order for the second sample to be accurate, the first sample of the ADC should contain all of the transient responses; hence, (3) shows that the sampling time of the ADC needs to be greater than the total propagation and settling time for each component.

Some known timing characteristics are given as follows.

- 1)  $T_{V_G} \approx 4\text{--}10 \ \mu \text{s}$  per step depending on the step size.

- 2)  $T_{\text{process}}$  is negligible in the ranges of  $<\mu$ s.

- 3)  $T_s \approx 2 \ \mu \text{s}-1 \text{ ms or } F_s \approx 1-500 \text{ kHz}.$

4)  $T_{\text{Load}} \approx T_{V_G} \approx 4-10 \ \mu \text{s}$  or  $F_{\text{Load}} \approx F_{V_G} \approx 100-250 \text{ kHz}$ . Since the highest  $F_s$  is 500 kHz,  $F_s \ll F_{\text{Load}}$ , and a linear increase in the adaptation time versus ADC sampling time is observed in Fig. 16, assuming  $T_{V_G} \approx 10 \ \mu \text{s}$  and a negligible processing time with  $K_{V_G}K_G = 0.6$ . Note that, in the figure, a sufficient margin higher than  $T_{V_G}$  (>25  $\mu$ s of total ADC measurement time for two samples) is needed for an accurate reading. The simulations in Fig. 16 allow for a more accurate estimation of the minimum adaptation time for the control loop. The adaptation time is strongly dependent on the ADC sampling rate, so, if the ADC sampling rate can be increased, the adaptation time can be reduced. Otherwise, the minimum adaption time is about 150  $\mu$ s with the current sampling rate with the number of steps to settling being approximately four.

## V. MEASUREMENT RESULTS

# A. Results From Feedback-Only Control

Feedback-only control implements a temporal control where the tuning uses two samples of the output signal levels at different times. The results are summarized in Table II.

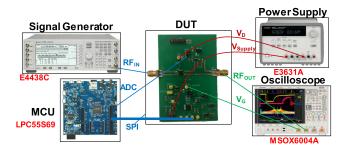

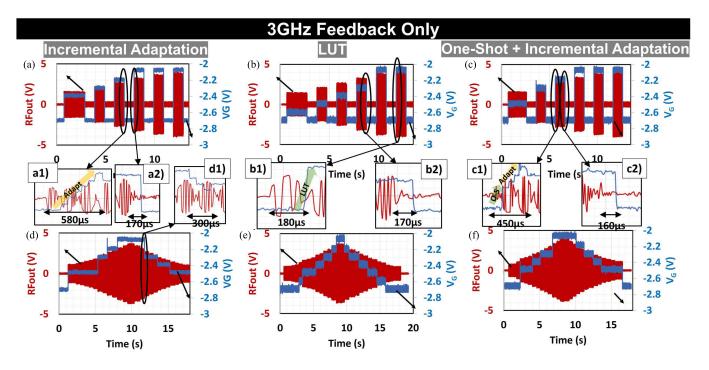

Fig. 18 presents the adaptation and timing characteristics for different control methods with the measurement setup in

TABLE II Design Comparison

| Control                                    | Interference On Off                                                                                                                                                                                                                | Interference Level Change                                                                 |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Incremental<br>Adaptation                  | -Slowest adaptation time $(\sim 600 \ \mu s)$<br>-wider frequency range adaptation                                                                                                                                                 | interference level change                                                                 |

| Look-Up<br>Table                           | -Fastest adaptation time<br>( $\sim$ 180 $\mu$ s)<br>-all steps are visible<br>during interference level<br>change<br>-narrower frequency<br>range adaptation<br>-requires more memory<br>space to implement full<br>look-up table | interference level change -settles to the same $V_G$                                      |

| One-Shot<br>+<br>Incremental<br>Adaptation | -Faster adaptation time<br>( $\sim$ 450 $\mu$ s)-wider frequency range<br>adaptation-frequencyspecific<br>one-shotone-shotone-shotone-shot                                                                                         | interference level change<br>-frequency specific<br>one-shot or<br>underestimation during |

Fig. 17. Measurement setup.

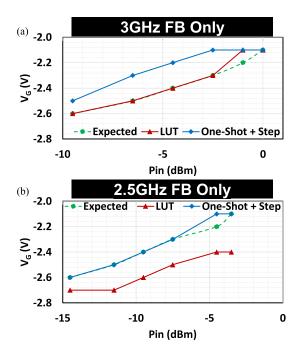

Fig. 17. Note that, after zooming into the transient, the RF output measured using an oscilloscope is not a perfect sine wave due to the undersampling of the oscilloscope trying to capture the signal with a larger time scale. Fig. 18(a)-(c) shows the adaptation of the LNA by varying different interference levels on and off. Different high interference levels at 3 GHz are forced at the input with the expectation of  $V_G$  to increase from -2.6 to -2.1 V in the increment of 0.1 V; at low interference levels,  $V_G$  is expected to drop down to -2.7 V. A summary of different settled  $V_G$ 's with respect to different input interference levels is presented in Fig. 19(a). As expected, the LUT [see Fig. 18(b)] is more aligned with the expected  $V_G$ as the LUT values are specifically for 3 GHz, while both the incremental adaptation only [see Fig. 18(a)] and the oneshot + incremental adaptation [see Fig. 18(c)] overestimate  $V_G$ . Fig. 18(a1), (b1), and (c1) show that the tuning times to adapt to an interference level for the incremental adaptation, LUT, and one-shot + incremental adaptation are 580, 180, and 450  $\mu$ s, respectively. Fig. 18(a2), (b2), and (c2) shows that the tuning times to adapt to a disappearing interference for the three control methods are very similar, around 170  $\mu$ s. Fig. 18(d)-(f) shows the adaptation of the LNA when the

Fig. 18. 3-GHz transient data with  $V_D = 10$  V. Transient data of RF output and  $V_G$  for input interference sequence of -9.5, -22.5, -6.5, -22.5, -4.5, -22.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5, -2.5,

interference level increases from -12.5 to -0.5 dBm and backs down to -12.5 dBm in increments of 1 dBm. With the LUT method in Fig. 18(e), every step of  $V_G$  is shown and roughly the same settling  $V_G$  for the same interference level, whereas, for the incremental adaptation [see Fig. 18(d)] and one-shot + incremental adaptation method [see Fig. 18(d)] and one-shot + incremental adaptation method [see Fig. 18(f)], some  $V_G$  steps are skipped and, sometimes, different  $V_G$  values for the same interference level. Fig. 18(d1) shows that, when the interference level decreases, the control loop is able to step down and adapt.

Fig. 19 shows the settling  $V_G$  values for different methods of control versus input power with frequencies of 3 and 2.5 GHz. In the 3-GHz plot in Fig. 19(a), the LUT method almost matches up with all the expected  $V_G$  to bring the LNA back to linearity, whereas the incremental adaptation only and one-shot + incremental adaptation overestimate for many  $P_{IN}$  values. However, in the 2.5-GHz plot in Fig. 19(b), LUT significantly underestimates the necessary  $V_G$  for linearity as the LUT is only captured at 3 GHz, and the algorithm tries to match the 2.5-GHz ADC values with the 3-GHz values. On the contrary, the one-shot + incremental adaptation method matches up with the expected better at 2.5 GHz than at 3 GHz due to the set threshold value being better suited at 2.5 GHz since the threshold value is chosen to adapt to a wider range of frequencies.

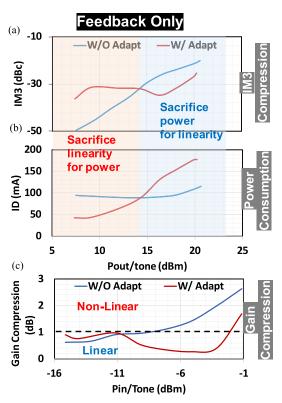

Fig. 20 shows the tradeoffs between an adaptive system versus a nonadaptive system operating in nominal conditions with a two-tone measurement. Fig. 20(a) and (b) shows that, when the interference is low, the adaptive system consumes less power while still maintaining linearity for the LNA in

Fig. 19. (a) Settled  $V_G$  value for different adaptation methods at 3 GHz on the feedback-only board. (b) Settled  $V_G$  value for different adaptation methods at 2.5 GHz on the feedback-only board.

comparison to the nonadaptive system having a higher IM3 compression and consumes more power; when the interference is high, the adaptive system consumes more power to bring the LNA back to linearity with a higher IM3 compression compared to the nonadaptive system with lower IM3 compression

Fig. 20. 3-GHz data for feedback board comparison with and without adaption for two-tone measurements for (a) IM3 compression, (b) drain current of the LNA, and (c) gain compression.

(LNA is nonlinear) and lower power consumption. Fig. 20(c) shows that the adaptive system is able to keep the LNA in the linearity range over a wider input range than the nonadaptive system in the nominal condition.

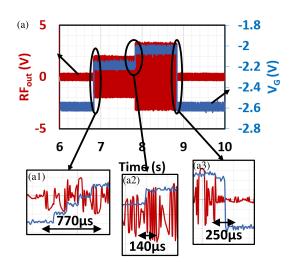

#### B. Results From Feedforward + Feedback Control

Feedforward + feedback design allows spatial control of the system where both the input and output signal levels can be sampled, and the linearity is determined by comparing the measured gain with the expected gain to ensure no gain compression. Fig. 21 shows that the tuning circuit is able to use spatial control to tune  $V_G$  of the LNA as the interferences appear, increase, and disappear; however, this method also suffers from an overestimation of the  $V_G$  value that a higher  $V_G$  value is determined. Note from Fig. 21(a1) that, unlike the overshoot in the feedback-only incremental adaptation control, since this board has the extra degree of observability and the measured gain is directly compared with the expected gain, tuning does not give overshoot in  $V_G$ . From Fig. 21(a1) to (a3), the tuning times for the interference appearance, increasing of interference, and disappearance of interference are 770, 140, and 250  $\mu$ s, respectively. The tuning times are below 1 ms; however, as shown in Fig. 21(a1), a longer tuning time is needed than the feedback-only incremental adaptation control as the ADC sampling time is lengthened to accurately measure the input power being close to the sensitivity level.

# C. System Comparison

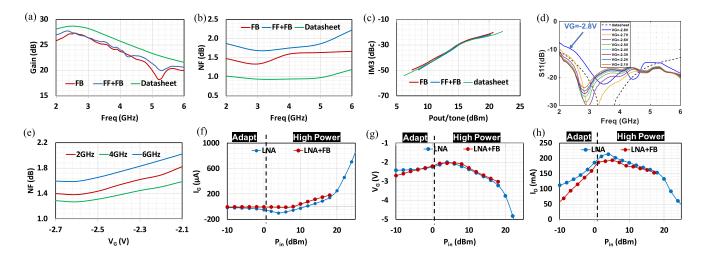

Fig. 22 presents different LNA characteristics after implementation on the feedback-only board, and the combined

Fig. 21. 3-GHz adaptation data for feedforward + feedback board when input interference level changes from -5.5 to -2.5 dBm. (a) Overall tuning of  $V_G$  and the effect on the output. (a1)–(a3) Timing characteristics for different tuning steps.

feedforward and feedback board with the datasheet values in similar bias conditions of  $V_D = 10$  V and  $I_D \approx 100$  mA. Note that the datasheet values are measured directly on the die; by implementing on a PCB, some degrees of degradation in the gain and NF are expected. Fig. 22(a) shows the gain comparison over the frequency range of 2-6 GHz. The gain of the boards shows a few dB of degradation in comparison to the datasheet while little difference between the different boards. Fig. 22(b) shows the noise figure (NF) versus frequency for different boards. The feedback-only board has an NF about 0.5 dB higher than the datasheet, and as expected with the feedforward and feedback combined board, the NF is again about 0.3 dB higher than the feedback-only layout due to the extra directional coupler before the LNA. Fig. 22(c) shows the IM3 compression versus desired output power for each tone. The IM3 compressions are relatively close across different boards and the datasheet.

Fig. 22(d) shows different return losses (S11) with respect to different  $V_G$  values. As shown in the plot, when  $V_G = -2.8$  V, the return loss is worse than all of the other voltages, so, when implementing the control loop, only  $V_G$  greater than -2.8 V is considered. For  $V_G$  between -2.7 and -2.1 V, the majority of the responses have an S11 lower than -15 dBm; other parts have an S11 lower than -10 dBm. Fig. 22(e) shows NF across  $V_G$  tuning range for 2, 4, and 6 GHz. Across  $V_G$ , the NF can increase by about 0.4 dB. When interference is low, instead of operating at nominal  $V_G$  of -2.4 V with a higher NF, lower NF can be achieved in the adaptive system with  $V_G$  of -2.7 V. When interference is high, higher linearity is achieved with higher NF and power consumption.

Fig. 22(f)–(h) shows the comparison of the high-power data for the LNA in Fig. 6 and LNA in a feedback system. In the adaptation range,  $V_G$  in the feedback system is continuously increasing to maintain linearity by adapting to the current input, while  $V_G$  increase in the LNA only system is caused by the nonlinearity of the LNA. The difference in linearity in the two systems can also be observed in the  $I_G$ , where the linear system has a consistent  $I_G$  in the ranges of  $\mu A$ ,

IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES

Fig. 22. Different LNA characteristics, such as gain, NF, and IM3 compression, are compared between the feedback system, the feedback + feedforward system, and the datasheet in (a)–(c), respectively ( $V_D = 10$  V, and  $I_D \approx 100$  mA). (d) Return loss (S11) for the feedback system. (e) NF versus  $V_G$  for different frequencies. (f)–(h) High input power comparison between LNA with a series resistance of 5.03 k $\Omega$  without adaptation (see Fig. 6) and LNA in the feedback system at 3 GHz.

| LNA  | LNA+FB                                       | LNA+FB+FF                                             |  |  |

|------|----------------------------------------------|-------------------------------------------------------|--|--|

| 28   | 26.5                                         | 26.5                                                  |  |  |

| 1    | 1.4                                          | 1.7                                                   |  |  |

| -7   | $-10.5 \sim 0.5$                             | $-14 \sim 0.5$                                        |  |  |

| 1    | $0.5 \sim 2$                                 | $0.3 \sim 1.8$                                        |  |  |

| 0    | 0.09                                         | 0.1                                                   |  |  |

| 0    | 1                                            | 2                                                     |  |  |

| none | Temporal                                     | Spacial                                               |  |  |

| none | 85                                           | 150                                                   |  |  |

|      | 28<br>1<br>-7<br>1<br>0<br>0<br>none<br>none | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |  |  |

TABLE III

\* 3 GHz Data

whereas the nonlinear system sees more of a revered biased current.  $I_D$  for both systems show an increase because of the increase in  $V_G$ . In the high-power range, the currents and the voltages are starting to overlap showing similar high-power effects, as described in Section III-B.

Table III shows comparisons between the datasheet LNA in nominal condition, LNA with feedback control, and LNA with feedback + feedforward control. According to the datasheet [28], the GaN LNA's nominal condition is  $V_D =$ 10 V and  $I_D =$  100 mA, which consumes about 1 W of power. The controls consume  $\leq 10\%$  of total LNA nominal power for a better linearity and LNA power consumption tradeoff. Most of the control power derives from the microcontroller consuming 80 mW of power, which is about 80%–90% of total control power. LNA with control gives a wide tuning range in power and linearity. When the system is operating in the low-power mode in a large EW Rx array, the power saving can be significant. Extra system power is consumed when higher linearity is required to decode the signal.

The feedforward + feedback design includes two pairs of the directional coupler and ED. With the extra directional coupler and ED1 before the LNA, NF increases by  $\approx 0.3$  dB,

and overall control power consumption increases by another 10 mW than the feedback-only design; however, the design gives more information on the input signal that will be more relevant in future works of an adaptive Rx. For example, if a filter was placed to remove the interference signal, the extra information on the input signal would allow us to determine if the interference is still present or has already been removed by the filter. The feedback-only design provides a simpler solution for the current application to detect the presence and the level of interference signal at the output of the LNA. Contrary to the spatial control in the feedforward + feedback design, the feedback-only design implements a temporal control. At the current stage, the extra degree of observability at the input of the LNA is not needed as no filter is present.

#### D. Comparison Table

Table IV shows the different works that contribute to adaptive transceivers over different implementation methods for higher resilience toward undesired interference.

# VI. FUTURE WORK

This work can be further extended by implementing a complete RF Rx front end, adding interference frequency detection and/or interference filtering circuitry for interference compression, and better use of some frequency-dependent control methods. The interference frequency detection circuits can assist with deciding other signals for interference cases, such as strong signals and strong interference. The adaptation time and the power consumption of the controlling circuit can be further minimized. If the Apollo4 microcontroller is utilized, the microcontroller would only consume milliwatts of power and reduced the total control power to <3% of nominal LNA power consumption [44]. A different LNA with orthogonal tunability can be explored so that, with a blocker, the gain can also be tuned to achieve large signal linearity. NF of the front end can also be further improved.

|                     |                                                                                                           |                                                  |                                                                                                                                   |                                                                                          | <b>A</b> (1   1                                                 |                                                                                            |                                        |                                                                                             |                                                                             |                                                       |

|---------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------|

|                     | Computation                                                                                               | Blocker Tolerant with                            | Blocker Cancellation                                                                                                              | Multi-Parameter                                                                          | Orthogonally                                                    | Pro-VIZOR                                                                                  | Data Priority vs Energy                | Environment-Adaptive                                                                        | Multi-Octave                                                                | Instinctual GaN                                       |

|                     | Communication                                                                                             | Harmonic Rejection                               | LNA                                                                                                                               | Adaptation Receiver                                                                      | Tunable LNA                                                     |                                                                                            | Priority Adaptative                    | Tx                                                                                          | Interference Detectors                                                      | Linearity-Power                                       |

|                     | Trade-off                                                                                                 | Front-end                                        |                                                                                                                                   |                                                                                          |                                                                 | [24],[18]                                                                                  | Transceiver                            |                                                                                             |                                                                             | Tradeoff Front-end                                    |

|                     | [19]                                                                                                      | [20]                                             | [21]                                                                                                                              | [22]                                                                                     | [23]                                                            | DAC'08                                                                                     | [16]                                   | [25]                                                                                        | [26] [27]                                                                   |                                                       |

|                     | JSSC'22                                                                                                   | JSSC'18                                          | TMTT'22                                                                                                                           | TCASI'14                                                                                 | TCASI'12                                                        | TCAD'14                                                                                    | TCAD'15                                | TCASI'11                                                                                    | MWCL'22 TMTT'22                                                             | This Work                                             |

| Implementation*     | IC (65nm)                                                                                                 | IC (65nm)                                        | IC (65nm)                                                                                                                         | IC (180nm) + COTS                                                                        | IC (180nm) + System<br>Simulation                               | COTS                                                                                       | COTS                                   | COTS + PCB                                                                                  | COTS + PCB                                                                  | Integrated PCB                                        |

| Control Goal        | Optimize energy,<br>latency and BER                                                                       | Harmonic rejection                               | Blocker cancelation                                                                                                               | Noise, linearity and<br>power trade-off                                                  | Power optimization                                              | Power optimization                                                                         | High<br>Throughput ↔ Low<br>energy/bit | PA linearity ↔ Power                                                                        | Max<br>Interference Detection                                               | LNA Linearity ↔<br>Power                              |

| Control Mechanism   | Actor-critical neuro-<br>controller for<br>processing depth, PA<br>power out and error<br>correction code | Harmonic rejecting<br>N-path filters with<br>LNA | LNA with another<br>feedforward path with<br>N-path filter mixers to<br>notch signal and copy<br>blocker to subtract<br>after LNA | Tuning knob and<br>automatic gain control<br>tuning while<br>maintaining minimum<br>SNIR | Orthogonal gain and<br>linearity tuning with<br>BER limitations | PAR reduction at Tx,<br>supply and bias for<br>LNA and mixer at Rx<br>with BER limitations | LUT for Transmitter<br>parameters      | PAR reduction with<br>Baseband<br>companding/<br>expanding of<br>the OFDM signal<br>PA Bias | Bandstop filter bias<br>bias                                                | LNA VG Bias                                           |

| Detection Parameter | Path-loss, noise<br>power, network size,<br>information content                                           |                                                  |                                                                                                                                   | SNIR                                                                                     | EVM                                                             | EVM                                                                                        | EVM                                    | EVM                                                                                         | Frequency + Power of<br>the highest<br>interference                         | Power                                                 |

| Detection Method    | On chip calculations                                                                                      |                                                  |                                                                                                                                   | FPGA SNIR<br>measurement                                                                 | Baseband EVM<br>calculation in MATLAB                           | Baseband EVM<br>calculation in MATLAB                                                      | Baseband EVM<br>calculation in MATLAB  | Baseband EVM<br>calculation in MATLAB                                                       | Power detectors +<br>ADCs at different<br>points on an open<br>circuit stub | Envelope detector+<br>ADC                             |

| Processor           | On chip DNN<br>processing elements                                                                        |                                                  |                                                                                                                                   | FPGA                                                                                     | MATLAB simulation                                               | PC MATLAB                                                                                  | PC MATLAB                              | PC MATLAB                                                                                   | FPGA                                                                        | Microcontroller                                       |

| Power Handling      | Low                                                                                                       | Low                                              | Low                                                                                                                               | Low                                                                                      | Low                                                             | Low                                                                                        | Low                                    | Low                                                                                         | High since coupler is<br>included                                           | High                                                  |

| System Power (mW)   |                                                                                                           | LNA: 33.8~43.8                                   | LNA : 20                                                                                                                          |                                                                                          | LNA: 3.6 ~ 32                                                   | LNA + Mixer : 20 ~ 150                                                                     |                                        | PA: 165-912                                                                                 | System: 800                                                                 | LNA: 500 ~ 2000 W<br>System: 100                      |

| Frequency (GHz)     | 2.4                                                                                                       | 0.2 ~ 1                                          | 1.35 ~ 2.7                                                                                                                        | 0.6                                                                                      | 0.07~1.5                                                        | 2.4                                                                                        | 2                                      | 2.4                                                                                         | 1-16                                                                        | 2~6                                                   |

| Tuning Time         |                                                                                                           |                                                  |                                                                                                                                   |                                                                                          |                                                                 |                                                                                            |                                        |                                                                                             | 500 ns                                                                      | 1 ms                                                  |

| Comment             |                                                                                                           | Chip measurement<br>only                         | Chip measurement<br>only                                                                                                          |                                                                                          | Only Simulation                                                 | Not integrated on one<br>PCB                                                               | Not integrated on one<br>PCB           | Not integrated on one<br>PCB                                                                | Stub area limitation                                                        | Can be implemented<br>on IC to improve<br>performance |

TABLE IV Comparison Table

\* IC+COTS: Custom IC with COTS connected through SMA connector. COTS: COTS connected through SMA connector. COTS+PCB: some custom microwave components connected with some components integrated into the PCB. Integrated PCB: components are integrated into one PCB without any SMA connections to other components.

The concept of the work can be expanded into other technologies by having a strong correlation between the bias voltages of the LNA, and linearity and the accessibility of the bias voltages. The work can also be expanded into other frequencies with correct characterizations of different components. The LNA and the onboard directional couplers are specifically for 2–6 GHz, and the ED2 can function up to 43.5 GHz.

If similar systems were to be built in low-power Rxs, a custom ASIC design can bring down the control loop power by orders of magnitude. Such systems are part of future work and will expand the applicability of instinctual Rxs to much wider power categories of RF systems.

#### VII. CONCLUSION

This article presents the first instinctual GaN LNA system demonstration with intelligent localized sensing, processing, and feedback controls to achieve sub-1-ms adaptation to a variety of interference scenarios. GaN LNA is utilized for the high-power handling capabilities in radar and EW applications. The system consumes  $\leq 10\%$  of nominal LNA power to provide a wide range of tuning. The linearity tuning range is about 11 dB; the LNA power consumption tuning range is about 0.5-2 W; and NF changes about 0.4 dB across the tuning range. When the frequency is known using LUT, the system adapts to an interference very accurately to bring the LNA back to linearity. When the frequency is unknown, the system is still able to adapt to interference with extra power consumption using either incremental adaptation only or one-shot + incremental adaptation. The feedback-only board provides simplicity of the design for this application. The adaptation time for the system is <1 ms, which closely matches the theoretical simulations.

#### REFERENCES

J. Yang et al., "Instinctual interference-adaptive low-power receiver with combined feedforward and feedback control," *IEEE Microw. Wireless Compon. Lett.*, vol. 31, no. 6, pp. 771–774, Mar. 2021.

- [2] Y. A. Adediran, H. Lasisi, and O. B. Okedere, "Interference management techniques in cellular networks: A review," *Cogent Eng.*, vol. 4, no. 1, Jan. 2017, Art. no. 1294133, doi: 10.1080/23311916.2017.1294133.

- [3] O. Axelssonm N. Billström, N. Rorsman, and M. Thorsell, "Impact of trapping effects on the recovery time of GaN based low noise amplifiers," *IEEE Microw. Wireless Compon. Lett.*, vol. 26, no. 1, pp. 31–33, Jan. 2016.

- [4] H. Li, X. Yang, and C. E. Saavedra, "A feedforward linearization technique implemented in IF band for active down-conversion mixers," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2017, pp. 296–299.

- [5] T. Nesimoglu, Z. Charalampopoulos, and M. A. Beach, "Interference suppression in radio receivers by using frequency retranslation," in *Proc. IEEE 10th Annu. Wireless Microw. Technol. Conf.*, Apr. 2009, pp. 1–5.

- [6] T. Nesimoglu, M. A. Beach, J. R. MacLeod, and P. A. Warr, "Mixer linearisation for software defined radio applications," in *Proc. IEEE 56th Veh. Technol. Conf.*, vol. 1, Sep. 2002, pp. 534–538.

- [7] M. Parvizi, K. Allidina, and M. N. El-Gamal, "An ultra-low-power wideband inductorless CMOS LNA with tunable active shunt-feedback," *IEEE Trans. Microw. Theory Techn.*, vol. 64, no. 6, pp. 1843–1853, Jun. 2016.

- [8] A. Dehqan, E. Kargaran, K. Mafinezhad, and H. Nabovati, "An ultra low voltage ultra low power CMOS UWB LNA using forward body biasing," in *Proc. IEEE 55th Int. Midwest Symp. Circuits Syst. (MWSCAS)*, Aug. 2012, pp. 266–269.

- [9] C. J. Jeong, W. Qu, Y. Sun, D. Y. Yoon, S. K. Han, and S. G. Lee, "A 1.5 V, 140 μA CMOS ultra-low power common-gate LNA," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, Jun. 2011, pp. 1–4.

- [10] S. N. Ali, M. A. Hoque, S. Gopal, M. Chahardori, M. A. Mokri, and D. Heo, "A continually-stepped variable-gain LNA in 65-nm CMOS enabled by a tunable-transformer for mm-wave 5G communications," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2019, pp. 926–929.

- [11] Z. Hao, L. Zhiqun, and W. Zhigong, "A wideband variable gain differential CMOS LNA for multi-standard wireless LAN," in *Proc. Int. Conf. Microw. Millim. Wave Technol.*, Apr. 2008, pp. 1334–1337.

- [12] S. Popuri, V. S. R. Pasupureddi, and J. Sturm, "A tunable gain and tunable band active balun LNA for IEEE 802.11 ac WLAN receivers," in *Proc. ESSCIRC Conf., 42nd Eur. Solid-State Circuits Conf.*, Sep. 2016, pp. 185–188.

- [13] S. Sen, M. Verhelst, and A. Chatterjee, "Orthogonally tunable inductorless RF LNA for adaptive wireless systems," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2011, pp. 285–288.