## Atomic layer deposited Al<sub>2</sub>O<sub>3</sub> for gate dielectric and passivation layer of single-walled carbon nanotube transistors

S. K. Kim, Y. Xuan, P. D. Ye, and S. Mohammadia)

School of Electrical and Computer Engineering, Purdue University, West Lafayette, Indiana 47907 and Birck Nanotechnology Center, Purdue University, West Lafayette, Indiana 47907

## J. H. Back and Moonsub Shim

Department of Materials Science and Engineering, University of Illinois at Urbana Champaign, Urbana, Illinois 61801

(Received 23 February 2007; accepted 16 March 2007; published online 17 April 2007)

High performance single-walled carbon nanotube field effect transistors (SWCNT-FETs) fabricated with thin atomic layer deposited (ALD)  $Al_2O_3$  as gate dielectrics and passivation layer are demonstrated. A 1.5  $\mu$ m gate-length SWCNT-FETs with 15 nm thick  $Al_2O_3$  insulator shows a gate leakage current below  $10^{-11}$  A at -2.5 V < V $_g$  < +7 V, a subthreshold swing of S  $\sim$  105 mV/decade, and a maximum on current of -12  $\mu$ A at a reverse gate bias of -1 V. Lack of hysteresis in IV characteristics and low low frequency noise indicate high quality oxide-nanotube interface achieved utilizing ALD  $Al_2O_3$  as gate dielectrics and passivation layer. © 2007 American Institute of Physics. [DOI: 10.1063/1.2724904]

Single-walled carbon nanotube field effect transistors (SWCNT-FETs) have attracted attention as complementary nanoscale devices conventional metal-oxidesemiconductor (CMOS) transistors due to excellent electrical properties of single-walled nanotubes. 1,2 Since their first demonstration in 1998, significant progress has been made in improving the electrical performance of these devices.<sup>4,5</sup> Current research in SWCNT-FETs is focused on achieving high transconductance, scaling down gate dielectrics, and eliminating hysteresis caused by various charge trapping mechanisms. An attractive research approach to improve the device transconductance and current capability while reducing hysteresis as pursued by several researchers is to utilize novel gate dielectric materials and passivation layers on SWCNTs. 4-7 Several groups have investigated new SWCNT-FET gate dielectric structures including (i) bottom gated with native Al<sub>2</sub>O<sub>3</sub> dielectrics, (ii) top gated with 15–20 nm thick SiO<sub>2</sub> dielectrics, and (iii) top gated with atomic layer deposited (ALD) 8-20 nm thick high-k zirconium oxide (ZrO<sub>2</sub>) (Ref. 4) and hafnium oxide (HfO<sub>2</sub>).<sup>5</sup> Among the above techniques, utilizing high-k ALD ZrO2 and HfO2 as gate dielectric is very promising and has achieved near ballistic transport and ideal subthreshold swing of ~60 mV/decade. The drawbacks of these techniques are that high-k materials such as ZrO2 and HfO2 are difficult to grow and difficult to remove using standard wet etching processes due to crystallization of ALD ZrO<sub>2</sub> and HfO<sub>2</sub> after postdeposition annealing (PDA). Additionally, HfO<sub>2</sub> and ZrO2 are biohazard material.

Passivation of SWCNT-FETs helps stabilizing their electrical characteristics against environmental variations. Difficulty in growth and etching as well as high dielectric constant are main reasons that ALD ZrO<sub>2</sub> and HfO<sub>2</sub> are not used as passivation layer. Instead, chemical vapor deposited (CVD) Si<sub>3</sub>N<sub>4</sub> (Ref. 8) and polymethylmethacrylate (PMMA) polymer<sup>9</sup> are utilized. However, Si<sub>3</sub>N<sub>4</sub> passivation leads to electrical degradation of carbon nanotube transistor. It is also

reported that PMMA passivation is not adequate to protect the nanotube channel from ambient humidity.<sup>10</sup>

In this letter, we report high performance and high interface quality top-gated SWCNT-FETs with  $Al_2O_3$  dielectric films deposited by ALD technique. ALD  $Al_2O_3$  films have been utilized as passivation and thin gate dielectric layers. The ALD  $Al_2O_3$  is annealed after dielectric layer deposition and can be patterned with standard lithographic processes using a simple wet etching process. These nanotube-based devices achieve high on current and high transconductance with no hysteresis and low interface trap density.

We have used low frequency noise characterization as well as hysteresis in  $V_{\sigma}$ - $I_{\rm d}$  characteristics for studying the interface quality in SWCNTs prior and after ALD Al<sub>2</sub>O<sub>3</sub> deposition. Previous work points out to hysteresis in CNT-FETs as a method to analyze interface quality.<sup>8,9</sup> The problem of hysteresis measurement is that hysteresis in  $V_{\sigma}$  depends on the sweeping rate of gate voltage and the range of gate voltage, which prevents measuring interface traps quantitatively. In CMOS technology, capacitance-voltage (C-V)measurement and low frequency noise are used to analyze the interface traps in oxide/semiconductors. Carbon nanotube interface has an extremely small gate dielectric capacitance,  $C_{\text{ox}} \sim 2\pi\varepsilon_0 \varepsilon / \ln(2t_{\text{ox}}/R) \sim 28 \text{ aF/nm},^4 \text{ much lower than the}$ detectable range of available laboratory equipment, preventing conventional C-V measurement as a possible characterization technique. 11 Low frequency noise is then the only quantitative method for analysis of interface traps in nanodevices.

The SWCNT-FET devices reported here, shown in the inset of Fig. 1, are fabricated on a high resistivity Si substrate  $(\rho\!\approx\!10~\text{k}\Omega)$  with a 500 nm SiO $_2$  thermal oxide. SWCNTs are synthesized on the thermal oxide by thermal CVD of methane on the substrate using commercial ferritin (Sigma) catalyst. The grown carbon nanotubes have a diameter of 1–3 nm with an approximate tube density of 2–10/ $\mu$ m². Following the nanotube growth, the ALD Al $_2$ O $_3$  film is deposited on SWCNTs on SiO $_2$  substrate using the ASM Microchemistry F-120 ALCVD $^{\rm TM}$  reactor. A 15 nm amorphous Al $_2$ O $_3$  film is deposited on the wafer at 300 °C followed by

a) Author to whom correspondence should be addressed; electronic mail: saeedm@purdue.edu

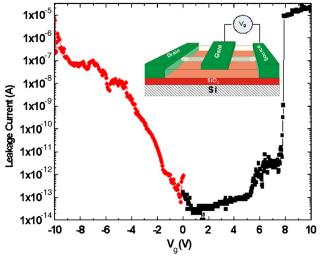

FIG. 1. Leakage current  $I_g$  (A) vs gate bias  $V_g$  (V) for SWCNT-FETs having 15 nm  $Al_2O_3$  dielectrics. Inset: cross section of the top gate single-walled carbon nanotube field effect transistors with 15 nm thick ALD-grown  $Al_2O_3$  as gate dielectric.

PDA in N<sub>2</sub> at 600 °C for 30 s. Figure 1 shows the gate leakage current of a SWCNT-FET having 1.5  $\mu m$  gate length with two semiconducting nanotubes in the channel. As can be seen from the figure, the leakage current is very small, in the range of 10 pA-10 fA at -2.5 V < V\_g < 7 V, about five orders of magnitude smaller than the drain current of nanotube devices. Using wet etching (diluted HF solution), the Al<sub>2</sub>O<sub>3</sub> oxide on the source and drain patterns is removed while the gate area is protected by photoresist. Metal contacts are formed by electron beam deposition of Pd followed by a lift-off process. Gate metal is defined by UV photolithography followed by the deposition of Ti/Au (10/50 nm) with a minimum gate length of 1.5  $\mu$ m. Ti/Au (20/450 nm) metal interconnects are finally deposited on top of the source and drain Pd contacts.

There are reports of high quality interface achieved between ALD Al<sub>2</sub>O<sub>3</sub> and carbon nanotubes, <sup>12</sup> Si, <sup>13</sup> and GaAs <sup>14</sup> substrates. In these reports, the quality of ALD Al<sub>2</sub>O<sub>3</sub> films exhibits a strong dependence on ALD growth conditions and PDA. 12-14 We have previously investigated high quality Al<sub>2</sub>O<sub>3</sub> films on GaAs substrate through PDA.<sup>14</sup> The deposited ALD Al<sub>2</sub>O<sub>3</sub> film shows highly electrical insulating characteristics, having very low leakage current density of  $\sim 10^{-9} - 10^{-7}$  A/cm<sup>2</sup> for 5 nm thick Al<sub>2</sub>O<sub>3</sub> at -3-+3 V gate bias. For the same oxide thickness compared to the state-ofthe-art SiO<sub>2</sub> on Si, the leakage current density of ALD Al<sub>2</sub>O<sub>3</sub> film on GaAs is similar or even one order of magnitude lower at a given gate bias. Al<sub>2</sub>O<sub>3</sub> has a high band gap (  $\sim$ 9 eV), a high breakdown electrical field (5–30 MV/cm), high permittivity (8.6-10), and high thermal stability (up to at least 1000 °C). It will also remain amorphous under typical heat treatment. In our current experiments, Al<sub>2</sub>O<sub>3</sub> films are grown on CNTs using alternating pulses of Al(CH<sub>3</sub>)<sub>3</sub> (the Al precursor) and H<sub>2</sub>O (the oxygen precursor) at 300 °C in a carrier N<sub>2</sub> gas flow. Postdeposition annealing is done in N<sub>2</sub> ambient at 600 °C for 30 s using rapid thermal processing. Unlike ALD HfO<sub>2</sub> or ZrO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub> can be conveniently etched using standard wet etching (HF) techniques even after high temperature annealing.

The 1/f noise spectrum in metal-oxide-semiconductor field effect transistors (MOSFETs) can be used as a qualita-

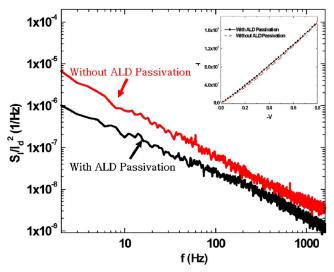

FIG. 2. Low frequency noise spectrum of current fluctuation of the prepostpassivation of ALD  $Al_2O_3$  SWCNTs for drain to source resistor. Inset: *IV* characteristics of pre-postpassivated SWCNT. Both resistances have the same resistance of 500 k $\Omega$ .

tive measure of the origin of the noise and the density and energy of the interface traps responsible for 1/f noise. <sup>15,16</sup> Similarly, measuring the low frequency noise spectrum of the SWCNTs can indicate interface trap density and energy around CNTs. In this letter, by measuring the 1/f noise prior to and after the deposition of ALD passivation layer, we monitor a change in the trap density around the CNTs assuming that the trapping-detrapping mechanism is responsible for noise. Figure 2 shows the  $I_d^2$  normalized low frequency noise spectrum of single-walled carbon nanotube biased at -0.3 V prior to and after ALD Al<sub>2</sub>O<sub>3</sub> passivation. By applying ALD Al<sub>2</sub>O<sub>3</sub> passivation layer, the resistance value of 500 k $\Omega$  remains intact as can be seen from the *IV* curve in the inset of Fig. 2. On the other hand, the 1/f noise spectrum of SWCNTs passivated by Al<sub>2</sub>O<sub>3</sub> is approximately one order of magnitude smaller than unpassivated SWCNTs. The small noise spectrum of the passivated SWCNTs indicates that the interface trap densities are remarkably low. Kim et al. reported that water molecules on or near SWCNTs are the

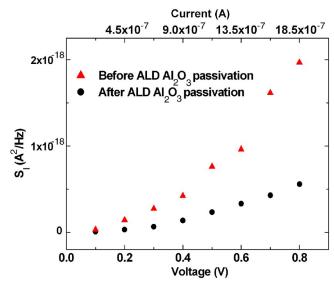

FIG. 3. Current vs current noise amplitude of  $S_I$  for drain to source resistor at 10 Hz as a function of voltage prior to ALD  $Al_2O_3$  passivation and after ALD  $Al_2O_3$  passivation.

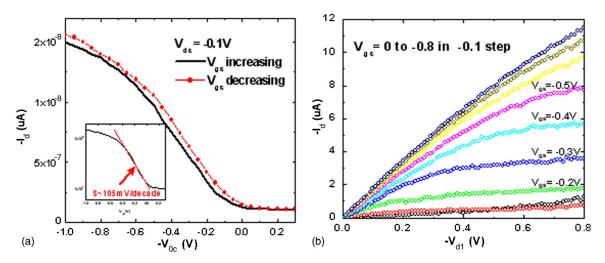

FIG. 4. Characteristics of a p-type SWCNT-FET with  $Al_2O_3$  as gate dielectrics. (a) Current  $I_d$  vs  $V_{gs}$  as increasing (line) and decreasing gating sweeps (points) for a 1.5  $\mu$ m gate-length SWCNT-FET at  $V_{ds}$  of -0.1 V. Inset: log-scaled current  $I_d$  vs  $V_{gs}$  curve. The subthreshold swing (S) is about 105 mV/decade. (b) Drain current vs drain bias as a function of gate bias of the same device.

primary source of interface charge traps, giving rise to large hysteresis. By passivating CNTs using ALD Al<sub>2</sub>O<sub>3</sub>, interface traps activated by water absorption from the ambient may be significantly reduced.

Figure 3 shows the correlation between the current noise amplitude  $(S_I)$  at 10 Hz and current (I) as a function of the applied voltage (V) prior to and after ALD Al<sub>2</sub>O<sub>3</sub> passivation. The 1/f noise spectrum can be found according to Hooge's empirical law

$$S_I(f) = \frac{q\mu_{\text{eff}}\alpha_H IV}{fL^2} = \frac{q\mu_{\text{eff}}\alpha_H I^2}{R_{\text{ch}}L^2 f},$$

where  $\alpha_H$  is the Hooge parameter, q is the electronic charge,  $\mu_{\rm eff}$  is the effective mobility of carriers inside the channel, and L is the channel length. The resistance  $R_{\rm ch}$  given by V/Iis a constant value of 500 k $\Omega$ . In both cases (prior to and after ALD  $Al_2O_3$  passivation), current noise amplitude  $(S_I)$  is proportional to  $I^2$ , a trend observed in semiconductor resistors. The estimated Hooge parameters prior to and after ALD  $Al_2O_3$  passivation are  $9 \times 10^{-3}$  and  $5.44 \times 10^{-3}$ , respectively. The device with ALD Al<sub>2</sub>O<sub>3</sub> passivation has superior prop-

Figure 4 shows the *I-V* characteristics for a 1.5  $\mu$ m gate length SWCNT-FET with a 15 nm thick Al<sub>2</sub>O<sub>3</sub> in the ambient environment. Figure 4(a) shows a typical  $I_d$  vs  $V_{gs}$  characteristics when  $V_{\rm gs}$  is swept from -1 to 1 V and back to -1 V. In most of the SWCNT-FET, the direction of  $V_{\rm gs}$ sweep and its speed will create a hysteresis response due to the interface charge traps, mainly from water molecules. The amount of voltage shift depends on the interface trap density on/near SWCNTs and how fast the sweep is done. Small hysteresis observed in the Fig. 4(a) indicates that ALD Al<sub>2</sub>O<sub>3</sub> suppresses the density of traps in SWCNT-FETs operating in ambient conditions. Figure 4(b) shows  $I_d$  vs  $V_{ds}$  at different gate biases. The curves resemble a conventional p-MOSFET characteristic, exhibiting linear region at low  $|V_{\rm ds}|$  and saturation region at higher  $|V_{\rm ds}|$ . The maximum intrinsic transconductance  $g_m = dI_{ds}/dV_{ds}|_{Vds=0.2 \text{ V}}$  of 3  $\mu$ S and the maximum on current of  $-12 \mu A$  are observed. The subthreshold swing (S) is about 105 mV/decade.

In conclusion, we have demonstrated the application of atomic layer deposited Al<sub>2</sub>O<sub>3</sub> gate dielectric and passivation layers for high performance SWCNT-FET. The subthreshold swing of  $S \sim 105$  mV/decade, high transconductance of 3  $\mu$ S at a drain bias of 0.2 V, and a maximum on current of  $-12 \mu A$  indicate that ALD-based Al<sub>2</sub>O<sub>3</sub> through postdeposition annealing can be used as gate dielectric for CNT transistors. Furthermore, low level of low frequency noise and hysteresis-free IV characteristics demonstrate that ALD Al<sub>2</sub>O<sub>3</sub> can be utilized as excellent passivation layer on SWCNTs.

The authors acknowledge David Chang for assistance in noise measurement. This work was supported by National Science Foundation NIRT (Grant No. CCF-05-6660).

<sup>1</sup>T. Durkop, S. A. Getty, E. Cobas, and M. S. Fuhrer, Nano Lett. 4, 35

<sup>2</sup>A. Javey, G. Jing, W. Qian, M. Lundstrom, and D. Hongjie, Nature (London) 424, 654 (2003).

<sup>3</sup>S. J. Tans, R. M. Verschueren, and C. Dekker, Nature (London) 393, 49

<sup>4</sup>A. Javey, K. Hyoungsub, M. Brink, W. Qian, A. Ural, G. Jing, P. McIntyre, P. McEuen, M. Lundstrom, and D. Hongjie, Nat. Mater. 1, 241 (2002).

<sup>5</sup>A. Javey, J. Guo, D. B. Farmer, Q. Wang, D. Wang, R. G. Gordon, M. Lundstrom, and H. Dai, Nano Lett. 4, 447 (2004).

<sup>6</sup>A. Bachtold, P. Hadley, T. Nakanishi, and C. Dekker, Science **294**, 1317 (2001).

<sup>7</sup>S. J. Wind, J. Appenzeller, R. Martel, V. Derycke, and A. Ph, Appl. Phys. Lett. 80, 3817 (2002).

<sup>8</sup>K. Daisuke, O. Hirokazu, O. Yasuhide, M. Kenzo, I. Koichi, M. Kazuhiko, S. Yasuhiro, M. Atsushi, and M. Hideki, Appl. Phys. Lett. 86, 113115 (2005).

W. Kim, A. Javey, O. Vermesh, Q. Wang, Y. Li, and H. Dai, Nano Lett. 3, 193 (2003).

<sup>10</sup>H. Shimauchi, Y. Ohno, S. Kishimoto, and T. Mizutani, Jpn. J. Appl. Phys., Part 1 45, 5501 (2006).

<sup>11</sup>S. Ilani, L. A. K. Donev, M. Kindermann, and P. L. McEuen, Nat. Phys. 2, 687 (2006).

<sup>12</sup>C. F. Herrmann, F. H. Fabreguette, D. S. Finch, R. Geiss, and S. M. George, Appl. Phys. Lett. 87, 123110 (2005).

<sup>13</sup>M. Ch., H. B. Park, J. Park, C. S. Wang, J.-C. Lee, S.-J. Oh, J. Jeong, K. S. Hyun, H.-S. Kang, Y.-W. Kim, and J.-H. Lee, J. Appl. Phys. 94,

<sup>14</sup>H. C. Lin, P. D. Ye, and G. D. Wilk, Appl. Phys. Lett. **87**, 182904 (2005). <sup>15</sup>F. N. Hooge and A. M. H. Hoppenbrouwers, Phys. Lett. **29A**, 642 (1969). <sup>16</sup>A. van der Ziel, Proc. IEEE **76**, 233 (1988).

<sup>17</sup>G. Ghibaudo and T. Boutchacha, Microelectron. Reliab. 42, 573 (2002).

Downloaded 24 Aug 2007 to 128.211.171.27. Redistribution subject to AIP license or copyright, see http://apl.aip.org/apl/copyright.jsp