# Multiwafer Vertical Interconnects for Three-Dimensional Integrated Circuits

Rosa R. Lahiji, *Student Member, IEEE*, Katherine J. Herrick, *Member, IEEE*, Yongshik Lee, *Member, IEEE*, Alexandros Margomenos, *Member, IEEE*, Saeed Mohammadi, *Senior Member, IEEE*, and Linda P. B. Katehi, *Fellow, IEEE*

Abstract—Low-loss multiwafer vertical interconnects appropriate for a microstrip-based circuit architecture are proposed. These transitions have been designed, fabricated, and measured for 100- $\mu$ m-thick silicon and GaAs substrates separately. Experimental results show excellent performance up to 20 GHz, with extremely low insertion loss (better than 0.12 and 0.38 dB for the two different silicon designs and 0.2 dB for the GaAs transition), and very good return loss (reflection of better than 12.9 and 17.3 dB for the two silicon designs, respectively, and 13.6 dB for the GaAs design). Using a high-performance transition allows for a more power-efficient interconnect, while it enables denser packaging by stacking the substrates on top of each other, as today's technologies demand.

Index Terms—Integrated circuit packaging, microstrip line, vertical interconnects.

#### I. INTRODUCTION

N TODAY'S technology, integrating a system is a major challenge in terms of having the most compact and efficient packaging. Microstrip lines are one of the best suited architectures for monolithic microwave integrated circuits (MMICs) and, hence, are widely used due to their large bandwidth, high power handling, excellent miniaturization, and small volume. At the same time, the microstrip architecture has been the most difficult one to utilize in multiwafer arrangements due to the extending ground planes and the parasitic inductances and capacitances associated with changes in the ground metallization.

High-density circuit architectures require multiwafer transitions that can be used to tightly integrate circuit components on multiple wafers, integrated using wafer-to-wafer bonding methods. Developing a multiwafer circuit using a low-loss vertical interconnect architecture results in less dissipated power per unit area and, hence, increases power-handling capability and reduces volume and cost. To design an optimal transition, not only the line impedances should be matched (to maximize the coupling and minimize the reflection), but also the fields on

Manuscript received October 12, 2005; revised February 4, 2006. This work was supported by the Defense Advanced Research Project Agency and managed by the Air Force Research Laboratory, Sensors Directorate, Aerospace Components and Subsystems Division, Wright Patterson AFB under the Intelligent RF-Front End Program.

- R. R. Lahiji, S. Mohammadi, and L. P. B. Katehi are with the School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN 47906 USA (e-mail: rrlahiji@purdue.edu).

- K. J. Herrick is with Raytheon RF Components, Andover, MA 01810 USA.

- Y. Lee is with the School of Electrical and Electronic Engineering, Yonsei University, Seoul 120-749, Korea.

- A. Margomenos is with EMAG Technologies Inc., Ann Arbor, MI 48108 USA.

Digital Object Identifier 10.1109/TMTT.2006.874867

the two interconnecting lines should make a transition in a way that reduces unwanted junction parasitics. Even at frequencies as low as L-band, matching the impedances alone is not adequate and the fields along the transition have to maintain their continuity as well. In a high-density circuit, good performance requires low loss combined with reduced parasitic radiation and proximity coupling between the various sections of the electromagnetic structure.

Previous research has demonstrated the development of efficient vertical transitions that transfer the wave (signal) from the backside of a wafer to the front side of the same wafer [1]–[3]. In addition, uniplanar transitions have been demonstrated that transition of the RF signal from one type of an interconnect to another [4]. Some examples of previous research include a coplanar waveguide (CPW)-to-microstrip transition on a single wafer [1], a CPW-to-CPW transition on a single wafer [2], a microstrip-to-coplanar stripline (CPS) transition, a slotline transition [3], and a CPS-to-CPW transition [4]. In all previous research, multiwafer transitions have thus far been designed and demonstrated in a finite-ground CPW circuit environment. Specifically, a CPW-to-CPW vertical transition was demonstrated on a silicon wafer, which transfers the signal from the front side of the bottom wafer to the backside of the top wafer, operated at frequencies as high as W-band [5]. As oppose to a CPW line, in a microstrip configuration, the ground and signal lines are separated by the thickness of the wafer. Hence, in order to make the transition of the microstrip line vertically from a lower wafer to the top wafer in a stacked configuration, both the signal and ground metallization have to go through vertically and, thus, multiple vias are needed.

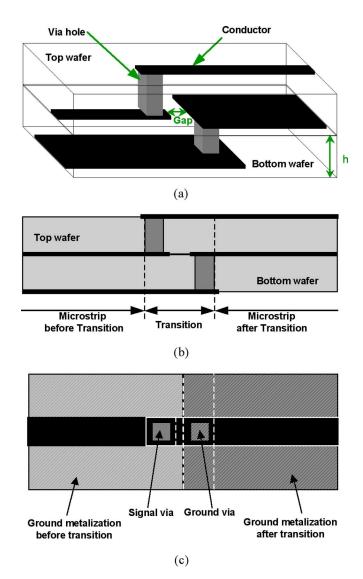

The study presented in this paper describes for the first time the development and successful demonstration of a new three-dimensional (3-D) microstrip-to-microstrip interconnect that can transfer RF signals vertically through stacks of wafers. These transitions have been successfully demonstrated with two 100- $\mu$ m GaAs wafers using deep reactive ion etching (DRIE) to form cylindrical vias [6] and are extended herein to multiwafer structures using two 100- $\mu$ m Si wafers and wet etching to form conical vias. Fig. 1 illustrates the primary idea of the proposed transitions. In the 3-D view, the wire-framed boxes represent the substrates, while in the side view, the substrates are recognized as solid boxes. Also for the clarity of this figure, only the metal layers are depicted in the top view.

# II. DESIGN AND MODELING

In order to implement the idea of the vertical interconnect, both signal and ground conductors have to make a transition

Fig. 1. Preliminary idea of vertical interconnects between two wafers (a) 3-D view. (b) Side view. (c) Top view. (Color version available online at: http://www.ieeexplore.ieee.org.)

from the bottom wafer to the top wafer. The signal conductor of both wafers is on the front side of each wafer, as depicted in Fig. 1. As shown in this figure, in addition to the signal lines, the ground lines are finite in size and their width has been designed to provide the appropriate characteristic impedance (50  $\Omega$ ). Both signal and ground lines are transited from a bottom wafer to the top wafer with vias that are etched through the wafers. The presence of vias increases the inductance of the line locally, which has to be compensated by introducing the proper capacitance at the transition point, for the desired frequency range. The design aspect for both silicon and GaAs wafers are identical, but due to the slight difference in fabrication processes, which will be described below, the parasitic elements introduced during transition are different in value. These parasitic capacitances and inductances are responsible for the continuity of the fields, near changes in geometry characteristics. Traditional methods to overcome these field discontinuities lead to either modifications of the geometrical structure in order to eliminate or minimize these parasitic values or to optimize their values so that

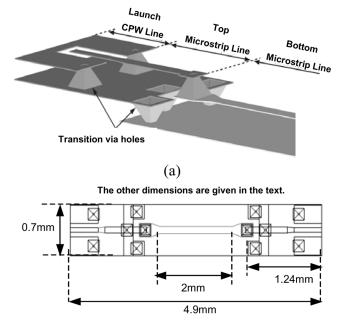

Fig. 2. First architecture (DES1): the optimized microstrip-to-microstrip vertical interconnects on silicon. (a) 3-D view. (b) Top view.

(b)

they compensate the effect of each other (creating a resonance). Hence, different architectures are proposed herein for each case specifically to maintain both the impedance match and the continuity of the fields. Each structure has been modified and optimized using Ansoft HFSS V.9.1, for the best impedance and field match in the desired frequency range (1–20 GHz) on both silicon and GaAs 100- $\mu$ m-thick wafers. The major difference between the designs originated from the available technology to fabricate the designs. Hence, the designs are reviewed separately herein.

## A. Silicon Transition Designs

As mentioned before, the idea is to transition the signal vertically through vias. This transition will delay the signal and introduces some inductance along the transition path, which has to be compensated with proper capacitance accordingly. Two different designs have been established, namely, DES1 and DES2, which are shown in Figs. 2 and 3, respectively. Both designs are optimized for a stacked configuration of two 100- $\mu$ m-thick high-resistivity ( $\rho > 2$  k  $\Omega$ ·cm) silicon substrates. For low resistivity substrates such as the ones used in current CMOS processes, long microstrip lines will introduce substantial loss and should be avoided. However, with some modifications, vertical transition designs presented here can be utilized for 3-D integrated circuits.

As it is obvious from these figures, DES1 has a higher count of vias for the ground transition when compared to DES2. The vias have a pyramidal shape with 162  $\mu$ m  $\times$  162  $\mu$ m opening windows because they are etched anisotropically through the wafer using silicon wet etching. Hence, the base of each via is  $20~\mu$ m  $\times$  20  $\mu$ m in area. The width of the signal line on the top wafer is 80- $\mu$ m wide, while on the lower wafer it is 100  $\mu$ m so that all lines have a characteristic impedance of 50  $\Omega$ . During

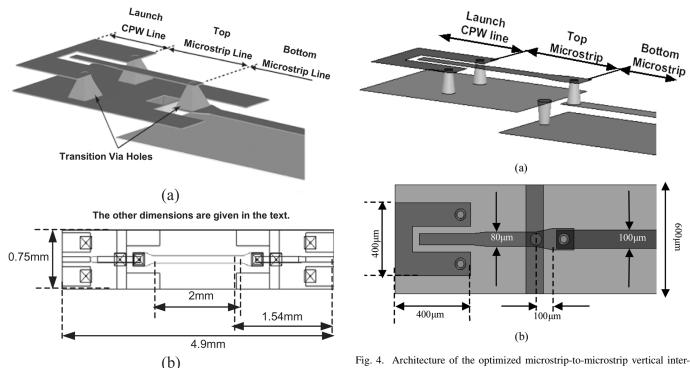

Fig. 3. Second architecture (DES2): the optimized microstrip-to-microstrip vertical interconnects on silicon. (a) 3-D view. (b) Top view.

the transition from the top wafer to the bottom wafer, the ground conductor of the top microstrip and the signal conductor of the bottom microstrip are sandwiched between the two wafers, thus causing a change in the characteristic impedance of the line. Specifically, the characteristic impedance increases from 50  $\Omega$  to a higher value. It is in an effort to correct for this change that the width of the signal line is widened from 80  $\mu$ m on the top microstrip to 100- $\mu$ m-wide line on the bottom microstrip.

In order to measure the *s*-parameters of the designed structure, a number of back-to-back transitions with different lengths of line in between them were fabricated. Moreover, to be able to make on-wafer measurements, a CPW section of line with a signal–gap–ground size of 60–40–250  $\mu$ m (50  $\Omega$ ) was utilized and appropriate CPW-to-microstrip transitions were designed and added at both ends.

In this design, with wet-etched vias, the ground vias open from the front side of the bottom wafer, while the signal via opens from the backside of the top wafer, allowing flexibility in defining the separation between the top and bottom wafer vias. This orientation of the vias aligns the inner sidewalls of the signal and ground vias of the transmission line in a parallel fashion and brings them in close proximity. Hence, the signal and ground currents are forced to flow along the parallel inner sidewalls of the vias, thus resulting in reduced parasitic radiation loss.

## B. GaAs Transition Design

A new transition based on cylindrical via architecture has been designed on a 100- $\mu$ m-thick GaAs wafers. The vias are fabricated by a DRIE so they are smaller in size and provide a more compact size design. In this design, the vias

connects on GaAs. (a) 3-D view. (b) Top view.

are cylindrical with a 60-\$\mu\$m diameter and with a pad size of 85 \$\mu\$m \times 85 \$\mu\$m. As illustrated in Fig. 4(a), the signal is fed through a 60-40-130-\$\mu\$m CPW section to the top microstrip and transitions to the bottom microstrip through the vias. As in silicon designs, the width of the microstrip line was increased appropriately to compensate the increase in \$\varepsilon\$\_{eff}\$ (effective permittivity) when the conductor is sandwiched between two substrates. Fig. 4(b) shows the dimensions of the fabricated structure.

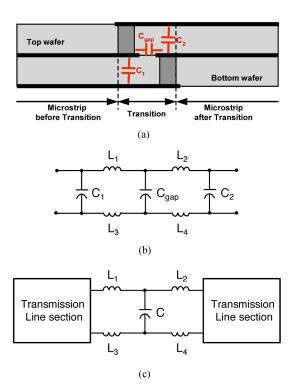

### C. Modeling

As mentioned in the design section, the lines and transitions have been designed to maintain a  $50-\Omega$  impedance across the lines and through the vias. A  $50-\Omega$  microstrip or CPW line is realized relatively easily, but in order to preserve the impedance along the transition, the effect of the geometrical discontinuities is studied. A simple model has been derived that describes the response of such a transition fairly well [see Fig. 5(b)].

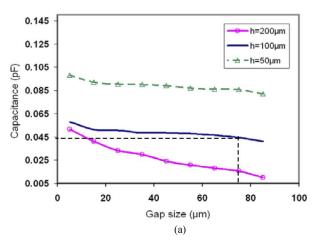

The inductance values are determined by the shape of the via and the via pad sizes, while the capacitance has two components: the parasitic open-end capacitance between the end of the microstrip signal conductor and the ground conductor  $[C_1, C_2]$  in Fig. 5(a)] and the gap capacitance between the signal and ground conductors at the midsection of the transition  $(C_{\rm gap})$ , the value of which is primarily determined by the separating gap. As the gap size decreases, the value of the  $C_{\rm gap}$  increases accordingly, while  $C_1$  and  $C_2$  values remain unchanged. On the other hand, increasing the thickness of the wafer decreases the value of  $C_1$  and  $C_2$ . Comparing these effects and the geometry dimensions, the  $C_1$  and  $C_2$  values can be negligible with respect to  $C_{\rm gap}$  for small gap sizes and thick wafers. As a result, we can further simplify the model to the one shown in Fig. 5(c), where  $C = C_{\rm gap}$ . The extension of the lines beyond the vias

Fig. 5. Modeling the transition. (a) Side view of the transition showing the capacitor components. (b) Simplified model of the geometry shown in (a). (c) Further simplified model of the transition. (Color version available online at: http://www.ieeexplore.ieee.org.)

are modeled as simple transmission lines, while the lumped circuit shown in this figure represents the transition section itself. The circuit parameters of this simplified model are derived within ADS 2003, while the physical structure is simulated and optimized using Ansoft HFSS V.9.1 to achieve the optimum impedance and desired field match in the operating frequency range (1-20 GHz). In order to derive the value of the passive components shown in Fig. 5(c)  $(L_i, i = 1, 2, 3, 4)$  and the capacitance C) as function of the given geometry, a detailed study is performed using both HFSS and ADS software. First by keeping the architecture and all the dimensions the same, the gap size [the distance between the metal traces, as shown in Fig. 1(a)] varies and, at each value, the structure is simulated within HFSS. Next, the wafer thickness [labeled as h in Fig. 1(a)] is varied and, for each value of the wafer thickness, the structure is simulated within HFSS. The simulated scattering parameters of each of the above-mentioned geometry parameters are exported from HFSS and then imported in ADS. By utilizing the gradient optimization, the value of circuit elements shown in Fig. 5(c) are derived so that the response of the circuit is best fitted to each corresponding set of data from HFSS.

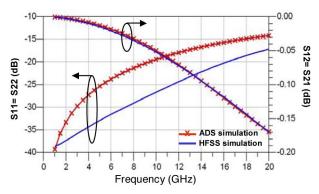

To demonstrate the above-described design process, a  $100-\mu m$  GaAs transition with gap size of 75  $\mu m$  has been used as an example here. This design is modeled in ADS by using the gradient optimizer to match the s-parameter results derived from simulating the physical 3-D structure in HFSS. Fig. 6 shows the response of this design in HFSS along with the response of the best fit model deduced from

Fig. 6. Simulation results with HFSS for the selected example and the response of the optimized model, which was extracted from ADS. (Color version available online at: http://www.ieeexplore.ieee.org.)

ADS by adjusting the values of the elements of the proposed simple circuit. The lumped-element circuit will show a more narrow frequency-band response when compared to the fabricated transmission-line structure. The theoretically calculated results in ADS (the line marked with x's) follow the real insertion-loss response from the HFSS model, almost perfectly up to 20 GHz, while the reflection coefficients compare less favorably. The discrepancy in the values of the reflection coefficients originates from the fact that the model used is using the lumped-element circuit and has been simplified by consolidating the three capacitances into one. Despite the simplifications, the results from the analysis agree fairly well with the measured behavior of the transition to the third decimal place  $(10^{-2} - 10^{-2.7} \approx 8 \times 10^{-3})$ . This extraction of the inductance and capacitance values is performed for each geometrical variation in the vertical interconnect structure and the value of the capacitance and inductances are plotted in Fig. 7(a) and (b), respectively. As observed from the graph in Fig. 7(a), the gap size is changed for three different wafer thickness values  $h=50~\mu\mathrm{m},\,100~\mu\mathrm{m},\,\mathrm{and}\,200~\mu\mathrm{m}.\,C_1$  and  $C_2$  being the open-end parasitic capacitances of the simplified transmission line, dominate when the wafer thickness is small compared to the gap size. Hence, the real value of the model parameter C might deviate slightly from the plotted curve, as the substrate gets thinner [this is the dotted plot in Fig. 7(a)]. However, as the gap size decreases, the value of the  $C_{\mathrm{gap}}$ increases and becomes a dominant term, thus, any variation of the gap size has a significant effect on C. On the other hand, by keeping the gap size at the nominal value, i.e., 75  $\mu$ m, and increasing the thickness of wafers, the inductance value increases accordingly. Hence, for a given thickness of the wafer, the value for  $L_i$ 's can be derived from Fig. 7(b). The C value can also be extrapolated from the graphs in Fig. 7(a) and an estimated value for the gap size can be realized as the starting point of the design. Proper dimensions for the transition can be maintained by using 3-D electromagnetic software such as HFSS and by optimizing the performance for the desired frequency range. For a 100- $\mu$ m-thick GaAs wafer and gap size of 75  $\mu$ m, the inductance and capacitances values can be read off the graphs as  $L_1 = L_2 = 0.166$  nH,  $L_3 = L_4 = 0.124$  nH, and C = 0.0445 pF.

Fig. 7. Variation of the modeled parameter values showed in Fig. 5 with respect to physical changes to the geometry on GaAs. (a) Capacitance. (b) Inductances. (Color version available online at: http://www.ieeexplore.ieee.org.)

#### III. FABRICATION

#### A. Silicon Design

The fabrication of the proposed silicon multiwafer transition is achieved via a combination of surface and bulk micromachining. Two 100- $\mu$ m-thick high-resistivity double-sided polished silicon wafers with thermal oxide on both sides are used. 1  $\mu$ m of gold is deposited on the topside using a liftoff process in order to form the top interconnect. The via structures are anisotropically etched in potassium hydroxide (KOH) and are metallized with 4  $\mu$ m of gold to form the bottom metallization layer. The required alignment marks for the front and backside of each wafer are formed using optical alignment. After completion of the fabrication steps on each of the two wafers separately (top and bottom wafers), the two wafers were bonded together to form the stacked multiwafer structure. The bonding alignment marks are etched through the wafers (DRIE) so that the two wafers can be aligned through the etched holes at four corners of the wafer. Finally a gold-to-gold thermo-compression bonding is performed at 365 °C [8], [9], which completes the process.

## B. GaAs Design

Fabrication of the multiwafer transition on GaAs utilizes industry standard processing and is compatible with active field-effect transistor (FET) fabrication and integration processes. With some minor differences, the process steps are similar to the silicon transition. Starting with full thickness GaAs wafers, one side of the wafers are fully processed and then flipped and mounted on carriers for backside processing. Backside processing includes thinning the GaAs wafer to  $100~\mu m$ , dry etching the  $60-\mu m$ -diameter vias, metallization, patterning, and scribing.

As in the silicon architecture, each of the top and bottom wafers is processed separately. After completion of the fabrication steps on each of the two wafers, the top and bottom transition substrates are bonded together by a thermo-compression gold to-gold bond to form the stacked multiwafer structure, similar to the silicon devices. Alignment is achieved by simply aligning the edges of the two wafer pieces.

#### IV. MEASUREMENT AND SIMULATION RESULTS

## A. Silicon Design

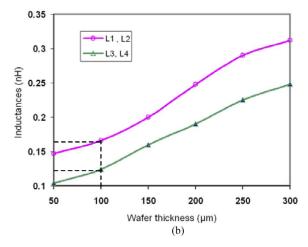

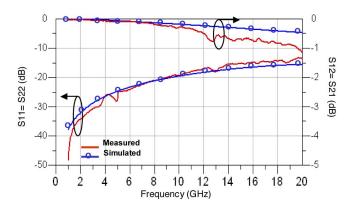

The fabricated structures have been measured using the 8722 network analyzer with a thru-reflect-line (TRL) calibration for 1–20 GHz. These calibration standards are fabricated on each chip and, in addition to providing calibration of the network analyzer, they serve to provide good measurements of the insertion loss in decibels per millimeter. On the silicon wafers, insertion loss of approximately 0.19 dB/mm has been measured. Fig. 8(a) demonstrates the measured and simulated results of the DES1 shown in Fig. 2, while Fig. 8(b) depicts the results of the DES2 (Fig. 3). As seen from these data, the measured and simulated reflections coefficients agree very well.

For DES1, a reflection of better than -12.9 dB and for DES2 better than -17.3 dB has been achieved for the whole frequency band. The measured insertion loss is slightly higher than the simulated insertion loss due to the fact that the simulations have been done for perfect conductors and the ohmic losses were not included. Assigning a finite conductivity to the lines and considering the ohmic losses in the simulations will not have any substantial effect on the reflection coefficient, but it will increase the insertion loss as the measurements have demonstrated. Comparing the return loss of the two designs  $(1 - |S_{11}|^2 - |S_{21}|^2)$ , it is seen that DES1 has a better loss at lower frequencies, but it degrades faster as frequency increases. This is due to the fact that the ground metallization of DES1 has multiple vias and, hence, is a more inductive structure with respect to DES2. This plays the dominant role in increasing the return loss at higher frequencies.

Nondeembedded insertion loss of better than 0.87 dB for DES1 and 1.47 dB for DES2 has been achieved. The measured insertion loss of each one of these structures includes the two back-to-back vertical transitions, along with a 2-mm-long microstrip line connecting the transitions. In addition, there are two 600- $\mu$ m-long sections of microstrip line right after the CPW-to-microstrip transitions.

To get a more accurate characterization of the transition, we deembedded the loss of the microstrip-line sections included in

Fig. 8. Measured and simulated response of the whole structure consisting of two back-to-back microstrip-to-microstrip vertical interconnect and CPW-to-microstrip transitions at both ends on silicon. (a) DES1. (b) DES2. (Color version available online at: http://www.ieeexplore.ieee.org.)

the designs (a total of approximately 3.2-mm-long microstrip lines). Fig. 9(a) and (b) shows the measured, deembedded, and simulated results for the insertion loss of each back-to-back transition separately. Based on these results, insertion loss of back-to-back transitions better than 0.24 dB for DES1 and 0.77 dB for DES2 has been achieved after deembedding. As a result, the insertion loss per individual vertical transition is 0.12 and 0.38 dB, respectively.

## B. GaAs Design

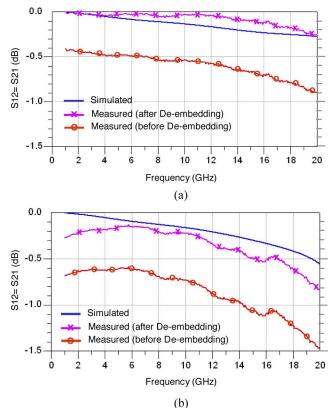

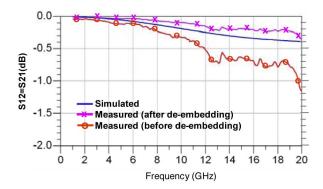

The designed transitions for the GaAs wafer have also been fabricated and measured using the 8722 network analyzer calibrated from 1 to 20 GHz. As mentioned in the design section, the two-port CPW measurement is possible by fabricating a back-to-back microstrip transition with additional microstrip-to-CPW transition at both ends. Fig. 10 demonstrates the measured and the simulated results of this design. As seen from this figure, the measured *s*-parameters agree very well with the simulated results from HFSS.

For this design, a reflection of better than 13.6 dB for the whole frequency band has been achieved. Similar to the silicon case, the measured insertion loss is slightly higher than the simulated results due to the fact that the simulations include perfect conductors and the ohmic losses were omitted. A non-deembedded insertion loss of better than 1.1 dB up to 20 GHz has been measured. The measured insertion loss of this structure includes the insertion loss of two vertical transitions in a back-to-back configuration along with the ohmic loss of the

Fig. 9. Simulated and measured response of a back-to-back vertical interconnects on silicon before and after deembedding the ohmic loss due to the excess microstrip sections. (a) DES1. (b) DES2. (Color version available online at: http://www.ieeexplore.ieee.org.)

Fig. 10. Measured and simulated response of the whole structure consisting of two back-to-back microstrip-to-microstrip vertical interconnects along with the CPW-to-microstrip feed lines at both ends on GaAs. (Color version available online at: http://www.ieeexplore.ieee.org.)

1-mm-long microstrip line, which connects these two transitions. There are also two 600- $\mu$ m-long sections of microstrip line, right after the CPW pads, which have to be considered when deembedding the excess loss terms. To get a more accurate characterization of the transition, the loss of the line sections included in the designs (approximately a total of 2.2-mm-long microstrip line) are deembedded. Fig. 11 demonstrates the insertion loss of the simulated and measured structure before and after deembedding. The response of the back-to-back transition has been extracted from the measurements and is plotted in this

Fig. 11. Simulated and measured response of the whole structure consisting of two back-to-back microstrip-to-microstrip vertical interconnects along with the CPW-to-microstrip feed lines at both ends on GaAs. (Color version available online at: http://www.ieeexplore.ieee.org.)

figure. Consequently, the insertion loss per vertical transition has been found to be less than 0.2 dB for the frequencies up to 20 GHz.

#### V. CONCLUSION

Novel microstrip architectures for multiwafer vertical interconnects compatible with industry-standard silicon micromachining and GaAs active wafer technology have been demonstrated. The transitions show very low insertion loss and good return loss for frequencies up to 20 GHz. These designs open new opportunities for further integration of multiwafer architectures in a new class of 3-D circuits. Since these transitions are based on a microstrip architecture, the presented designs are very flexible and will result in significant reduction of chip size along with cost and power consumption.

#### ACKNOWLEDGMENT

The authors would like to acknowledge the help and assistance of Dr. J.-H. Jeon, Purdue University, West Lafayette, IN.

#### REFERENCES

- [1] G. P. Gauthier, L. P. B. Katehi, and G. M. Rebeiz, "W-band finite ground coplanar waveguide (FGGPW) to microstrip line transition," in IEEE MTT-S Int. Microw. Symp. Dig., Jun. 1998, vol. 1, pp. 107–109.

- [2] A. Margomenos, D. Peroulis, J. P. Becker, and L. P. B. Katehi, "Silicon micromachined interconnects for on-wafer packaging of MEMS devices," in *Silicon Monolithic Integr. Circuits RF Syst. Top. Meeting Dig.*, Sep. 2001, pp. 33–36.

- [3] K. Goverdhanam, R. N. Simons, and L. P. B. Katehi, "Novel vertical interconnects with 180 degree phase shift for amplifiers, filters, and integrated antennas," in *Silicon Monolithic Integr. Circuits RF Syst. Top. Meeting Dig.*, Sep. 2001, pp. 201–204.

- [4] N. I. Dib, R. N. Simons, and L. P. B. Katehi, "New uniplanar transitions for circuit and antenna applications," *IEEE Trans. Microw. Theory Tech.*, vol. 43, no. 12, pp. 2868–2873, Dec. 1995.

- [5] K. J. Herrick and L. P. B. Katehi, "RF W-band wafer-to-wafer transition," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2000, pp. 73–76.

- [6] R. R. Lahiji, K. J. Herrick, S. Mohammadi, and L. P. B. Katehi, "Low loss multi-wafer vertical interconnects for three dimensional integrated circuits," in *Proc. 35th Eur. Microw. Conf.*, Paris, France, Oct. 2005, vol. 1, pp. 177–180.

- [7] M. A. Schmidt, "Wafer-to-wafer bonding for microstructure formation," *Proc. IEEE*, vol. 86, no. 8, pp. 1575–1585, Aug. 1998.

- [8] N. Ahmed and J. J. Svitak, "Characterization of gold–gold thermocompression bonding," *Solid-State Technol.*, pp. 25–32, Nov. 1975.

- [9] K. J. Herrick, W-Band Three-Dimensional Integrated Circuits Utilizing Silicon Micromachining. Ann Arbor, MI: The Univ. Michigan at Ann Arbor, 2000.

- [10] Ansoft HFSS. ver. 9.1, Ansoft Corporation, Pittsburgh, PA, 2003.

- [11] A. Margomenos and L. P. B. Katehi, "Fabrication and accelerated hermeticity testing of an on-wafer package for RF MEMS," *IEEE Trans. Microw. Theory Tech.*, vol. 52, no. 6, pp. 1626–1636, Jun. 2004.

Rosa R. Lahiji (S'97) was born in Ann Arbor, MI. She received the B.S. degree in electrical engineering from Tehran University, Tehran, Iran, in 2000, the M.S. degree from The University of Michigan at Ann Arbor, in 2003, and is currently working toward the Ph.D. degree at Purdue University, West Lafayette, IN

Her research interests include RF and microwave circuits and packaging, RF microelectromechanical systems (MEMS), 3-D integration of RF and microwave systems, and nanotechnology.

Katherine J. Herrick (S'91–M'00) received the B.S.E. and M.S.E. degrees in electrical engineering and Ph.D. in electrical engineering from The University of Michigan at Ann Arbor, in 1994, 1996, and 2000, respectively. Her doctoral dissertation concerned integrated 3-D microwave circuits up to W-band utilizing silicon micromachining.

She is currently a Research Scientist with Raytheon RF Components, Andover, MA, where she focuses on high-frequency metamorphic high electron-mobility transistor (MHEMT) technologies,

microwave circuit design, and integrated array programs through 110 GHz. In addition, she is part of the Intelligent RF Front End Defense Advanced Research Projects Agency (DARPA) team. Prior to joining Raytheon in January 2001, she conducted research as a Post-Doctoral Research Fellow in the areas of packaged MEMS and multilayer silicon circuits. She has authored or coauthored over 25 technical papers. She holds several patents.

**Yongshik Lee** (S'00–M'04) was born in Seoul, Korea. He received the B.S. degree from Yonsei University, Seoul, Korea, in 1998, and the M.S. and Ph.D. degrees in electrical engineering from The University of Michigan at Ann Arbor, in 2001 and 2004, respectively.

From 2004 to 2005, he was with EMAG Technologies Inc., Ann Arbor, MI, as a Research Engineer. In September 2005, he joined Yonsei University, as an Assistant Professor. His current research interests include GaAs monolithic microwave/millimeter-wave

integrated circuits and silicon micromachining for high-frequency applications.

Alexandros Margomenos (M'99) was born in Thessaloniki, Greece. He received the B.Sc. degree in physics from the Aristotle University of Thessaloniki, Thessaloniki, Greece, in 1998, and the M.Sc. and Ph.D. degrees in electrical engineering and computer science from The University of Michigan at Ann Arbor, in 2000 and 2003 respectively.

Since July of 2003, he has been a Senior Research Engineer with EMAG Technologies Inc., Ann Arbor, MI. His research interests include microwave and millimeter-wave circuits, silicon micromachining,

3-D integration, packaging, and micromachined antenna design. He is also involved with the design and implementation of packages for RF MEMS switches and the creation of 3-D integrated system-on-a-chip architectures. He holds one patent in the area of packaging of RF MEMS. He has one patent pending.

**Saeed Mohammadi** (S'89–M'92–SM'02) received the Ph.D. degree in electrical engineering from The University of Michigan at Ann Arbor, in 2000.

He is currently an Assistant Professor of electrical and computer engineering from Purdue University, West Lafayette, IN. His group is currently involved in research of RF devices and circuits, RF packaging, and nanoelectronic technology. He has authored or coauthored over 50 journals and refereed conference papers in these areas.

Dr. Mohammadi serves as an associate editor for

IEEE MICROWAVE AND WIRELESS COMPONENTS LETTERS.

Linda P. B. Katehi (S'81–M'84–SM'89–F'95) received the B.S.E.E. degree from the School of Mechanical and Electrical Engineering, National Technical University of Athens, Athens, Greece, in 1977, and the M.S.E.E. and Ph.D. degree in electrical engineering from the University of California at Los Angeles (UCLA), in 1979 and 1981, respectively.

Following her undergraduate studies, for two years she was a Senior Engineer with the Naval Research Laboratory. In the Fall of 1979, she joined UCLA. She is currently the John A. Edwardson Dean of En-

gineering and Professor of Electrical and Computer Engineering with Purdue University, West Lafayette, IN (since 2002). She is the former Senior Associate

Dean and Professor of electrical engineering and computer science at The University of Michigan at Ann Arbor. She holds 12 U.S. patents and nine U.S. patent applications. she has authored or coauthored nine book chapters, 183 published papers in refereed journals, and 363 papers in symposia proceedings. She has been invited to numerous seminars and workshops. As a faculty member, she has focused her research on the development and characterization of 3-D integration and packaging of integrated circuits with particular emphasis on MEMS devices, high-Q evanescent-mode filters, and the theoretical and experimental study of planar circuits for hybrid-monolithic and monolithic oscillator, amplifier, and mixer applications. She pioneered the development of on-wafer integration techniques that lead to low-cost high-performance integrated circuits for radar, satellite, and wireless applications.

Dr. Katehi is a member of the Nominations Committee for the National Medal of Technology, the chair of the National Science Foundation (NSF) Advisory Committee to the Engineering Directorate, a member of the Engineering Advisory Committee for Iowa State University, a member of the National Research Council (NRC) Telecommunications Board, a member of the NRC Army Research Laboratory Advisory Committee on Sensors and Electronics Division (SED), a member of the NSF Advisory Committee to Computer and Information Science and Engineering (CISE), a member of the National Aeronautics and Space Administration (NASA) Aeronautics Technical Advisory Committee (ARAC), and a member of the Department of Defense (DoD) Advisory Group on Electron Devices. She is also a member of the National Academy of Engineering (NAE) Committee on the Future of Engineering Research and a member of the Administrative Committee (AdCom) of the IEEE Microwave Theory and Techniques Society (IEEE MTT-S). She has been the recipient of numerous national and international technical awards.