# An X-Band High-Power Amplifier Using SiGe/Si HBT and Lumped Passive Components

Zhenqiang Ma, Student Member, IEEE, Saeed Mohammadi, Member, IEEE, Liang-Hung Lu, Pallab Bhattacharya, Fellow, IEEE, Linda P. B. Katehi, Fellow, IEEE, Samuel A. Alterovitz, Member, IEEE, and George E. Ponchak, Senior Member, IEEE

Abstract—We report the design and fabrication of a compact microwave monolithic integrated circuit (MMIC) amplifier, which demonstrates high output power at X-Band. A single-stage power amplifier is demonstrated, with a double-mesa type SiGe/Si HBT as the active device and spiral inductors and MIM capacitors as lumped passive components. At 8.4 GHz, a linear gain of 8.7 dB, an output power at peak efficiency of 23 dBm, and a saturated output power  $P_{sat}$  of 25 dBm, are measured. To our knowledge, this is the first MMIC X-Band power amplifier using SiGe/Si HBTs.

Index Terms—Lumped passives, MMIC power amplifier, SiGe/Si HBT.

### I. INTRODUCTION

ECENT advances in SiGe/Si heterojunction bipolar transistors (HBTs) [1], [2] have made them suitable for microwave applications. However, power amplifiers using SiGe/Si HBTs have only been demonstrated at C-Band frequencies [3] and the demonstration of a MMIC power amplifier is still lacking. While the implementation of a MMIC power amplifier is useful and necessary for system-on-a-chip scenarios, its successful development relies on the availability of high-performance SiGe/Si HBTs and high-Q factor on-chip passive components. In this letter, we report the measured performance characteristics of monolithically integrated single-stage MMIC power amplifiers consisting of high-frequency SiGe/Si HBTs and lumped high-Q passive elements.

#### II. MMIC DESIGN AND FABRICATION

The development of high performance of SiGe/Si HBTs was initiated with the device heterostructure design and a proper layout, taking into consideration the requirements for high power handling capability, thermal stability, and high-frequency operation. The factors considered for optimization of the heterostructure design have been described by us elsewhere [4]. The HBT grown by CVD is shown in Fig. 1. A double-mesa process was used to fabricate discrete HBTs [5]. A ten-finger  $(2 \times 30 \ \mu m^2)$ , total emitter area is 780  $\mu m^2$ ) common-base

Manuscript received March 12, 2001; revised May 17, 2001. The work was supported by NASA-GRC under Grant NAG3-2237 and NASA-JPL under Contract 96-1358. The review of this letter was arranged by Associate Editor Dr. Shigeo Kawasaki.

Z. Ma, S. Mohammadi, L.-H. Lu, P. Bhattacharya, and L. P. B. Katehi are with the Department of Electrical Engineering and Computer Science, University of Michigan, Ann Arbor, MI 48109-2122 USA.

S. A. Alterovitz and G. E. Ponchak are with the NASA Glenn Research Center, Cleveland, OH 44135 USA.

Publisher Item Identifier S 1531-1309(01)06648-X.

| Emitter cap Si n+ P 2x10 <sup>19</sup> cm <sup>-3</sup> 100 nm   Emitter Si n P 1x10 <sup>18</sup> cm <sup>-3</sup> 100 nm   Spacer Si <sub>0.75</sub> Ge <sub>0.25</sub> i - 5 nm   Base Si <sub>0.75</sub> Ge <sub>0.25</sub> p+ B 5x10 <sup>19</sup> cm <sup>-3</sup> 20 nm   Spacer Si <sub>0.75</sub> Ge <sub>0.25</sub> i - 5 nm   Collector Si n- P 4x10 <sup>16</sup> cm <sup>-3</sup> 500 nm   Sub-collector Si n+ P 2x10 <sup>19</sup> cm <sup>-3</sup> 1000 nm   substrate Si(100) p- 1x10 <sup>12</sup> cm <sup>-3</sup> 540 μm 540 μm |              |                                       |      |   |                                     |         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------|------|---|-------------------------------------|---------|

| Spacer Si <sub>0.75</sub> Ge <sub>0.25</sub> i 5 nm   Base Si <sub>0.75</sub> Ge <sub>0.25</sub> p+ B 5x10 <sup>19</sup> cm <sup>-3</sup> 20 nm   Spacer Si <sub>0.75</sub> Ge <sub>0.25</sub> i 5 nm 5 nm   Collector Si n- P 4x10 <sup>16</sup> cm <sup>-3</sup> 500 nm   Sub-collector Si n+ P 2x10 <sup>19</sup> cm <sup>-3</sup> 1000 nm                                                                                                                                                                                                      | Emitter cap  | Si                                    | n+   | Ρ | 2x10 <sup>19</sup> cm <sup>-3</sup> | 100 nm  |

| Base Si <sub>0.75</sub> Ge <sub>0.25</sub> p+ B 5x10 <sup>19</sup> cm <sup>-3</sup> 20 nm   Spacer Si <sub>0.75</sub> Ge <sub>0.25</sub> i 5 nm   Collector Si n- P 4x10 <sup>16</sup> cm <sup>-3</sup> 500 nm   Sub-collector Si n+ P 2x10 <sup>19</sup> cm <sup>-3</sup> 1000 nm                                                                                                                                                                                                                                                                 | Emitter      | Si                                    | n    | Ρ | 1x10 <sup>18</sup> cm <sup>-3</sup> | 100 nm  |

| Spacer Si <sub>0.75</sub> Ge <sub>0.25</sub> i 5 nm   Collector Si n- P 4x10 <sup>16</sup> cm <sup>-3</sup> 500 nm   Sub-collector Si n+ P 2x10 <sup>19</sup> cm <sup>-3</sup> 1000 nm                                                                                                                                                                                                                                                                                                                                                             | Spacer       | Si <sub>0.75</sub> Ge <sub>0.25</sub> | , ti |   |                                     | 5 nm    |

| Collector Si n- P 4x10 <sup>16</sup> cm <sup>-3</sup> 500 nm   Sub-collector Si n+ P 2x10 <sup>19</sup> cm <sup>-3</sup> 1000 nm                                                                                                                                                                                                                                                                                                                                                                                                                   | Base         | Si <sub>0.75</sub> Ge <sub>0.25</sub> | p+   | в | 5x10 <sup>19</sup> cm <sup>-3</sup> | 20 nm   |

| Sub-collector Si n+ P 2x10 <sup>19</sup> cm <sup>-3</sup> 1000 nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Spacer       | Si <sub>0.75</sub> Ge <sub>0.25</sub> | i    |   |                                     | 5 nm    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Collector    | Si                                    | n-   | Ρ | 4x10 <sup>16</sup> cm <sup>-3</sup> | 500 nm  |

| ະ Substrate Si(100) p- 1x10 <sup>12</sup> cm <sup>-3</sup> 540 μm ຈ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Sub-collecto | or Si                                 | n+   | Ρ | 2x10 <sup>19</sup> cm <sup>-3</sup> | 1000 nm |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ≍ Substrate  | Si(100)                               | p-   |   | 1x10 <sup>12</sup> cm <sup>-3</sup> | 540µm ≍ |

Fig. 1. Schematic of SiGe/Si double heterostructure HBT.

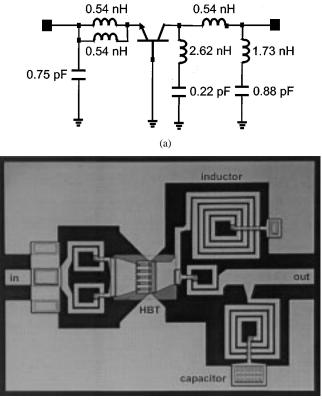

(CB) HBT exhibits an  $f_{\text{max}}$  of 62 GHz with breakdown voltage  $BV_{ceo}$  of 22.5 V. The maximum gain ( $G_{max}$ ) at 8.4 GHz is 12.2 dB. The Gummel-Poon model parameters of the HBTs were extracted from measured dc and small-signal S-parameters, and the accuracy of the large-signal model was verified with load-pull measurements on the same devices. Detailed characteristics of the discrete devices have been reported elsewhere [4]. The on-chip matching networks were realized with micromachined spiral inductors and SiO MIM capacitors, which were fabricated on the high-resistivity ( $\rho > 10\,000 \ \Omega$ -cm) Si wafers (0.54 mm thick) [5]. Depending on the geometry and the size of these lumped elements, the Q-factors of the fabricated spiral inductors and capacitors varied in the range of 10-16 and 40-70, respectively, as a result of reduced parasitic from the micromachined structure. The input and output matching networks were designed for high output power. The circuit simulation and optimization were done with the help of HP EES of LIBRA, based on the large-signal model of the HBTs and the measured S-parameters of the passive elements. The stability of the circuit was analyzed before the circuit layout was designed. The schematic of the circuit using a 10-finger CB SiGe/Si HBT is shown in Fig. 2(a) and the photomicrograph of the fabricated MMIC power amplifier is shown in Fig. 2(b). The small chip size of  $1 \times 0.75 \text{ mm}^2$  results from the use of lumped passive elements.

#### **III. POWER AMPLIFIER PERFORMANCE**

The MMIC power amplifier was tested on-wafer under continuous wave (CW) operation (class A) at room temperature and no wafer thinning or extra heat sinking was employed. Fig. 3

(b)

Fig. 2. (a) Schematic of MMIC power amplifier using common-base (CB) SiGe/Si HBT and passive components; (b) photomicrograph of a fabricated MMIC power amplifier (chip size,  $1 \times 0.75$  mm<sup>2</sup>).

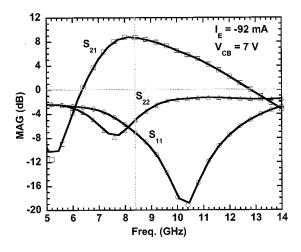

Fig. 3. Small-signal performance of MMIC power amplifier with 8.7 dB gain at 8.4 GHz and input/output return loss of 7.1 dB and 4.9 dB, respectively, at the same frequency.

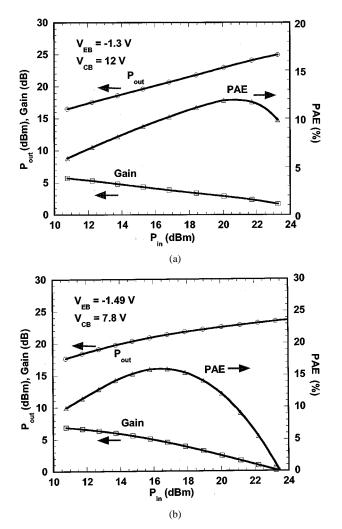

shows the measured small-signal gain and input/output return losses of the power amplifier. At 8.4 GHz and with a bias of  $I_E = -92$  mA and  $V_{CB} = 7$  V, the small-signal gain is 8.7 dB, with input and output return loss of 7.1 dB and 4.9 dB, respectively. These values vary with bias and the goal of these measurements was to optimize the maximum gain. Fig. 4(a) shows the output power, gain and power added efficiency (PAE) as a function of input power, measured at 8.4 GHz, with the HBT biased at  $V_{EB} = -1.3$  V and  $V_{CB} = 12$  V (class A) for maximum output power. The output power at the peak value of PAE (12%)

Fig. 4. (a) Power performance of the SiGe/Si HBT MMIC amplifier biased at  $V_{EB} = -1.3$  V and  $V_{CB} = 12$  V. 23 dBm output power at peak efficiency and 25 dBm in saturation were obtained; (b) power performance of the SiGe/Si HBT MMIC amplifier biased at  $V_{EB} = -1.49$  V and  $V_{CB} = 7.8$  V. Peak PAE of 16% was obtained.

is 23 dBm (200 mW) and 25 dBm (316 mW) in its saturation. Although the design of the circuit was optimized for maximum output power, higher PAE (16%) was observed when the circuit was biased for optimum PAE, as shown in Fig. 4(b). The stability of the CB configuration, compared to that of the CE configuration, has been of concern due to the higher unilateral gain in the former case [6]. However, no oscillation was observed at any bias points, indicating the successful design and implementation of the matching circuits. The small-signal gain of the amplifier (8.7 dB) is 3.5 dB lower than the  $G_{\text{max}}$  (12.2 dB), indicating large losses in the lumped elements. The major portion of the loss originates in the spiral inductors due to their relatively low Q-factors. These inductors are also responsible for the relatively low input/output return loss. The discrete HBTs, fabricated on the same wafer, demonstrate good repeatability of excellent dc and high frequency characteristics. However, dc measurements on the HBTs which are embedded in the circuit show lower current levels with the same applied bias. The reduced current level is a direct consequence of resistive loss in the spiral inductors, which is a major disadvantage of these lumped passive elements, in spite of their small area.

## IV. CONCLUSION

A class A single-stage X-Band MMIC power amplifier incorporating a SiGe/Si HBT and lumped passive components is demonstrated for the first time. At 8.4 GHz, an output power of 23 dBm at peak PAE, 12%, was observed with a saturation output power of 25 dBm. Higher PAE (16%) was also observed when the circuit was biased for this purpose. It was found that the loss of the spiral inductors accounts for the major loss in the MMIC.

#### REFERENCES

A. Schüppen, U. Erben, A. Gruhle, H. Kibbel, H. Schumacher, and U. König, "Enhanced SiGe heterojunction bipolar transistors with 160 GHz-f<sub>max</sub>," in *IEDM Tech. Dig.*, Dec. 1995, pp. 743–746.

- [2] K. Oda, E. Ohue, M. Tanabe, H. Shimamoto, T. Onai, and K. Washio, "130 GHz-f<sub>T</sub> SiGe HBT technology," in *IEDM Tech. Dig.*, Dec. 1997, pp. 791–794.

- [3] U. Erben, M. Wahl, A. Schüppen, and H. Schumacher, "Class-A SiGe HBT power amplifiers at C-band frequencies," *IEEE Microwave Guided Wave Lett.*, vol. 5, pp. 435–436, Dec. 1995.

- [4] Z. Ma, S. Mohammadi, P. Bhattacharya, L. P. B. Katehi, S. A. Alterovitz, and G. E. Ponchak, "A high power and high gain X-band Si/SiGe/Si heterojunction bipolar transistor," *IEEE Trans. Microwave Theory Tech.*, 2001, to be published.

- [5] J.-S. Rieh, L.-H. Lu, L. P. B. Katehi, P. Bhattacharya, E. T. Croke, G. E. Ponchak, and S. A. Alterovitz, "X- and Ku-band amplifiers based on Si/SiGe HBTs and micromachined lumped components," *IEEE Trans. Microwave Theory Tech.*, vol. 46, pp. 685–694, May 1998.

- [6] J.-S. Rieh, L.-H. Lu, Z. Ma, X. Liu, L. P. B. Katehi, P. Bhattacharya, and E. T. Croke, "Small- and large-signal operation of X-band CE and CB SiGe/Si power HBTs," in *IEEE Microwave Theory Tech. Symp. Dig.*, Anaheim, CA, June 1999, pp. 1191–1194.