# Design of Toroidal Inductors Using Stressed Metal Technology

Jeong-Il Kim, Dae-Hee Weon, Jong-Hyeok Jeon, Saeed Mohammadi and Linda P. B. Katehi

School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN 47907-2035

Abstract — This paper presents design, fabrication and characterization of three-dimensional (3-D) toroidal inductors using a stressed metal technology developed at Purdue University. The fabricated 31-turn toroidal inductor on high-resistivity silicon substrate shows inductance value of 25.4 nH and peak quality factor of 14.2. Because of the arc deployment of inductor turns, it is found that a sufficiently narrow turn-to-turn gap is essential to achieve high inductance value. In addition, it is found that, even for toroidal inductors, the substrate effects are the dominant loss mechanism at high frequencies and should be suppressed in order to obtain high values of the quality factor.

Index Terms — Toroidal, three dimensional, on-chip inductor, quality factor, stressed metals.

### I. INTRODUCTION

Lumped inductors have been essentially used in RF applications such as matching networks and RF chokes [1]. Especially, the requirement for high-performance on-chip inductors has been a key issue to enhance the performance of silicon-based RFIC's. To achieve high-Q (quality factor) and high  $S_{RF}$  (Self Resonant Frequency) inductors, many techniques to reduce conductor losses, substrate losses, and parasitic capacitances have been reported. Among them, solenoid-type 3-D inductors showed very high-Q at microwave frequencies [2],[3]. However, noise coupling and electromagnetic interference with neighboring components are implicit in these 3-D structures because the magnetic field is not confined to inductor itself. Toroidal inductors ideally have a concentrated magnetic field along the core that induces little eddy current [1],[4]. These features as well as high inductance values are very attractive to achieve high-performance.

Recent papers demonstrated the performance of micromachined toroidal inductors for RF applications [1],[4],[5]. Microreplicated toroidal inductor fabricated by polymer replication technology [4] showed an inductance of 6.0 nH and a peak Q of 50, but was not compatible with conventional integrated circuit process. On-chip toroidal inductors on low-resistivity Si substrate [1] achieved the quality factor of more than 20, but inductance value of 2.5nH is very low considering its size. These values are comparable to a suspended large circular loop inductor. Another on-chip toroidal inductor on silicon substrate [5] showed low quality factor.

In this work, toroidal inductors are fabricated on low-resistivity (10-20  $\Omega$ .cm) and high-resistivity (10 K $\Omega$ .cm) silicon substrates using recently introduced stressed metal technology [2],[6]. Also, design considerations to obtain high-

performance toroidal inductors are investigated by both experimental characterization and simulation techniques.

#### II. TECHNOLOGY AND DESIGN

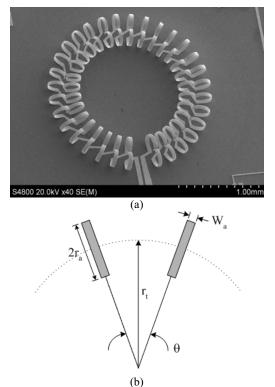

A stressed metal technology is utilized to develop the toroidal inductors on silicon substrates. The appropriate bending moment due to an induced stress gradient is obtained by the use of Au and Cr layers, which are both compatible with integrated circuit fabrication. The detailed process of this technology is described in [2]. Fig. 1(a) shows a fabricated 31 turn toroidal inductor.

To investigate the performance of toroidal inductors, various inductors designs were developed and fabricated on low- and high-resistivity silicon substrates. Design parameters for toroidal inductors are defined as shown in Fig. 1(b). These design parameters are determined by considering the desired RF performance as well as the constraints of the fabrication process.

Fig. 1. Self-assembled toroidal inductor: (a) SEM micro photograph (31 turns) (b) Design parameters

#### III. RESULTS

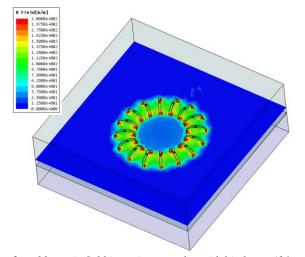

The S-parameters of all fabricated devices were measured using the 8510XF network analyzer and pads parasitics were de-embedded by measuring the matched patterns [7]. Several devices of the same geometry were measured to ensure repeatable measurements. In addition, Ansoft HFSS simulation was performed to predict the performance of toroidal inductors with different design parameters. Fig. 2 shows the simulated magnetic field around a 16 turn toroidal inductor at a frequency of 345MHz. Note that the magnetic field is highly concentrated in the core of the device.

Fig. 2. Magnetic field intensity around toroidal inductor (16 turns and frequency at 345MHz.

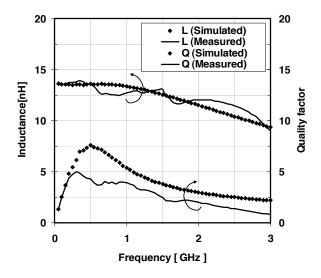

Fig. 3 shows measured and simulated inductance, L, and quality factor, Q, for a 16-turn inductor fabricated on a low-resistivity silicon substrate with a thin  $(0.85\mu m)$  SiO<sub>2</sub> dielectric layer at the top. As can be seen from the figure, the simulated results are comparable to the measured ones. The simulated Q's usually tend to predict higher values than the measured ones due to the inability of the full-wave simulators estimate ohmic losses accurately.

Table 1 summarizes the extracted parameters derived from the measured S-parameterst of the fabricated 16 and 31 turn inductors. On high-resistivity silicon substrate with a  $SiO_2$  of  $0.85\mu m$ , the 31-turn toroidal inductor shows the low-frequency inductance value of 25.4 nH and the peak quality factor of 14.2.

## IV. DISCUSSION

The following results are deduced from both measurement and simulation:

From the magnetic field intensity around the toroidal inductor in Fig. 2, it can be seen that part of the magnetic field penetrates in the center area of the toroid. This part of the magnetic field contributes to a parasitic

lossy planar inductance ( $L_{trace}$ ). According to HFSS simulations, the loss of this inductance increases as the length of the metal footprint on the Si substrate increases. In order to reduce the loss associated with this inductor, either a high resistivity substrate or a substrate backside removal should be utilized.

- When the gap between neighboring turns is wide, the mutual inductances ( $L_{\text{mutual}}$ ) are very low and do not change the value of the total inductance substantially. This is especially true for the toroidal inductor due to the arc deployment of the inductor turns.

- In our 16-turn design, each inductor turn has a value of 0.56 nH (L<sub>s</sub>) while the interconnect metal trace inductor has a self-inductance of 3.4 nH (L<sub>trace</sub>). Simple addition of these inductances (16\*L<sub>s</sub> + L<sub>trace</sub>) results in 12.4 nH for 16-turn inductor, which is very close to the measured results.

Fig. 3. Measured and simulated inductance value and quality factor of 16-turn toroidal inductor on low-resistivity silicon substrate.

**Table 1.** Extracted parameters of toroidal inductors calculated from S-parameters measurement. Inductors in this table have  $r_t = 690 \mu m$  for 16 turns,  $r_t = 820 \mu m$  for 31 turns,  $W_a = 45 \mu m$ ,  $r_a = 155 \mu m$ , and 4  $\mu m$  electroplated Au thickness,

| Substrate      | # of turns | L (nH) | Q <sub>max</sub> | $S_{RF}$ (GHz) |

|----------------|------------|--------|------------------|----------------|

| Low ρ          | 16         | 13.8   | 4.98             | 7.05           |

| (10 - 20 Ω·cm) | 31         | 28.2   | 4.11             | 3.35           |

| High ρ         | 16         | 12.9   | 18.5             | 4.82           |

| (> 10K Ω·cm)   | 31         | 25.4   | 14.2             | 2.98           |

The advantages of toroidal inductors such as lower electromagnetic interference with neighboring components and high inductance values and quality factors can be achieved via optimized designs. Thus, additional design considerations were investigated by the HFSS simulation.

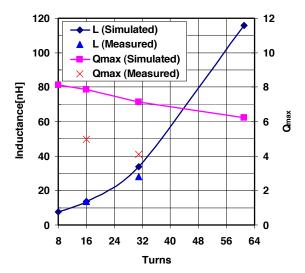

## A. Number of turn (N)

Fig. 4 shows the tradeoff between quality factor and inductance as a function of number of turns in a toroidal inductor. The difference between the theoretical and experimental Q values is attributed to the underestimated ohmic loss by the high-frequency simulator. As the number of turns increases with the fixed radius of toroid (r<sub>1</sub>), the magnetic mutual coupling between inductor turns grows due to the decreased turn-to-turn gap. Note that the inductance values of 31- turn ( $\theta = 11.25$  deg.) and 61-turn ( $\theta = 5.625$ deg.) inductors should be calculated by  $L_{total} = N*L_s + L_{trace} +$ 2\*L<sub>mutual</sub> due to the large mutual inductances, while those of 8- turn ( $\theta = 25$  deg.) and 16-turn ( $\theta = 22.5$  deg.) inductor can be estimated by simple addition of  $L_{total} = N*L_s + L_{trace}$ . The decrease of quality factor with an increasing number of turns can be attributed to the increased parasitic capacitance and RF resistance of interconnect metal traces. The self-resonant frequency naturally decreases due to the increase of inductance at larger number of turns.

Fig. 4. Simulated L and Q versus number of turns (on low-resistivity silicon substrate). Toroid radii  $(r_t)$  of 31-turn inductor are 690  $\mu$ m for simulated results and 820  $\mu$ m for measured ones, respectively.

## B. Gap between turns

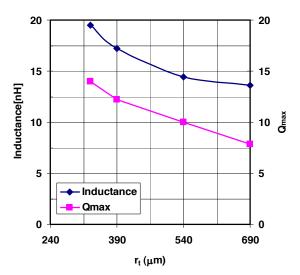

By decreasing the toroid radius  $(r_t)$  when the number of turns are kept constant, the turn-to-turn gap decreases. As a result, the mutual magnetic coupling increases resulting in a higher overall inductance as shown in Fig. 5. Also note that the quality factor increases with a decreasing radius of the toroid due to reduced length of the interconnect metal footprints on the Si substrate.

Fig. 5. Simulated L and Q versus toroid radius (16-turn on low-resistivity silicon substrate).

#### C. Width of inductor turns

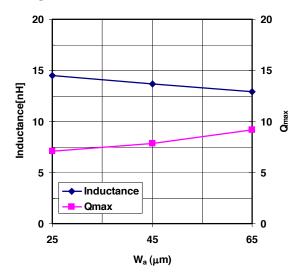

As shown in Fig. 6, the quality factor increases with an increasing width of the inductor turns due to the lower dc resistance. However, the inductance value decreases due to higher parasitic effects. Same behavior is generally observed in most planar and three-dimensional inductors.

Fig. 6. Simulated L and Q versus width of inductor turn (16-turn on low-resistivity silicon substrate)

## D. Substrate effect

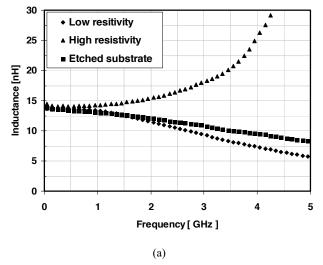

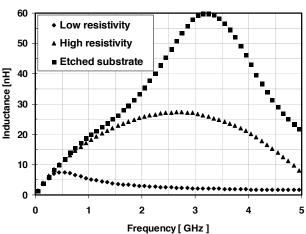

Fig. 7 depicts that effect of substrate loss on the inductance value and the quality factor of toroidal inductors on low and high resistivity silicon substrates as well as etched substrates (inductor on a membrane). Low-frequency inductance values do not change as the substrate loss changes, while the quality factor shows a noticeable improvement, especially at high

frequencies, when the inductor is printed on a high-resistivity or etched substrate [8] This is due to the reduction of the parasitic capacitance.

Fig. 7. Simulated results with different substrate: (a) L and (b) Q

## VII. CONCLUSION

Toroidal inductors based on a stressed metal technology were fabricated and inductor performances versus design parameters were investigated. From measured and simulated results, it seems obvious even for a toroidal inductor on a silicon substrate that the substrate effects should be eliminated in order to achieve a high quality factor. This can be obtained by using a high-resistivity substrate, insulator on silicon substrate, or substrate removal via etching (inductor on

membrane). Also, the gap between the inductor turns should be narrow enough to take advantage of the mutual inductance effect. We believe that the innermost gap of less than  $50\mu m$  is suitable for our toroidal inductors. The advantages of toroidal inductors such as high inductance value, high quality factor, and less electromagnetic interference with neighboring components make them suitable for a number of interesting RF applications.

### ACKNOWLEDGEMENT

This work is supported by DARPA Technology for Efficient and Agile Microsystems (TEAM) DAAB07-02-1-L430.

#### REFERENCES

- [1] W. Y. Liu, J. Suryanarayanan, J. Nath, S. Mohammadi, L. P. B. Katehi, and M. B. Steer, "Toroidal Inductors for Radio-Frequency Integrated Circuits," *IEEE Trans. Microwave Theory & Tech.*, vol. 52, no. 2, pp. 646-654, Feb. 2004.

- [2] D. -H. Weon, J. -H. Jeon, J. -I. Kim, S. Mohammadi, and L. P. B. Katehi, "High-Q Integrated 3-D Inductors and Transformers for High Frequency Applications", 2004 IEEE MTT-S Int. Microwave Symp., pp. 877 880, June 2004.

- [3] H. Lu, B. Pillans, and J. B. Lee, "Micromachined On-Chip High-Aspect Ratio Air Core Solenoid Inductors for Multi-GHz Applications", 2004 IEEE MTT-S Int. Microwave Symp., pp. 881 – 884, June 2004.

- [4] V. Ermolov, T. Lindström, H. Nieminen, M. Olsson, M. Read, T. Ryhänen, S. Silanto, and S. Uhrberg, "Microreplicated RF Toroidal Inductor," *IEEE Trans. Microwave Theory & Tech.*, vol. 52, no. 1, pp. 29-37, Jan. 2004.

- [5] K. L. Scott, T. Hirano, H. Yang, H. Singh, R. T. Howe, and A. M. Niknejad, "High-Performance Inductors Using Capillary Based Fluidic Self-Assembly," *J. Microelectromech. Syst.*, vol. 13, no. 2, pp. 300-309, Apr. 2004.

- [6] K. Van Schuylenbergh, C. L. Chua, D. K. Fork, J. Lu, and B. Griffiths, "Self-assembled out-of-plane high-Q integrated inductors" 2002 IEEE Int. Electron Device Meeting (IEDM), pp. 479-482, Dec. 2002.

- [7] K. Schimpf, B. Benna, and D. Proetel, "A new approach to characterize substrate losses of on-chip inductors," *Proc. IEEE* 2001 Int. Conference on Microelectronic Test Structures, Vol. 14, pp. 115-118, March 2001.

- [8] D. -H. Weon, J. -I. Kim, J. -H. Jeon, S. Mohammadi, and L. P. B. Katehi, "High Performance Micro-Machined Inductors on CMOS Substrate", 2005 IEEE MTT-S Int. Microwave Symp., submitted