# High Performance Micro-Machined Inductors on CMOS Substrate

Dae-Hee Weon, Jeong-Il Kim, Jong-Hyeok Jeon, Saeed Mohammadi, and Linda P. B. Katehi

School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN 47907-2035

Abstract – Using a combination of micromachining and three-dimensional (3-D) processing technologies, we have designed, fabricated, and tested inductors on CMOS grade Si substrate ( $10\sim20~\Omega$ -cm resistivity) which exhibit very high quality factor and high resonant frequency. A 1.2 nH inductor in this process achieves a record high quality factor of  $\sim140$  at 12GHz, with Q > 100 for frequencies between 8 to 20GHz. The technology to fabricate these inductors is based on one step deposition and electroplating of a stressed layered metal combination of Cr and Au and is fully compatible with CMOS technology.

Index Terms – high quality factor, high frequency, CMOS compatible, three dimensional, stressed metal, micromachining, integrated inductor.

## I. INTRODUCTION

The requirement for high performance passive elements is the most stringent in designing stateof-the-art radio frequency integrated circuits (RFICs). High-Q inductors play a very important role in the performance achieved by RFICs such as voltage controlled oscillators (VCOs), low-noise amplifiers (LNAs), filters, mixers, and power amplifiers (PAs) [1]-[4]. By the advent of deep submicron CMOS and SiGe heterojunction bipolar technologies, the operating frequency of Si-based RFICs has been increasing up to W-band frequency range. While at very high frequencies (>30GHz), transmission line sections are the inductive elements of choice because they exhibit reasonably high quality factors [5], at lower frequencies (< 20GHz) lumped element inductors are preferred because of their relatively small dimensions.

The quality factor and resonant frequency of integrated spiral inductors on a CMOS substrate are usually very low, because of substrate losses and ohmic losses due to the finite thickness of inductor metals. Several papers have reported

unconventional on-chip inductors integrated with RF circuits, such as voltage controlled oscillators (VCOs) [6],[7] and power amplifier (PA) [8]. There have been reports on suspended spiral inductors [9]-[11] and vertical spiral inductors [12], all of them limited to modest quality factors and relatively low self-resonance frequencies. Recently, spiral inductors with a quality factor above 100 and self resonant frequency above 50GHz have been demonstrated. These inductors were suspended over a low loss ceramic substrate and had a copper metal thickness above 50µm [13].

We have previously reported novel micromachined technology developed specifically for the design and fabrication of high performance 3-D inductors [14]. In that demonstration, a 1nH inductor was fabricated on high resistivity Si substrate (>10k  $\Omega$ ·cm) and exhibited a quality factor of Q > 60 at frequencies from 3 GHz to 7 In the work presented herein, we are reporting a variety of micro-machined high-Q and high frequency 3-D inductors fabricated on low resistivity Si substrates (10~20 Ω·cm) using a stressed metal technology. A combination of backside dry and wet etching has been utilized to improve the performance of these inductors by removing the substrate material and thus reducing the substrate parasitics. A 1.2nH inductor using this technology achieves a self-resonant frequency,  $f_{sr} > 40GHz$  and a quality factor, Q > 100 at frequencies from 8GHz to 20 GHz. To our knowledge these are the highest reported quality self-resonance frequencies and inductors fabricated on CMOS grade substrate.

## II. TECHNOLOGY

The inductors presented herein are based on a recently developed stressed metal technology [14] in which a Cr/Au metal layered-combination is deposited to create a metal with a built-in stress.

This built-in stress is used to create a spiral inductor printed on a thin dielectric membrane. The CMOS substrate underneath the inductor is removed by using a combination of dry and wet etching. This post-CMOS fabrication method results in three-dimensional inductors with excellent high-frequency performance. This technology has allowed us to use CMOS grade substrate to achieve record high performance inductors.

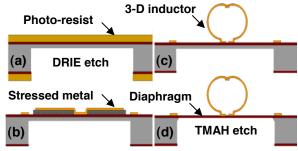

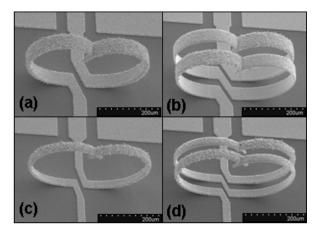

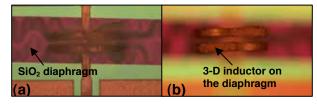

Fig. 1 shows the process sequence that is followed to fabricate the demonstrated micro-machined inductors. First, the oxidized Si substrate is etched by DRIE from the backside of the areas underneath the inductors to achieve a thinned Si substrate with a thickness of less than 100 µm (Fig. 1(a)). Then, the three dimensional inductors are fabricated (Fig. 1(b) and (c)) on these areas using the previously reported stressed metal technology [14]. A Au electroplating step is then performed to improve the metal contact resistance and also the rigidity of the structure. Fig. 2 shows the fabricated one-turn and two-turn inductors at this stage. Finally, the remained Si substrate was etched from the back using TMAH (Fig. 1(d)). The 3-D inductors on a 0.85 µm SiO<sub>2</sub> diaphragm after TMAH etch are shown in Fig. 3. With the lossy Si substrate underneath the inductors replaced by a thin SiO<sub>2</sub> diaphragm, the inductors show a high quality factor and high self-resonant frequency.

**Fig. 1.** Schematic cross-sectional views of the fabrication process flow for 3-D inductor on SiO<sub>2</sub> diaphragm.

To investigate the effects of the substrate and resulting loss and parasitic capacitances on the performance of the inductors, we have fabricated and characterized inductors with one and two turns and metal line widths of 25  $\mu$ m, 35  $\mu$ m, and 45  $\mu$ m before and after substrate etch. In addition, to assess the impact of the substrate loss we

compared the performance of inductors fabricated on low and high resistivity substrates.

### III. RF CHARACTERIZATION

**Fig. 2.** SEM microphotographs of 3-D inductors fabricated on partially thinned Si substrate (a) 1 turn and 45  $\mu$ m width (b) 2 turn and 45  $\mu$ m width (c) 1 turn and 25  $\mu$ m width (d) 2 turn and 25  $\mu$ m width.

**Fig. 3.** Microscope images of 3-D inductor (2 turn and 45  $\mu$ m width) fabricated on SiO<sub>2</sub> diaphragm (a) focused on the diaphragm (b) focused on the inductor.

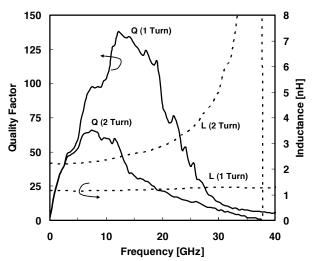

**Fig. 4.** Measured quality factor and inductance value of 1-turn and 2-turn inductors fabricated with 45  $\mu$ m width on SiO<sub>2</sub> diaphragm.

The S-parameters of the fabricated inductors were measured using the Agilent 8722 network analyzer. To perform accurate quality factor measurements when the values are very high, a very thorough calibration and accurate de-embedding of pads parasitics is needed [16]. Herein, several inductors of the same geometry were measured to ensure repeatability in the measurements. The deviation of the measurement values was within 3%. Fig. 4 shows the measured quality factor, Q, and inductance, L, extracted from the measured Sparameters for one-turn and two-turn inductors fabricated using the presented technology. As can be seen from this figure, for one-turn inductor, a peak Q of 138 is achieved at 12GHz. The selfresonant frequency of the inductor is over 40GHz. For the two-turn inductor, a maximum Q of 66 and self-resonant frequency of 38 GHz are achieved.

| # of<br>Turns | Width<br>[µm] | L<br>[nH] | Quality Factor | SRF<br>[GHz] |

|---------------|---------------|-----------|----------------|--------------|

| 1             | 25            | 1.23      | 38.2@7.0GHz    | >40          |

| 1             | 35            | 1.22      | 51.6@7.5GHz    | >40          |

| 1             | 45            | 1.16      | 137.5@12GHz    | >40          |

| 2             | 25            | 2.60      | 30.5@3.0GHz    | 33           |

| 2             | 35            | 2.45      | 32.8@3.5GHz    | 35           |

| 2             | 45            | 2.20      | 66.1@7.5GHz    | 38           |

**Table 1.** Extracted parameters of 3-D inductors calculated from S-parameters measurement. Inductors in this table have  $20\mu m$  gap between the fingers and  $350\mu m$  diameter and  $4.0\mu m$  electroplated Au thickness.

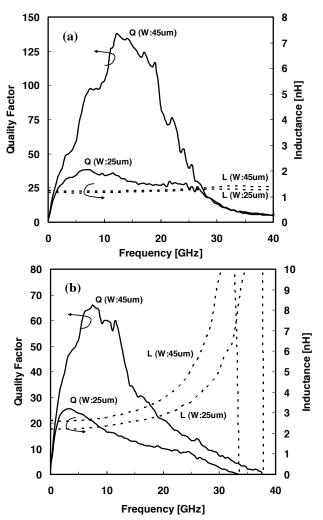

Fig. 5 shows the quality factor, Q, and inductance, L, extracted from the measured S-parameters for one-turn and two-turn inductors fabricated on a 0.85µm SiO<sub>2</sub> diaphragm with different widths of the spiral turns. As shown in the figure, the inductor with 45µm width has a higher quality factor and self-resonant frequency than the inductor with 25µm finger width. Table 1 summarizes the performance of several inductors fabricated using the presented this technology. The data is extracted from the S-parameter measurement.

The following conclusions have been derived from the measured data were:

The inductance value increases with the number of turns in a perfectly quadratic

- manner. This is due to the high mutual inductance in the two-turn inductors.

- Increasing the width of the conductor increases the quality factor significantly while it changes the self-resonant frequency only marginally.

**Fig. 5.** Measured quality factor and inductance value of (a) 1-turn inductors (b) 2-turn inductors with different finger widths on SiO<sub>2</sub> diaphragm.

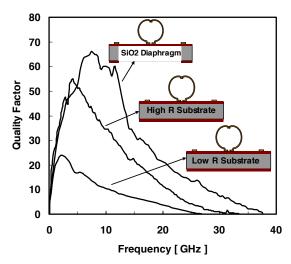

To investigate the effect of the Si substrate on the inductor performance, we have also measured the RF performance of two-turn inductors in terms of the quality factor, Q, and inductance, L, as functions of frequency. The Q and L values were extracted from the measured S-parameters. The inductor had a metal width of 45  $\mu$ m and was fabricated on a low-resistivity Si substrate (10~20  $\Omega$ ·cm), high-resistivity Si substrate (>10k  $\Omega$ ·cm) [14], and a 0.85  $\mu$ m SiO<sub>2</sub> diaphragm. As expected, the inductors printed on the diaphragm have the

highest quality factor and self-resonant frequency as compared to those fabricated on the low and high resistivity substrates.

The following conclusions were deducted from the measurements:

- The quality factor increases with the resistivity of the substrate.

- Eliminating the substrate drastically increases quality factor of the inductor.

- High-Q and high frequency inductors can be fabricated with CMOS substrate using a post CMOS micromachining process.

### IV. CONCLUSION

Various three-dimensional inductors were fabricated on a low resistivity silicon substrate using a post-CMOS stressed metal technology [14]. These inductors exhibited a very high self resonant frequency and a very high quality factor compared to their printed spiral counterparts. Quality factors above 100 were measured at frequencies up to 20GHz. The availability of high-Q and high self-resonant inductors on CMOS technology will open up new design directions for RF and microwave integrated circuits.

**Fig. 6.** Measured data of quality factor and inductance of 2-turn inductor fabricated on low resistivity Si substrate, on high resistivity Si substrate and on SiO<sub>2</sub> diaphragm.

## **ACKNOWLEDGEMENTS**

This work is supported by DARPA Technology for Efficient and Agile Microsystems (TEAM) DAAB07-02-1-L430.

#### **REFERENCES**

- T.H. Lee, The Design of CMOS Radio-Frequency Integrated Circuits. Cambridge, U.K.: Cambridge Univ. Press. 1998.

- [2] D.K. Shaeffer and T.H. Lee, "A 1.5 V, 1.5 GHz CMOS low noise amplifier," *IEEE J.Solid-State Circuits.*, vol.32, pp. 745-759, May 1997.

- [3] M.D.M. Hershenson, A. Hajimiri, S.S. Mohan, S.P. Boyd, and T.H. Lee, "Design and optimization of LC oscillators," in 1999 IEEE/ACM Int. Conf. Computer-Aided Design Tech. Dig., pp. 65-69.

- [4] T. Sowlati, C. Andre, J. Sitch, G. Rabjohn, and D. Smith, "Low Voltage, High Efficiency GaAs Class E Power Amplifiers for Wireless Transmitters," *IEEE J.Solid-State Circuits.*, vol.30, pp. 1074-1080, October 1995.

- [5] C.H. Doan et. al, "Design of CMOS for 60GHz applications," IEEE International Solid-State Circuits Conference, ISSCC, pp. 440 - 538 Vol.1, 2004.

- [6] J. W. M. Rogers, V. Levenets, C. A. Pawlowicz, N. G. Tarr, T. J. Smy, and C. Plett, "Post-processed Cu inductors with application to a completely integrated 2-GHz VCO," *IEEE Trans. Electron Devices*, vol. 48, pp. 1284–1287, June 2001.

- [7] E.-C. Park, J.-B. Yoon, S. Hong, and E. Yoon, "A 2.6 GHz low phasenoise VCO monolithically integrated with high Q MEMS inductors," in 28th Eur. Solid-State Circuits Conf., Sept. 2002.

- [8] Y. E. Chen, Y. K. Yoon, J. Laskar, and M. Allen, "A 2.4 GHz integrated CMOS power amplifier with micromachined inductors," in *IEEE Int. Microwave Symp. Dig.*, June 2001, pp. 523–526.

- [9] J.-B. Yoon, et al. "High-performance three-dimensional on-chip inductors fabricated by novel micromachining technology for RF MMIC," in *IEEE Int. Microwave Symp.Dig.*, June 1999, pp. 1523–1526.

- [10] J. Y. Park and M. G. Allen, "High Q spiral-type microinductors on silicon substrates," *IEEE Trans. Magn.*, vol. 35, pp. 3544–3546, Sept. 1999.

- [11] J.-B. Yoon, C.-H. Han, E. Yoon, and C.-K. Kim, "Monolithic high-Q overhang inductors fabricated on silicon and glass substrates," in *IEDM Tech. Dig.*, Dec. 1999, pp. 753–756.

- [12] J. Zou, J. G. Nickel, D. Trainor, C. Liu, and J. E. chutt-Aine, "Development of vertical planar coil inductors using plastic deformation magnetic assembly (PDMA)," in *IEEE Int. Microwave Symp. Dig.*, June 2001, pp. 193–196.

- [13] S.Pinel, et al, "Very high-Q inductors using RF-MEMS technology for System-On-Package wireless communication integrated module," 2003 IEEE MTT-S Int. Microwave Symp. Dig., June 2004, pp. 1497-1500.

- [14] Dae-Hee Weon, Jong-Hyeok Jeon, Jeong-Il Kim, Saeed Mohammadi, and Linda P. B. Katehi, "High-Q Integrated 3-D Inductors and Transformers for High Frequency Applications" 2004 IEEE MTT-S Int. Microwave Symp. Dig., June 2004, pp. 877-880.

- [15] T.M. Weller et al., "New results using membrane-supported circuits: a Ka-band power amplifier and survivability testing," *IEEE Transactions on Microwave Theory and Techniques*, V44, N9, Sept. 1996 pp. 1603-1606

- [16] K. Schimpf et al., Proc. IEEE 2001 Int. Conference on Microelectronic Test Structures, Vol.14, March 2001 pp. 115.