## ECE 573

Problem Set 5: Register allocation

For the following problems, use the following piece of three-address code (the target of each instruction is the last temporary listed):

- 1. ld a, T1

- 2. ld b, T2

- 3. + T1, T2, T3

- 4. ld c, T4

- 5. + T1, T2, T5

- 6. + T4, T5, T6

- 7. + T3, T6, T7

- 8. + T7, a

When performing register allocation for this code, assume that only temporaries are assigned to registers.

1. We perform liveness analysis from the bottom up (so read the table from the bottom up, including comments):

| Inst | Live temps     | Comments                                                                        |

|------|----------------|---------------------------------------------------------------------------------|

| 1    | T1             | T2 killed in instruction 2, so not live.                                        |

| 2    | T1, T2         | T3 killed in instruction 3, so not live.                                        |

| 3    | T1, T2, T3     | T4 killed in instruction 4, so not live.                                        |

| 4    | T1, T2, T3, T4 | T5 killed in instruction 5, so not live, T1, T2 used in instruction 5, so live. |

| 5    | T3, T4, T5     | T6 killed in instruction 6, so not live. T4, T5 used in instruction 6, so live. |

| 6    | T3, T6         | T7 killed in instruction 7, so not live. T3, T6 used in instruction 7, so live. |

| 7    | T7             | T7 used in instruction 8, so live.                                              |

| 8    | _              | Nothing live after 8.                                                           |

- 2. After instruction 4, there are four live variables, so we would need 4 registers to perform register allocation without spilling.

- 3. The register assignments are as follows

| Inst | R1 | R2 | R3 | Comment                                |

|------|----|----|----|----------------------------------------|

| 1    | T1 |    |    |                                        |

| 2    | T1 | T2 |    |                                        |

| 3    | T1 | T2 | Т3 |                                        |

| 4    | T1 | T2 | T4 | Spill T3, since it isn't used until 7  |

| 5    | T5 |    | T4 | Free T1, T2                            |

| 6    | T6 |    | _  | Free T4, T5                            |

| 7    | T7 |    |    | Free T6, T3 loaded into R2, then freed |

| 8    | _  |    |    |                                        |

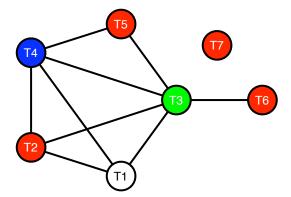

4. The interference graph for the code above is given below:

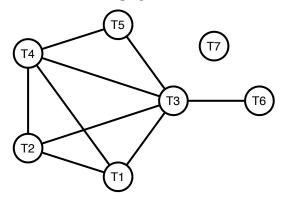

5. The order of simplification is given in the table below (the convention I am using is to remove as many nodes with 2 edges first, then nodes with 1 edge, then nodes with 0 edges), along with the simplified graph. I will stop once I get to a graph with just three nodes.

| Inst | Var removed | Simplified graph |

|------|-------------|------------------|

| 1    | <b>T</b> 5  | T4 T7 T6 T6      |

| 2    | Т6          | T4 T7 T3         |

| 3    | Т7          | T4 T3 T3         |

| 4    | T1 (spill)  | T2 T3            |

We will thus put T2, T3 and T4 in registers R1, R2 and R3, respectively, then T1 is spilled, then T7 is placed in R1, then T6 is placed in R1, then T5 is placed in R1. The colored graph (with red, green and blue assigned to R1, R2 and R3 respectively) is: