# Introduction Scheduling (Part 1) Introduction and Acyclic Scheduling

CS 380C: Advanced Compiler Techniques

Thursday, October 11th 2007

▲□▶ ▲□▶ ▲三▶ ▲三▶ 三三 のへで

### Code Generator

- Back end part of compiler (code generator)

- Instruction scheduling

- Register allocation

### Instruction Scheduling

- Input: set of instructions

- Output: total order on that set

| Lecture Overview | Introduction | Constraints | List Scheduling | Conclusion |

|------------------|--------------|-------------|-----------------|------------|

|                  |              |             |                 |            |

|                  |              |             |                 |            |

| Lecture Ou       | ıtline       |             |                 |            |

### Lectures

- Introduction and acylic scheduling (today)

- Software pipelining (Tuesday 23)

## Today

- Definition of instruction scheduling

- Constraints

- Scheduling process

- Acylic scheduling: list scheduling

## Introduction to Instruction Scheduling

#### Context

- Backend part of the compiler chain (code generation)

- Inputs: set of instructions (assembly instructions)

- Outputs: a schedule

- Set of scheduling dates (one date per instruction)

- Total order

#### Goal

- Minimize the execution time (number of cycles)

- Different possible objective functions to minimize:

- Power consumption

- . . .

| Lecture Overview | Introduction | Constraints | List Scheduling | Conclusion |

|------------------|--------------|-------------|-----------------|------------|

|                  |              |             |                 |            |

|                  |              |             |                 |            |

| Constraints      |              |             |                 |            |

• Is it possible to generate any schedule?

| Lecture Overview | Introduction | Constraints | List Scheduling | Conclusion |

|------------------|--------------|-------------|-----------------|------------|

|                  |              |             |                 |            |

|                  |              |             |                 |            |

| Constraints      |              |             |                 |            |

• Is it possible to generate any schedule?

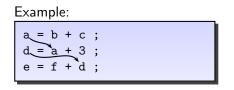

Example:

a = b + c ; d = a + 3 ;e = f + d ; • Possibility to change instruction order?

▲□▶ ▲□▶ ▲三▶ ▲三▶ 三三 のへで

| Lecture Overview | Introduction | Constraints | List Scheduling | Conclusion |

|------------------|--------------|-------------|-----------------|------------|

|                  |              |             |                 |            |

|                  |              |             |                 |            |

| Constraints      |              |             |                 |            |

• Is it possible to generate any schedule?

- Possibility to change instruction order?

- No, because of *data dependences*

- Flow dependences on a and d

◆□▶ ◆□▶ ◆□▶ ◆□▶ □ のQ@

• Data dependences enforce a partial order for the final schedule

◆□ ▶ ◆□ ▶ ◆ □ ▶ ◆ □ ▶ ● □ ● ● ● ●

• Other types of constraints?

- Data dependences enforce a partial order for the final schedule

- Other types of constraints?

Example:

a = b + c ;d = e + f ; • Target architecture with 1 ALU

▲□▶ ▲□▶ ▲三▶ ▲三▶ 三三 のへで

- Data dependences enforce a partial order for the final schedule

- Other types of constraints?

Example:

a = b + c ;d = e + f ;

- Target architecture with 1 ALU

- Impossible to use the same functional unit concurrently

◆□▶ ◆□▶ ◆□▶ ◆□▶ □ のQ@

Resource constraints

- Data dependences enforce a partial order for the final schedule

- Other types of constraints?

Example:

a = b + c ;d = e + f ;

- Target architecture with 1 ALU

- Impossible to use the same functional unit concurrently

- Resource constraints

## Constraints

• Two types of constraints: *data dependences* and *resource usage*

## Constraints influencing Instruction Scheduling

### Constraints

- Data dependences

- Resource constraints

### Rule

• The final schedule *must* respect these constraints

### Dealing with constraints

How to represent such constraints to deal with during the scheduling process?

## Constraints influencing Instruction Scheduling

#### Constraints

- Data dependences

- Resource constraints

### Rule

• The final schedule *must* respect these constraints

### Dealing with constraints

- How to represent such constraints to deal with during the scheduling process?

- Data dependences  $\rightarrow$  graph

- Resource constraints → reservation tables or automaton

## Data Dependence Representation

### Data Dependence Graph (DDG)

- 1 node  $\Leftrightarrow$  1 instruction

- 1 edge  $\Leftrightarrow$  1 flow dependence (directed graph)

- Edge label = parameters of the dependence

- Latency (# of cycles)

- Distance (# of iterations)

(日) (日) (日) (日) (日) (日) (日)

## Data Dependence Representation

## Data Dependence Graph (DDG)

- 1 node  $\Leftrightarrow$  1 instruction

- 1 edge  $\Leftrightarrow$  1 flow dependence (directed graph)

- Edge label = parameters of the dependence

- Latency (# of cycles)

- Distance (# of iterations)

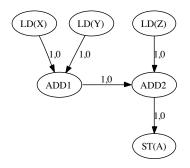

## • Example (1-cycle latency):

a = b + c ; // ADD1 d = a + 3 ; // ADD2 e = a + d ; // ADD3

## Data Dependence Representation

## Data Dependence Graph (DDG)

- 1 node  $\Leftrightarrow$  1 instruction

- 1 edge  $\Leftrightarrow$  1 flow dependence (directed graph)

- Edge label = parameters of the dependence

- Latency (# of cycles)

- Distance (# of iterations)

• Example (1-cycle latency):

a = b + c ; // ADD1 d = a + 3 ; // ADD2 e = a + d ; // ADD3

(1) 「 「 」 ( 目 ) ( 目 ) ( 日 )

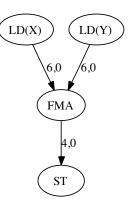

• Daxpy loop: *double alpha times X plus Y*

•

$$y \leftarrow \alpha \times x + y$$

- Targeting Itanium ISA:

- LD: Load from memory (latency 6 cycles from L2 cache)

- ST: Store to memory

- FMA: Fuse multiply and add (latency 4 cycles)

## Data Dependence Representation – Example 2

Daxpy loop: double alpha times X plus Y

•

$$y \leftarrow \alpha \times x + y$$

- Targeting Itanium ISA:

- LD: Load from memory (latency 6 cycles from L2 cache)

- ST: Store to memory

- FMA: Fuse multiply and add (latency 4 cycles)

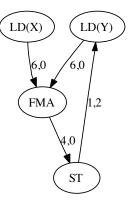

## Data Dependence Representation – Example 3

- Daxpy loop with inter-iteration dependence

- Inter-iteration dependence

- Distance of 2

## Data Dependence Representation – Example 3

- Daxpy loop with inter-iteration dependence

- Inter-iteration dependence

- Distance of 2

◆□▶ ◆□▶ ◆□▶ ◆□▶ □ ○○○

## Data Dependence Representation

#### Remarks

- Circuits allowed for a distance > 0

- For basic block, this is only a DAG

### Drawbacks

- One fix digit for latency

- Fixed latencies

- May not be suitable for cache/memory accesses

- One digit for the distance

- Only uniform dependences

◆□▶ ◆□▶ ◆三▶ ◆三▶ ○○○

## Resource Constraint Representation

#### Resources

• Second set of constraints: resource usage/assignment

#### Overview

- Need to check if two instructions may race for the same resource (functional unit, bus, pipeline stage, ...)

- Can be several cycles ahead (latency > 1)

## Resource Constraint Representation

#### Resources

Second set of constraints: resource usage/assignment

#### Overview

- Need to check if two instructions may race for the same resource (functional unit, bus, pipeline stage, ...)

- Can be several cycles ahead (latency > 1)

#### State-of-the-art

• 2 representations: reservation tables and automaton

## Reservation Tables – Definition

### Reservation tables

• Intuitive way: resource usage of one instruction as a 2D table

#### Semantics

- Rows: latency of the instruction (in cycles)

- Columns: number of resources available in the target architecture

- Cell (i, j) is marked ⇔ instruction requires i<sup>th</sup> resource during its j<sup>th</sup> cycle of execution

- Binary tables

- Several tables per instruction (alternatives/options)

◆□▶ ◆□▶ ◆□▶ ◆□▶ □ のQ@

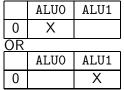

Example with pipelined resources:

- 2 fully pipelined resources (ALU): ALU0 and ALU1

- 2 instructions ADD and MUL

- Constraints:

- ADD can be executed on ALUO or ALU1

- MUL can only be executed on ALU1

Example with pipelined resources:

- 2 fully pipelined resources (ALU): ALU0 and ALU1

- 2 instructions ADD and MUL

- Constraints:

- ADD can be executed on ALU0 or ALU1

- MUL can only be executed on ALU1

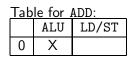

Tables for ADD:

| Tab | Table for MUL: |      |  |

|-----|----------------|------|--|

|     | ALUO           | ALU1 |  |

| 0   |                | Х    |  |

◆□▶ ◆□▶ ◆□▶ ◆□▶ □ のQ@

## Reservation Tables – Example 1

## ADD instruction:

|   | ALUO | ALU1 |

|---|------|------|

| 0 | Х    |      |

OR

|   | ALUO | ALU1 |

|---|------|------|

| 0 |      | Х    |

MUL instruction:

|   | ALUO | ALU1 |

|---|------|------|

| 0 |      | Х    |

| ٩ | Are th | ne | followi | ng sequend | ces valid? |

|---|--------|----|---------|------------|------------|

|   | ADD    | I  | ADD     | ?          |            |

|   | ADD    | Ι  | MUL     | ?          |            |

|   | MUL    | I  | MUL     | ?          |            |

|   | ADD    | ;  | ADD     | ?          |            |

|   | ADD    | Т  | MUL :   | MUL. 7     |            |

▲□▶ ▲□▶ ▲三▶ ▲三▶ 三三 のへで

## Reservation Tables – Example 1

## ADD instruction:

|   | ALUO | ALU1 |

|---|------|------|

| 0 | Х    |      |

OR

|   | ALUO | ALU1 |

|---|------|------|

| 0 |      | Х    |

MUL instruction:

|   | ALUO | ALU1 |

|---|------|------|

| 0 |      | Х    |

| ٩ | Are th | ie | follov | vin | g se | quences      | valid? |

|---|--------|----|--------|-----|------|--------------|--------|

|   | ADD    | Ι  | ADD    |     |      | $\checkmark$ |        |

|   | ADD    | I  | MUL    |     |      |              |        |

|   | MUL    | I  | MUL    |     |      | ×            |        |

|   | ADD    | ;  | ADD    |     |      | $\checkmark$ |        |

|   | ADD    | I  | MUL    | ;   | MUL  | . 🗸          |        |

|   |        |    |        |     |      |              |        |

## ADD instruction:

|   | ALUO | ALU1 |

|---|------|------|

| 0 | Х    |      |

OR

|   | ALUO | ALU1 |

|---|------|------|

| 0 |      | Х    |

MUL instruction:

|   | ALUO | ALU1 |

|---|------|------|

| 0 |      | Х    |

| ٩ | Are th | ie | follov | vin | g se | quences      | valid? |

|---|--------|----|--------|-----|------|--------------|--------|

|   | ADD    | I  | ADD    |     |      | $\checkmark$ |        |

|   | ADD    | I  | MUL    |     |      |              |        |

|   | MUL    | I  | MUL    |     |      | ×            |        |

|   | ADD    | ;  | ADD    |     |      | $\checkmark$ |        |

|   | ADD    | I  | MUL    | ;   | MUL  | . V          |        |

|   |        |    |        |     |      |              |        |

- Test if instructions can be scheduled together: AND operation

- Update resource usage: OR operation

◆□▶ ◆□▶ ◆□▶ ◆□▶ □ のQ@

Example with complex resources:

- 2 resources: ALU and LD/ST

- 3 instructions ADD, SUB and LD

- Constraints:

- ADD instructions have a latency of 1 cycle

- SUB instructions have a latency of 2 cycles

- LD uses first the ALU for 1 cycle and then the LD/ST resource for 1 cycle

◆□▶ ◆□▶ ◆□▶ ◆□▶ □ のQ@

Example with complex resources:

- 2 resources: ALU and LD/ST

- 3 instructions ADD, SUB and LD

- Constraints:

- ADD instructions have a latency of 1 cycle

- SUB instructions have a latency of 2 cycles

- LD uses first the ALU for 1 cycle and then the LD/ST resource for 1 cycle

| Tab | Table for SUB: |       |  |  |

|-----|----------------|-------|--|--|

|     | ALU            | LD/ST |  |  |

| 0   | Х              |       |  |  |

| 1   | Х              |       |  |  |

◆□▶ ◆□▶ ◆□▶ ◆□▶ □ ○○○

### ADD instruction:

|   | ALU | LD/ST |

|---|-----|-------|

| 0 | Х   |       |

SUB instruction:

|   | ALU | LD/ST |

|---|-----|-------|

| 0 | Х   |       |

| 1 | Х   |       |

LD instruction:

|   | ALU | LD/ST |

|---|-----|-------|

| 0 | Х   |       |

| 1 |     | Х     |

## • Are the following sequences valid?

| ADD   SUB      | ? |

|----------------|---|

| ADD   ADD      | ? |

| SUB   LD       | ? |

| LD ; ADD       | ? |

| LD ; SUB       | ? |

| SUB ; LD       | ? |

| ADD ; SUB ; LD | ? |

| LD ; ADD ; SUB | ? |

▲□▶ ▲□▶ ▲□▶ ▲□▶ ▲□ ● ● ●

### ADD instruction:

|   | ALU | LD/ST |

|---|-----|-------|

| 0 | Х   |       |

SUB instruction:

|   | ALU | LD/ST |

|---|-----|-------|

| 0 | Х   |       |

| 1 | Х   |       |

LD instruction:

|   | ALU | LD/ST |

|---|-----|-------|

| 0 | Х   |       |

| 1 |     | Х     |

### • Are the following sequences valid?

| ADD   SUB      | $\times$ |

|----------------|----------|

| ADD   ADD      | $\times$ |

| SUB   LD       | $\times$ |

| LD ; ADD       |          |

| LD ; SUB       |          |

| SUB ; LD       | $\times$ |

| ADD ; SUB ; LD | $\times$ |

| LD ; ADD ; SUB |          |

▲□▶ ▲□▶ ▲三▶ ▲三▶ 三三 のへで

#### ADD instruction:

|   | ALU | LD/ST |

|---|-----|-------|

| 0 | Х   |       |

SUB instruction:

|   | ALU | LD/ST |

|---|-----|-------|

| 0 | Х   |       |

| 1 | Х   |       |

LD instruction:

|   | ALU | LD/ST |

|---|-----|-------|

| 0 | Х   |       |

| 1 |     | Х     |

• Are the following sequences valid?

| ADD   SUB      | ×        |

|----------------|----------|

| ADD   ADD      | $\times$ |

| SUB   LD       | $\times$ |

| LD ; ADD       |          |

| LD ; SUB       |          |

| SUB ; LD       | $\times$ |

| ADD ; SUB ; LD | $\times$ |

| LD ; ADD ; SUB |          |

• Test and update according to latencies of instructions

#### Use

• AND operation to check if several instruction can be scheduled

◆□▶ ◆□▶ ◆□▶ ◆□▶ □ ○○○

OR operation to update the resource state

#### Advantages

- Intuitive representation

- Small storage

#### Drawbacks

- Many tests

- Redundant information

| Lecture Overview | Introduction | Constraints | List Scheduling | Conclusion |

|------------------|--------------|-------------|-----------------|------------|

|                  |              |             |                 |            |

| Automaton        |              |             |                 |            |

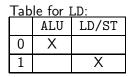

### Insight

• Pre-processing of possible resource usages

#### Semantics

- 1 state of the automaton  $\Leftrightarrow$  1 assignment of resources

- 1 transition of the automaton  $\Leftrightarrow$  scheduling of an instruction at the current cycle

### Transition label

- Label of a transition: the instruction to schedule

- Special label: NOP instruction to advance the current cycle

|   | ALUO | ALU1 | OR |   | ALUO | ALU1 |

|---|------|------|----|---|------|------|

| 0 | Х    |      | OK | 0 |      | Х    |

|   | ALUO | ALU1 |

|---|------|------|

| 0 |      | Х    |

◆□▶ ◆□▶ ◆ □▶ ◆ □▶ ○ □ ○ ○ ○ ○

| Aut | Automaton – Example 1             |      |      |    |   |      |      |  |   |      |      |   |

|-----|-----------------------------------|------|------|----|---|------|------|--|---|------|------|---|

| AI  | ADD instruction: MUL instruction: |      |      |    |   |      |      |  |   |      |      |   |

|     |                                   | ALUO | ALU1 | OR |   | ALUO | ALU1 |  |   | ALUO | ALU1 | Ì |

|     | 0                                 | Х    |      | UK | 0 |      | Х    |  | 0 |      | Х    |   |

Constraints

• 2 fully-pipelined resources  $\Rightarrow$  2 bits per state

?

▲ロト ▲御 ト ▲ 臣 ト ▲ 臣 ト ○ 臣 - の Q ()

• Are the following sequences valid?

ADD ? ADD ADD ; ADD ADD MUL ? ? ADD | MUL ; MUL ? MUL MUL

• Are the following sequences valid?

▲ロト ▲御 ト ▲ 臣 ト ▲ 臣 ト ○ 臣 - の Q ()

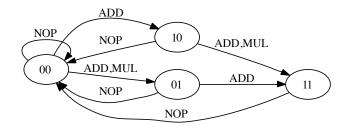

# Automaton – Example 2

# ADD instruction:

|   | ALU | LD/ST |

|---|-----|-------|

| 0 | Х   |       |

# SUB instruction:

|   | ALU | LD/ST |

|---|-----|-------|

| 0 | Х   |       |

| 1 | Х   |       |

### LD instruction:

|   | ALU | LD/ST |

|---|-----|-------|

| 0 | Х   |       |

| 1 |     | Х     |

◆□▶ ◆□▶ ◆ □▶ ◆ □▶ ○ □ ○ ○ ○ ○

#### ADD instruction:

|   | ALU | LD/ST |

|---|-----|-------|

| 0 | Х   |       |

| SUB instruction: |     |       |  |  |  |

|------------------|-----|-------|--|--|--|

|                  | ALU | LD/ST |  |  |  |

| 0                | Х   |       |  |  |  |

| 1                | Х   |       |  |  |  |

| <u>LD i</u> | LD instruction: |       |  |  |  |  |

|-------------|-----------------|-------|--|--|--|--|

|             | ALU             | LD/ST |  |  |  |  |

| 0           | Х               |       |  |  |  |  |

| 1           |                 | Х     |  |  |  |  |

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 のへぐ

• Are the following sequences valid?

| ADD   SUB | ? | LD ; SUB       | ? |

|-----------|---|----------------|---|

| ADD   ADD | ? | SUB ; LD       | ? |

| SUB   LD  | ? | ADD ; SUB ; LD | ? |

| LD ; ADD  | ? | LD ; ADD ; SUB | ? |

|           |   |                |   |

• Are the following sequences valid?

| ADD   SUB | ×            | LD ; SUB       | $\checkmark$ |

|-----------|--------------|----------------|--------------|

| ADD   ADD | ×            | SUB ; LD       | ×            |

| SUB   LD  | ×            | ADD ; SUB ; LD | ×            |

| LD ; ADD  | $\checkmark$ | LD ; ADD ; SUB |              |

#### Use

- An instruction can be currently scheduled if there is an output arc from the current state labeled with this instruction

- Update the state by following this arc

## Advantages

Low query time: table lookup

## Drawbacks

- Huge computational time (offline)

- Large storage

- $\Rightarrow$  split into several automata

- Not very flexible

- e.g. hard to schedule instructions not cycle-wise

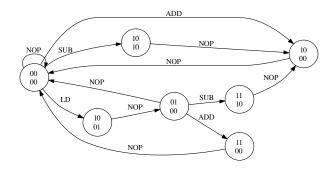

### Scheme of a classical scheduler

- High-level part: main heuristic taken care of the data dependences and driving the scheduling process

- Low-level part: storage of the resource usages and updates of the global assignments

◆□▶ ◆□▶ ◆□▶ ◆□▶ □ ○○○

# Scheme of a classical scheduler

- High-level part: main heuristic taken care of the data dependences and driving the scheduling process

- Low-level part: storage of the resource usages and updates of the global assignments

## Scheduling process

- Process begins in the high-level part

- Pick up the next instruction to insert in the partial schedule

- Query the low-level part for resource assignements:

- If okay, then goes on with another instruction

- Otherwise backtrack

# Acyclic Scheduling: List Scheduling

### Context

- Schedule a basic block  $\Rightarrow$  acyclic scheduling

- Goal: minimize the length of the generated code

- Must respect data dependences and resource constraints

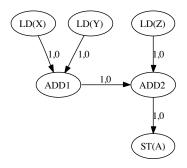

## Example

• Sum the first element of 3 vectors X, Y and Z in the first cell of array A:

$$A[O] = X[O] + Y[O] + Z[O];$$

- 3 instructions: ADD, LD, ST (1-cycle latency)

- 3 fully-pipelined resources: ALU, LDO and LD/ST1 units

◆□▶ ◆□▶ ◆三▶ ◆三▶ →三 ∽ ⊙へ⊙

# DDG?

Reservation tables:

▲ロト ▲御 ト ▲ 臣 ト ▲ 臣 ト ○ 臣 - の Q ()

# DDG:

# Acyclic Scheduling – Example

DDG:

# Reservation tables:

### ADD instruction:

|   | ALU | LDO | LD/ST1 |

|---|-----|-----|--------|

| 0 | Х   |     |        |

# LD instruction:

|   | ALU | LDO | LD/ST1 |

|---|-----|-----|--------|

| 0 |     | Х   |        |

|   | ALU | LDO | LD/ST1 |

|---|-----|-----|--------|

| 0 |     |     | Х      |

## ST instruction:

|   | ALU | LDO | LD/ST1 |

|---|-----|-----|--------|

| 0 |     |     | Х      |

◆□▶ ◆□▶ ◆□▶ ◆□▶ ▲□ ◆ ��

# Acyclic Scheduling – Example

Reservation tables:

ADD instruction:

|   | ALU | LDO | LD/ST1 |

|---|-----|-----|--------|

| 0 | Х   |     |        |

LD instruction:

|   | ALU | LDO | LD/ST1 |

|---|-----|-----|--------|

| 0 |     | Х   |        |

|   | ALU | LDO | LD/ST1 |

|---|-----|-----|--------|

| 0 |     |     | Х      |

ST instruction:

|   | ALU | LDO | LD/ST1 |

|---|-----|-----|--------|

| 0 |     |     | Х      |

▲ロト ▲御 ト ▲ 臣 ト ▲ 臣 ト ○ 臣 - の Q ()

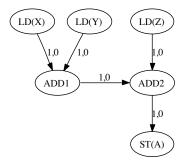

A possible schedule?

# DDG:

▲ロト ▲御 ト ▲ 臣 ト ▲ 臣 ト ○ 臣 - の Q ()

• A possible schedule respecting both constraints and minimizing the total length:

| LD(X)   LD(Y); | // Cycle 1                     |

|----------------|--------------------------------|

| ADD1   LD(Z) ; | // Cycle 2                     |

| ADD2 ;         | // Cycle 3                     |

| ST ;           | <pre>// Cycle 4 = length</pre> |

• A possible schedule respecting both constraints and minimizing the total length:

| LD(X)   LD(Y) ; | // Cycle 1                     |

|-----------------|--------------------------------|

| ADD1   LD(Z) ;  | // Cycle 2                     |

| ADD2 ;          | // Cycle 3                     |

| ST ;            | <pre>// Cycle 4 = length</pre> |

- Good the execute as much instructions as possible

- Pick up the good instruction is crucial (LD(X) and LD(Y) before LD(Z))

- Be careful of explicit resource assignments through reservation tables:

- Only one valid combination to execute a ST and a LD at the same cycle

### Principle

- List scheduling algorithm is based on this approach

- Sort the instruction according to priority based on data dependences

- Pick up one ready instruction in priority order

- Until every instruction has been scheduled

## Priority

- Many priority schemes exist

- We will use the *height-based priority*.

- Priority of a node is the longest path from that node to the furthest leaf

- The path is weighted by latencies

| Lecture Overview | Introduction | Constraints | List Scheduling | Conclusion |

|------------------|--------------|-------------|-----------------|------------|

|                  |              |             |                 |            |

|                  |              |             |                 |            |

| Conclusion       |              |             |                 |            |

# Instruction scheduling

• Generate a total order of a set of instructions

# Constraints

- Data dependences

- Represented as a graph: DDG

- Resource usages

- Represented as reservation tables or automaton

# Acyclic scheduling

- List scheduling

- Assign priority to instructions according to their contribution to the critical path