## **Practice Quiz 2**

Closed Book and Notes

- 1. The direction that current flows between the drain (D) and source (S) of N-channel and P-channel MOSFETS is as follows:

- (A) N-channel: D $\rightarrow$ S; P-channel: S $\rightarrow$ D

- (B) N-channel: S→D; P-channel: D→S

- (C) N-channel:  $D \rightarrow S$ ; P-channel:  $D \rightarrow S$

- (D) N-channel:  $S \rightarrow D$ ; P-channel:  $S \rightarrow D$

- (E) none of the above

- 2. For most CMOS logic families, the maximum acceptable V<sub>IL</sub> is:

- (A) 10% of the power supply voltage

- (B) 30% of the power supply voltage

- (C) 50% of the power supply voltage

- (D) 70% of the power supply voltage

- (E) 90% of the power supply voltage

- Ref. P. 17 of Lecture Summary notes

Ref. p. 12 of Lecture Summary motes

- 3. For most CMOS logic families, the **switching threshold** is:

- (A) 10% of the power supply voltage

- (B) 30% of the power supply voltage

- (C) 50% of the power supply voltage

- (D) 70% of the power supply voltage

- (E) 90% of the power supply voltage

- Ret: P.16 of Lecture Summery notes

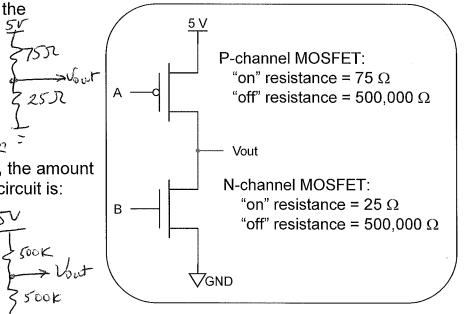

- P-on N-on

- 4. When **A = 0 V** and **B = 5 V**, the potential at **Vout** will be:

- (A) 0.00 V(B) 1.25 V Vout =

- (C) 2.50 V  $(\frac{25}{75+25}) \times 5 = \frac{1.25}{1.25}$

- (E) none of the above

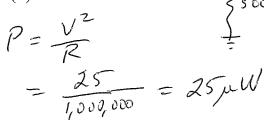

- N-OFF P-off 5. When A = 5 V and B = 0 V, the amount

- of power dissipated by this circuit is:

- (A)  $5 \mu W_{\perp}$

- (B) 25 µW

- (C) 50 mW (D) 250 mW

- (E) none of the above