# Lecture Summary – Module 4

Arithmetic and Computer Logic Circuits

#### Learning Outcome: an ability to analyze and design computer logic circuits

#### Learning Objectives:

- 4-1. <u>compare and contrast</u> three different signed number notations: sign and magnitude, diminished radix, and radix

- 4-2. <u>convert</u> a number from one signed notation to another

- 4-3. <u>describe</u> how to perform sign extension of a number represented using any of the three notation schemes

- 4-4. perform radix addition and subtraction

- 4-5. <u>describe</u> the various conditions of interest following an arithmetic operation: overflow, carry/borrow, negative, zero

- 4-6. describe the operation of a half-adder and write equations for its sum (S) and carry (C) outputs

- 4-7. describe the operation of a full adder and write equations for its sum (S) and carry (C) outputs

- 4-8. <u>design</u> a "population counting" or "vote counting" circuit using an array of half-adders and/or fulladders

- 4-9. design an N-digit radix adder/subtractor circuit with condition codes

- 4-10. design a (signed or unsigned) magnitude comparator circuit that determines if A=B, A<B, or A>B

- 4-11. <u>describe</u> the operation of a carry look-ahead (CLA) adder circuit, and <u>compare</u> its performance to that of a ripple adder circuit

- 4-12. <u>define</u> the CLA propagate (P) and generate (G) functions, and <u>show</u> how they can be realized using a half-adder

- 4-13. write the equation for the carry out function of an arbitrary CLA bit position

- 4-14. draw a diagram depicting the overall organization of a CLA

- 4-15. <u>determine</u> the worst case propagation delay incurred by a practical (PLD-based) realization of a CLA

- 4-16. describe how a "group ripple" adder can be constructed using N-bit CLA blocks

- 4-17. describe the operation of an unsigned multiplier array constructed using full adders

- 4-18. <u>determine</u> the full adder arrangement and organization (rows/diagonals) needed to construct an NxM-bit unsigned multiplier array

- 4-19. <u>determine</u> the worst case propagation delay incurred by a practical (PLD-based) realization of an NxM-bit unsigned multiplier array

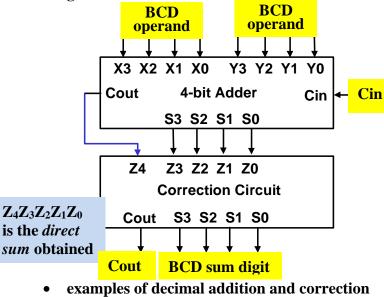

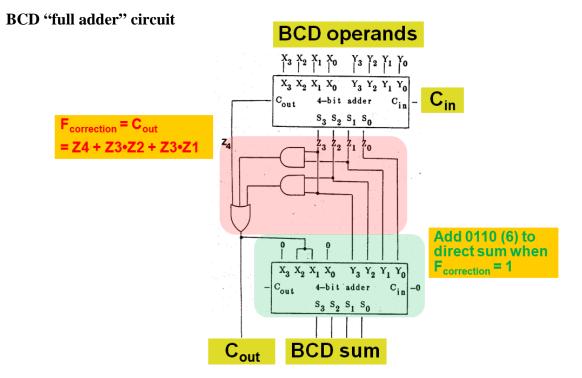

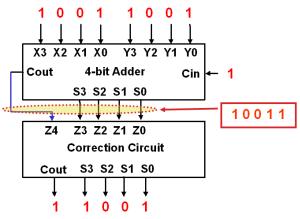

- 4-20. describe the operation of a binary coded decimal (BCD) "correction circuit"

- 4-21. <u>design</u> a BCD full adder circuit

- 4-22. design a BCD N-digit radix (base 10) adder/subtractor circuit

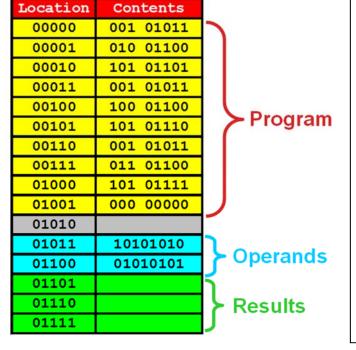

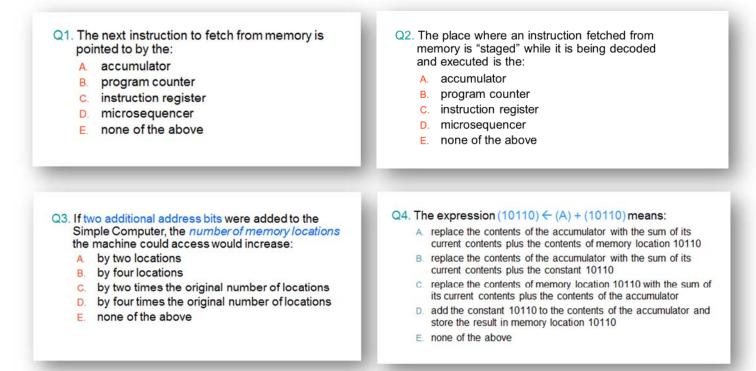

- 4-23. define computer architecture, programming model, and instruction set

- 4-24. <u>describe</u> the top-down specification, bottom-up implementation strategy as it pertains to the design of a computer

- 4-25. describe the characteristics of a "two address machine"

- 4-26. describe the contents of memory: program, operands, results of calculations

- 4-27. describe the format and fields of a basic machine instruction (opcode and address)

- 4-28. <u>describe</u> the purpose/function of each basic machine instruction (LDA, STA, ADD, SUB, AND, HLT)

- 4-29. <u>define</u> what is meant by "assembly-level" instruction mnemonics

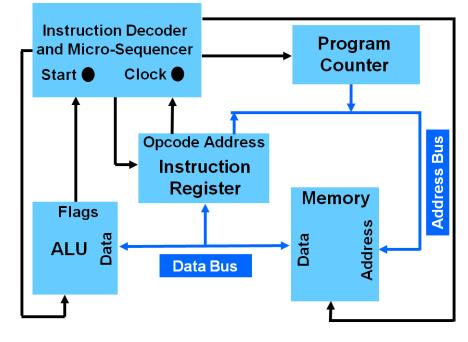

- 4-30. <u>draw</u> a diagram of a simple computer, showing the arrangement and interconnection of each functional block

- 4-31. <u>trace</u> the execution of a computer program, identifying each step of an instruction's microsequence (fetch and execute cycles)

- 4-32. distinguish between synchronous and combinational system control signals

- 4-33. describe the operation of memory and the function of its control signals: MSL, MOE, and MWE

- 4-34. <u>describe</u> the operation of the program counter (PC) and the function of its control signals: ARS, PCC, and POA

- 4-35. <u>describe</u> the operation of the instruction register (IR) and the function of its control signals: IRL and IRA

- 4-36. <u>describe</u> the operation of the ALU and the function of its control signals: ALE, ALX, ALY, and AOE

- 4-37. describe the operation of the instruction decoder/microsequencer and derive the system control table

- 4-38. <u>describe</u> the basic hardware-imposed system timing constraints: only one device can drive a bus during a given machine cycle, and data cannot pass through more than one flip-flop (register) per cycle

- 4-39. <u>discuss</u> how the instruction register can be loaded with the contents of the memory location pointed to be the program counter *and* the program counter can be incremented on the same clock edge

- 4-40. modify a reference ALU design to perform different functions (e.g., shift and rotate)

- 4-41. describe how input/output instructions can be added to the base machine architecture

- 4-42. describe the operation of the I/O block and the function of its control signals: IOR and IOW

- 4-43. <u>compare and contrast</u> the operation of OUT instructions with and without a transparent latch as an integral part of the I/O block

- 4-44. <u>compare and contrast</u> "jump" and "branch" transfer-of-control instructions along with the architectural features needed to support them

- 4-45. distinguish conditional and unconditional branches

- 4-46. describe the basis for which a conditional branch is "taken" or "not taken"

- 4-47. <u>describe</u> the changes needed to the instruction decoder/microsequencer in order to dynamically change the number of instruction execute cycles based on the opcode

- 4-48. <u>compare and contrast</u> the machine's asynchronous reset ("START") with the synchronous state counter reset ("RST")

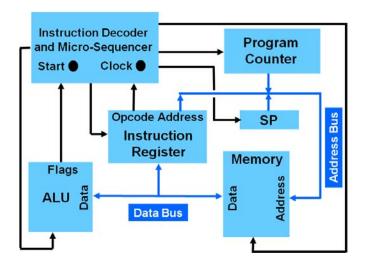

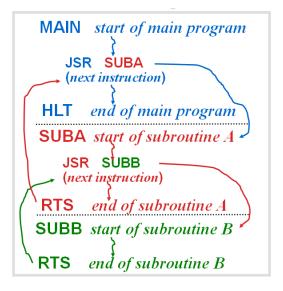

- 4-49. describe the operation of a stack mechanism (LIFO queue)

- 4-50. <u>describe</u> the operation of the stack pointer (SP) register and the function of its control signals: ARS, SPI, SPD, SPA

- 4-51. <u>compare and contrast</u> the two possible stack conventions: SP pointing to the top stack item vs. SP pointing to the top stack item

- 4-52. <u>describe</u> how stack manipulation instructions (PSH/POP) can be added to the base machine architecture

- 4-53. <u>discuss</u> the consequences of having an unbalanced set of PSH and POP instructions in a given program

- 4-54. <u>discuss</u> the reasons for using a stack as a subroutine linkage mechanism: arbitrary nesting of subroutine calls, passing parameters to subroutines, recursion, and reentrancy

- 4-55. <u>describe</u> how subroutine linkage instructions (JSR/RTS) can be added to the base machine architecture

- 4-56. <u>analyze</u> the effect of changing the stack convention utilized (SP points to top stack item vs. next available location) on instruction cycle counts

# Lecture Summary – Module 4-A

Signed Number Notation

Reference: Digital Design Principles and Practices (4th Ed.) pp. 39-43, (5th Ed.) pp. 44-48

- overview signed number notations

- sign and magnitude (SM)

- o diminished radix (DR)

- o radix (R)

- only negative numbers are different positive numbers are the same in all 3 notations

- sign and magnitude

- vacuum tube vintage

- left-most ("most significant") digit is sign bit

- $0 \rightarrow \text{positive}$

- $R-1 \rightarrow$  negative (where R is *radix* or *base* of number)

- o positive-negative pairs are called *sign and magnitude complements* of each other

- o negation method: replace sign digit (n<sub>s</sub>) with R-1-n<sub>s</sub>

- diminished radix

- o most significant digit is still sign bit

- o positive-negative pairs are called *diminished radix complements* of each other

- o negation method: subtract each digit (including  $n_s$ ) from R-1, i.e.  $-(N)_R = (R^n-1)_R (N)_R$

**Observations:**

**1.** SM and DR have a balanced set of positive and negative numbers

representation for zero, which

positive and negative numbers

can lead to round-off errors in

3. Virtually all computers in service

results in an "extra negative number" – this unbalanced set of

(as well as +0 and -0)

numeric computations

today use R notation

2. R notation has a single

- radix

- o most significant digit is still sign bit

- o positive-negative pairs are called *radix complements* of each other

- negation method: add one to the DR complement of  $(N)_R$ , i.e.  $-(N)_R = (R^n)_R (N)_R$

- comparison (3-bit signed numbers, each notation):

| <b>N</b> <sub>10</sub> | SM  | DR  | R   |

|------------------------|-----|-----|-----|

| +3                     | 011 | 011 | 011 |

| +2                     | 010 | 010 | 010 |

| +1                     | 001 | 001 | 001 |

| +0                     | 000 | 000 | 000 |

| -0                     | 100 | 111 |     |

| -1                     | 101 | 110 | 111 |

| -2                     | 110 | 101 | 110 |

| -3                     | 111 | 100 | 101 |

| _4                     |     |     | 100 |

All positive number representations are identical

Radix has no "negative zero"

All negative number representations are *different* Radix has an extra negative number

#### • simplifications for binary (base 2)

- SM: complement sign position  $(0 \leftrightarrow 1)$

- DR (also called 1's complement): complement each bit

- R (also called 2's complement):

- add 1 to DR complement -or-

- scan number from right to left and complement each bit to the left of the first "1" encountered

- sign extension: SM pad magnitude with leading zeroes; R and DR replicate the sign digit

1. The five-bit radix number, R(10101)<sub>2</sub>, converted to sign and magnitude notation, is:

- A. SM (10101)2

- B. SM (01010)<sub>2</sub>

- C. SM (11010)<sub>2</sub>

- D. SM (11011)<sub>2</sub>

- E. none of the above

# 2. The five-bit diminished radix number, DR(10101)<sub>2</sub>, converted to sign and magnitude notation, is:

- A. SM (10101)2

- B. SM (01010)2

- C. SM (11010)<sub>2</sub>

- D. SM (11011)<sub>2</sub>

- E. none of the above

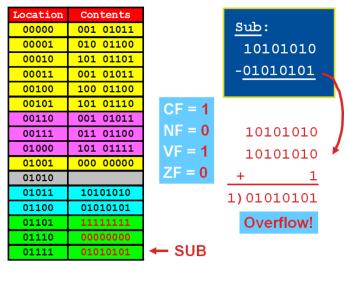

# Lecture Summary – Module 4-B

Radix Addition and Subtraction

Reference: Digital Design Principles and Practices (4th Ed.) pp. 39-43, (5th Ed.) pp. 48-52

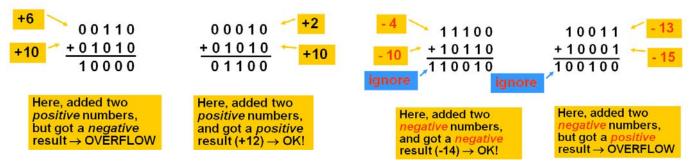

- radix addition

- o method: add all digits, including the sign digits; ignore any carry out of the sign position

- o note that overflow can occur, since we are working with numbers of *fixed length*

- overflow occurs if two numbers of *like sign* are added and a result with the *opposite sign* is obtained

- overflow cannot occur when adding numbers of opposite sign

- another way to detect overflow: if the carry *in* to the sign position is *different* than the carry *out* of the sign position, then overflow has occurred

- when overflow occurs, there is *no valid numeric result*

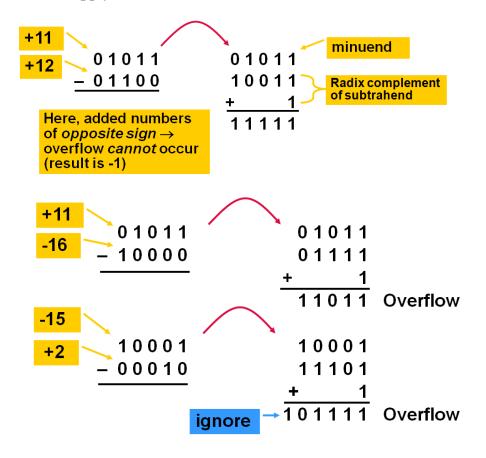

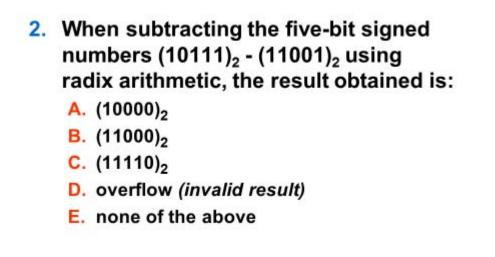

#### • radix subtraction

• method: form the radix complement of the subtrahend and ADD (the same rules for overflow detection apply)

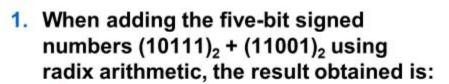

- A. (10000)<sub>2</sub>

- B. (110000)<sub>2</sub>

- C. (11000)<sub>2</sub>

- D. overflow (invalid result)

- E. none of the above

# Lecture Summary – Module 4-C

Adder, Subtractor, and Comparator Circuits

**Reference:** *DDPP* (4<sup>th</sup> Ed.) pp. 458-466, 474-478; (5<sup>th</sup> Ed.) pp. 331-339, 341-345, 372-375

- overview

- an adder circuit combines two operands based on rules described in 5-C

- same addition rules apply for both signed (2's complement) and unsigned numbers

- o subtraction performed by taking complement of subtrahend and performing add

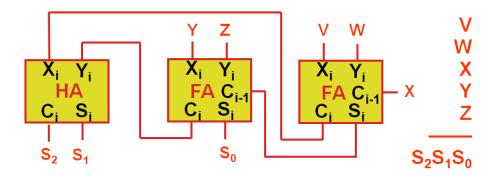

- building blocks

- half adder

| Xi | Yi | Ci | Si |

|----|----|----|----|

| 0  | 0  |    |    |

| 0  | 1  |    |    |

| 1  | 0  |    |    |

| 1  | 1  |    |    |

o full adder

| Xi | Yi | Ci-1 | Ci | Si |

|----|----|------|----|----|

| 0  | 0  | 0    |    |    |

| 0  | 0  | 1    |    |    |

| 0  | 1  | 0    |    |    |

| 0  | 1  | 1    |    |    |

| 1  | 0  | 0    |    |    |

| 1  | 0  | 1    |    |    |

| 1  | 1  | 0    |    |    |

| 1  | 1  | 1    |    |    |

• "vote counting" application

The Digi-Vota-Matic is a three-judge score tabulation system that allows each judge to enter a score ranging from "0" ( $00_2$ ) to "3" ( $11_2$ ) on a pair of DIP switches, and displays the sum of the three scores (ranging from "0" to "9") on a 7-segment LED.

- 1. Implemented using a CASE statement in Verilog, a circuit that finds the sum of three 2-bit unsigned numbers would require \_\_\_\_\_assignments.

- A. 16

- **B.** 32

- C. 64

- D. 128

- E. none of the above

- Implemented using a 22V10 PLD, a circuit that finds the sum of three 2-bit unsigned numbers would require no more than \_\_\_\_ macrocells.

- A. 2

- **B.** 4

- C. 8

- D. 16

- E. none of the above

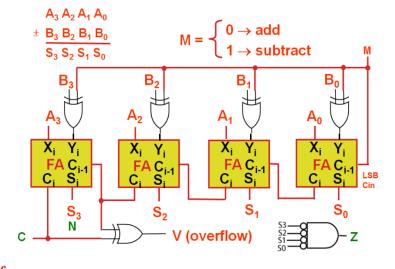

- multi-digit adder/subtractor

- ripple = iterative

- to subtract, take DR radix complement of subtrahend and add 1

- conditions of interest ("condition codes")

- overflow (V)

- negative (N)

- zero (Z)

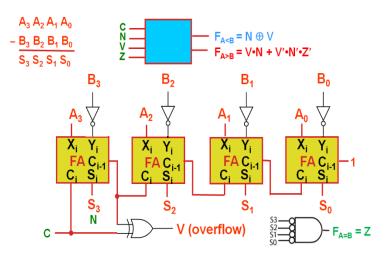

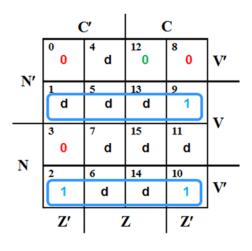

magnitude comparator

•

carry/borrow (C)

- calculate A–B and condition codes

results (A=B, A<B, A>B) are *functions of*

- the condition codes

| A1 | A0 | B1 | <b>B0</b> | ?                                                         | С | Ζ | Ν | V |

|----|----|----|-----------|-----------------------------------------------------------|---|---|---|---|

| 0  | 0  | 0  | 0         | A=B                                                       | 1 | 1 | 0 | 0 |

| 0  | 0  | 0  | 1         | A <b< td=""><td>0</td><td>0</td><td>1</td><td>0</td></b<> | 0 | 0 | 1 | 0 |

| 0  | 0  | 1  | 0         | A>B                                                       | 0 | 0 | 1 | 1 |

| 0  | 0  | 1  | 1         | A>B                                                       | 0 | 0 | 0 | 0 |

| 0  | 1  | 0  | 0         | A>B                                                       | 1 | 0 | 0 | 0 |

| 0  | 1  | 0  | 1         | A=B                                                       | 1 | 1 | 0 | 0 |

| 0  | 1  | 1  | 0         | A>B                                                       | 0 | 0 | 1 | 1 |

| 0  | 1  | 1  | 1         | A>B                                                       | 0 | 0 | 1 | 1 |

| 1  | 0  | 0  | 0         | A <b< td=""><td>1</td><td>0</td><td>1</td><td>0</td></b<> | 1 | 0 | 1 | 0 |

| 1  | 0  | 0  | 1         | A <b< td=""><td>1</td><td>0</td><td>0</td><td>1</td></b<> | 1 | 0 | 0 | 1 |

| 1  | 0  | 1  | 0         | A=B                                                       | 1 | 1 | 0 | 0 |

| 1  | 0  | 1  | 1         | A <b< td=""><td>0</td><td>0</td><td>1</td><td>0</td></b<> | 0 | 0 | 1 | 0 |

| 1  | 1  | 0  | 0         | A <b< td=""><td>1</td><td>0</td><td>1</td><td>0</td></b<> | 1 | 0 | 1 | 0 |

| 1  | 1  | 0  | 1         | A <b< td=""><td>1</td><td>0</td><td>1</td><td>0</td></b<> | 1 | 0 | 1 | 0 |

| 1  | 1  | 1  | 0         | A>B                                                       | 1 | 0 | 0 | 0 |

| 1  | 1  | 1  | 1         | A=B                                                       | 1 | 1 | 0 | 0 |

$F_{A < B} = N \oplus V$

F<sub>A>B</sub> = V•N + V'•N'•Z'

- When performing radix addition, the XOR of the carry in to the sign position with the carry out of the sign position provides a means to:

- A. generate a carry that is propagated forward

- B. generate a borrow that is propagated forward

- C. check for a negative result

- D. check for an invalid result

- E. none of the above

- 2. Following a subtract operation, the carry flag (C) can be used to:

- A. generate the *complement of a borrow* that is propagated forward

- B. generate a *borrow* that is propagated forward

- C. check for a negative result

- D. check for an invalid result

- E. none of the above

- Following an add operation, the negative flag (N) can be used to:

- A. generate a carry that is propagated forward

- B. generate a borrow that is propagated forward

- C. check for a negative result

- D. check for an invalid result

- E. none of the above

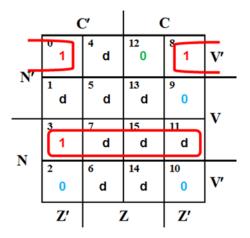

Generate from stage 1

Propagated by

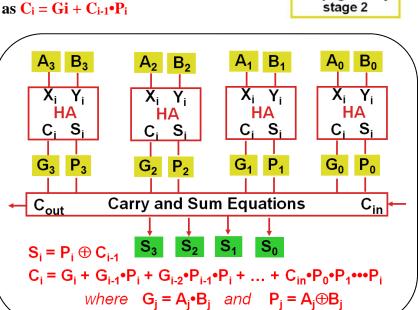

# Lecture Summary – Module 4-D

Carry Look-Ahead (CLA) Adder Circuits

Reference: DDPP (4th Ed.) pp. 478-482, 484-488; (5th Ed.) pp. 376-383, 384-386

- introduction

- o previously considered iterative ("ripple") adder circuit

- problem: propagation delay increases with number of bits

- o solution: determine carries in parallel rather than iteratively  $\rightarrow$  significant speedup

- $\circ$  "look-ahead"  $\rightarrow$  "anticipated"

- definitions and derivations

- generate function (carry *guaranteed*)  $G_i = X_i \cdot Y_i$

- propagate function (carry *in* propagated *out*)  $P_i = X_i \oplus Y_i$

- note that a "PG box" is just a half-adder (HA)

- can rewrite sum bit equation as  $S_i = P_i \oplus C_{i-1}$  (C-1 is  $C_{in}$ )

- can rewrite carry out equation as  $C_i = Gi + C_{i-1} \cdot P_i$

- rewriting carry equations for 4-bit adder in terms of P's and G's

$$\circ \quad \mathbf{C}_{-1} = \mathbf{C}_{\mathrm{in}}$$

- $\circ \quad \mathbf{C}_0 = \mathbf{G}_0 + \mathbf{C}_{\mathrm{in}} \bullet \mathbf{P}_0$

- $\circ \quad \mathbf{C}_1 = \mathbf{G}_1 + \mathbf{C}_0 \bullet \mathbf{P}_1$

- $\circ \quad \mathbf{C}_2 = \mathbf{G}_2 + \mathbf{C}_1 \bullet \mathbf{P}_2$

- $C_3 = C_{out} = G_3 + C_2 \cdot P_3$

- rewriting carry equations for 4bit adder in terms of *available inputs* (successive expansion)

- $\circ \quad \mathbf{C}_{-1} = \mathbf{C}_{in}$

- $\circ \quad \mathbf{C}_0 = \mathbf{G}_0 + \mathbf{C}_{\mathrm{in}} \bullet \mathbf{P}_0$

- $\circ \quad C_1 = G_1 + C_0 \bullet P_1 = G_1 + (G_0 + C_{in} \bullet P_0) \bullet P_1 = G_1 + G_0 \bullet P_1 + C_{in} \bullet P_0 \bullet P_1$

- know what these equations are "saying"

- C<sub>2</sub> = \_\_\_\_\_

- C<sub>3</sub> = \_\_\_\_\_

- observations

- regardless of adder length (number of operand bits), the time required to produce any sum digit is the same (i.e. they are all produced *in parallel*)

- large CLA adders are difficult to build in practice because of "product term explosion"

- reasonable compromise is to make a group ripple adder (cascading m-bit CLA blocks together to get desired operand length)

x 1 1 x

x 0 1 x

#### ECE 270 IM:PACT

• 4-bit CLA realized in Verilog

```

module cla4(X, Y, CIN, S);

input wire [3:0] X, Y; // Operands

input wire CIN; // Carry in

output wire [3:0] S; // Sum outputs

// Carry equations (C[3] is Cout)

wire [3:0] C;

wire [3:0] P, G;

wire [3:0] C;

assign G = X & Y; // Generate functions G[0] = X[0]&Y[0];

G[1] = \dots \text{ so on}

assign P = X ^ Y; // Propagate functions P[0] = X[0]^Y[0];

P[1] = .. so on

// Carry function definitions

assign C[0] = G[0] | CIN \& P[0];

assign C[1] = G[1] | G[0] & P[1] | CIN & P[0] & P[1];

assign C[2] = G[2] | G[1] & P[2] | G[0] & P[1] & P[2]

CIN & P[0] & P[1] & P[2];

assign C[3] = G[3] | G[2] & P[3] | G[1] & P[2] & P[3]

G[0] & P[1] & P[2] & P[3]

CIN & P[0] & P[1] & P[2] & P[3];

assign S[0] = CIN ^ P[0];

assign S[3:1] = C[2:0] ^ P[3:1];

endmodule

```

• alternate version using "+" (addition) operator

```

module cla4p(X, Y, CIN, S);

input wire [3:0] X, Y; // Operands

input wire CIN; // Carry in

output wire [3:0] S; // Sum outputs

assign S = X + Y + \{3'b000, CIN\};

endmodule

```

• identical timing analysis for both versions  $\rightarrow$  "+" operator synthesizes CLA equations

| Timing | Analysis for | ispMACH 4256ZE | 5.8 ns CPLD |

|--------|--------------|----------------|-------------|

| Delay  | - Level      | Source         | Destination |

| =====  | =====        | =====          | =========   |

| 6.40   | 1            | CIN            | <b>S</b> 3  |

| 6.40   | 1            | X0             | <b>S</b> 3  |

| 6.40   | 1            | Y0             | <b>S</b> 3  |

| 6.35   | 1            | Xl             | <b>S</b> 3  |

| 6.35   | 1            | Yl             | S3          |

| 6.30   | 1            | X2             | <b>S</b> 3  |

| 6.30   | 1            | ¥2             | <b>S</b> 3  |

| 6.25   | 1            | Y3             | <b>S</b> 3  |

|        |              |                |             |

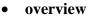

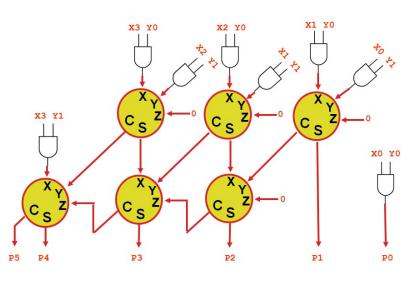

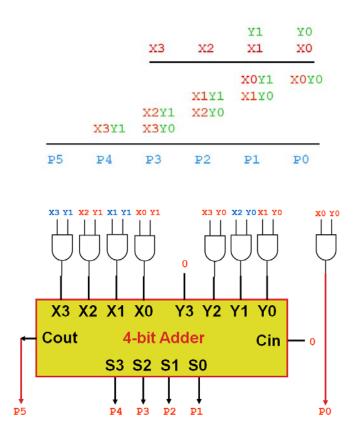

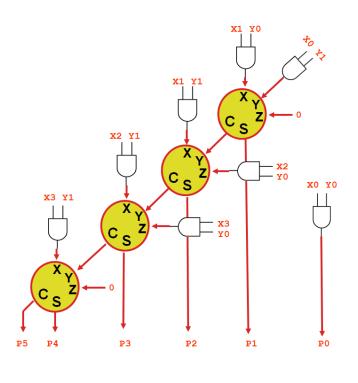

### Lecture Summary – Module 4-E Multiplier Circuits

**Reference:** *DDPP* (4<sup>th</sup> Ed.) pp. 45-47, 494-497; (5<sup>th</sup> Ed.) pp. 54-56, 416-419

• consider 3x3 unsigned binary multiplication:

- o based on "shift and add" algorithm

- each row is called a *product component*

- each x<sub>i</sub>•y<sub>i</sub> term represents a *product component bit* (logical AND)

- the *product* **P** is obtained by adding together the product components

- generalizations for an NxM multiplier array circuit

- N = number of bits in multiplicand

- **M** = number of bits in multiplier

- produces an N+M digit result

- requires NxM AND gates to generate the product components

- o requires N-1 "diagonals" of full adders

- o requires **M** rows of full adders

- exercise: 4x2 multiplier array circuit

|    |      | Х3   | X2   | X1<br>Y1 | x0<br>X0 |

|----|------|------|------|----------|----------|

|    |      | X3Y0 | X2Y0 | X1Y0     | X0X0     |

| ~  | X3¥1 | X2Y1 | X1Y1 | X0Y1     |          |

| P5 | P4   | P3   | P2   | Pl       | PO       |

13

- generalizations for an NxM multiplier

- N = number of bits in multiplicand (top)

- **M** = number of bits in multiplier (bottom)

- produces an N+M digit result

- requires NxM AND gates to generate the product components

- requires N–1 *diagonals* of full adders

- requires M rows of full adders

- 1. A 6x4 unsigned binary multiplier array would require <u>rows</u> of full adder cells

- A. 3

- **B.** 4

- C. 5

- D. 6

- E. none of the above

- 2. A 6x4 unsigned binary multiplier array would require <u>"diagonals</u>" of full adder cells

- A. 3

- **B**. 4

- C. 5

- D. 6

- E. none of the above

| <ul> <li>3. A 6x4 unsigned binary multiplier array would requirefull adder cells</li> <li>A. 10</li> <li>B. 18</li> <li>C. 20</li> <li>D. 24</li> <li>E. none of the above</li> </ul>                                                                                                                                    | <ul> <li>4. A 6x4 unsigned binary multiplier array would require AND gates to generate the product component bits</li> <li>A. 10</li> <li>B. 18</li> <li>C. 20</li> <li>D. 24</li> <li>E. none of the above</li> </ul>                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>5. Assuming a large 10 ns PLD was used to generate each product component bit and implement each full adder cell, the worst case propagation delay of a 6x4 unsigned binary multiplier array would be ns</li> <li>A. 80</li> <li>B. 90</li> <li>C. 100</li> <li>D. 110</li> <li>E. none of the above</li> </ul> | <ul> <li>6. A 4x6 unsigned binary multiplier array would requirerows of full adder cells</li> <li>A. 3</li> <li>B. 4</li> <li>C. 5</li> <li>D. 6</li> <li>E. none of the above</li> </ul>                                                                                                                                |

| <ul> <li>7. A 4x6 unsigned binary multiplier array would require "diagonals" of full adder cells</li> <li>A. 3</li> <li>B. 4</li> <li>C. 5</li> <li>D. 6</li> <li>E. none of the above</li> </ul>                                                                                                                        | <ul> <li>8. A 4x6 unsigned binary multiplier array would requirefull adder cells</li> <li>A. 10</li> <li>B. 18</li> <li>C. 20</li> <li>D. 24</li> <li>E. none of the above</li> </ul>                                                                                                                                    |

| <ul> <li>9. A 4x6 unsigned binary multiplier array would requireAND gates to generate the product component bits</li> <li>A. 10</li> <li>B. 18</li> <li>C. 20</li> <li>D. 24</li> <li>E. none of the above</li> </ul>                                                                                                    | <ul> <li>10. Assuming a large 10 ns PLD was used to generate each product component bit and implement each full adder cell, the worst case propagation delay of a 4x6 unsigned binary multiplier array would bens</li> <li>A. 80</li> <li>B. 90</li> <li>C. 100</li> <li>D. 110</li> <li>E. none of the above</li> </ul> |

#### realizations in Verilog ٠

- use *expressions* to define product components

- use *addition operator* (+) to form unsigned sum of product components

- example: 4x4 multiplier array circuit

```

/* 4x4 Combinational Multiplier */

module mul4x4(X, Y, P);

input wire [3:0] X, Y; // Multiplicand, multiplier

output wire [7:0] P; // Product bits

wire [7:0] PC[3:0];

// Four 8-bit variables

// 0000<mark>X3</mark>X2X1X0

assign PC[0] = \{8\{Y[0]\}\} \& \{4'b0, X\};

assign PC[1] = {8{Y[1]}} & {3'b0, X, 1'b0}; // 000X3X2X1X00

assign PC[2] = {8{Y[2]}} & {2'b0, X, 2'b0}; // 00X3X2X1X000

assign PC[3] = \{8\{Y[3]\}\} \& \{1'b0, X, 3'b0\}; // 0X3X2X1X0000

assign P = PC[0] + PC[1] + PC[2] + PC[3];

endmodule

```

{8{Y[0]}} will extend the 1-bit signal Y[0] to an 8-bit vector

| Timiı | ng Ana | lysis for | ispMACH    | 4256ZE 5.8 ns CPLD |  |

|-------|--------|-----------|------------|--------------------|--|

| De    | lay    | Level     | Source     | Destination        |  |

| ===   | ===    | =====     | ======     | ==========         |  |

| 6     | .50    | 1         | <b>X</b> 0 | P4                 |  |

| 6     | .50    | 1         | <b>X</b> 0 | P5                 |  |

| 6     | .50    | 1         | X1         | P4                 |  |

| 6     | .50    | 1         | X1         | P5                 |  |

| 6     | .50    | 1         | X2         | P4                 |  |

| 6     | .50    | 1         | X2         | P5                 |  |

| 6     | .50    | 1         | Y0         | P4                 |  |

| 6     | .50    | 1         | Y0         | P5                 |  |

| 6     | .50    | 1         | Y1         | P4                 |  |

| 6     | .50    | 1         | Y1         | P5                 |  |

| 6     | .50    | 1         | Y2         | P4                 |  |

| 6     | .50    | 1         | Y2         | P5                 |  |

| 6     | .45    | 1         | X3         | P4                 |  |

| 6     | .45    | 1         | X3         | P5                 |  |

| 6     | .45    | 1         | ¥3         | P4                 |  |

| 6     | .45    | 1         | ¥3         | P5                 |  |

| 6     | .05    | 1         | <b>X</b> 0 | P0                 |  |

| 6     | .05    | 1         | <b>X</b> 0 | P1                 |  |

| 6     | .05    | 1         | <b>X</b> 0 | P2                 |  |

| 6     | .05    | 1         | <b>X</b> 0 | P3                 |  |

|       |        |           |            |                    |  |

|       |        |           |            |                    |  |

### Lecture Summary – Module 4-F BCD Adder Circuits

Reference: Digital Design Principles and Practices (4th Ed.) pp. 48-51; (5th Ed.) pp. 58-60

- overview

- o external computer interfaces may need to read or display decimal digits (examples)

- o need to perform arithmetic operations on decimal numbers directly

- most commonly used code in *binary-coded decimal* (BCD)

- object is to design circuit that adds two BCD digit codes plus carry in, to produce a sum digit plus a carry out

- want to use standard 4-bit binary adder modules as "building blocks"

- note that there are six "unused combinations" in BCD, so potential exists for needed to perform a "correction"

- summary of rules

- o if the sum of two BCD digits is ≤ 9 (i.e. 1001), no correction is needed

- if the sum of two BCD digits is > 9, the result must be corrected by adding six (0110)

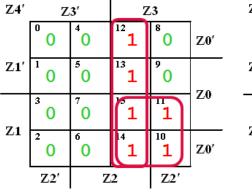

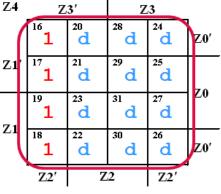

- "correction function" derivation

| <b>N</b> <sub>10</sub> | $Z_4 Z_3 Z_2 Z_1 Z_0$ | $C_{out}$ S <sub>3</sub> S <sub>2</sub> S <sub>1</sub> S <sub>0</sub> | Correction       |

|------------------------|-----------------------|-----------------------------------------------------------------------|------------------|

| 0                      | 00000                 | 0 0 0 0 0                                                             | <none></none>    |

| 1                      | 00001                 | 0 0 0 0 1                                                             | <none></none>    |

| 2                      | 00010                 | 0 0 0 1 0                                                             | <none></none>    |

| 3                      | 00011                 | 0 0 0 1 1                                                             | <none></none>    |

| 4                      | 00100                 | 0 0 1 0 0                                                             | <none></none>    |

| 5                      | 00101                 | 0 0 1 0 1                                                             | <none></none>    |

| 6                      | 00110                 | 0 0 1 1 0                                                             | <none></none>    |

| 7                      | 00111                 | 0 0 1 1 1                                                             | <none></none>    |

| 8                      | 01000                 | 0 1 0 0 0                                                             | <none></none>    |

| 9                      | 01001                 | 0 1 0 0 1                                                             | <none></none>    |

| 10                     | 01010                 | 1 0 0 0 0                                                             | ⊲add 6>          |

| 11                     | 01011                 | 1 0 0 0 1                                                             | <add 6=""></add> |

| 12                     | 01100                 | 1 0 0 1 0                                                             | ⊲add 6>          |

| 13                     | 01101                 | 1 0 0 1 1                                                             | <add 6=""></add> |

| 14                     | 01110                 | 1 0 1 0 0                                                             | <add 6=""></add> |

| 15                     | 01111                 | 1 0 1 0 1                                                             | <add 6=""></add> |

| 16                     | 10000                 | 1 0 1 1 0                                                             | <add 6=""></add> |

| 17                     | 10001                 | 1 0 1 1 1                                                             | ⊲add 6>          |

| 18                     | 10010                 | 1 1 0 0 0                                                             | <add 6=""></add> |

| 19                     | 10011                 | 1 1 0 0 1                                                             | <add 6=""></add> |

$$F_{\text{correction}} = C_{\text{out}} =$$

$$Z4 + Z3 \cdot Z2 + Z3 \cdot Z1$$

•

• example: maximum value that can be generated by a BCD full adder cell (9+9+Cin)

• example: circuit that produces the diminished radix complement of a BCD digit

module ninescmp(X, Y); input wire [3:0] X; // Input code // Output code output reg [3:0] Y; always @ (X) begin case (X) 4'b0000: Y = 4'b1001;Y = 4'b1000;4'b0001: Y = 4'b0111;4'b0010: Y = 4'b0110;4'b0011: 4'b0100: Y = 4'b0101;4'b0101: Y = 4'b0100;4'b0110: Y = 4'b0011;4'b0111: Y = 4'b0010;4'b1000: Y = 4'b0001;4'b1001: Y = 4'b0000;default: Y = 4'b0000; // used for inputs > 9 endcase end endmodule

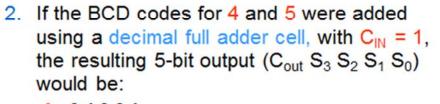

- 1. If the BCD codes for 8 and 5 were added using a decimal full adder cell, with  $C_{IN} = 1$ , the resulting 5-bit output ( $C_{out} S_3 S_2 S_1 S_0$ ) would be:

- A. 01101 B. 01110 C. 10011 D.10100

- E. none of the above

- A. 01001

- B. 01010

- C. 10000

- D.10001

- E. none of the above

# Lecture Summary – Module 4-G

Simple Computer – Top-Down Specification

Reference: Meyer Supplemental Text, pp. 1-18

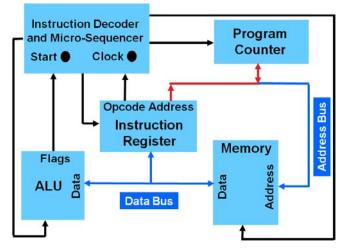

- overview

- o the "ultimate application" of what we have learned

- computer defn sequential execution of stored program

- o architecture defn arrangement and interconnection of functional blocks

- house analogy

- big picture

- o input/output

- o start (reset)

- o clock

- floor plan

- o programming model

- instruction set

- o registers

- o instruction format

- opcode

- address

- two-address machine

- programming example

- memory snapshot

| Opcode | Mnemonic    | Function Performed                                  |

|--------|-------------|-----------------------------------------------------|

| 000    | HLT         | Halt – stop, discontinue execution                  |

| 001    | LDA addr    | Load A with contents of location addr               |

| 010    | ADD addr    | Add contents of <i>addr</i> to contents of A        |

| 011    | SUB addr    | Subtract contents of <i>addr</i> from contents of A |

| 100    | AND addr    | AND contents of <i>addr</i> with contents of A      |

| 101    | STA addr    | Store contents of A at location addr                |

| Aslala | Instruction | O - man - m to                                      |

| Addr   | Instruction | Comments                                            |

| 00000  | LDA 01011   | Load A with contents of location 01011              |

| 00001  | ADD 01100   | Add contents of location 01100 to A                 |

| 00010  | STA 01101   | Store contents of A at location 01101               |

| 00011  | LDA 01011   | Load A with contents of location 01011              |

| 00100  | AND 01100   | AND contents of 01100 with contents of A            |

| 00101  | STA 01110   | Store contents of A at location 01110               |

| 00110  | LDA 01011   | Load A with contents of location 01011              |

| 00111  | SUB 01100   | Subtract contents of location 01100 from A          |

| 01000  | STA 01111   | Store contents of A at location 01111               |

| 01001  | HLT         | Stop – discontinue execution                        |

## Calculation of ADD, AND, and SUB results:

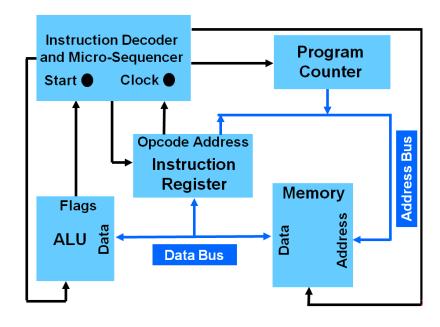

- block diagram

- o memory

- program counter

- o instruction register

- arithmetic logic unit

- instruction decoder and micro-sequencer

#### • notes

- each functional block is "self-contained" (can be *independently tested*)

- o can add more instructions by increasing number of opcode bits

- o can add more memory by increasing the number of address bits

- o can increase numeric range by increasing the number of data bits

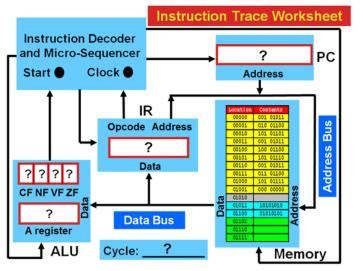

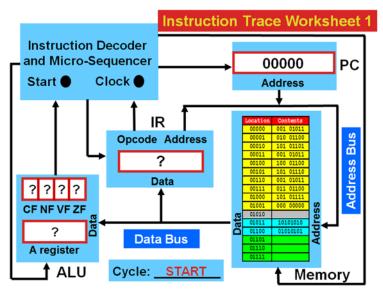

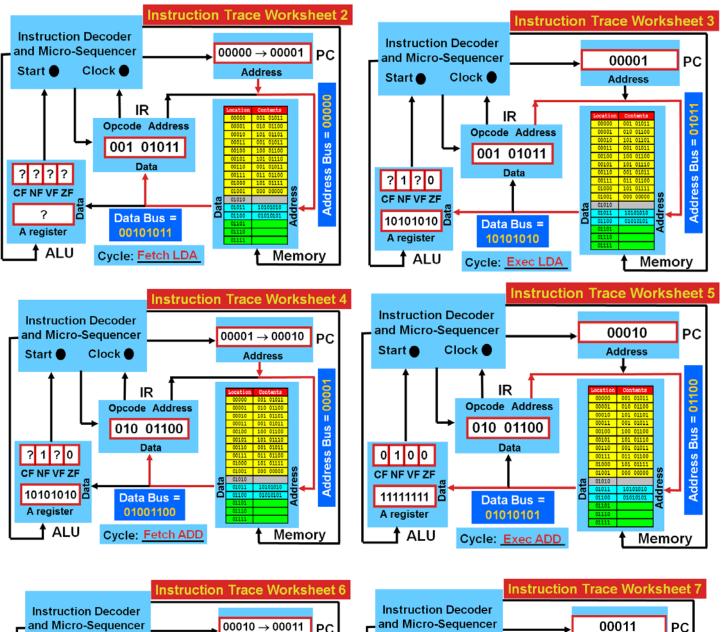

# Lecture Summary – Module 4-H

Simple Computer – Instruction Tracing

Reference: Meyer Supplemental Text, pp. 18-24

- overview

- two basic steps in "processing" an instruction

- fetch

- execute

- $\circ$  will trace the processing of several instructions to better understand this

- program segment to trace

| Addr  | Instruction | Comments                               |

|-------|-------------|----------------------------------------|

| 00000 | LDA 01011   | Load A with contents of location 01011 |

| 00001 | ADD 01100   | Add contents of location 01100 to A    |

| 00010 | STA 01101   | Store contents of A at location 01101  |

• worksheet

#### Notes:

- 1. The clock edges drive the <u>synchronous</u> functions of the computer (e.g., increment program counter)

- 2. The decoded states (here, fetch and execute) enable the <u>combinational</u> functions of the computer (e.g., turn on tri-state buffers)

• step 1 (after START pushbutton pressed)

Start 🔴

0 1 0 0

CF NF VF ZF

A register

11111111 🗳

1 ALU

= 0110

Bus

Address

# Lecture Summary – Module 4-I

Simple Computer – Bottom-Up Implementation

Reference: Meyer Supplemental Text, pp. 24-42

- overview

- o finished top-down specification of design

- ready for bottom-up implementation

- all system control signals *active high*

- some control signals *mutually exclusive*

- all blocks use the *same clock signal*

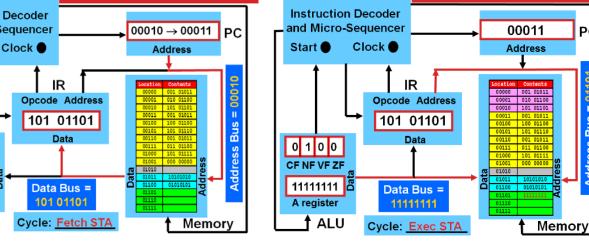

- memory

- key definitions/terms

- read/write

- "random access" (wrt prop delay)

- static (does not need "refresh")

- volatile (loses data when "off")

- size NxM (here 32x8)

- 3 control signals

- MSL memory select

- MOE memory output enable

- MWE memory write enable

- notes

- read operation is combinational

- write operation involves open/closing latch  $\rightarrow$  setup and hold timing matters

Q1. When a set of control signals are said to be mutually exclusive, it means that:

- A. all the control signals may be asserted simultaneously

- only one control signal may be asserted at a given instant

- C. each control signal is dependent on the others

- any combination of control signals may be asserted at a given instant

- E. none of the above

Q2. For the memory subsystem, the set of signals that are mutually exclusive is:

- A. MSL and MOE

- B. MSL and MWE

- C. MOE and MWE

- D. MSL, MOE, and MWE

- E. none of the above

- program counter

- o basically a binary "up" counter with tri-state outputs and an asynchronous reset

- o 3 control signals

- ARS asynchronous reset

- PCC program counter count enable

- POA program counter output on address bus tri-state buffer enable

```

/* Program Counter Module */

module pc(CLK, PCC, POA, RST, ADRBUS_z);

input wire CLK;

// PC count enable

input wire PCC;

input wire POA; // PC output on address bus tri-state enable

input wire RST; // asynchronous reset (connected to START)

output wire [4:0] ADRBUS z;

wire [4:0] next PC;

reg [4:0] PC;

assign ADRBUS z = POA ? PC : 5'bZZZZZ;

always @ (posedge CLK, posedge RST) begin

if (RST == 1'b1)

PC <= 5'b00000;

else

PC <= next PC;

end

11

(PCC) ? count up : retain value;

assign next PC = (PCC) ? (PC+1) : PC;

endmodule

```

- instruction register

- o basically an 8-bit data register, with tri-state outputs on the lower 5 (address) bits

- o upper 3 bits (opcode) output directly to instruction decoder and micro-sequencer

- two control signals

- IRL instruction register load enable

- IRA instruction register address field tri-state output enable

```

/* Instruction Register Module */

module ir (CLK, IR z, DB z, IRL, IRA);

input wire CLK;

input wire IRL; // IR load enable

input wire IRA; // IR output on address bus enable

input wire [7:0] DB_z; // data bus

output wire [7:0] IR_z; // IR_z[4]..IR_z[0] connected to address bus

// IR z[7]..IR z[5] supply opcode to IDMS

reg [7:0] IR;

wire [7:0] next IR;

assign IR z[4:0] = IRA ? IR[4:0] : 5'bZZZZZ;

assign IR z[7:5] = IR[7:5];

always @ (posedge CLK) begin

IR <= next IR;</pre>

end

11

(IRL) ? load : retain state (select load or retain state based on IRL)

assign next_IR = (IRL) ? DB_z : IR;

endmodule

```

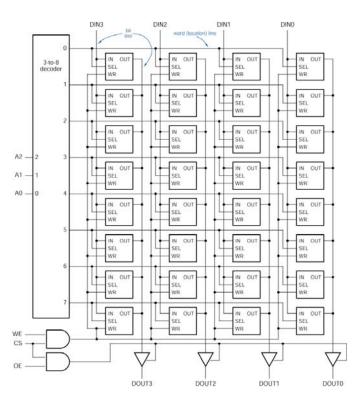

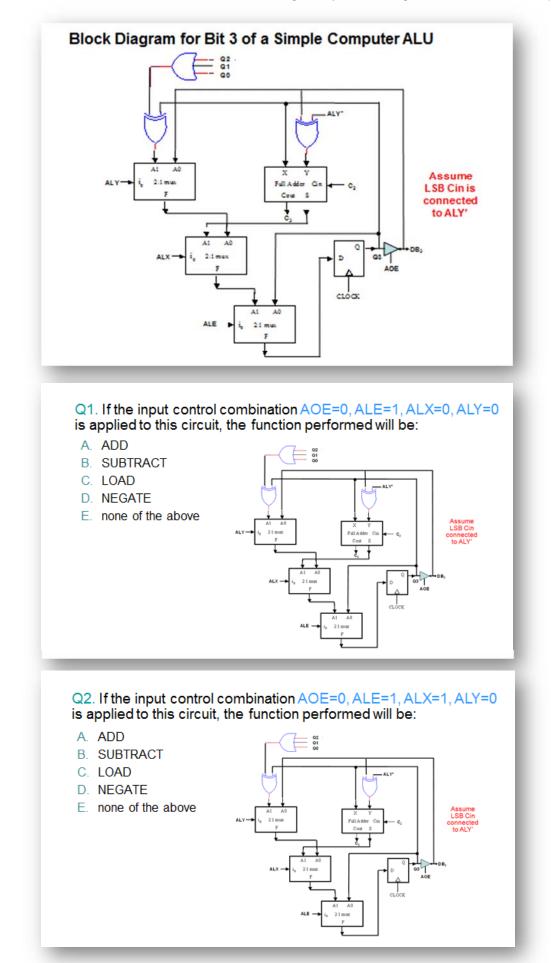

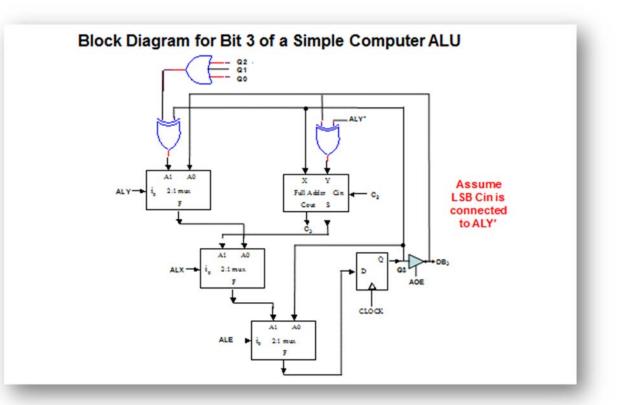

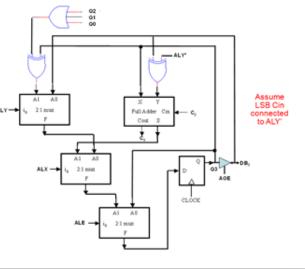

#### • ALU

- o a multi-function register that performs arithmetic and logical operations

- four control signals

- ALE overall ALU enable

- ALX function select

- ALY function select

- AOE A register tri-state output enable

```

/* ALU Module */

module alu(CLK, ALE, AOE, ALX, ALY, DB z, CF, VF, NF, ZF);

/* 8-bit, 4-function ALU with bi-directional data bus

Accumulator register is AQ, tri-state data bus is DB z

ADD:

(AQ[7:0]) <- (AQ[7:0]) + DB_z[7:0]

SUB:

(AQ[7:0]) <- (AQ[7:0]) - DB_z[7:0]

(AQ[7:0]) <- DB_z[7:0]

LDA:

AND:

(AQ[7:0]) <- (AQ[7:0]) \& DB_z[7:0]

OUT: Value in AQ[7:0] output on data bus DB z[7:0]

AOE ALE

ALX ALY

Function

CF

ZF NF

VF

___

___

____

___

_____

_

==

==

_

1

0

0

ADD

0

х

х

х

х

0

0

SUB

х

1

1

x

х

x

0

1

1

0

LDA

•

х х

•

0

1 1 1

AND

х х

1

0

d

d

OUT

•

•

0

0

d

d

<none>

.

.

X -> flag affected • -> flag not affected

Note: If ALE = 0, the state of all register bits should be retained */

```

o block diagram of one bit

input wire CLK;

endmodule

```

input wire ALE; // overall ALU enable

input wire AOE; // data bus tri-state output enable

input wire ALX, ALY; // function select

inout wire [7:0] DB z;

// bidirectional 8-bit tri-state data bus

output reg CF, VF, NF, ZF; // condition code register bits (flags)

// Carry, Overflow, Negative, Zero

// Carry equations

wire [7:0] CY;

// Combinational ALU outputs

wire [7:0] ALU;

wire [7:0] S;

wire [7:0] L;

// Adder/subtractor sum

// LDA/AND multiplexer output

reg [7:0] AQ;

// A register flip-flops

// Next state variables

reg next_CF, next_VF, next_NF, next_ZF;

reg [7:0] next_AQ;

// Declaration of intermediate equations

// Least significant bit carry in (0 for ADD, 1 for SUB => ALY)

assign CIN = ALY;

// Intermediate equations for adder/subtractor SUM (S) selected when ALX = 0

assign S = AQ ^ (DB_z ^ ALY) ^ {CY[6:0],CIN};

// Ripple carry equations (CY[7] is COUT, DB_z is data from data bus)

assign CY = AQ & (ALY ^{DB}z) | AQ & {CY[6:0],CIN} | ALY & DB_z & {CY[6:0],CIN};

// Intermediate equations for LOAD and AND, selected when ALX = 1

// (ALY)? AND : LDA (select LDA or AND based on ALY)

assign L = ALY ? AQ & DB_z : DB_z ;

// Combinational ALU outputs

11

(ALX)? L : S (select LDA/AND or ADD/SUB based on ALX)

assign ALU = ALX ? L : S;

// Register bit and data bus control equations

always @ (posedge CLK) begin

AQ \ll next AQ;

end

always @ (AQ, ALE, ALU) begin

next AQ = ALE ? ALU : AQ;

end

AOE ALE ALX ALY

Function CF ZF NF

VF

assign DB_z = AOE ? AQ : 8'bZZZZZZZ;

--- --- ---

____

____

==

=

0

1

0

0

ADD

хх

x

х

// Condition code register state equations

1

0 1

SUB

хххх

0

• x x •

always @ (posedge CLK) begin

0

1 1 0

LDA

1

1 1

d d

0

AND

• x x

•

CF <= next CF;

1

0

OUT

.

ZF <= next_ZF;</pre>

.

•

•

d d <none>

0

0

•

NF <= next NF;

VF <= next VF;

X -> flag affected • -> flag not affected

end

always @ (CF, NF, ZF, VF, ALE, ALX, ALY, CY) begin

: CF;

next_{CF} = ALE ? (ALX ? CF : (CY[7])

next_{ZF} = ALE ? (ALU = 0)

: ZF;

next NF = ALE ? ALU[7]

: NF;

next VF = ALE ? (ALX ? VF : (CY[7] ^ CY[6])) : VF;

end

```

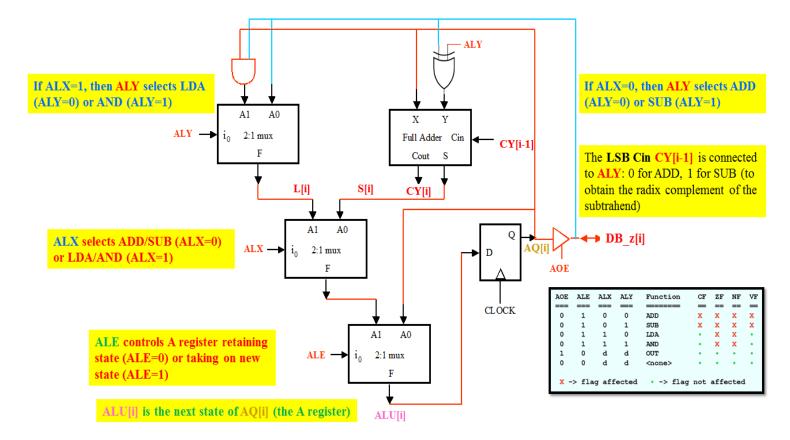

- instruction decoder and microsequencer

- o state machine that tells all the other state machines what to do ("orchestra director")

- micro-sequence consists of two steps (states)

- fetching instruction from memory

- executing instruction

- fetch/execute state represented by single flip-flop (SQ)

- **fetch cycle**

- POA (output location of instruction on address bus)

- MSL (select memory, i.e., enable memory to participate)

- MOE (turn on memory tri-state buffers, so that selected location can be read)

- IRL (enable IR to load instruction fetched from memory)

- PCC (enable PC to increment)

- execute cycle ALU functions (ADD, SUB, LDA, AND)

- IRA (output operand location on address bus)

- MSL (select memory)

- MOE (enable memory to be read)

- ALE (enable ALU to perform the selected function)

- execute cycle STA instruction

- IRA (output location at which to store result)

- MSL (select memory)

- MWE (enable write to memory)

- AOE (output data in A register via data bus to memory)

- o to stop execution ("halt"), need a "run/stop" flip-flop

- when START pressed, asynchronously set RUN flip-flip

- when HLT instruction executed, asynchronously clear RUN flip-flop

- AND the RUN signal with each synchronous enable signal → effectively disables all functional blocks

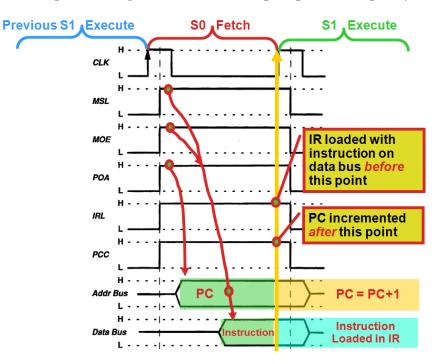

The synchronous fetch functions (IRL and PCC) will take place on the clock edge that causes the state counter to transition from the fetch state to the execute state

RUN <= 1'b0;

$\mathbf{end}$

|                                                                | Decoded                                                              | Instruction                                                                                                                            |                                                                              | ш                        | ш                                |                              |                          |                      |       |                             |        |                           |        |

|----------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------|----------------------------------|------------------------------|--------------------------|----------------------|-------|-----------------------------|--------|---------------------------|--------|

|                                                                | State                                                                | Mnemonic                                                                                                                               | MSL                                                                          | MOE                      | MWE                              | D<br>C<br>C                  | POA                      | R                    | RA    | AOE                         | ALE    | ALX                       | ALY    |

|                                                                | <b>S</b> 0                                                           | -                                                                                                                                      | н                                                                            | н                        |                                  | н                            | н                        | н                    |       |                             |        |                           |        |

|                                                                | <b>S1</b>                                                            | HLT (000)                                                                                                                              | L                                                                            |                          |                                  | L                            |                          | L                    |       |                             | L      |                           |        |

|                                                                | <mark>\$1</mark>                                                     | LDA (001)                                                                                                                              | н                                                                            | н                        |                                  |                              |                          |                      | н     |                             | н      | н                         |        |

|                                                                | <u>\$1</u>                                                           | ADD (010)                                                                                                                              | н                                                                            | н                        |                                  |                              |                          |                      | н     |                             | н      |                           |        |

|                                                                | <u>\$1</u>                                                           | SUB (011)                                                                                                                              | н                                                                            | н                        |                                  |                              |                          |                      | н     |                             | н      |                           | н      |

|                                                                | <u>\$1</u>                                                           | AND (100)                                                                                                                              | н                                                                            | н                        |                                  |                              |                          |                      | н     |                             | н      | н                         | н      |

|                                                                | 51<br>51                                                             | STA (101)                                                                                                                              | н                                                                            |                          | н                                |                              |                          |                      | н     | н                           |        |                           |        |

|                                                                |                                                                      |                                                                                                                                        |                                                                              |                          |                                  |                              |                          |                      |       |                             |        |                           |        |

|                                                                |                                                                      | and Microseq<br>OP, MSL, MO                                                                                                            |                                                                              |                          |                                  | , PO                         | A, A                     | RS,                  | IRL   | , IR                        | A, A   | LE,                       | ALX,   |

|                                                                |                                                                      |                                                                                                                                        |                                                                              |                          |                                  |                              |                          |                      |       |                             |        |                           |        |

| nput wire (                                                    |                                                                      |                                                                                                                                        | 1                                                                            | 1 20                     | unab                             | none                         |                          | יסריתי               |       | chhu                        | ++     |                           |        |

| put wire                                                       | [2:0] OP;                                                            |                                                                                                                                        | 1                                                                            | / op                     | code                             | bit                          | s (i                     | npu                  | t fr  | om I                        | R5.    | -<br>IR7)                 | )      |

| tput wire                                                      | MSL, MOE,                                                            | MWE ;                                                                                                                                  | 11                                                                           | / Me                     | mory                             | con                          | trol                     | l sig                | gnal  | s                           |        |                           |        |

|                                                                |                                                                      | ARS;                                                                                                                                   |                                                                              |                          |                                  |                              |                          |                      |       |                             |        |                           |        |

| tput wire                                                      | IRL, IRA;                                                            | ATY AOF.                                                                                                                               | <pre>// IR control signals AOE; // ALU control signals (without flags)</pre> |                          |                                  |                              |                          |                      |       |                             |        |                           |        |

| itput wire                                                     | ALE, ALA,                                                            | ALI, AOE;                                                                                                                              | //                                                                           | AL                       | 0 00                             | ntro                         | 1 51                     | .gna.                | LS (  | with                        | out    | TIA                       | js)    |

| g SQ, nex                                                      | t sg;                                                                |                                                                                                                                        | 11                                                                           | / St                     | ate                              | coun                         | ter                      |                      |       |                             |        |                           |        |

| RUN, nez                                                       | xt_RUN;                                                              |                                                                                                                                        | 11                                                                           | RU                       | N/HL                             | T st                         | ate                      |                      |       |                             |        |                           |        |

| ire LDA, Stire [1:0] :                                         | S;                                                                   | UB, AND, HLT                                                                                                                           | 11                                                                           | / St                     | ate                              | nam<br>vari<br>ronc          | able                     |                      | t fo  | r RU                        | N      |                           |        |

|                                                                |                                                                      |                                                                                                                                        |                                                                              |                          |                                  |                              |                          |                      |       |                             |        |                           |        |

| ssign LDA = ~<br>ssign ADD = ~<br>ssign SUB = ~<br>ssign AND = | OP[2] & ~OP<br>OP[2] & OP<br>OP[2] & OP<br>OP[2] & OP<br>OP[2] & ~OP | <pre>[1] &amp; ~OP[0];<br/>[1] &amp; OP[0];<br/>[1] &amp; ~OP[0];<br/>[1] &amp; OP[0];<br/>[1] &amp; OP[0];<br/>[1] &amp; OP[0];</pre> | <br>  <br>                                                                   | LDA<br>ADD<br>SUB<br>AND | opcod<br>opcod<br>opcod<br>opcod | le =<br>le =<br>le =<br>le = | 001<br>010<br>011<br>100 |                      |       |                             |        |                           |        |

| Decoded state                                                  | definition                                                           | S                                                                                                                                      |                                                                              |                          | Ор                               | code                         | Mne                      | monio                | : Fu  | nctior                      | n Perf | ormed                     | 1      |

| assign S[0] =                                                  |                                                                      | / fetch                                                                                                                                |                                                                              |                          |                                  | 00                           | HLT                      | addr                 |       | lt – sto<br>ad A w          |        |                           |        |

| assign S[1] =                                                  | sg; //                                                               | / execute                                                                                                                              |                                                                              |                          |                                  |                              | ADD                      |                      |       | d cont                      |        |                           |        |

| if(START ==                                                    | dge CLK, po:<br>1'b1) //                                             | sedge START) be<br>/ start in fetc                                                                                                     | -                                                                            | ate                      | 1                                | 1 1<br>0 0<br>0 1            | AND                      | addr<br>addr<br>addr | AN    | btract<br>ID con<br>ore coi | tents  | of add                    | r with |

| SQ <= 1'b0<br>else                                             |                                                                      | / if RUN negate                                                                                                                        | ed, r                                                                        | eset                     | s SO                             |                              |                          |                      |       |                             |        |                           |        |

| SQ <= next                                                     |                                                                      | 2                                                                                                                                      |                                                                              |                          | Ĩ                                |                              |                          |                      |       |                             |        |                           |        |

| end                                                            |                                                                      |                                                                                                                                        |                                                                              |                          |                                  |                              |                          |                      |       |                             |        |                           |        |

| ays @ (SQ,<br>wext_SQ = RU<br>L                                | · ·                                                                  |                                                                                                                                        |                                                                              |                          |                                  |                              |                          |                      |       |                             |        |                           |        |

| / Run/stop                                                     |                                                                      |                                                                                                                                        |                                                                              |                          |                                  |                              |                          |                      |       |                             |        |                           |        |

| if(START ==<br>RUN <= 1'b                                      | dge CLK, po:<br>1'b1)<br>1;                                          | sedge RUN_ar, p<br>// RUN                                                                                                              | set 1                                                                        | to 1                     | when                             | STAF                         | T as                     |                      |       |                             | by a   | flip-f<br>n alv<br>in its | väys   |

| else if(RUN_<br>RUN <= 1'b                                     |                                                                      | // RUN                                                                                                                                 | is cl                                                                        | Leare                    | d who                            | en HI                        | T is                     | exec                 | cuted |                             | unle   | ss ot                     | heru   |

AOE

н

н

н

ALE

н н

н

н

н н

ALX

Ρ

н

н

```

// System control equations

assign MSL = RUN & (S[0] | S[1] & (LDA | STA | ADD | SUB | AND));

assign MOE = S[0] | S[1] \& (LDA | ADD | SUB | AND);

assign MWE = S[1] \& STA;

assign ARS = START;

assign PCC = RUN \& S[0];

assign POA = S[0];

assign IRL = RUN & S[0];

assign IRA = S[1] & (LDA | STA | ADD | SUB | AND);

assign AOE = S[1] \& STA;

assign ALE = RUN & S[1] & (LDA | ADD | SUB | AND);

assign ALX = S[1] & (LDA | AND);

Decoded

Instruction

BOR

POA

assign ALY = S[1] & (SUB | AND);

₹

<u> A</u>SI

PCC

ΠĀ

State

Mnemonic

R

SO

н

н

н

н

н

_

endmodule

S1

HLT (000)

S1

LDA

(001)

н

н

н

ADD

(010)

н

н

н

S1

SUB

(011)

н

S1

н

н

```

**S1**

**S1**

AND

(100)

STA (101)

н н

н

н

- system data flow analysis procedure

- o understand operation of functional units

- o understand what each instruction does

- o identify address & data source/destination

- o identify micro-operations required

- o identify control signals that need to be asserted

- examine timing relationship

- system data flow analysis constraints

- o only one device can drive the bus during a machine cycle

- data cannot pass through more than one flip-flop or latch per cycle

# Q1. The increment of the program counter (PC) needs to occur as part of the "fetch" cycle because:

- A. if it occurred on the "execute" cycle, the new value might not be stable in time for the subsequent "fetch" cycle

- B. if it occurred on the "execute" cycle, it would not be possible to execute an "STA" instruction

- C. if it occurred on the "execute" cycle, it would not be possible to read an operand from memory

- D. if it occurred on the "execute" cycle, it would not be possible to read an instruction from memory

- E. none of the above

Q2. The program counter (PC) can be incremented on the same cycle that its value is used to fetch an instruction from memory because:

- A. the synchronous actions associated with the IRL and PCC control signals occur on different fetch cycle phases

- B. the IRL and PCC control signals are not asserted simultaneously by the IDMS

- C. the load of the instruction register is based on the data bus value prior to the system CLOCK edge, while the increment of the PC occurs after the CLOCK edge

- D. the load of the instruction register occurs on the negative CLOCK edge, while the increment of the PC occurs on the positive CLOCK edge

- E. none of the above

# Q3. Incrementing the program counter (PC) on the same clock edge that loads the instruction register (IR) does not cause a problem because:

- A. the memory will ignore the new address the PC places on the address bus

- B. the output buffers in the PC will not allow the new PC value to affect the address bus until the next fetch cycle

- C. the IR will be loaded with the value on the data bus prior to the clock edge while the contents of the PC will increment after the clock edge

- D. the value in the PC will change in time for the correct value to be output on the address bus (and fetch the correct instruction), before the IR load occurs

- E. none of the above

#### Q4. The hardware constraint that "data cannot pass through more than one edge-triggered flip-flop per clock cycle" is based on the fact that:

- A. only a single entity can drive a bus on a given clock cycle

- B. the system clock has limited driving capability

- C. the flip-flops that comprise a register do not change state simultaneously, so additional time must be provided before the register's output can be used

- D. for a D flip-flop with clocking period  $\Delta$ , Q(t+ $\Delta$ )=D(t)

- E. none of the above

### Lecture Summary – Module 4-J

Simple Computer – Basic Extensions

Reference: Meyer Supplemental Text, pp. 42-50

- overview

- o will use "spare" opcodes (110 and 111) to add new instructions

- o will add rows and columns to original system control table as needed

- shift instructions (extension to ALU)

- translation of bits to the left or right

- o end off: discard bit shifted out

- preserving: retain bit shifted out

- logical: zero fill (zero shifted in)

- arithmetic: sign preserving

| Decoded<br>State | Instruction<br>Mnemonic | MSL | MOE | MWE | PCC | POA | IRL | IRA | AOE | ALE | ALX | ALY |  |

|------------------|-------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|--|

| <b>SO</b>        | -                       | н   | Н   |     | н   | н   | Н   |     |     |     |     |     |  |

| <b>S1</b>        | HLT (000)               | L   |     |     | L   |     | L   |     |     | L   |     |     |  |

| <b>S1</b>        | LDA (001)               | н   | н   |     |     |     |     | н   |     | н   |     |     |  |

| <b>S1</b>        | LSR (010)               |     |     |     |     |     |     |     |     | н   |     | н   |  |

| <b>S1</b>        | ASL (011)               |     |     |     |     |     |     |     |     | н   | н   |     |  |

| <b>S1</b>        | ASR (100)               |     |     |     |     |     |     |     |     | Н   | Н   | Н   |  |

| <b>S1</b>        | STA (101)               | н   |     | Н   |     |     |     | Н   | Н   |     |     |     |  |

| <b>S1</b>        |                         |     |     |     |     |     |     |     |     |     |     |     |  |

| <b>S1</b>        |                         |     |     |     |     |     |     |     |     |     |     |     |  |

```

/* ALU Module Version 2 */

module alu(CLK, ALE, AOE, ALX, ALY, DB, CF, VF, NF, ZF);

/* 8-bit, 4-function ALU with bi-directional data bus

LDA: (AQ[7:0]) < -DB z[7:0]

LSR: (AQ[7:0]) <- 0 AQ7 AQ6 AQ5 AQ4 AQ3 AQ2 AQ1, CF <- AQ0

ASL: (AQ[7:0]) <- AQ6 AQ5 AQ4 AQ3 AQ2 AQ1 AQ0 0 , CF <- AQ7

ASR: (AQ[7:0]) <- AQ7 AQ7 AQ6 AQ5 AQ4 AQ3 AQ2 AQ1, CF <- AQ0

OUT: Value in AQ[7:0] output on data bus DB_z[7:0]

AOE ALE ALX ALY Function

CF ZF NF

VF

____ ___ ___

____

_____

-

0

LDA

0

1

0

• x x

0 1 0 1 LSR

ххх

ххх

0 1 1 0 ASL

0 1 1 1 ASR

ххх

0 d d OUT

1

•

٠

•

0 0 d d <none>

X -> flag affected • -> flag not affected

Note: If ALE = 0, the state of all register bits should be retained */

```

```

input wire CLK;

// ALU control lines

// ALU CONCLUTION INCLUTION

input wire ALE; // Overall ALU enable

input wire AOE; // Data bus tri-state output enable

input wire ALX, ALY; // Function select

inout wire [7:0] DB_z; // Bidirectional 8-bit data bus

output reg CF, VF, NF, ZF; // Condition code bits (flags)

// Carry, Overflow, Negative, Zero

// Combinational ALU outputs

wire [7:0] ALU;

// Accumulator (A) register

reg [7:0] AQ;

// Next state variables

reg next_CF, next_VF, next_NF, next_ZF;

reg [7:0] next_AQ;

// Combinational ALU outputs

always @ (ALX, ALY, DB_z) begin

case ({ALX,ALY})

2'b00: ALU = DB_z; // LDA

2'b01: ALU = {1'b0,AQ[7:1]}; // LSR

2'b10: ALU = {AQ[6:0],1'b0}; // ASL

2'b11: ALU = {AQ[7],AQ[7:1]}; // ASR

idcase

2'b00: ALU = DB_z;

endcase

end

// Register bit and data bus control equations

always @(posedge CLK) begin

AQ <= next_AQ;

end

always @ (ALE, ALU, AQ) begin

next_AQ = ALE ? ALU : AQ;

end

assign DB z = AOE ? AQ : 8'bZZZZZZZ;

// Flag register state equations

always @ (posedge CLK) begin

CF <= next_CF;

ZF <= next ZF;

NF <= next NF;

VF <= next_VF;</pre>

end

always @ (ALE, ALX, ALY, CF, ZF, NF, VF, ALU, AQ) begin

casez ({ALE,ALX,ALY})

3'b0??: next_CF = 1'b0;

3'b100: next_CF = CF; // LDA (not affected)

3'b101: next_CF = AQ[0]; // LSR

3'b110: next_CF = AQ[7]; // ASL

3'b111: next_CF = AQ[0]; // ASR

endcase

next_ZF = ALE ? (ALU == 0) : ZF;

next_NF = ALE ? ALU[7] : NF;

// NOTE: NOT AFFECTED

next VF = VF;

end

endmodule

```

Q1. If the input control combination AOE=1, ALE=1, ALX=1, ALY=1 is applied to this circuit, the function (inadvertently) performed on (A) will be equivalent to:

- A. logical left shift

- B. logical right shift

- c. rotate left

- D. rotate right

- E. none of the above

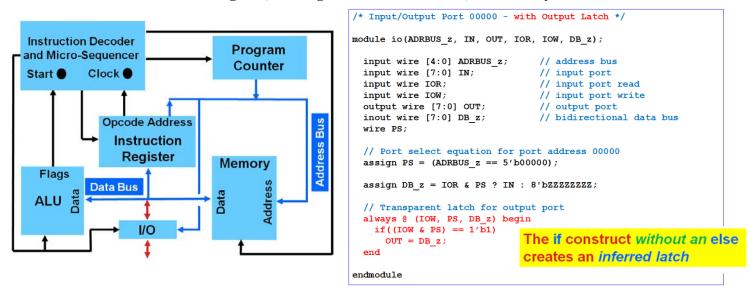

#### • input/output (I/O) instructions

- o new instructions

- IN addr input data from port addr and load into A register

- OUT *addr* output data in A register to port *addr*

- new control signals

- IOR asserted when IN executed

- IOW asserted when OUT executed

- o modified block diagram, Verilog code for I/O module, modified system control table

| Decoded<br>State | Instruction<br>Mnemonic | MSL | MOE | MWE | PCC | POA | IRL | IRA | AOE | ALE | ALX | ALY | IOR | MOI |

|------------------|-------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| <b>SO</b>        |                         | н   | н   |     | Н   | н   | н   |     |     |     |     |     |     |     |

| S1               | HLT (000)               | L.  |     |     | L   |     | L   |     |     | L   |     |     |     |     |

| <b>S1</b>        | LDA (001)               | н   | н   |     |     |     |     | Н   |     | Н   | Н   |     |     |     |

| <b>S1</b>        | ADD (010)               | н   | н   |     |     |     |     | н   |     | н   |     |     |     |     |

| <b>S1</b>        | SUB (011)               | н   | н   |     |     |     |     | н   |     | н   |     | Н   |     |     |

| <b>S1</b>        | AND (100)               | н   | Н   |     |     |     |     | Н   |     | Н   | Н   | Н   |     |     |

| <b>S1</b>        | STA (101)               | н   |     | н   |     |     |     | Н   | Н   |     |     |     |     |     |

| <b>S1</b>        | IN (110)                |     |     |     |     |     |     | Н   |     | Н   | Н   |     | н   |     |

| <b>S1</b>        | OUT (111)               |     |     |     |     |     |     | н   | н   |     |     |     |     | н   |

```

// System control equations

assign MSL = RUN & (S[0] | S[1] & (LDA | STA | ADD | SUB | AND));

assign MOE = S[0] | S[1] & (LDA | ADD | SUB | AND);

assign MWE = S[1] & STA;

assign ARS = START;

assign PCC = RUN & S[0];

assign POA = S[0];

assign IRL = RUN & S[0];

assign IRA = S[1] & (LDA | STA | ADD | SUB | AND | IN | OUT);

assign AOE = S[1] & (STA | OUT);

assign ALE = RUN & S[1] & (LDA | ADD | SUB | AND | IN);

assign ALX = S[1] & (LDA | AND);

assign ALY = S[1] & (SUB | AND);

assign IOR = S[1] & IN;