Reading Assignment:

DDPP 4<sup>th</sup> Ed. pp. 196-210, 5<sup>th</sup> Ed, pp. 100-117

Learning Objectives:

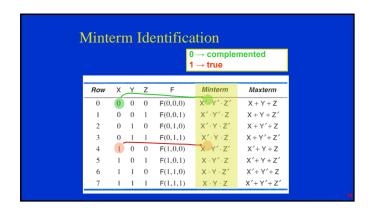

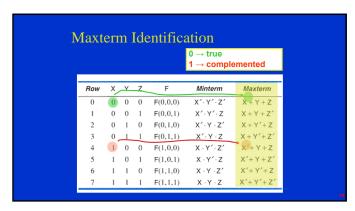

Identify minterms (product terms) and maxterms (sum terms)

List the standard forms for expressing a logic function and give an example of each: sum-of-products (SoP), product-of-sums (PoS), ON set, OFF set

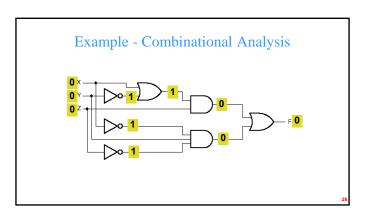

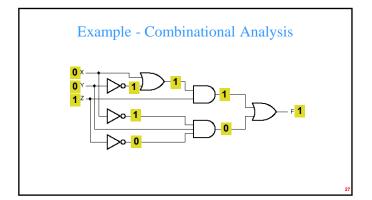

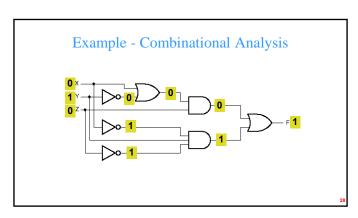

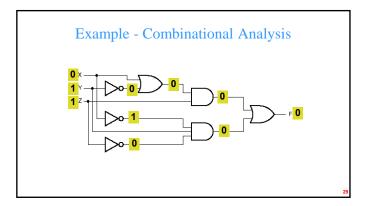

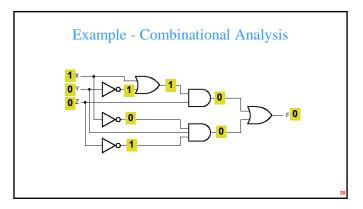

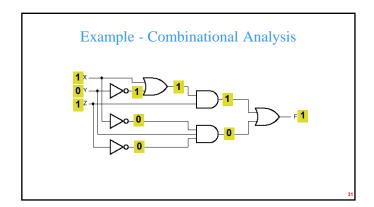

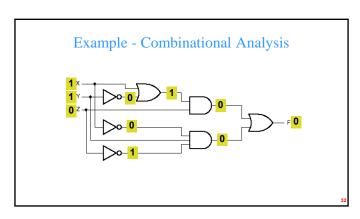

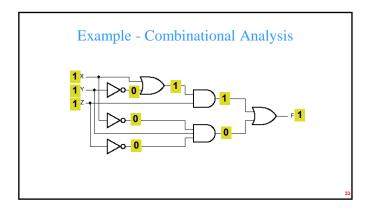

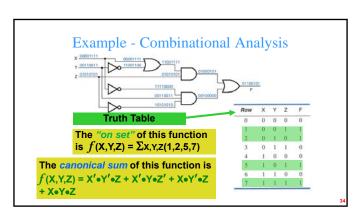

Analyze the functional behavior of a logic circuit by constructing a truth table that lists the relationship between input variable combinations and the output variable

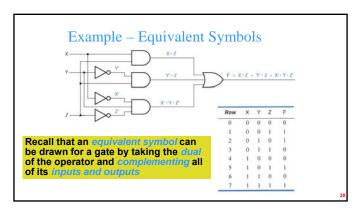

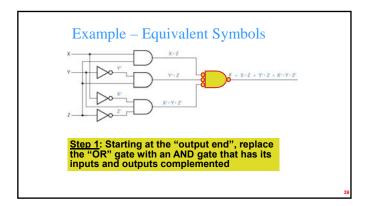

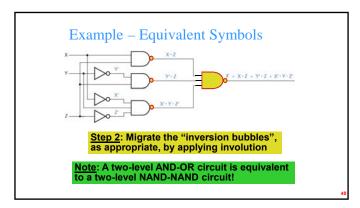

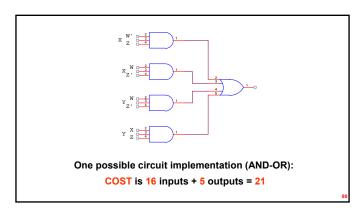

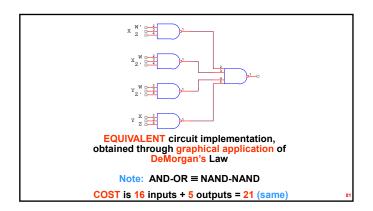

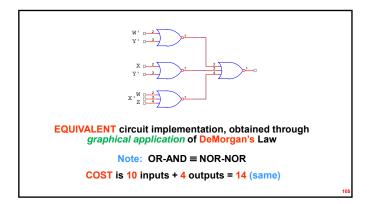

Transform a logic circuit from one set of symbols to another through graphical application of DeMorgan's Law

Realize a combinational function directly using basic gates (NOT, AND, OR, NAND, NOR)

## Outline

- Overview

- Definitions

- Minterm identification

- Maxterm identification

- ON Sets and OFF sets

- Combinational circuit analysis

- Equivalent symbols

- Combinational circuit synthesis

## Overview

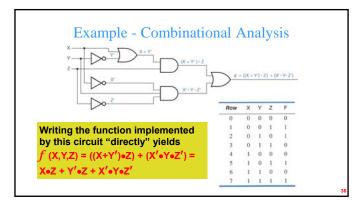

- We analyze a combinational logic circuit by obtaining a formal description of its logic function

Once we have a description of the logic function, we can:

- determine the behavior of the circuit for various input combinations

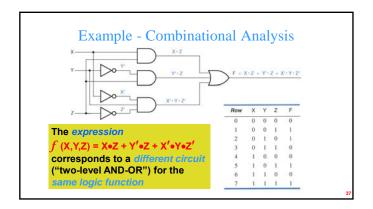

- manipulate an algebraic description to suggest different circuit structures

- transform an algebraic description into a standard form (e.g., sum-of-products for PLD implementation)

use an algebraic description of the circuit's functional behavior in the analysis of a larger system that includes the circuit

## **Definitions**

- Definition: A combinational logic circuit is one whose output depend only on its current combination of input values (or "input combination")

- <u>Definition</u>: A *logic function* is the ass*ignment* of "0" or "1" to each possible combination of its input variables

## **Definitions**

- Definition: A literal is a variable or the complement of a variable

- Definition: A product term is a single literal or a logical product of two or more literals

- Definition: A sum-of-products expression is a logical sum of product terms

- <u>Definition</u>: A sum term is a single literal or a logical sum of two or more literals

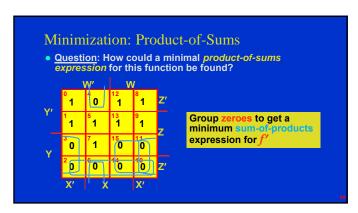

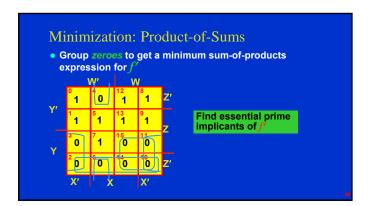

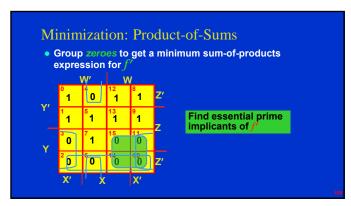

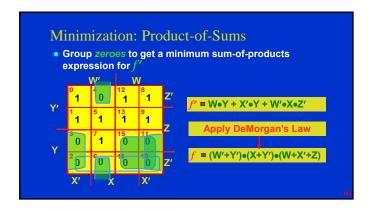

- <u>Definition</u>: A <u>product-of-sums</u> expression is a logical product of sum terms

## **Examples**

W, X, Y'Literals

$W \bullet X \bullet Z$ **Product Term**

$X \bullet Y' + W \bullet Z$  Sum of Products Expression

X + Y + Z'Sum Term

(X + Y) • (W + Z') Product of Sums Expression

## **Definitions**

- <u>Definition</u>: A normal term is a product or sum term in which no variable appears more than once

- **<u>Definition</u>**: An n-variable *minterm* is a normal product term with n literals

- <u>Definition</u>: An n-variable *maxterm* is a normal sum term with n literals

- Definition: The canonical sum of a logic function is a sum of miniterms corresponding to input combinations for which the function produces a "1" output

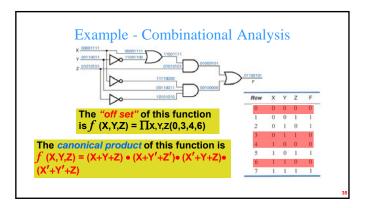

- <u>Definition</u>: The canonical product of a logic function is a product of maxterms corresponding to input combinations for which the function produces a "0" output

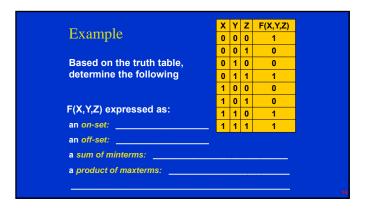

ON Sets and OFF Sets

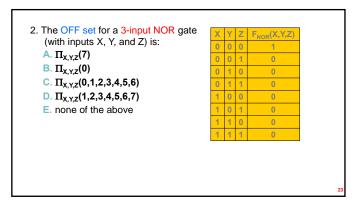

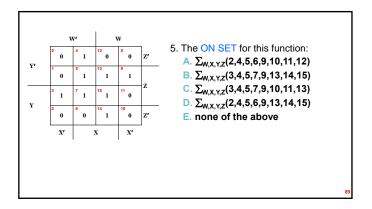

• <u>Definition</u>: The minterm list that "turns on" an output function is called the *on set*• <u>Example</u>:  $\Sigma_{X,Y,Z}(0,1,2,3)$ Indicates "sum" (of products)

Rows of truth table that are "1"

• <u>Definition</u>: The maxterm list that "turns off" an output function is called the *off set*• <u>Example</u>:  $\Pi_{X,Y,Z}(4,5,6,7)$ Indicates "product" (of sums)

Rows of truth table that are "0"

Example  $\begin{array}{c|cccc}

X & Y & Z & F(X,Y,Z) \\

0 & 0 & 0 & 1 \\

0 & 0 & 1 & 0 \\

0 & 0 & 1 & 0 \\

0 & 0 & 1 & 0 \\

0 & 0 & 1 & 0 \\

0 & 1 & 1 & 1 \\

1 & 0 & 0 & 0 \\

1 & 0 & 1 & 0 \\

1 & 0 & 1 & 0 \\

1 & 0 & 1 & 0 \\

1 & 0 & 1 & 0 \\

1 & 0 & 1 & 0 \\

1 & 0 & 1 & 0 \\

1 & 0 & 1 & 0 \\

1 & 0 & 1 & 0 \\

1 & 1 & 0 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1 & 1 & 1 & 1 \\

1$

School of Electrical & Computer Engineering Purdue University, College of Engineering

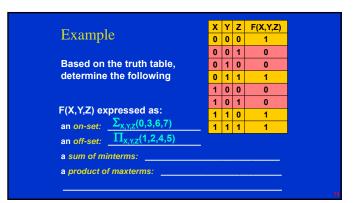

| P 1                                                                                                                                | Х          | Υ   | Z   | F(X,Y,Z)            |

|------------------------------------------------------------------------------------------------------------------------------------|------------|-----|-----|---------------------|

| Example                                                                                                                            | 0          | 0   | 0   | 1                   |

|                                                                                                                                    | 0          | 0   | 1   | 0                   |

| Based on the truth table,                                                                                                          | 0          | 1   | 0   | 0                   |

| letermine the following                                                                                                            | 0          | 1   | 1   | 1                   |

|                                                                                                                                    | 1          | 0   | 0   | 0                   |

|                                                                                                                                    | 1          | 0   | 1   | 0                   |

| X,Y,Z) expressed as:                                                                                                               | 1          | 1   | 0   | 1                   |

| n on-set: $\Sigma_{X,Y,Z}(0,3,6,7)$                                                                                                | _ 1        | 1   | 1   | 1                   |

| an off-set: $\frac{\prod_{X,Y,Z}(1,2,4,5)}{\prod_{X,Y,Z}(1,2,4,5)}$ a sum of minterms: $\frac{X'*Y'*Z'+X}{\prod_{X,Y,Z}(1,2,4,5)}$ | _<br>'•Y•Z | + X | (•Y | • <u>Z' + X•Y</u> • |

| Evamela                                                                              | X       | Υ   | z  | F(X,Y,Z)    |

|--------------------------------------------------------------------------------------|---------|-----|----|-------------|

| Example                                                                              | 0       | 0   | 0  | 1           |

|                                                                                      | 0       | 0   | 1  | 0           |

| Based on the truth table,                                                            | 0       | 1   | 0  | 0           |

| letermine the following                                                              | 0       | 1   | 1  | 1           |

|                                                                                      | 1       | 0   | 0  | 0           |

|                                                                                      | 1       | 0   | 1  | 0           |

| (X,Y,Z) expressed as:                                                                | 1       | 1   | 0  | 1           |

| an on-set: $\Sigma_{X,Y,Z}(0,3,6,7)$                                                 | _ 1     | 1   | 1  | 1           |

| an off-set: $\Pi_{X,Y,Z}(1,2,4,5)$<br>a sum of minterms: $X' \cdot Y' \cdot Z' + X'$ |         | н X | ·Υ | •Z' + X•Y•  |

| a product of maxterms:                                                               |         |     |    |             |

| (X+Y+Z')•(X+Y'+Z)• (X'+Y                                                             | '+Z)•(X | ĽŦ  | Y+ | <b>7</b> ') |

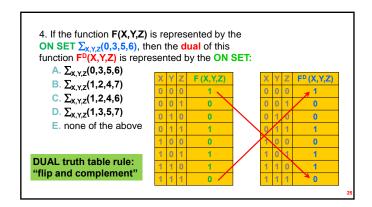

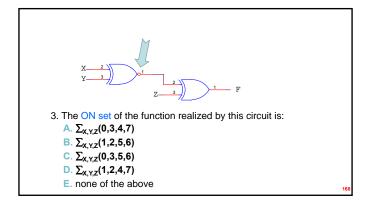

Clicker Quiz

3. If the function  $\mathbf{F}(\mathbf{X},\mathbf{Y},\mathbf{Z})$  is represented by the ON SET  $\sum_{\mathbf{X},\mathbf{Y},\mathbf{Z}}(\mathbf{0},\mathbf{3},\mathbf{5},\mathbf{6})$ , then the complement of this function  $\mathbf{F}'(\mathbf{X},\mathbf{Y},\mathbf{Z})$  is represented by the ON SET:

A.  $\sum_{\mathbf{X},\mathbf{Y},\mathbf{Z}}(\mathbf{0},\mathbf{3},\mathbf{5},\mathbf{6})$ B.  $\sum_{\mathbf{X},\mathbf{Y},\mathbf{Z}}(\mathbf{1},\mathbf{2},\mathbf{4},\mathbf{7})$ C.  $\sum_{\mathbf{X},\mathbf{Y},\mathbf{Z}}(\mathbf{1},\mathbf{2},\mathbf{4},\mathbf{6})$ D.  $\sum_{\mathbf{X},\mathbf{Y},\mathbf{Z}}(\mathbf{1},\mathbf{3},\mathbf{5},\mathbf{7})$ E. none of the above

## Summary There are numerous ways a combinational logic function can be represented truth table algebraic sum of minterms (sum-of-products expression) minterm list (ON set) algebraic product of maxterms (product-of-sums expression) maxterm list (OFF set)

Clicker Quiz

- 1. A NOR gate is logically equivalent to:

- A. an AND gate with inverted inputs

- B. an OR gate with inverted inputs

- C. a NAND gate with inverted inputs

- D. a NOR gate with inverted inputs

- E. none of the above

- 2. An OR gate is logically equivalent to:

- A. an AND gate with inverted inputs

- B. an OR gate with inverted inputs

- C. a NAND gate with inverted inputs

- D. a NOR gate with inverted inputs

- E. none of the above

- 3. A circuit consisting of a level of **NOR gates** followed by a level of **AND gates** is **logically equivalent** to:

- A. a multi-input OR gate

- B. a multi-input AND gate

- C. a multi-input NOR gate

- D. a multi-input NAND gate

- E. none of the above

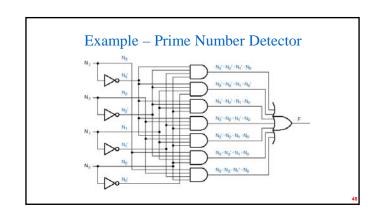

## Combinational Synthesis

- A circuit *realizes* ("makes real") an expression if its output function equals that expression

- Such a circuit is called a realization of the function

- Typically there are many possible realizations of the same function

- Circuit transformations can be made algebraically or graphically

## Combinational Synthesis

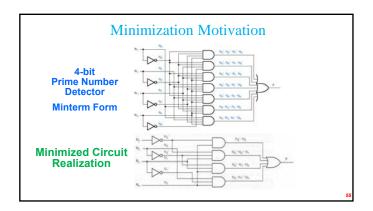

- The starting point for designing a combinational logic circuit is usually a word description of a problem

- Example: Design a 4-bit prime number detector (or, Given a 4-bit input combination M = N3N2N1N0, design a function that produces a "1" output for M = 1, 2, 3, 5, 7, 11, 13 and a "0" output for all other numbers)

f (N3,N2,N1,N0) =  $\Sigma$ N3,N2,N1,N0(1,2,3,5,7,11,13)

## Reading Assignment:

DDPP 4th Ed. pp. 210-222, 5th Ed. pp. 117-125

## **Learning Objectives:**

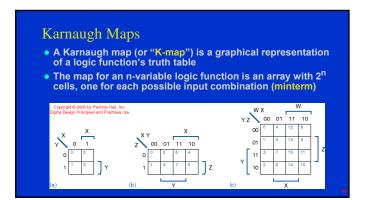

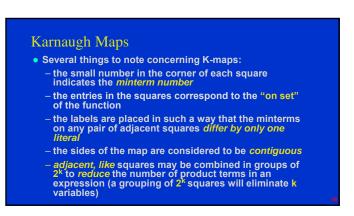

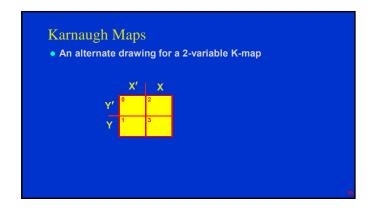

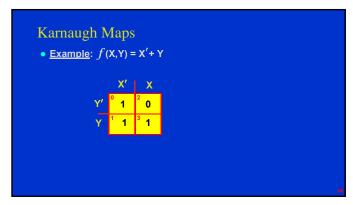

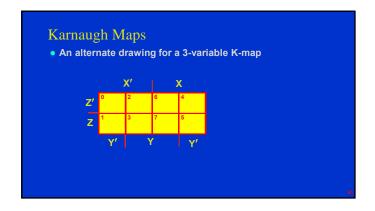

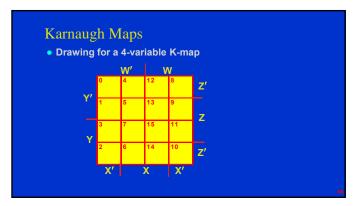

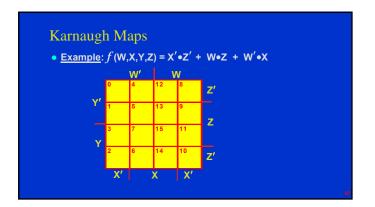

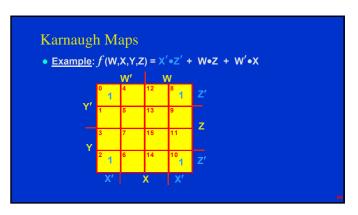

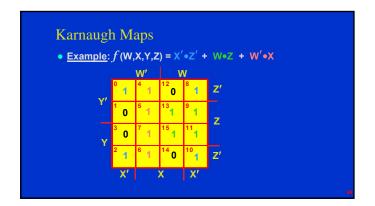

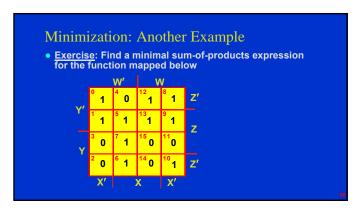

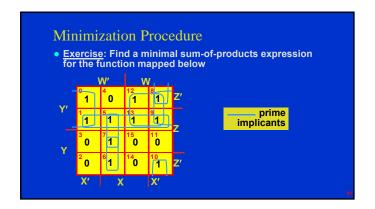

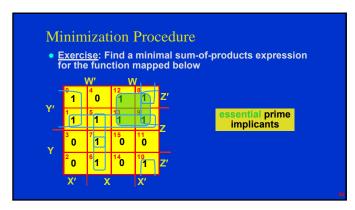

- Draw a Karnaugh Map ("K-map") for a 2-, 3-, 4-, or 5-variable logic function

- List the assumptions underlying function minimization

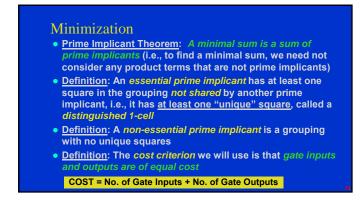

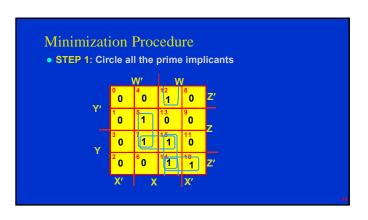

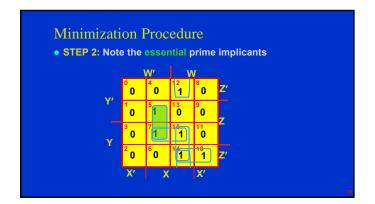

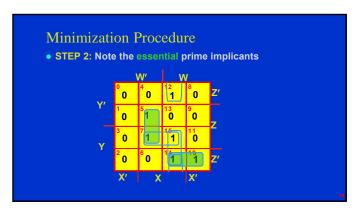

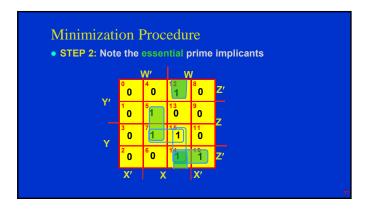

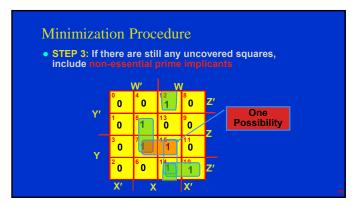

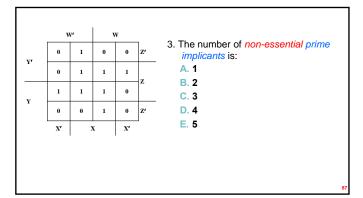

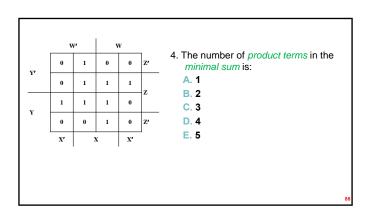

- Identify the prime implicants ("PI"), essential PI, and non-essential PI of a function depicted on a K-map

- Use a K-map to minimize a logic function (including those that are incompletely specified) and express it in either minimal SoP or PoS form

- Use a K-map to convert a function from one standard form to another

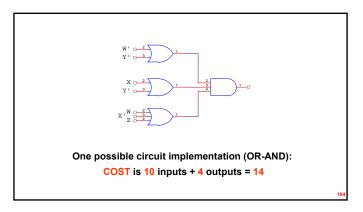

- Calculate and compare the cost (based on the total number of gate inputs plus the number of gate outputs) of minimal SoP and PoS realizations of a given function

- Realize a function depicted on a K-map as a two-level NAND circuit, two-level NOR circuit, or as an open-drain NAND/wired-AND circuit

## Outline

- Overview

- Representation of logic functions using K-maps

- Minimization of logic functions using K-maps

- NAND-Wired AND configuration

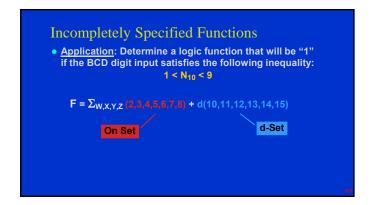

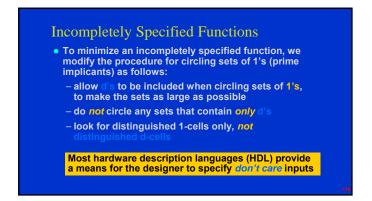

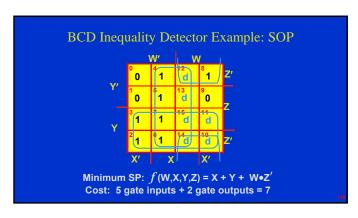

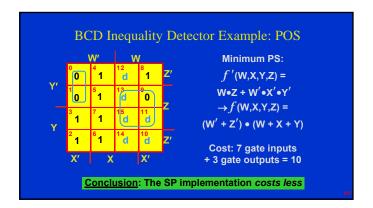

- Incompletely specified functions

- where they occur

- how to minimize them

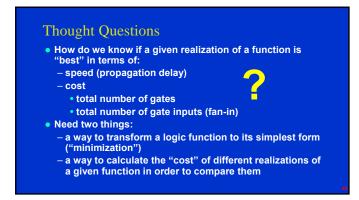

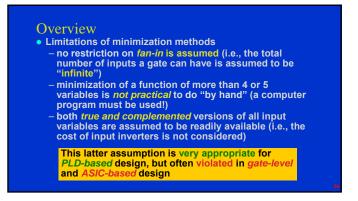

## Overview

- Minimization is an important step in both ASIC (application specific integrated circuit) design and in PLD-based (programmable logic device) design

- Extra gates and gate inputs require more chip area ("real estate") and thereby increase cost and power consumption

- Canonical sum and product expressions (which can be determined "directly" from a truth table) are particularly expensive because the number of minterms [maxterms] grows exponentially with the number of variables

## Overview

- Minimization reduces the cost of two-level AND-OR, OR-AND, NAND-NAND, NOR-NOR circuits by:

- minimizing the number of first-level gates

- minimizing the number of inputs on each first-level gate

- minimizing the number of inputs on the second-level

- Most minimization methods are based on a generalization of the Combining Theorems (T10 and T10'):

Expression • X + Expression • X' = Expression

Takeaway: The fundamental basis of logic minimization is the COMBINING THEOREM

School of Electrical & Computer Engineering Purdue University, College of Engineering

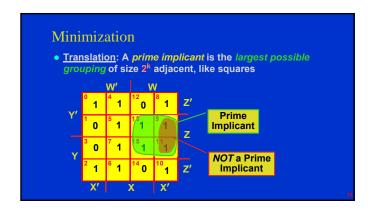

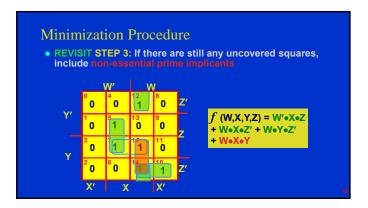

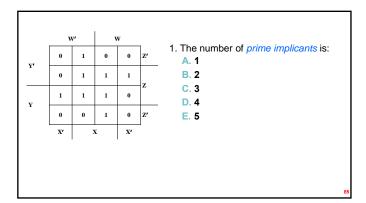

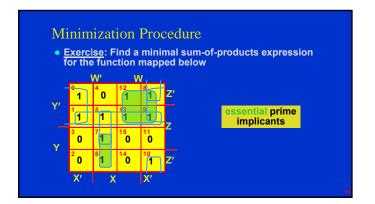

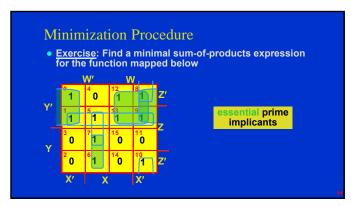

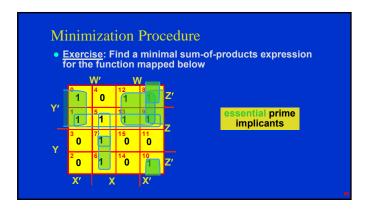

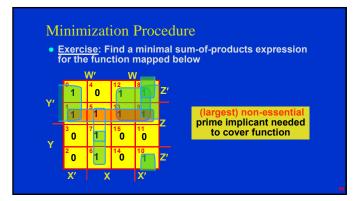

## Minimization Definition: A logic function p implies a logic function f if for every input combination such that p = 1, then f = 1 also (i.e., if p implies f, then f is 1 for every input combination that p is 1, and maybe some more – or "f covers p") Definition: A prime implicant of an n-variable logic function f is a normal product term P that implies f, such that if any literal is removed from P, then the resulting product term does not imply f

Clicker Quiz

|    | v    | V' | , | W  | _  | O. The average of according prime                                    |

|----|------|----|---|----|----|----------------------------------------------------------------------|

| Y' | 0    | 1  | 0 | 0  | Z' | <ol> <li>The number of essential prime<br/>implicants is:</li> </ol> |

| 1  | 0    | 1  | 1 | 1  |    | A. 1                                                                 |

|    | 1    | 1  | 1 | 0  | z  | B. 2<br>C. 3                                                         |

| Y  | 0    | 0  | 1 | 0  | Z' | D. 4                                                                 |

|    | X' X |    | K | X' | _  | E. 5                                                                 |

18

| BCD Inequality Detector Example |                 |      |            |  |  |

|---------------------------------|-----------------|------|------------|--|--|

|                                 | N <sub>10</sub> | WXYZ | F(W,X,Y,Z) |  |  |

|                                 | 0               | 0000 | 0          |  |  |

|                                 | 1               | 0001 | 0          |  |  |

|                                 | 2               | 0010 | 1          |  |  |

|                                 | 3               | 0011 | 1          |  |  |

|                                 | 4               | 0100 | 1          |  |  |

|                                 | 5               | 0101 | 1          |  |  |

|                                 | 6               | 0110 | 1          |  |  |

|                                 | 7               | 0111 | 1          |  |  |

|                                 | 8               | 1000 | 1          |  |  |

|                                 | 9               | 1001 | 0          |  |  |

|                                 |                 |      |            |  |  |

Clicker Quiz

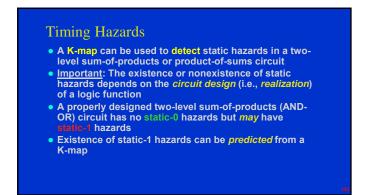

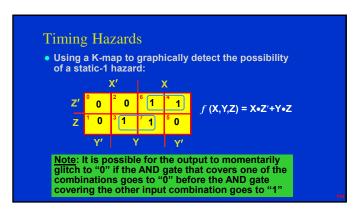

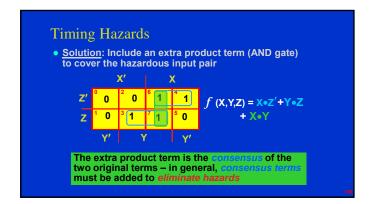

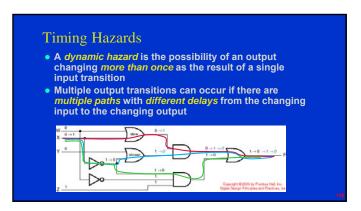

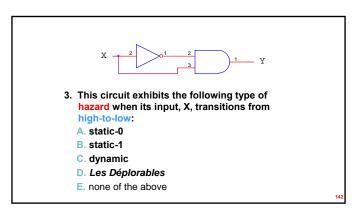

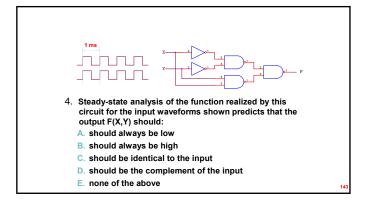

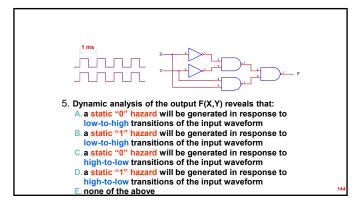

## Outline • Timing hazards - Static - Dynamic • Elimination of timing hazards • Clever utilization of timing hazards • Designing hazard-free circuits

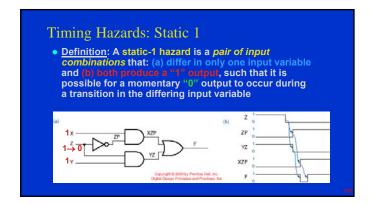

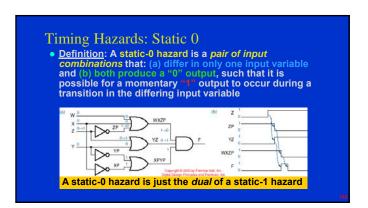

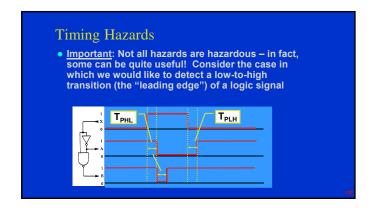

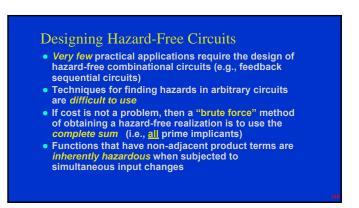

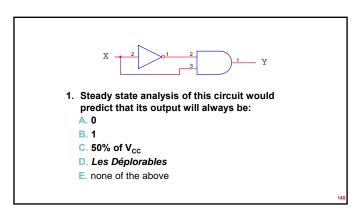

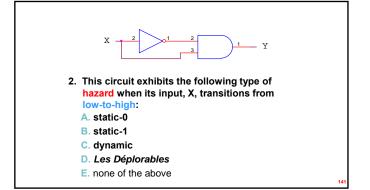

# Timing Hazards The combinational circuit analysis methods described thus far ignore propagation delay and predict only the steady state behavior Gate propagation delay may cause the transient behavior of logic circuit to differ from that predicted by steady state analysis A circuit's output may produce a short pulse (often called a glitch) at time when steady state analysis predicts the output should not change A hazard is said to exist when a circuit has the possibility of producing such a glitch

## Clicker Quiz

Reading Assignment:

DDPP 4th Ed. pp. 447-448, 5th Ed. pp. 320-322

Learning Objectives:

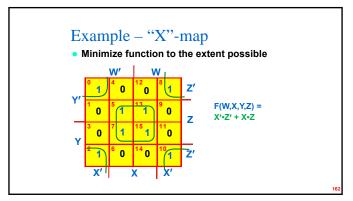

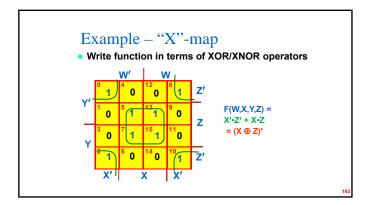

Identify properties of XOR/XNOR functions

Simplify an otherwise non-minimizable function by expressing it in terms of XOR/XNOR operators

## Outline

- XOR and XNOR functions

- XOR operator properties

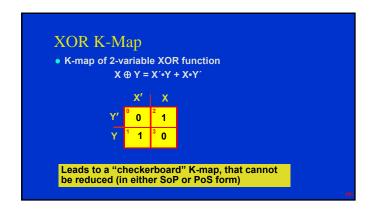

- XOR "checkerboard" K-map

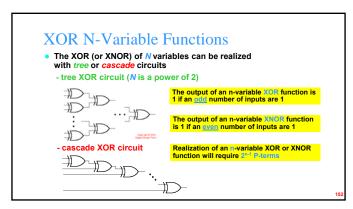

- XOR N-variable functions

- Realization of "non-reducible" functions using XOR/XNOR gates

## **XOR/XNOR Functions**

- An Exclusive-OR (XOR) gate is a 2-input gate whose output is "1" if exactly one of its inputs is "1" (or, an XOR gate produces an output of "1" if its inputs are different)

- An Exclusive-NOR (XNOR) gate is the complement of an XOR gate – it produces an output of "1" if its inputs are the same

- An XNOR gate is also referred to as an Equivalence (or XAND) gate

- Although XOR is not one of the basic functions of switching algebra, discrete XOR gates are commonly used in practice

## **XOR/XNOR Functions**

- The "ring sum" operator ⊕ is often used to denote the XOR function: X⊕Y = X'•Y + X•Y'

- The XNOR function can be thought of as either the dual or the complement of the XOR function

$(X \oplus Y)' = (X \oplus Y)^D = X' \cdot Y' + X \cdot Y$

| Х | Υ | Χ⊕Y | (X⊕Y)′ |

|---|---|-----|--------|

| 0 | 0 | 0   | 1      |

| 0 | 1 | 1   | 0      |

| 1 | 0 | 1   | 0      |

| 1 | 1 | 0   | 1      |

|   |   |     |        |

## XOR Operator ⊕ Properties

- X ⊕ X = X'•X + X•X' = 0 + 0 = 0

- $X' \oplus X' = X \cdot X' + X' \cdot X = 0 + 0 = 0$

- X ⊕ 1 = X' •1 + X•0 = X'

- X' ⊕ 1 = X•1 + X'•0 = X

- (X ⊕ Y)′ = X ⊕ Y ⊕ 1

- X ⊕ Y = Y ⊕ X

- $X \oplus (Y \oplus Z) = (X \oplus Y) \oplus Z$

- X•(Y ⊕ Z) = (X•Y) ⊕ (X•Z)

XOR and XNOR Equivalent Symbols

25

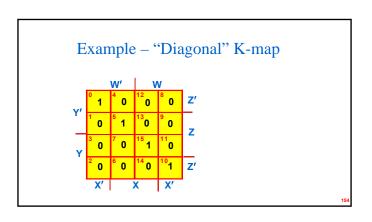

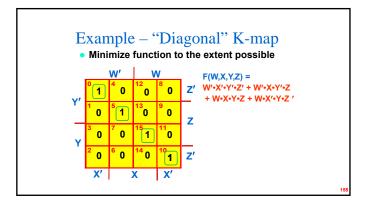

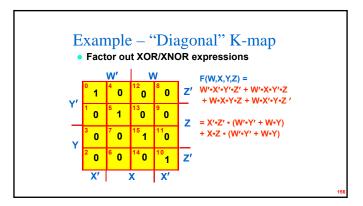

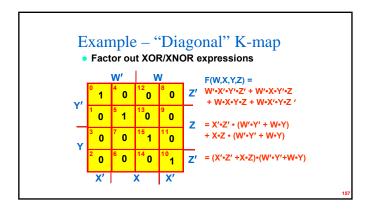

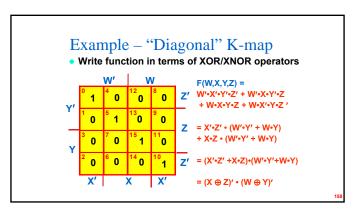

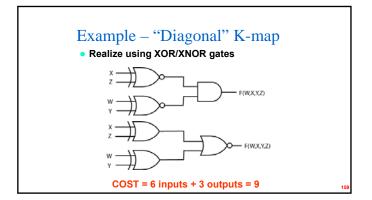

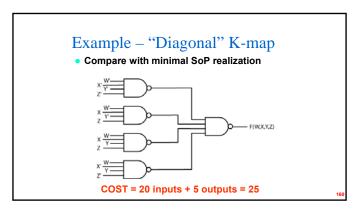

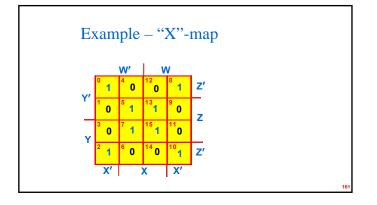

## Non-Reducible Functions • Functions that cannot be significantly reduced using conventional minimization techniques can sometimes be simplified by implementing them with XOR/XNOR gates • Candidate functions that may be simplified this way have K-maps with "diagonal 1's" • Technique: Write out function in SoP form, and "factor out" XOR/XNOR expressions

Clicker Quiz

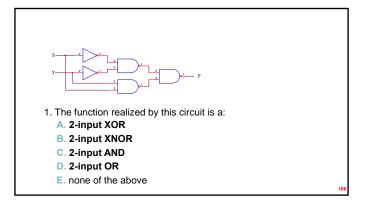

2. The ON set of the function realized by this circuit is:

A.  $\sum_{X,Y}(0,2)$ B.  $\sum_{X,Y}(0,3)$ C.  $\sum_{X,Y}(1,2)$ D.  $\sum_{X,Y}(1,3)$ E. none of the above

4. The XOR property listed below that is NOT true is:

A. X ⊕ 0 = X

B. X ⊕ 1 = X'

C. X ⊕ X = X

D. X ⊕ X' = 1

E. none of the above

5. The following is NOT an equivalent symbol for an XOR gate:

A.

B.

C.

D.

E. none of the above

Reading Assignment:

DDPP 4<sup>th</sup> Ed. pp. 370-383, 840-859; 5<sup>th</sup> Ed. pp. 246-252

Learning Objectives:

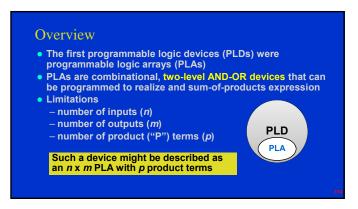

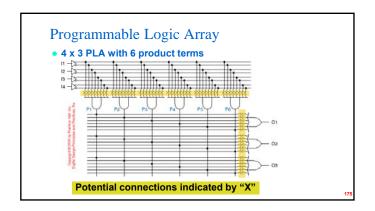

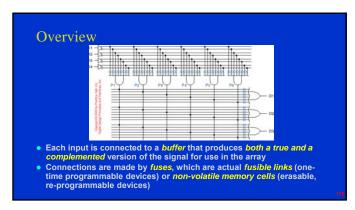

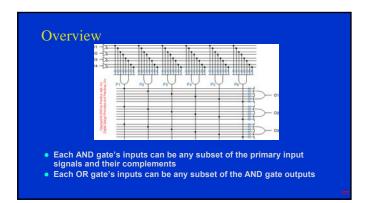

Describe the genesis of programmable logic devices

List the differences between complex programmable logic devices (CPLDs) and field programmable gate arrays (FPGAs) and describe the basic organization of each

## Outline Overview Programmable Logic Arrays (PLAs) Programmable Array Logic (PALs) Generic Array Logic (GALs) Complex PLDs Field Programmable Gate Arrays (FPGAs) Summary

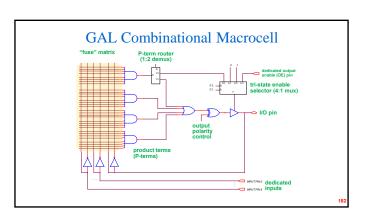

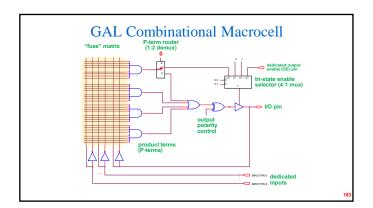

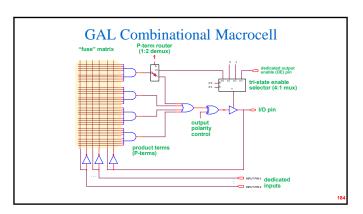

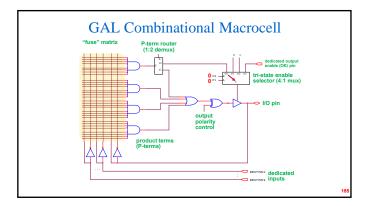

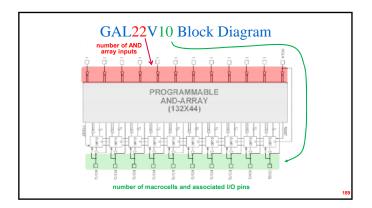

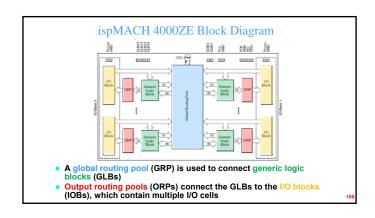

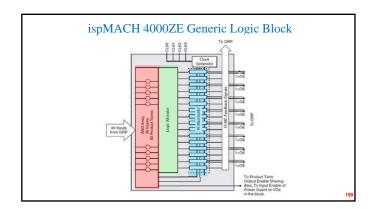

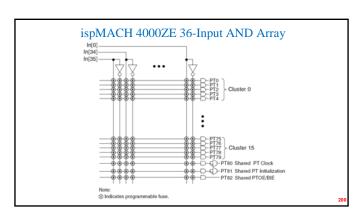

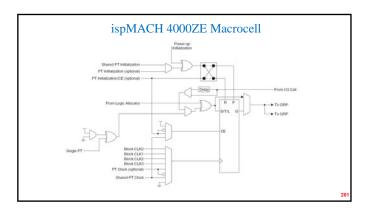

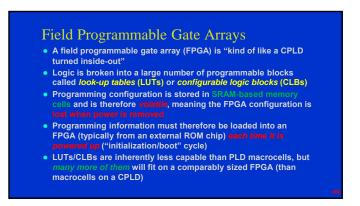

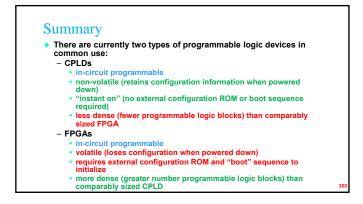

Complex PLDs (CPLDs)

Modern complex PLDs (CPLDs) contain hundreds of macrocells and I/O pins, and are designed to be erased/reprogrammed in-circuit (called "isp")

Because CPLDs typically contain significantly more macrocells than I/O pins, capability is provided to use macrocell resources "internally" (called a node)

Example: The Lattice ispMACH 4000 series CPLDs feature 36-input, 16-macrocell GLBs

A "breakout board" utilizing an ispMACH 4256ZE device (with 256 macrocells and 144 pins) will be used for the second half of the lab experiments

## Reading Assignment:

DDPP 4th Ed. pp. 237-243, 290-335; 5th Ed. pp. 177-233

## Learning Objectives:

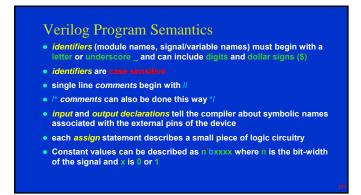

- List the basic features and capabilities of a hardware description language

- List the syntactic elements of a Verilog module

- Identify operators and keywords used to create Verilog modules

- Write equations using Verilog dataflow syntax

- Define functional behavior by creating truth tables with the casez construct in Verilog

## Outline

- Overview

- Verilog and ispLever<sup>™</sup>

- Verilog coding semantics

- Verilog module structure

- Verilog symbols for logical operationsSample Verilog modules

- Structural code in Verilog

## Overview

- Hardware description languages (HDLs) are the most common way to describe the programming configuration of a CPLD or an FPGA

The first HDL to enjoy widespread use was PALASM ("PAL Assembler")

- from Monolithic Memories, Inc. (inventors of the PAL device)

- Early HDLs only supported equation entry

- Next generation languages such as CUPL (Compiler Universal for Programmable Logic) and ABEL (Advanced Boolean Expression Language) added more advanced capabilities:

- truth tables and clocked operator tables

- logic minimization

- high-level constructs such as when-else-then and state diagram

- timing analysis

## Overview

- Both VHDL and Verilog started out as simulation languages (later developments in these languages allowed actual hardware design)

- Both languages support modular, hierarchical coding and support a wide variety of high-level programming constructs - represer

- a higher lo

- proceduresfunction calls

- conditional and iterative statements

I Pitfall – Because VHDL and Verilog have their genesis as simulation languages, it is possible to create non-synthesizable

HDL code using them (i.e., code that can simulate a digital system,

Advantage - VHDL and Verilog are much better adapted to large scale system design Verilog has become the most common language for IC design and verification.

## Verilog and ispLever<sup>TM</sup>

- Because Verilog is so commonly used in industry and you will need it in future classes, you will be introduced to Verilog in this course

- You will use Verilog to program legacy PLDs (like the 22V10) as well as current generation CPLDs (like the ispMACH 4256ZE)

- We will use the Lattics ispLever Classic 1.8 software package in lab, which includes support for ABEL, Verilog, and VHDL as well as schematic entry

- You can obtain your own free copy of this software from the Lattice Semiconductor web site (www.li

## Verilog and ispLever<sup>TM</sup>

- A Verilog module is a text file containing:

- documentation (program name, comments)

- declarations that identify the inputs and outputs of the logic functions to be performed

- statements that specify the logic functions to be performed

- Because you need to be able to program a PLD or CPLD, your t be strictly limited to syntax that translates neatly into logic circuitry

- Verilog source files are transformed into a fuse map file by the compiler integrated into ispLever

- A universal programmer is used to burn the fuse map file into a legacy PLD device (an isp device can be programmed directly from the integrated ispVM tool via a USB cable)

```

Verilog MODULE Structure (Example 1)

// comments start with double slash, keywords highlighted in red

/* or they can be bounded with slash star as in C */

sodula nand_nor(sel,A,B,Y);

input wise Sel, A, B;

output wise Sel, A, B;

output wise Y;

Describes a circuit called mand_nor

with inputs Sel, A, B, and output Y

wisa Y1, Y2, Y3, Y4;

4 individual wire names Y1...Y4

assign Y = Y3 | Y4;

assign Y1 = A & B;

assign Y2 = A | B;

assign Y3 = (-Y1) & Sel;

assign Y4 = (-Y2) & (-Sel);

endmodule

```

```

Verilog MODULE Structure (Example 1)

moduls nand_nor(Sel,A,B,Y);

input wire Sel, A, B /* synthesis loc="4,5,6" */;

output wire Y /* synthesis loc="7" */;

output wire Y /* synthesis loc="7" */;

wire Y1, Y2, Y3, Y4;

assign Y = Y3 | Y4;

assign Y = A & B;

assign Statements are not the only way of describing your logic, but they are the simplest for very small combinational logic designs

endmodule

```

```

Verilog MODULE Structure (Example 1)

sodule nand_nor(Sel,A,B,Y);

input wire Sel, A, B /* synthesis loc="4,5,6" */;

cutput wire [1:0] Y /* synthesis loc="7,8" */;

wire Y1, Y2, Y3,Y4;

The index range [1:0] makes Y into a 2-bit vector Y[1] assign Y = [Y3,Y4];

assign Y = [Y3,Y4];

assign Y1 = A & B;

assign Y2 = A | B;

assign Y2 = A | B;

assign Y3 = (-Y1) & Sel;

assign Y4 = (-Y2) & (-Sel);

enducedule

```

```

Verilog BIT Literals

wire a,b;

wire [2:0] Y;

assign a = 1'b0;

assign b = 1'b1;

assign Y = 3'b100;

3 bits equal to binary 1

3 bits equal to 1002

Y[2]=1'b1 Y[1]=1'b0 Y[0]=1'b0

```

```

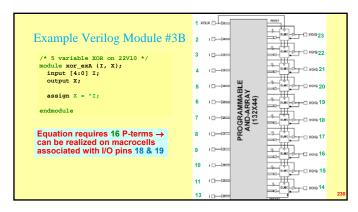

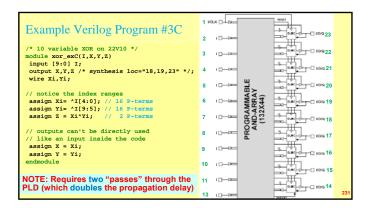

Example Verilog Module #1A

/* Verilog Combinational Example for GAL22V10 */

module verilog_exA(A,B,C,D,X,Y,Z);

input A,B,C,D /* synthesis loc="2,3,4,5" */;

output X,Y,Z /* synthesis loc="14,15,16" */;

// dataflow style logic equations

assign X = (A & B) | -(C & D);

assign Y = -(B & D) | -(A & B & D);

assign Z = A & -(B & C & C -D);

// use parenthesis for readability

// and to make sure order of operations

// (precedence) are as intended

mitted and automatically assigned by

endmodule

```

```

Example Verilog Module #IB

/* Verilog Combinational Example for GAL22V10

with active low inputs */

// "n" prefix is just a naming convention

module verilog_exA(nA,nB,nC,nD,X,Y,Z);

input nA,nB,nC,nD /* synthesis loc="2,3,4,5" */;

output X,Y,Z /* synthesis loc="2,3,4,5" */;

output X,Y,Z /* synthesis loc="14,15,16" */;

wire A,B,C,D;

assign A = -nA; // to treat inputs as

assign B = -nB; // active low, you must

assign C = -nC; // invert them

assign D = -nD;

assign X = (A & B) | ~(C & D);

assign X = (A & B) | ~(C & D);

assign Z = A & ~(B & C & ~D);

endmodule

```

```

Example Verilog Module #IC

/* Verilog Combinational Example for GAL22V10

with active low inputs and outputs */

module verilog_exA(nA,nB,nC,nD,nX,nY,nZ);

input nA,nB,nC,nD /* synthesis loc="2,3,4,5" */;

output nX,nY,nZ /* synthesis loc="14,15,16" */;

wire A,B,C,D;

assign A = -nA; // to treat inputs as

assign B = -nB; // active low, you must

assign C = -nC; // invert them

assign D = -nD;

// to make outputs active low, invert the

// value assigned to the output

assign nX = -( (A & B) | -(C & D) );

assign nX = -( (A & B) | -(C & D) );

assign nX = -( (A & C & C & D) );

endmodule

```

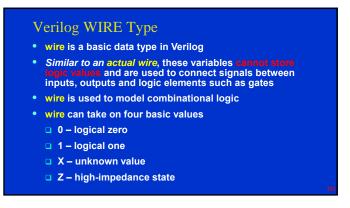

# Verilog REG Data Types • Similar data type to wire, but reg can be used to store information • Unlike wire, reg can be used to model both combinational and sequential logic • For behavioral code using an always block, the output must be type reg • For dataflow code with assign statements, the outputs must be of type wire • Examples: \*\*Reg Byyes\*; // one bit variable called Byyes\* \*\*Reg [7:0] Byyes\*; // 8-bit variable called Byyes\*

```

ALWAYS Block in Verilog

• An always block lets you write "behavioral" style code, similar to C

• Should have a sensitivity list associated with it: all statements in the always block will be evaluated when the conditions in this list are triggered

• Conditions may be any change to the signal or rising or falling edges of the signals

```

```

ALWAYS Block in Verilog

Example always blocks:

always @ (A,B,C) begin

...

All statements will be evaluated whenever A, B, or C change their values

end

always @ (posedge CLK) begin

...

end

All statements will be evaluated on the positive (rising) edge of CLK signal (use negrodge for falling edge of CLK)

always @ (*) begin

...

All statements will be evaluated whenever any input signal in the always block changes

```

```

Verilog CASE Syntax

Similar to the case structure in C

Compares expression to a set of cases and evaluates the statement(s) associated with first matching case

All cases defined between case (signal) .. endcase

Multiple statements for a case must be enclosed in a begin and end block

Multiple comparison signals can be concatenated as case ((signal1, signal2...signaln)) and compared against values of their total bit width

If the logic does not cover all possible bit combinations of the comparison signal(s), a default case must be added. e.g. a 3-bit signal for comparison will need a default case if 8 cases are not provided

```

```

Verilog MODULE Structure (Example 2)

module nand_nor(Sel,A,B,Y);

input Sel, A, B /* synthesis loe="4,5,6" */;

output reg Y /* synthesis loe="4,5,6" */;

always @ (Sel,A,B) begin

cass ({Sel,A,B})

3'b000: Y = 1'b1; // row 0

3'b001: Y = 1'b1; // row 1

3'b010: Y = 1'b1; // row 2

// (remaining combinations)

default: Y = 1'b0; // or use a default cass

andmass

endmodule

Y must be declared as reg

type to be an output of an always block

Y must be declared as reg

type to be an output of an always block

Y must be declared as reg

type to be an output of an always block

Y must be declared as reg

type to be an output of an always block

Y must be declared as reg

type to be an output of an always block

Y must be declared as reg

type to be an output of an always block

Occupancy of the form of the

```

```

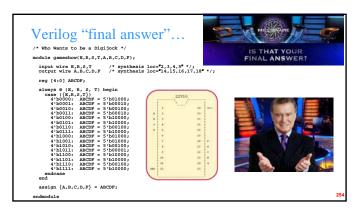

Example Verilog Module #2

/* Truth table example */*

module ttex(E, B, S, T, A, B, CD, P)

module ttex(E, B, S, T, A, B, CD, P)

continue to the state of the stat

```

```

Verilog Built-in Primitives

and not Usage of built-in primitives is illustrated in the next slide. The same syntax can be used for user-defined modules as well.

nor bufif1

nor bufif1

xor notif1

superior of the primitives is illustrated in the next slide. The same syntax can be used for user-defined modules as well.

For more information, refer to Section 5.7 in the Wakerly text.

```

```

Structural Code in Verilog

• Example illustrating multiple modules connected

module structural_ex(A,B,C,D,X,Y);

input wire A, B, C, D;

output wire X, Y;

wire AB, CD;

and AND2a (AB, A, B); // AB = A & B

and AND2b (CD, C, D); // CD = C & D

os OR2a (X, AB, CD); // X = AB | CD

assign Y = (A & B) | (C & D);

endmodule

```

### Clicker Quiz

- 1. Which of the following is  $\underline{\textbf{not}}$  a valid Verilog identifier?

- **B. 2X**

- C. XY

- D. \_XY

- E. none of the above

- 2. Which of the following specifies a range of bits within a bit vector X in Verilog?

- A. X3..X1

- B. X(3:1)

- C. [3:1]

- D. X[3:1]

- E. none of the above

- 3. For input or output port declarations, which of the following statements is not true?

- A. "synthesis loc" declarations associate the device's physical pins with symbolic port names

- B. pin numbers are optional

- C. if pin numbers are not specified, the pin numbers are assigned by the "fitter" program based on the PLD characteristics

- D. the pin may be declared active high or active low

- E. none of the above

4. The order in which different assign expressions are placed in the body of a Verilog module does not matter.

B. false

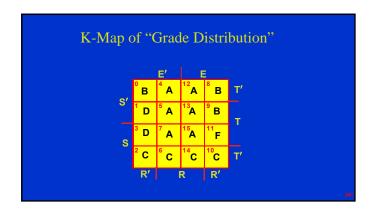

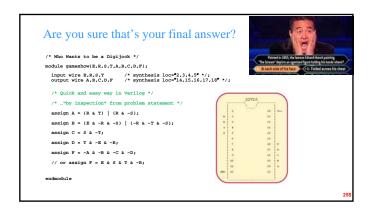

### Example - Your BFFAM's "Crazy Grader"

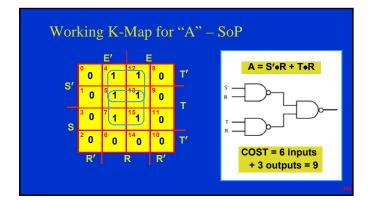

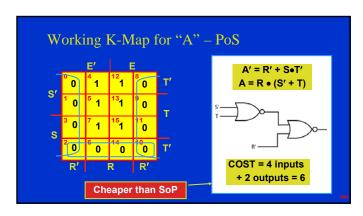

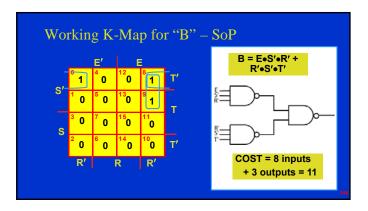

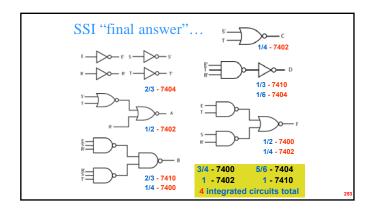

Your "best friend from another major" (BFFAM) has been asked to design a circuit that determines grades based on the characters (E,R,S,T) in a student's last name, as follows:

- Give a grade of "A" if name contains an R and a T -or-an R and not an S

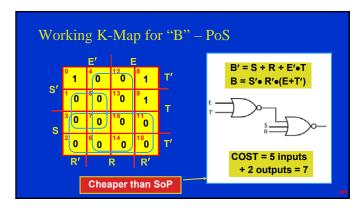

- Give a grade of "B" if name contains an E and not an R and not a S -or- does not contain an R and not a T and not an S

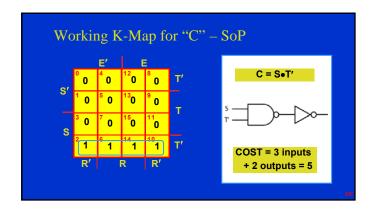

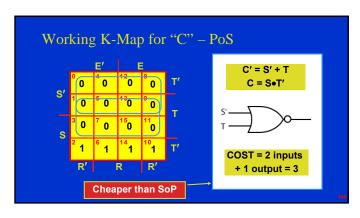

- Give a grade of "C" if name contains an S and not a T

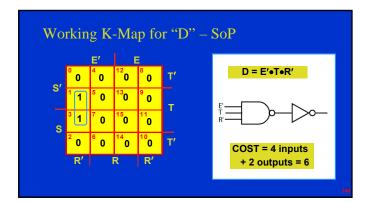

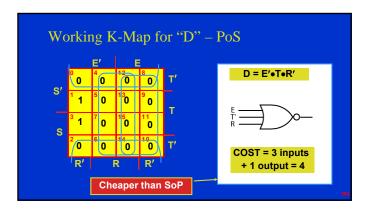

Give a grade of "D" if name contains a T and not an E

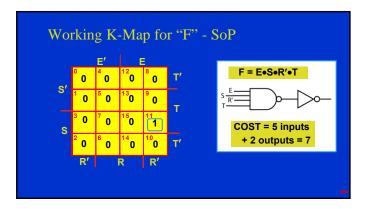

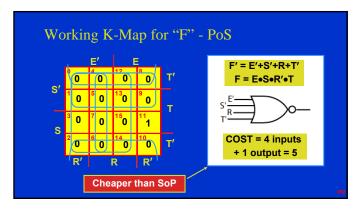

- Give a grade of "F" if none of the above (name contains an E and an S and a T and not an R)

© 2019 by D. G. Meyer 41

© 2019 by D. G. Meyer 42

Reading Assignment:

DDPP 4th Ed. pp. 384-390, 403-409; 5th Ed. pp. 250-256, 260-278

Learning Objectives:

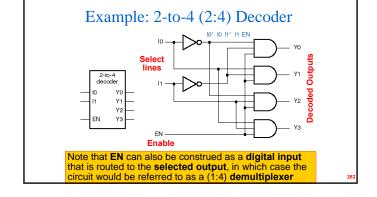

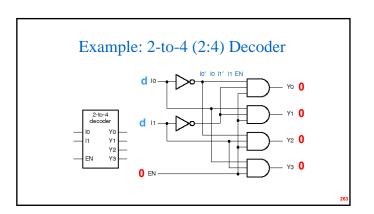

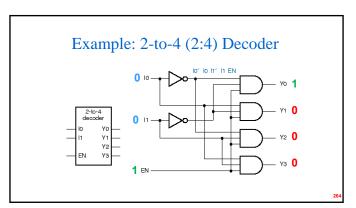

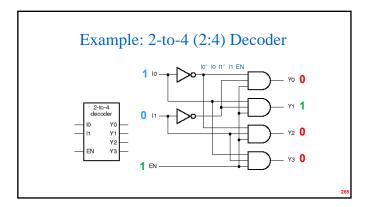

Define the function of a decoder (demultiplexer) and describe how it can be used as a combinational building block

Illustrate how a decoder can be used to realize an arbitrary Boolean function

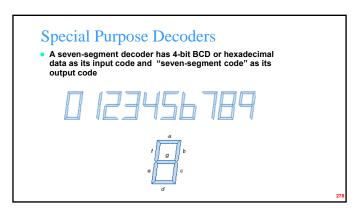

# Outline Overview Binary decoders Decoders in Verilog Special purpose decoders

### Overview

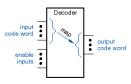

- <u>Definition</u>: A decoder is a multiple-input, multiple-output logic circuit that converts coded inputs into coded outputs

- The input code generally has fewer bits than the output code

- In a one-to-one mapping, each input code word produces a different output code word

### Overview

- The most commonly used input code is an n-bit binary code, where an n-bit word represents one of 2<sup>n</sup> different coded values

- Sometimes an n-bit binary code is truncated to represent fewer than 2<sup>n</sup> values (e.g., BCD)

- The most commonly used output code is a 1-out-of-m code, which contains m bits, where only one bit is asserted at any time (the output code bits are mutually exclusive)

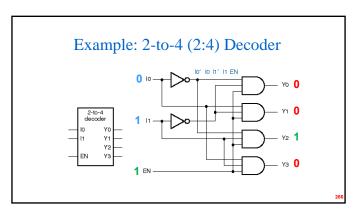

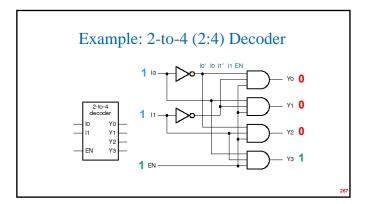

### Binary Decoders The most common decoder circuit is an n-to-2<sup>n</sup> decoder or binary decoder Binary decoder Binary decoders have an n-bit binary input code and a 1-out-of-2<sup>n</sup> output code Application: Used to activate exactly one of 2<sup>n</sup> outputs based on an n-bit value Analogy: Electronically-controlled rotary selector switch

nput to one of 2<sup>n</sup> outputs

s typically referred to as a (1-to-2<sup>n</sup>) **demultiplexer**

### **Key Observations**

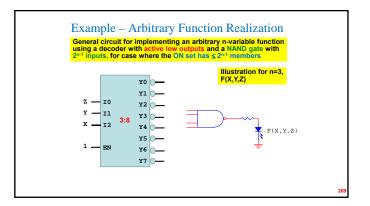

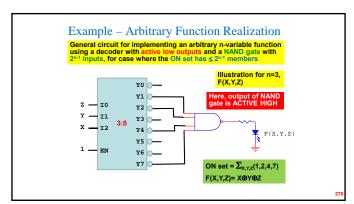

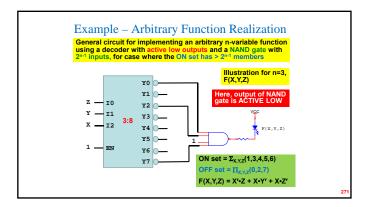

- Key Observation #1: each output of an n to 2<sup>n</sup> binary decoder represents a minterm of an n-variable Boolean function; therefore, any arbitrary Boolean function of n-variables can be realized with an n-input binary decoder by simply "OR-ing" the needed outputs

- Key Observation #2: if the decoder outputs are <u>active low</u>, a NAND gate can be used to "OR" the minterms of the function (representing its ON set)

- Key Observation #3: if the decoder outputs are active low, an AND gate can be used to "OR" the minterms of the complement function (representing its OFF set)

- <u>Key Observation #4</u>: a NAND gate (or AND gate) with at most 2<sup>n-1</sup> inputs is needed to implement an arbitrary n-variable function using an n to 2<sup>n</sup> binary decoder (that has <u>active low</u> outputs)

```

Decoders in Verilog

/* 3:8 Decoder / 1:8 Demultiplexer with Active-Low Outputs */

module dec38L(EN, I, nY);

input wire EH;

input wire [2:0] I;

output wire [7:0] N;

wire [7:0] Y;

assign NY = -Y;

// Active-low output pins

wire [7:0] Y;

assign Y[0] = EN & -I[2] & -I[1] & -I[0];

assign Y[1] = EN & -I[2] & -I[1] & -I[0];

assign Y[2] = EN & -I[2] & -I[1] & -I[0];

assign Y[3] = EN & -I[2] & -I[1] & -I[0];

assign Y[3] = EN & -I[2] & -I[1] & -I[0];

assign Y[3] = EN & -I[2] & -I[1] & -I[0];

assign Y[3] = EN & -I[2] & -I[1] & -I[0];

assign Y[3] = EN & -I[2] & -I[1] & -I[0];

assign Y[3] = EN & -I[2] & -I[1] & -I[0];

assign Y[3] = EN & I[2] & -I[1] & -I[0];

assign Y[3] = EN & I[2] & -I[1] & -I[0];

assign Y[3] = EN & I[2] & I[1] & -I[0];

assign Y[7] = EN & I[2] & I[1] & -I[0];

assign Y[7] = EN & I[2] & I[1] & -I[0];

assign Y[7] = EN & I[2] & I[1] & -I[0];

```

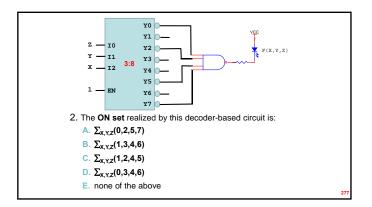

Clicker Quiz

```

1. The OFF set realized by this decoder-based circuit is:

A. \Pi_{X,Y,Z}(0,2,5,7)

B. \Pi_{X,Y,Z}(1,3,4,6)

C. \Pi_{X,Y,Z}(1,2,4,5)

D. \Pi_{X,Y,Z}(0,3,4,6)

E. none of the above

```

```

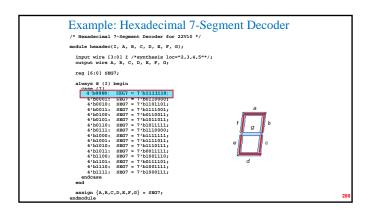

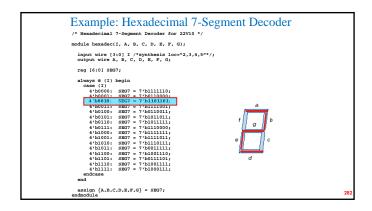

Example: Hexadecimal 7-Segment Decoder

/* Nexadecimal 7-Segment Decoder for 22/10 */

module hexadec(I, A, B, C, D, E, F, G);

input wire [3:0] I /* synthesis loc="2,3,4,5" */;

output wire A, B, C, D, E, F, G);

reg [6:0] SEG7;

always G (1) begin

case (1)

4-b00001; SEG7 = 7-b1111110;

4-b0001; SEG7 = 7-b110001;

4-b0016; SEG7 = 7-b110010;

4-b0016; SEG7 = 7-b110011;

4-b0101; SEG7 = 7-b110011;

4-b0101; SEG7 = 7-b110011;

4-b0101; SEG7 = 7-b110011;

4-b1001; SEG7 = 7-b110011;

4-b1001; SEG7 = 7-b1001110;

4-b101; SEG7 = 7-b100110;

4-b101; SEG7 = 7-b1001110;

4-b101; SEG7 = 7-b100110;

4-b101; SEG7 = 7-b1001110;

4-b101; SEG7 = 7-b100110;

4-b101; SEG7 = 7-b1001110;

4-b101; SEG7 = 7-b100110;

4-b101; SEG7 = 7-b100110;

4-b101; SEG7 = 7-b100110;

4-b101; SEG7 = SEG7;

8-B101; SEG7 = SEG7;

8-B

```

```

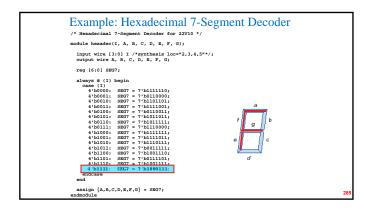

Example: Hexadecimal 7-Segment Decoder

/* Nexadecimal 7-Segment Decoder for 22V10 */

module hexadec(I, A, B, C, D, E, F, G);

input wire (3:0) I /*synthesis loc=*2,3,4,5**/;

output wire A, B, C, D, E, F, G)

reg (6:0) SEOT;

always 6 (I) begin

case (I)

4 bb001: SEOT = 7*bb110001;

4 bb001: SEOT = 7*bb110001;

4 bb001: SEOT = 7*bb110001;

4 bb001: SEOT = 7*bb11001;

4 bb100: SEOT = 7*bb10010;

4 bb101: SEOT = 7*bb0010;

4 bb101: SEOT = 7*bb10010;

4 bb102: SEOT = 8EOT;

251

```

```

Example: Hexadecimal 7-Segment Decoder

(* Nexadecimal 7-Segment Decoder for 22V10 */

module hexadec(I, A, B, C, D, E, F, G);

input wire [3:0] I (*gyathesis loc="2,3,4,5"*/;

output wire A, B, C, D, E, F, G);

reg [6:0] SEG7;

always @ (I) begin

case (I) SEG7 = "hillilli",

4-holool; SEG7 = "hillilli",

4-holool; SEG7 = "hollinool;

4-holool; SEG7 = "hollinool;

4-holoil; SEG7 = "hollinool;

4-holoil; SEG7 = "hollinool;

4-holoil; SEG7 = "hollinool;

4-hollin; SEG7 = "hollinool;

4-hollin; SEG7 = "hollinool;

4-hollin; SEG7 = "hollinool;

4-hollin; SEG7 = "hollinii;

4-hollin; SEG7 = "hollinii;

4-holool; SEG7 = "holoolin;

4-holool; SEG7 = "holoolin;

4-hollin; SEG7 = "holoolin;

4-hollin; SEG7 = "holoolin;

4-holool; SEG7 = SEG7;

4-holool; SEG7 = SEG7;

4-holool; SEG7 = "holoolin;

4-holool; SEG7 = SEG7;

4-holool; SEG7 = "holoolin;

4-hol

```

```

Example: Hexadecimal 7-Segment Decoder

/* Rexadecimal 7-Segment Decoder for 22V10 */

module hexadec(I, A, B, C, D, E, P, 0);

input wire [3:0] I /*gynthesis loc="2,3,4,5**/;

output wire A, B, C, D, E, F, 0;

reg [6:0] SEGT;

always @ (1) begin

case (1)

4-booloo: SEGT = ?*billiolo;

4-booloo: SEGT = ?*billioloo;

4-booloo: SEGT = SEGT = SEGT;

6-cooloo: SEGT = SEGT = SEGT;

6-cooloo: SEGT = SEGT = SEGT;

6-cooloo: SEGT = SEG

```

Reading Assignment:

DDPP 4th Ed. pp. 408-412, 430-432; 5th Ed. 279-280, 308-310

Learning Objectives:

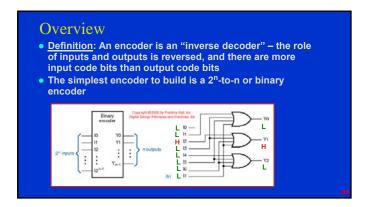

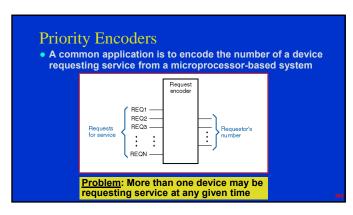

Define the function of an encoder and describe how it can be used as a combinational building block

Discuss why the inputs of an encoder typically need to be prioritized

# Outline Overview Priority Encoders Tri-State Outputs Keypad Encoders

## Priority Encoders • Solution: Assign priority to the input lines, such that when multiple inputs are asserted simultaneously, the highest priority (i.e. highest numbered) input "wins" – such a device is called a priority encoder • An easy way to specify this functionality in Verilog is to use the casez construct • Example: An 8-to-3 encoder with active high inputs and outputs, including a "strobe" output (G) to indicate if any input has been asserted

```

Verilog CASEZ Construct

• use ? as "wild card"

• beware of non-unique expressions – first matching expression wins

casez ({sel,A,B})

3'b00*: Y = 1'b1; 000 or 001 both yield Y = 1'b1

3'b010: Y = 1'b1;

3'b011: Y = 1'b0;

// etc.

endcase

```

```

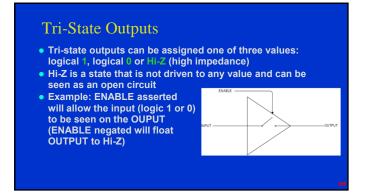

Tri-State Outputs

In Verilog, an output value of 'bZ (high- impedance or Hi-Z) assigned to an output port disables ("floats") the output

tri is a wire type used for tri-state values

Can use the conditional operator?: to implement a tri-state buffer

output tri D_z; input wire D,EN;

assign D_z = EN? D: 1'bZ (ternary operator)

If EN == 1, D_z = D

If EN == 0, D_z=1'bZ (disabled)

Example: Create a Verilog module that implements a 4:2 priority encoder with tri-state encoded outputs (E1, E0). This design should include an active high output strobe (G) that is asserted when any input is asserted

```

```

Example: 4-to-2 Priority Encoder with Tri-State Outputs

/* 4-to-2 Priority Encoder With Tri-State Enable */

module prienc42(I, E_E, G, EN);

input wire [3:0] I; // input 0 - lowest priority,

// input wire 3N; // tri-state enable control input

output wire 3N; // tri-state enable control input

output wire 3N; // tri-state enabled output

output wire 6; // stroke *go* output (high if any input is asserted)

reg [2:0] EG; // EG = {E,G}

always 8 (I) begin

cases (I)

4-bool; EG = 3-bool; // No imputs active

4-bool; EG = 3-bool; // No imputs active

4-bool; EG = 3-bool; // Input 0 wins

4-bool; EG = 3-bool; // Input 1 wins

4-bool; EG = 3-bool; // Input 2 wins

4-bool; EG = 3-bool; // Input 2 wins

4-bool; EG = 3-bool; // Input 3 wins

endcase

end

amsign G = EG[0];

ansign Ex = EN ? EG[2:1] : 2-bxz;

endmodule

```

### Keypad Encoders

- Another common use for encoders is to encode keypads and keyboards

- <u>Example</u>: Design a 10-to-4 priority encoder for encoding a BCD keypad using a 22V10

- <u>Solution</u>: Modify the 8-to-3 priority encoder Verilog file described previously (include tri-state output capability)

Clicker Quiz

```

/* Different Priority Encoder */

module diff_pri(A,B,C,D,E,G);

input wire A, B, C, D;

output wire [1:0] E;

output wire [1:0] E;

output wire G;

reg [2:0] E EG(2:1);

assign G = EG(2:1);

assign G = EG(0);

always @ (A, B, C, D) begin

caser ((A,B,C,D))

4*b0001: EG = 3*b500;

4*b0001: EG = 3*b501;

4*b017: EG = 3*b501;

4*b017: EG = 3*b501;

4*b177: EG = 3*b501;

4*b177:

```

```

1. The highest priority input is:

A. A

B. B

C. C

D. D

E. none of the above

/* Different Priority Encoder */

module diff_pri(A,B,C,D,E,G);

input wire A, B, C, D,

output wire (1:0) B;

output wire G;

reg (2:0) EG;

assign E = EG(2:1);

assign E = EG(2:1);

assign E = EG(2:1);

assign E = EG(2:1);

ES = 3*b000;

4*b0001: EG = 3*b101;

4*b0017: EG = 3*b101;

4*b0177: EG = 3*b001;

endcase

end

endmodule

```

```

3. If input A is asserted, the outputs will be:

A. E1=0, E0=0, G=0

B. E1=0, E0=0, G=1

C. E1=1, E0=1, G=0

D. E1=1, E0=1, G=1

E. none of the above

/* Different Priority Encoder */

module diff_pri(A,B,C,D,E,G);

input wire A, B, C, D;

output wire (1:0) E;

output wire (2:0) Eg;

reg [2:0] Eg;

assign E = EG[2:1];

assign G = EG[0:1];

always @ (A, B, C, D) begin

caser ((A,B,C,D))

4-b0001: EG = 3-b001;

4-b0017: EG = 3-b001;

4-b017: EG = 3-b001;

4-b017: EG = 3-b001;

endcase

end

endmodule

```

```

4. When inputs B and C are asserted simultaneously (and A is negated) the outputs will be:

A. E1=0, E0=0, G=1

B. E1=0, E0=1, G=1

C. E1=1, E0=0, G=1

D. E1=1, E0=1, G=1

E. none of the above

A. E1=0, E0=1, G=1

G. E1=0=0, G=1

G. E1=1, E0=0, G=1

G. E1=1, E0=1, G1

```

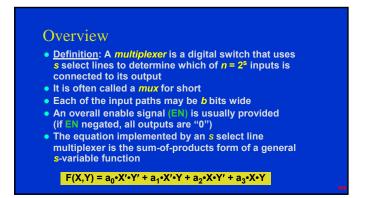

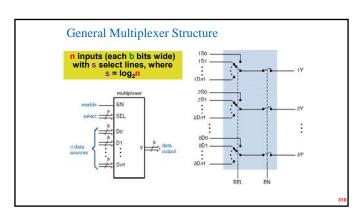

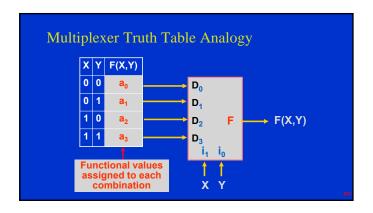

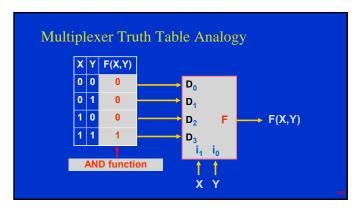

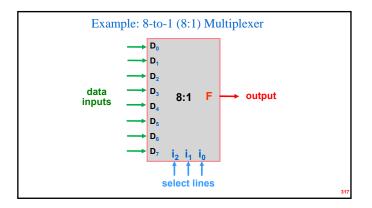

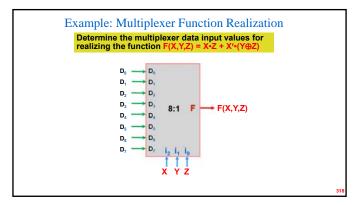

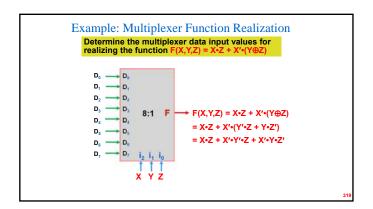

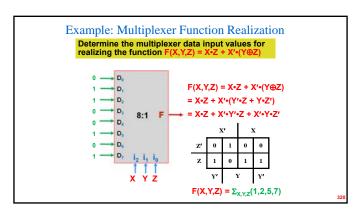

# Outline Overview General multiplexer structure Multiplexer truth table analogy Multiplexer function generation Multiplexers in Verilog

### Multiplexers in Verilog • Multiplexer functionality can be expressed in Verilog in several different ways: using conventional sum-of-products expressions using case structures using if-else constructs or ternary operators • Example: 8-to-1 X 1-bit multiplexer using a 22V10 PLD (conventional SoP) • Example: 4-to-1 X 8-bit multiplexer using a CPLD (two advanced methods)

```

Example: 8 to-1 x 1-bit Multiplexer

/* 8-to-1 x 1-bit Multiplexer Using 22V10 */

module mux811(D, EN, S, Y);

input wire (7:01 D; // Data inputs

input wire (8:01 D; // Pata inputs

input wire (2:01) S; // Select lines

output wire (2:01) S; // Select lines

output wire Y; // Output

assign Y = EN & (-s[2] & -s[1] & -s[0] & D[0] |

-s[2] & -s[1] & s[0] & D[1] |

-s[2] & s[1] & s[0] & D[1] |

-s[2] & s[1] & s[0] & D[1] |

s[2] & -s[1] & s[0] & D[1] |

s[2] & -s[1] & s[0] & D[1] |

s[2] & s[1] & s[2] & s[2

```

```

Example: 4-to-1 x 8-bit Multiplexer - Method 2

/* 4-to-1 x 8-bit Multiplexer Using CPLD */

module mux418b(EN, S, A, B, C, D, Y_x);

input wire EN;

input wire [1:0] S;

input wire [1:0] A, B, C, D;

// 8-bit inputs

input wire [7:0] Y_z;

// 8-bit output buses

output tri [7:0] Y_z;

// 8-bit output bus

reg [7:0] Y;

assign Y_z = EN ? Y : 8'bZZZZZZZZ;

always @ (8) begin

y = 8'b0000000;

came (9)

2'd0: Y = A;

// d stands for decimal

2'd1: Y = B;

2'd2: Y = C;

2'd3: Y = D;

// default: Y = 8'b00000000;

endcase

end

endmodule

```

## Clicker Quiz

```

/* Big Multiplexer */

module bigmux(EN, S, A, B, C, D, Y_Z);

input wire EN;

input wire [1:0] S;

input wire [7:0] A, B, C, D;

output tri [7:0] Y_Z;

wire [7:0] Y;

assign Y_Z = EN ? Y : 8 bZZZZZZZZ;

assign Y = -$[1] & -$[0] & A |

-$[1] & $[0] & B |

$[1] & -$[0] & C |

$[1] & $[0] & D;

endmodule

```

```

1. The number of equations generated by this program (that would be burned into a PLD that realized this design) is:

A. 2

B. 8

C. 9

D. 16

E. none of the above

```

```

2. When EN=0, S[1]=1, and S[0]=1, the output Y_Z:

A. will all be Hi-Z

B. will all be zero

C. will all be one

D. will be equal to the inputs D

E. none of the above

| **Temporaria** | **Tem

```

```

3. When EN=1, S[1]=1, and S[0]=1, the output Y

A. will all be Hi-Z

B. will all be zero

C. will all be one

D. will be equal to the input D

E. none of the above

7 Big Multiplexer */

module bigmux(EN, S, A, B, C, D, Y, E);

input wire [1:0] $;

input wire [1:0] $, B, C, B;

output wire [7:0] Y, E;

wire [7:0] Y,

massign Y = -811 & -8101 & A |

-811 & 8101 & B |

S(1) & -8101 & B |

S(1) & -8

```

### Reading Assignment:

DDPP 4th Ed. pp. 306-308, 5th Ed. 198-201

### **Learning Objectives:**

- Understand the need for using top level (hierarchical) modules

- Understand how top level modules are created in Verilog using structural Verilog syntax

### Outline

- Overview

- Instantiating modules

- Example top level modules

### Overview

- <u>Definition</u>: A top level module is the highest level module in a design hierarchy that instantiates other modules and connects them

- Separating logic across multiple modules serves the advantage of reusability for modules and removing redundant logic

- Example: If two modules use a 4-to-1 mux, create a separate module for the mux, and simply instantiate it in the other modules

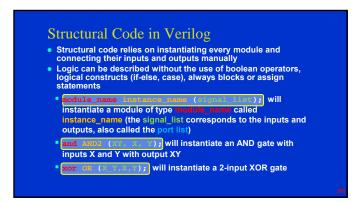

### **Instantiating Modules**

- Follows structural style of instantiation: module\_name instance\_name (signal\_list);

- Signals in signal\_list will be connected in the order of that module's portlist – this is called port mapping by order

- Alternatively, port mapping by name can be used, which is a more error-free method – here, each signal passed to the instantiated module uses the name of the signal in the module's port list to indicate where it is connected

### Example Top Level Modules | module and\_or(A,B,C,D); | input wire A, B; | output wire C, D; | assign C = A & B; | assign D = A \ B; | endmodule | module top\_order(w,x,y,z); | input wire w, x; | output wire

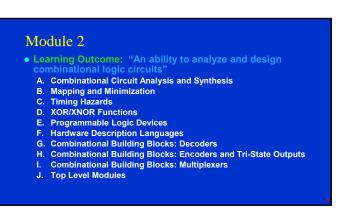

### Module 2 Combinational Logic Circuits

- Learning Outcome: "An ability to analyze and design

- combinational logic circuits

- A. Combinational Circuit Analysis and Synthesis

- B. Mapping and Minimization

- C. Timing Hazards

- D. XOR/XNOR Functions

- E. Programmable Logic DevicesF. Hardware Description Languages

- G. Combinational Building Blocks: Decoders

- H. Combinational Building Blocks: Encoders and Tri-State Outputs

- I. Combinational Building Blocks: Multiplexers

- J. Top Level Modules