#### Lecture Summary – Module 1

Switching Algebra and CMOS Logic Gates

#### Learning Outcome: an ability to analyze and design CMOS logic gates

#### Learning Objectives:

- 1-1. <u>convert</u> numbers from one base (radix) to another: 2, 10, 16

- 1-2. <u>define</u> a binary variable

- 1-3. identify the theorems and postulates of switching algebra

- 1-4. <u>describe</u> the principle of duality

- 1-5. <u>describe</u> how to form a complement function

- 1-6. prove the equivalence of two Boolean expressions using perfect induction

- 1-7. describe the function and utility of basic electronic components (resistors, capacitors, diodes, MOSFETs)

- 1-8. <u>define</u> the switching threshold of a logic gate and identify the voltage ranges typically associated with a "logic high" and a "logic low"

- 1-9. <u>define</u> assertion level and <u>describe</u> the difference between a positive logic convention and a negative logic convention

- 1-10. <u>describe</u> the operation of basic logic gates (NOT, NAND, NOR) constructed using N- and P-channel MOSFETs and <u>draw</u> their circuit diagrams

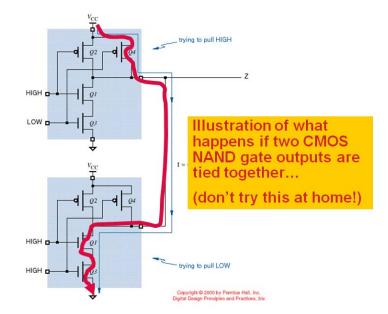

- 1-11. define "fighting" among gate outputs wired together and describe its consequence

- 1-12. <u>define</u> logic gate fan-in and describe the basis for its practical limit

- 1-13. <u>identify</u> key information contained in a logic device data sheet

- 1-14. <u>calculate</u> the DC noise immunity margin of a logic circuit and describe the consequence of an insufficient margin

- 1-15. describe the consequences of a "non-ideal" voltage applied to a logic gate input

- 1-16. describe how unused ("spare") CMOS inputs should be terminated

- 1-17. describe the relationship between logic gate output voltage swing and current sourcing/sinking capability

- 1-18. describe the difference between "DC loads" and "CMOS loads"

- 1-19. <u>calculate</u> V<sub>OL</sub> and V<sub>OH</sub> of a logic gate based on the "on" resistance of the active device and the amount of current sourced/sunk by the gate output

- 1-20. <u>calculate</u> logic gate fan-out and identify a practical lower limit

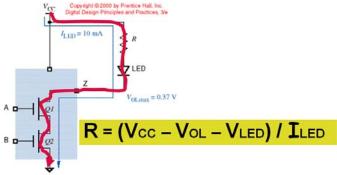

- 1-21. <u>calculate</u> the value of current limiting resistor needed for driving an LED

- 1-22. describe the deleterious effects associated with loading a gate output beyond its rated specifications

- 1-23. define propagation delay and list the factors that contribute to it

- 1-24. <u>define</u> transition time and list the factors that contribute to it

- 1-25. <u>estimate</u> the transition time of a CMOS gate output based on the "on" resistance of the active device and the capacitive load

- 1-26. describe ways in which load capacitance can be minimized

- 1-27. identify sources of dynamic power dissipation

- 1-28. <u>plot</u> power dissipation of CMOS logic circuits as a function of operating frequency

- 1-29. plot power dissipation of CMOS logic circuits as a function of power supply voltage

- 1-30. describe the function and utility of decoupling capacitors

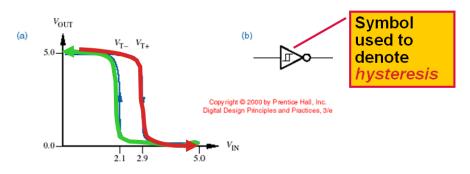

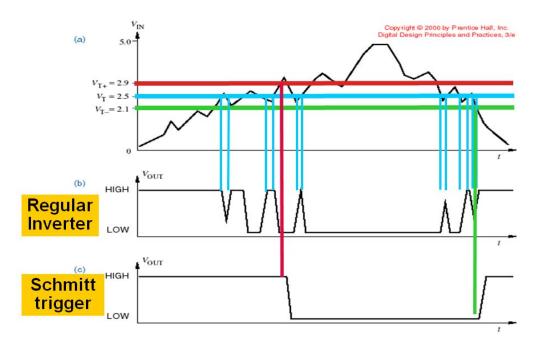

- 1-31. define hysteresis and describe the operation of Schmitt-trigger inputs

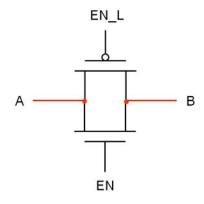

- 1-32. <u>describe</u> the operation and utility of a transmission gate

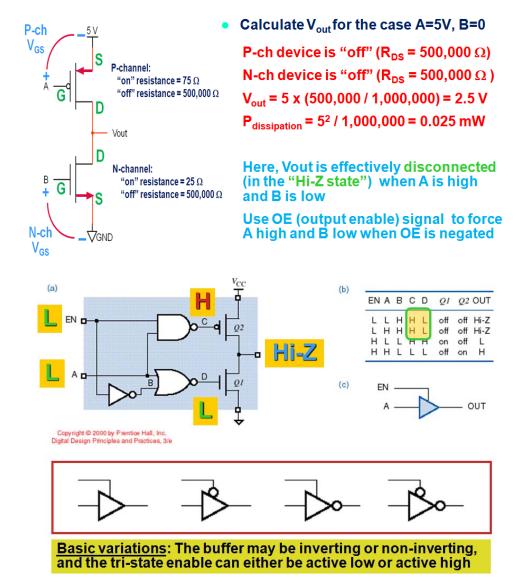

- 1-33. define high-impedance state and describe the operation of a tri-state buffer

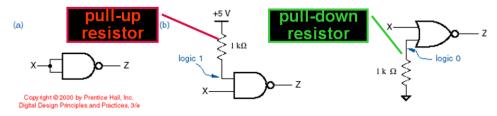

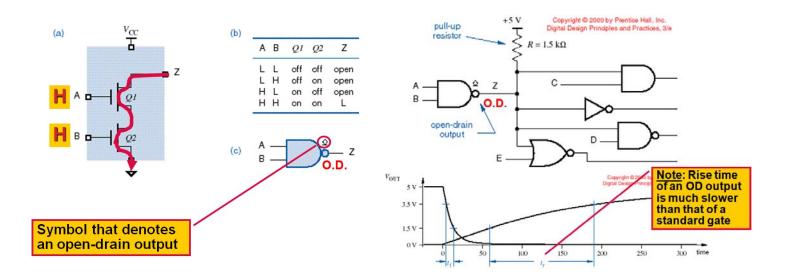

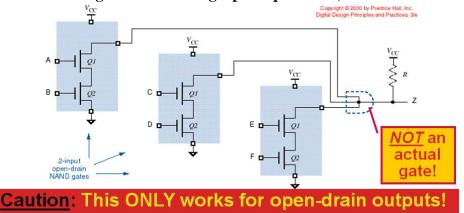

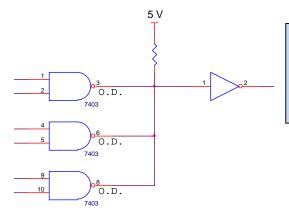

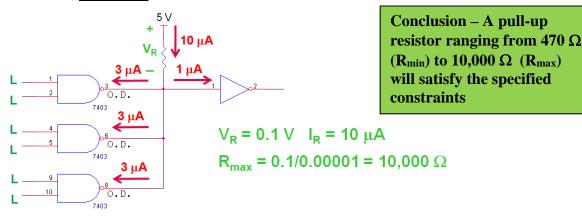

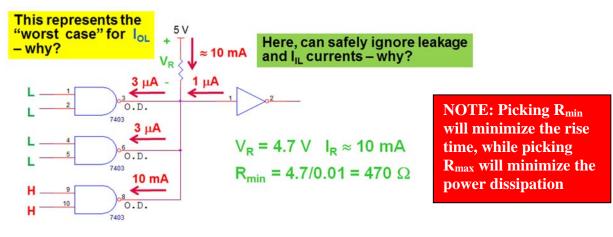

- 1-34. define open drain as it applies to a CMOS logic gate output and calculate the value of pull-up resistor needed

- 1-35. describe how to create "wired logic" functions using open drain logic gates

- 1-36. calculate the value of pull-up resistor needed for an open drain logic gate

#### Lecture Summary – Module 1-A

Number Systems

Reference: Digital Design Principles and Practices 4th Ed. pp. 25-34, 5th Ed. pp. 35-44

- overview

- $\circ$  d<sub>n</sub> digits of base R number

- $\circ$  c<sub>n</sub> converted corresponding digits in base 10

- $\circ$  dealing with *unsigned* numbers only at this point  $\rightarrow$  leading zeroes don't matter

- table of correspondence

| N <sub>2</sub> | N <sub>3</sub> | N <sub>4</sub> | $N_5$ | $N_6$ | N <sub>7</sub> | N <sub>8</sub> | N <sub>9</sub> | N <sub>10</sub> | N <sub>16</sub> |

|----------------|----------------|----------------|-------|-------|----------------|----------------|----------------|-----------------|-----------------|

| 0              | 0              | 0              | 0     | 0     | 0              | 0              | 0              | 0               | 0               |

| 1              | 1              | 1              | 1     | 1     | 1              | 1              | 1              | 1               | 1               |

| 10             | 2              | 2              | 2     | 2     | 2              | 2              | 2              | 2               | 2               |

| 11             | 10             | 3              | 3     | 3     | 3              | 3              | 3              | 3               | 3               |

| 100            | 11             | 10             | 4     | 4     | 4              | 4              | 4              | 4               | 4               |

| 101            | 12             | 11             | 10    | 5     | 5              | 5              | 5              | 5               | 5               |

| 110            | 20             | 12             | 11    | 10    | 6              | 6              | 6              | 6               | 6               |

| 111            | 21             | 13             | 12    | 11    | 10             | 7              | 7              | 7               | 7               |

| 1000           | 22             | 20             | 13    | 12    | 11             | 10             | 8              | 8               | 8               |

| 1001           | 100            | 21             | 14    | 13    | 12             | 11             | 10             | 9               | 9               |

| 1010           | 101            | 22             | 20    | 14    | 13             | 12             | 11             | 10              | Α               |

| 1011           | 102            | 23             | 21    | 15    | 14             | 13             | 12             | 11              | в               |

| 1100           | 110            | 30             | 22    | 20    | 15             | 14             | 13             | 12              | С               |

| 1101           | 111            | 31             | 23    | 21    | 16             | 15             | 14             | 13              | D               |

| 1110           | 112            | 32             | 24    | 22    | 20             | 16             | 15             | 14              | E               |

| 1111           | 120            | 33             | 30    | 23    | 21             | 17             | 16             | 15              | F               |

| 10000          | 121            | 100            | 31    | 24    | 22             | 20             | 17             | 16              | 10              |

- integer conversion: base R to base 10

- method: iterative multiply and add

- o based on nested expression of a number

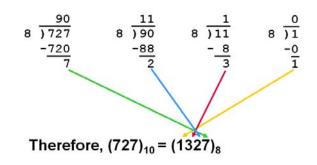

- integer conversion: base 10 to base R

- method: iterative division

- remainders become digits of converted number

- quotient of zero indicates conversion is complete

#### Example: Convert (727)<sub>10</sub> to base 8

$$(d_{3}d_{2}d_{1}d_{0})_{R} = (N)_{10}$$

=  $c_{3}xR^{3} + c_{2}xR^{2} + c_{1}xR^{1} + c_{0}xR^{0}$

=  $(((c_{3}xR + c_{2})xR + c_{1})xR + c_{0})$

Example: Convert (4352)<sub>8</sub> to base 10

$4 \times 8 + 3 = 35$   $35 \times 8 + 5 = 285$   $285 \times 8 + 2 = 2282$ Therefore,  $(4352)_8 = (2282)_{10}$

- short cut for conversion among powers of 2 (from base "A" to base "B")

- method: size log<sub>2</sub>R groupings

- write an n-digit binary number for each base A digit in the original number, where n  $= \log_2 A$

- $\circ$  starting at the least significant position, form m-digit groups, where m =  $\log_2 B$

Example: Convert (136)<sub>8</sub> to base 2 and base 16

| 1    | 3   | 6    |

|------|-----|------|

| 001  | 011 | 110  |

| 0101 |     | 1110 |

| 5    |     | E    |

Therefore,  $(136)_8 = (1011110)_2 = (5E)_{16}$

Exercise: Convert (110101)<sub>2</sub> to bases 8 and 16

| 6    | 5    |

|------|------|

| 110  | 101  |

| 110  | 101  |

| 0011 | 0101 |

| 3    | 5    |

Therefore,  $(110101)_2 = (\underline{65})_8 = (\underline{35})_{16}$

#### Lecture Summary – Module 1-B

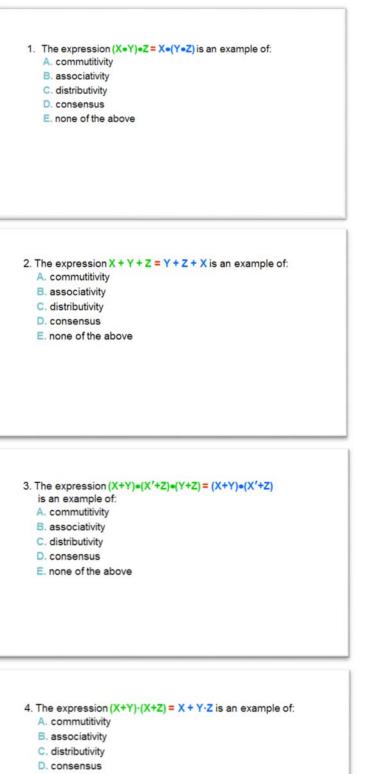

Switching Algebra

Reference: Digital Design Principles and Practices 4th Ed. pp. 183-199, 5th Ed. pp. 89-105

- overview

- formal analysis techniques for digital circuits are based on a two-valued algebraic system called *Boolean algebra* (named after George Boole, who invented it in 1854); Claude Shannon (1938) showed how to adapt Boolean algebra to analyze and describe the behavior of circuits built from relays

- <u>definition</u>: the *axioms* (or *postulates*) of a mathematical system are a minimal set of basic definitions that we assume to be true, from which all other information about the system can be derived

- <u>notation</u>: a *prime* (') will be used to denote an inverter's function (i.e., the *complement* of a logic signal) note that *prime* is an *algebraic operator*, that X' is an *expression*, and that Y=X' is an *equation*

- <u>definition</u>: a *binary variable*, X, is a two-valued quantity such that:

- if  $X \neq 1$ , then X = 0

- if  $X \neq 0$ , then X = 1

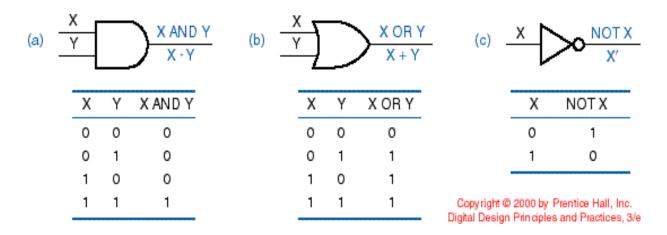

- <u>definition</u>: the function of a 2-input AND gate is called *logical multiplication* and is symbolized by a *multiplication dot* (•)

- <u>definition</u>: the function of a 2-input OR gate is called *logical addition* and is symbolized algebraically by a *plus sign* (+)

- <u>convention</u>: Multiplication (AND) has *implied precedence* over addition (OR)

- five axioms completely define switching algebra (note that the second axiom in each pair is referred to as the *dual* of the first one)

| $\succ  (A1)  X = 0  \text{if } X \neq 1$ | $(A1^{D}) X = 1 \text{ if } X \neq 0$      |

|-------------------------------------------|--------------------------------------------|

| ➤ (A2) if X = 0, then X' = 1              | > (A2 <sup>D</sup> ) if X = 1, then X' = 0 |

| > (A3) $0 \cdot 0 = 0$                    |                                            |

| > (A4) $1 \cdot 1 = 1$                    | > $(A4^{D}) 0 + 0 = 0$                     |

| > (A5) $0 \cdot 1 = 1 \cdot 0 = 0$        | > $(A5^{D})$ $1 + 0 = 0 + 1 = 1$           |

- duality

- <u>definition</u>: the *dual* of an expression is formed through the simultaneous interchange of the operators "·" and "+" and the elements "0" and "1"

- <u>important principle</u>: if two Boolean expressions can be proven to be equivalent using a given sequence of axioms or theorems, then the *dual expressions* may be proven to be equivalent by simply applying the sequence of *dual* axioms or theorems

- basic logic gates ("Boolean's Big Three")

- AND produces a 1 output iff all its inputs are 1

- OR produces a 1 output if one or more of its inputs are 1

- NOT (inverter) produces an output value that is the opposite of its input value

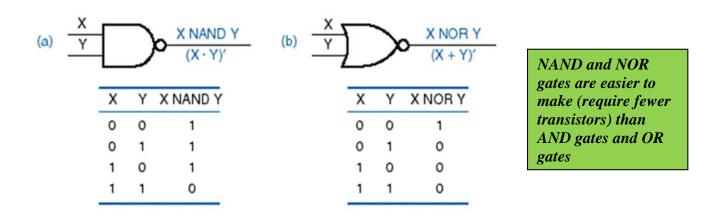

- other basic gates (more commonly used)

- NAND ("Not AND") produces the opposite of an AND gate's output

- NOR ("Not OR") produces the opposite of an OR gate's output

• logical completeness: "anything digital" can be built using solely AND, OR, and NOT gates -or- solely using NAND gates -or- solely using NOR gates

- theorems

- <u>definition</u>: switching algebra *theorems* are statements, known always to be true, that allow manipulation of algebraic expressions

- <u>definition</u>: a technique called *perfect induction* can be used to prove switching algebra theorems ("perfect" implies the use of *all possible combinations* of the values of the variables – thus, it is an *exhaustive* type of proof)

- o single-variable theorems

|   | (T4) (X')' = X                                       |                                                              | Involution         |

|---|------------------------------------------------------|--------------------------------------------------------------|--------------------|

| • | $(\mathbf{T3}) \mathbf{X} + \mathbf{X} = \mathbf{X}$ | $(\mathbf{T3^{D}}) \mathbf{X} \cdot \mathbf{X} = \mathbf{X}$ | <b>Idempotency</b> |

| • | (T2) X + 1 = 1                                       | $(\mathbf{T2^{D}}) \mathbf{X} \cdot 0 = 0$                   | Null elements      |

| • | (T1) $X + 0 = X$                                     | $(\mathbf{T}1^{\mathbf{D}}) \mathbf{X} \cdot 1 = \mathbf{X}$ | <b>Identities</b>  |

- (T5) X + X' = 1 (T5<sup>D</sup>)  $X \cdot X' = 0$  Complements

- two- and three-variable theorems

- (T6) **X** + **Y** = **Y** + **X** *Commutivity*

- $(\mathbf{T6^{D}}) \mathbf{X} \cdot \mathbf{Y} = \mathbf{Y} \cdot \mathbf{X}$

- (T7) (X + Y) + Z = X + (Y + Z) Associativity (T7<sup>D</sup>)  $(X \cdot Y) \cdot Z = X \cdot (Y \cdot Z)$

- (T8)  $X \cdot Y + X \cdot Z = X \cdot (Y + Z)$ (T8<sup>D</sup>)  $(X + Y) \cdot (X + Z) = X + Y \cdot Z$

- (T9)  $X + X \cdot Y = X$ (T9<sup>D</sup>)  $X \cdot (X + Y) = X$

- (T10)  $X \cdot Y + X \cdot Y' = X$  Combining (T10<sup>D</sup>)  $(X + Y) \cdot (X + Y') = X$

- <u>Note</u>: In all theorems, it is possible to replace each variable with an arbitrary logic expression

- (T11)  $\mathbf{X} \cdot \mathbf{Y} + \mathbf{X'} \cdot \mathbf{Z} + \mathbf{Y} \cdot \mathbf{Z} = \mathbf{X} \cdot \mathbf{Y} + \mathbf{X'} \cdot \mathbf{Z}$  Consensus

- $(T11^{D}) (X + Y) \cdot (X' + Z) \cdot (Y + Z) = (X + Y) \cdot (X' + Z)$

- <u>example</u>: proof of T8<sup>D</sup> using perfect induction

| XYZ | Y•Z | $X + Y \bullet Z$ | X + Y | X + Z | (X+Y)•(X+Z) |

|-----|-----|-------------------|-------|-------|-------------|

| 000 | 0   | 0                 | 0     | 0     | 0           |

| 001 | 0   | 0                 | 0     | 1     | 0           |

| 010 | 0   | 0                 | 1     | 0     | 0           |

| 011 | 1   | 1                 | 1     | 1     | 1           |

| 100 | 0   | 1                 | 1     | 1     | 1           |

| 101 | 0   | 1                 | 1     | 1     | 1           |

| 110 | 0   | 1                 | 1     | 1     | 1           |

| 111 | 1   | 1                 | 1     | 1     | 1           |

|     |     | r.h.              |       |       | l.h.s.      |

<u>example</u>: proof of T9 using other theorems

(T9)

$$\mathbf{X} + \mathbf{X} \cdot \mathbf{Y} = \mathbf{X} \cdot \mathbf{1} + \mathbf{X} \cdot \mathbf{Y}$$

(T1<sup>D</sup>)

=  $\mathbf{X} \cdot (\mathbf{1} + \mathbf{Y})$  (T8)

=  $\mathbf{X} \cdot \mathbf{1}$  (T2)

=  $\mathbf{X}$  (T1<sup>D</sup>)

• <u>example</u>: verify the following equivalence relationship

$$X \cdot Y + Y \cdot Z + X' \cdot Z = X \cdot Y + Y \cdot Z \cdot (X + X') + X' \cdot Z$$

= X \cdot Y + X \cdot Y \cdot Z + X' \cdot Y \cdot Z + X' \cdot Z

= X \cdot Y \cdot (1 + Z) + X' \cdot Z \cdot (Y + 1)

= X \cdot Y + X' \cdot Z

- n-variable theorems

- (T12) X + X + ... + X = X(T12<sup>D</sup>)  $X \cdot X \cdot ... \cdot X = X$

- (T13)  $(X1 \cdot X2 \cdot ... \cdot Xn)' = X1' + X2' + ... + Xn'$  DeMorgan's Law (T13<sup>D</sup>)  $(X1 + X2 + ... + Xn)' = X1' \cdot X2' \cdot ... \cdot Xn'$

- (T14)  $[F(X1,X2,...,Xn)]' = F^{D}(X1',X2',...,Xn')$  Generalized DeMorgan's Law

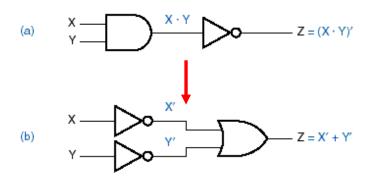

- equivalent circuits based on DeMorgan's law (T13)

$(\mathbf{X} \cdot \mathbf{Y})' = \mathbf{X}' + \mathbf{Y}'$

observation: a *logically equivalent circuit* can be formed by taking the *dual* of the operator(s) <u>and</u> *complementing* all the inputs and outputs

(c)

$$X$$

(c)  $Y$

(d)  $X$

(c)  $X$

(c)  $Z = (X \cdot Y)'$

(c)  $Z = X' + Y'$

E. none of the above

#### Lecture Summary – Module 1-C Basic Electronic Components and Concepts

**Reference:** *DDPP* supplement "Appendix B: Electrical Circuits Review" (link on References page)

- voltage difference in electrical potential, expressed in volts

- **current** the flow of charge in a conductor between two points having a difference in potential, expressed in *amperes* (amps)

- **resistor** a device that limits the amount of current flowing through a circuit, measured in *ohms* (Ω)

- resistance is also referred to as *impedance* (inverse of impedance is *admittance*)

- $\circ$  fundamental relationship: the voltage drop (V<sub>R</sub>) across a resistor is equal to the product of the current flowing through it (I<sub>R</sub>) and the value of the resistance (R)

- $\circ \quad Ohm's \ Law \ \mathbf{V} = \mathbf{I} \times \mathbf{R}$

- resistors in series:  $\mathbf{R}_{\mathrm{T}} = \mathbf{R}_1 + \mathbf{R}_2 + \mathbf{R}_3$  -

- resistors in parallel:  $1/R_T = 1/R_1 + 1/R_2 + 1/R_3$

- potentiometer (variable resistor/voltage divider):

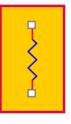

- Kirchhoff's Current Law (KCL) sum of currents at any node is zero (based on conservation of electric charge)

- **power** amount of energy, expressed in *watts*, typically calculated as the product of the *voltage* drop across a device and the *current* flowing through it

| $\circ  \mathbf{P} = \mathbf{V} \times \mathbf{I}$   | based on Ohm's Law                          |

|------------------------------------------------------|---------------------------------------------|

| $\circ \mathbf{P} = \mathbf{V}^2 / \mathbf{R}$       | substitutions:                              |

|                                                      | I = V / R                                   |

| $\circ  \mathbf{P} = \mathbf{I}^2 \times \mathbf{R}$ | $\mathbf{V} = \mathbf{I} \times \mathbf{R}$ |

V<sub>B</sub>

Vp

$V_{A} + V_{B} + V_{C} + V_{D} = 0$

$\mathbf{I}_{A} + \mathbf{I}_{B} + \mathbf{I}_{C} = \mathbf{0}$

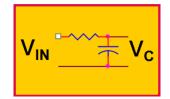

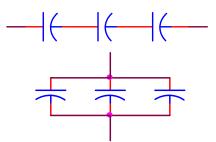

- capacitor a device that stores an electric charge, measured in *farads* (F)

- a resistor-capacitor (RC) network charges and discharges exponentially

- the voltage across a capacitor cannot change instantaneously

- the product of R and C is called the RC time constant

- $\circ \quad \mathbf{V}_{\mathbf{C}} = \mathbf{V}_{\mathbf{I}\mathbf{N}} \times (\mathbf{1} \mathbf{e}^{-t/\mathbf{R}\mathbf{C}})$

- capacitors in series:  $1/C_T = 1/C_1 + 1/C_2 + 1/C_3$

- capacitors in parallel:  $C_T = C_1 + C_2 + C_3$

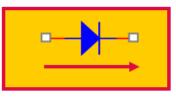

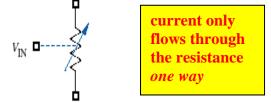

- **diode** a device that restricts the flow of current to a single direction (from its *anode* to its *cathode*)

- a diode through which current is flowing (because the voltage at the anode is greater than at the cathode) is *forward biased*

- if current is not flowing through a diode (because the voltage at the cathode is greater than at the anode), the diode is *reverse biased*

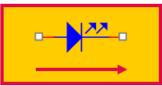

- light emitting diode (LED) a diode that emits visible (red/yellow/green/blue/white) or invisible (infrared) light when forwarded biased

- the brightness of an LED is proportional to the amount of current flowing through it (called the *forward current*)

- a *resistor* is placed in series with an LED to limit the amount of current flowing through it

- the voltage drop across an LED when it is forward biased is called the *forward voltage*

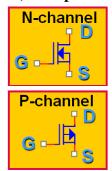

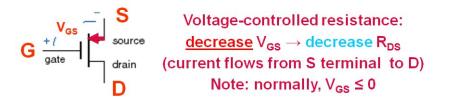

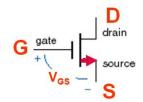

- field effect transistor (FET) a 3-terminal device (G-gate, S-source, D-drain) that provides a voltage-controlled *impedance*

- N-channel: *high* potential on G (gate) relative to S (source) causes transistor to turn on (low impedance between S and D terminals)

- P-channel: *low* potential on G (gate) relative to S (source) causes transistor to turn on

- o can be used as a voltage-controlled switch

Voltage-controlled resistance: increase  $V_{GS} \rightarrow decrease R_{DS}$ Note: normally,  $V_{GS} \ge 0$ N-channel MOSFET +  $V_{GS}$ S As  $R_{DS}$  decreases, power delivered to load ( $R_L$ ) increases

#### Lecture Summary – Module 1-D

Logic Signals and CMOS Logic Circuits

**Reference:** Digital Design Principles and Practices 4<sup>th</sup> Ed. pp. 79-96, 141-148; 5<sup>th</sup> Ed. pp. 8-25, 790-796

- overview

- a logic value, 0 or 1, is often referred to as a *binary digit* or *bit*

- o "LOW" and "HIGH" are often used in place of "0" and "1" to refer to *logic signals*

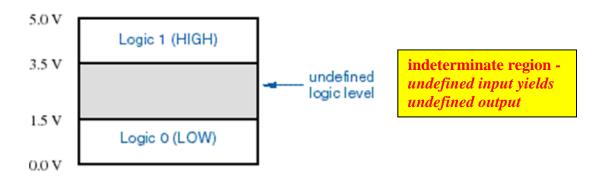

- LOW a signal in the range of "lower" voltages (e.g., 0 1.5 volts for 5V CMOS logic), which is interpreted as a logic 0

- HIGH a signal in the range of "higher" voltages (e.g., 3.5 5.0 volts for 5V CMOS logic), which is interpreted as a logic 1

- the *assignment* of 0 and 1 to LOW and HIGH, respectively, is referred to as a *positive logic convention* (or simply "positive logic")

- a positive logic signal that is *asserted* is in the HIGH state, and is therefore referred to as an "active high" signal

- a positive logic signal that is *negated* is in the LOW state

- the opposite assignment (1 to LOW and 0 to HIGH) is referred to as a negative logic convention (or "negative logic")

- a negative logic signal that is *asserted* is in the LOW state, and is therefore referred to as an "active low" signal

- a negative logic signal that is *negated* is in the HIGH state

- logic families

- complementary metal oxide semiconductor (CMOS) logic is both the most capable and the easiest to understand commercial digital logic technology, and accounts for the vast majority of the worldwide integrated circuit (IC) market

- 5-volt CMOS logic levels (other operating voltage ranges proportioned accordingly)

- MOS field effect transistor (MOSFET)

- modeled as a 3-terminal device that acts like a voltage-controlled resistance

- in digital logic applications, MOSFETs are operated so that their resistance is either very high (transistor is "off") or very low (transistor is "on")

- P-channel MOS (PMOS)

N-channel MOS (NMOS)

Voltage-controlled resistance: increase  $V_{GS} \rightarrow decrease R_{DS}$ (current flows from D terminal to S) Note: normally,  $V_{GS} \ge 0$

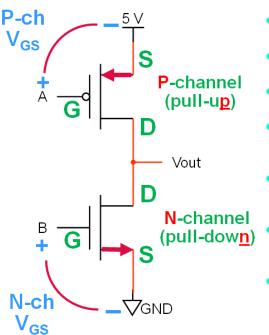

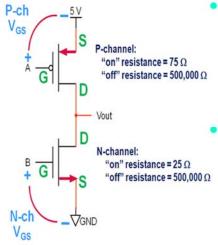

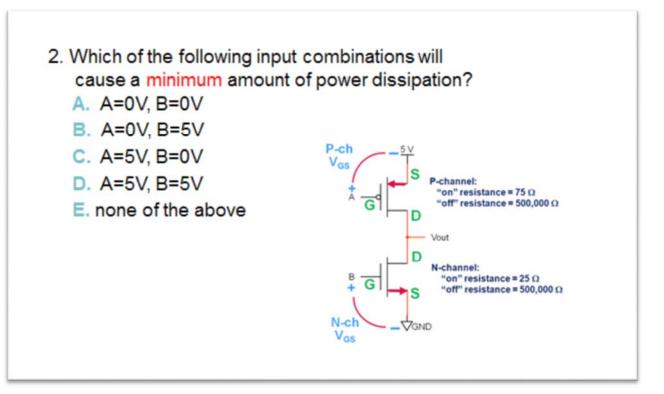

basic CMOS logic circuit

- The S terminal of the P-ch MOSFET is connected to 5 V

- The S terminal of the N-ch MOSFET is connected to GND

- The D terminals of both MOSFETs are connected to the output (Vout)

- The direction of current flow in the P-ch device is from the S terminal to the D terminal ("sources" current)

- The direction of current flow in the N-ch device is from the D terminal to the S terminal ("sinks" current)

- A high voltage on the G terminal of the N-ch MOSFET (relative to GND) turns it on

- A low voltage on the G terminal of the P-ch MOSFET (relative to 5 V) turns it on

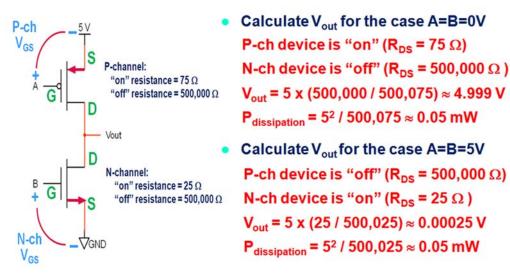

• <u>example</u>: inverter operation (very low power dissipation, very low voltage drop across "on" device under "no load" conditions)

<u>example</u>: "non-inverter" operation (Q: what would you call each of these cases?)

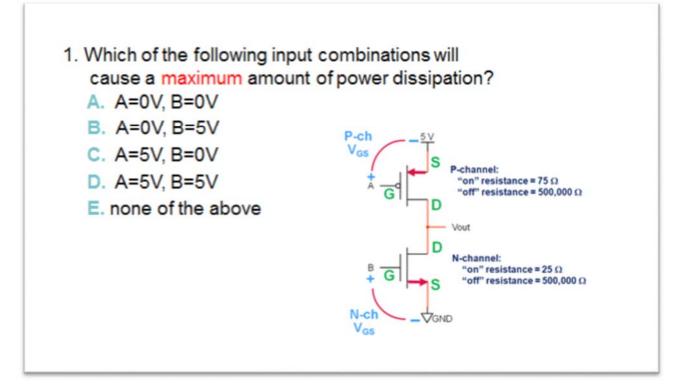

- Calculate  $V_{out}$  for the case A=0, B=5 V P-ch device is "on" ( $R_{DS} = 75 \Omega$ ) N-ch device is "on" ( $R_{DS} = 25 \Omega$ )  $V_{out} = 5 \times (25 / 100) = 1.25 V$  $P_{dissipation} = 5^2 / 100 = 250 \text{ mW}$

- Calculate V<sub>out</sub> for the case A=5V, B=0 P-ch device is "off" (R<sub>DS</sub> = 500,000 Ω)

N-ch device is "off" (R<sub>DS</sub> = 500,000 Ω)

V<sub>out</sub> = 5 x (500,000 / 1,000,000) = 2.5 V P<sub>dissipation</sub> = 5<sup>2</sup> / 1,000,000 = 0.025 mW

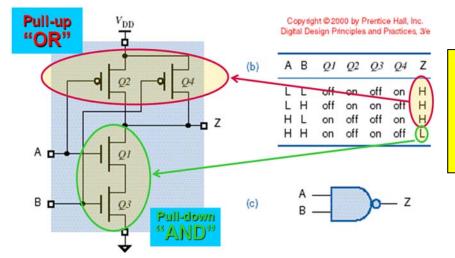

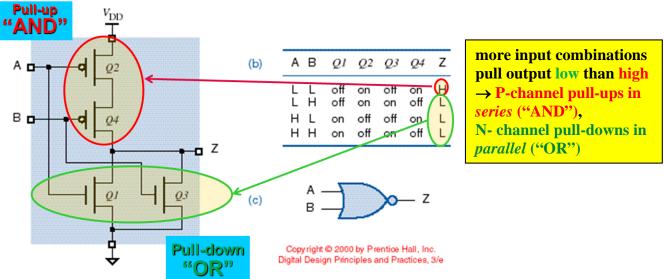

- basic CMOS NAND gate

more input combinations pull output high than low → P-channel pull-ups in parallel ("OR"), N-channel pull-downs in series ("AND")

• fighting!

• basic CMOS NOR gate

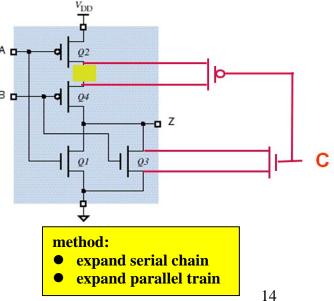

- fan-in

- <u>definition</u>: the number of inputs a gate can have in a particular logic family is called the <sup>A</sup> <sup>D</sup> logic family's *fan-in*

- CMOS gates with more than two inputs can be <sup>B</sup> obtained by extending the "series-parallel" circuit designs (e.g., for NAND and NOR gates) illustrated previously

- in practice, the additive "on" resistance of series transistors limits the fan-in of CMOS gates to a relatively small number

- <u>example</u>: expand fan-in of 2-input NOR gate to 3 inputs

#### Lecture Summary – Module 1-E Logic Levels and Noise Margins

**Reference:** Digital Design Principles and Practices 4<sup>th</sup> Ed. pp. 96-103, 5<sup>th</sup> Ed. pp. 745-753

- overview

- objective: to be able to design *real* circuits using CMOS or other logic families design 0 margins

- need to ensure that the "digital abstraction" is valid for a given circuit

- need to provide adequate engineering *design margins* to ensure that a circuit will work properly under a variety of conditions

- need to be able to read and understand data sheets and specifications, in order to create reliable and robust real-world circuits and systems

- o noise

- the main reason for providing engineering design margins is to ensure proper operation in the presence of *noise*

VOUT .

- examples of noise sources:

- cosmic rays

- magnetic fields generated by machinery •

- power supply disturbances

- the "switching action" of the logic circuits themselves

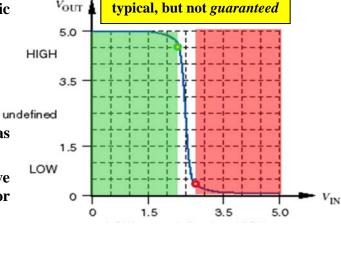

- CMOS inverter input/output transfer characteristic

- factors that cause the transfer characteristic to varv

- power supply voltage

- temperature

- output loading

- conditions under which a device was fabricated

- o sound engineering practice dictates that we use more "conservative" specifications for LOW and HIGH

- input/output voltage definitions

- V<sub>OHmin</sub> the minimum output voltage in the HIGH state

- V<sub>IHmin</sub> the minimum input voltage guaranteed to be recognized as a HIGH

- V<sub>ILmax</sub> the maximum input voltage guaranteed to be recognized as a LOW

- V<sub>OLmax</sub> the maximum output voltage in the LOW state

- DC noise margin

- definition: a measure of how much noise it takes to *corrupt* a worst-case output voltage into a value that may not be recognized properly by an input

- calculation of DC noise margin (or the "noise immunity margin")

- HC family (5-volt) CMOS data sheet

| ym.             | Parameter             | Test                                                  | Conditions <sup>1)</sup> | Min. | Тур.(2) | Max. | Unit |

|-----------------|-----------------------|-------------------------------------------------------|--------------------------|------|---------|------|------|

| V <sub>IH</sub> | Input HIGH level      | Guaranteed logic                                      | 3.15                     | -    | -       | V    |      |

| V <sub>IL</sub> | Input LOW level       | Guaranteed logic                                      | 12                       | -    | 1.35    | V    |      |

| I <sub>IH</sub> | Input HIGH current    | $V_{\rm CC} = Max., V_{\rm I}$                        | —                        | —    | 1       | μΑ   |      |

| IIL             | Input LOW current     | $V_{\rm CC} = Max., V_{\rm I}$                        |                          | -    | -1      | μΑ   |      |

| V <sub>IK</sub> | Clamp diode voltage   | $V_{\rm CC} = { m Min., I_{ m N}} =$                  | -                        | -0.7 | -1.2    | V    |      |

| IOS             | Short-circuit current | $V_{\rm CC} = {\rm Max.},^{(3)}$                      | -                        | -    | -35     | mA   |      |

| ,               | Output HIGH voltage   | $V_{\rm CC} = Min.,$                                  | $I_{OH} = -20 \ \mu A$   | 4.4  | 4.499   |      | V    |

| он              | Output mon voitage    | $V_{\rm IN} = V_{\rm IL}$                             | $I_{OH} = -4 \text{ mA}$ | 3.84 | 4.3     | 0    | V    |

| v               | Output LOW voltage    | $V_{\rm CC} = Min.$                                   | I <sub>OL</sub> = 20 μA  | -    | .001    | 0.1  | V    |

| VOL.            | Output LOW voltage    | $V_{\rm IN} = V_{\rm IH}$ $I_{\rm OL} = 4 \text{ mA}$ |                          |      | 0.17    | 0.33 |      |

For HC family (5-volt) CMOS:

DCNM = min (4.4 - 3.15, 1.35 - 0.1)= 1.25 v

Q: Is a DCNM of 1.25 V "good" or "bad"?

#### • other gate input considerations

• if the inputs to a CMOS circuit are not close to the Vcc / GND rails, the "on" transistor may not be *fully on* and the "off" transistor may not be *fully off* – causing power dissipation of the device to *increase*

• unused ("spare") CMOS inputs should *never* be left unconnected ("floating") – a small amount of circuit noise can temporarily make a floating input look HIGH (solution: tie unused inputs high or low using a pull-up or pull-down resistor, respectively)

• CMOS device inputs are subject to damage from electrostatic discharge (ESD) – touch a source of earth ground before handling static sensitive devices or circuit boards that contain them

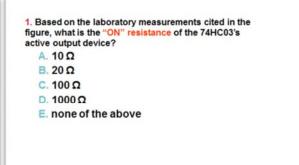

#### 1. For CMOS gates, V<sub>IHmin</sub> is typically:

- A. 10% of the supply voltage (Vcc)

- B. 30% of the supply voltage (Vcc)

- C. 50% of the supply voltage (Vcc)

- D. 70% of the supply voltage (Vcc)

- E. 90% of the supply voltage (Vcc)

## 2. For CMOS gates, the *switching threshold* is typically:

- A. 10% of the supply voltage (Vcc)

- B. 30% of the supply voltage (Vcc)

- C. 50% of the supply voltage (Vcc)

- D. 70% of the supply voltage (Vcc)

- E. 90% of the supply voltage (Vcc)

# If a CMOS gate input voltage is 50% of its V<sub>cc</sub> (supply) voltage, then: A. the logic gate will dissipate *less* power than it would if the input was 1% of its power supply voltage B. the logic gate will dissipate *less* power than it would if the input was 99% of its power supply voltage

- C the logic gate will dissipate *more* power than it would if the input was *either* 1% or 99% of its power supply voltage

- D.the logic gate will dissipate no power

- E none of the above

#### Lecture Summary – Module 1-F Current Sourcing and Sinking

Reference: Digital Design Principles and Practices 4th Ed. pp. 103-114, 5th Ed. pp. 753-764

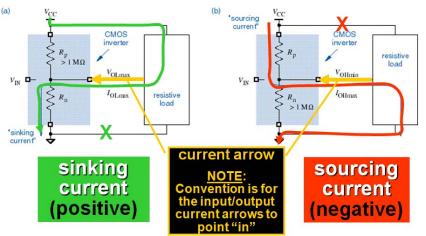

#### • sourcing and sinking current

- CMOS gate inputs have a very high impedance and consume *very little current* (about 1 microamp) from the circuits that drive them

- I<sub>IL</sub> maximum current that flows into the input in the LOW state

- **I**<sub>IH</sub> maximum current that flows into the input in the HIGH state

- IC manufacturers specify a maximum load for the output in each state (HIGH or LOW) and guarantee a worst-case output voltage for that load

- I<sub>OL</sub> maximum current that the output can "sink" in the LOW state while still maintaining an output voltage *no greater than* V<sub>OLmax</sub>

- I<sub>OH</sub> maximum current that the output can "source" in the HIGH state while still maintaining an output voltage *no less than* V<sub>OHmin</sub>

- sourcing/sinking sign convention

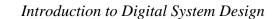

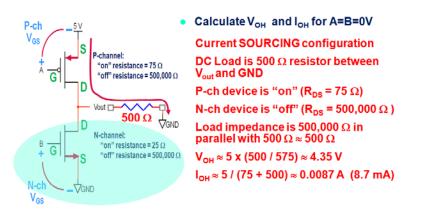

- "CMOS loads" vs. "DC loads"

- often times gate outputs need to drive devices that require a non-trivial amount of current to operate called a *resistive* load or *DC* load

- when driving a resistive load, the output of a CMOS circuit is not nearly as *ideal* as described previously (the output voltage swing may significantly degrade)

- in either output state, the CMOS output transistor that is "on" has a non-zero resistance, and a load connected to its output terminal will cause a voltage drop across this resistance

- consequently, most CMOS devices have two sets of loading specifications:

- "CMOS loads" device output connected to other CMOS inputs, which require very little current to recognize a "high" input or "low" input

- "DC loads" device output connected to resistive loads (devices that consume significant current, typically several milliamps)

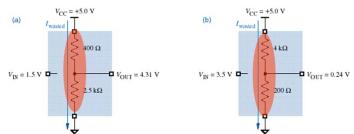

- example: inverter current sourcing (DC load)

#### In the current SOURCING configuration, the inverter output is active high ("asserted high"); the N-channel pull-down virtually "disappears"

#### • example: inverter – current sinking (DC load)

- fan-out

- <u>definition</u>: the number of gate inputs that a gate output can drive *without exceeding* its worst-case loading specifications

- o depends on characteristics of both the output device and the inputs being driven

- o must be examined for both the "sourcing" and "sinking" cases

- limitations due to capacitive loading (impact on rise/fall times may be more of a limiting factor than fan-out or DCNM)

- o "practical" fan-out is the minimum of the HIGH- and LOW-state fan-outs

| Sym.              | Parameter                         | Test                                                      | Conditions <sup>(1)</sup>    | Min. | Тур.(2) | Max. | Unit |

|-------------------|-----------------------------------|-----------------------------------------------------------|------------------------------|------|---------|------|------|

| $V_{\mathrm{IH}}$ | Input HIGH level                  | Guaranteed logic                                          | 3.15                         |      | _       | V    |      |

| V <sub>IL</sub>   | Input LOW level                   | Guaranteed logic                                          | -                            | -    | 1.35    | V    |      |

| $I_{\rm IH}$      | Input HIGH current                | $V_{\rm CC} = { m Max.}, V_{\rm I}$                       | -                            | -    | 1       | μA   |      |

| I <sub>II.</sub>  | Input LOW current                 | $V_{\rm CC} = { m Max.}, V_{\rm I}$                       | -                            | -    | -1      | μΑ   |      |

| $V_{\rm IK}$      | Clamp diode voltage               | $V_{\rm CC} = { m Min., I_{ m N}} =$                      | -                            | -0.7 | -1.2    | V    |      |

| IIOS              | Short-circuit current             | $V_{\rm CC} = {\rm Max.},^{(3)} V$                        |                              |      | -35     | mA   |      |

| V <sub>OH</sub>   | Output HIGH voltage               | $V_{\rm CC} = Min.,$                                      | I <sub>OH</sub> = -20 µA     | 4.4  | 4.499   | -    | V    |

| OH                | Output more voltage               | $V_{\rm IN} = V_{\rm IL}$                                 | $I_{\rm OH} = -4 \text{ mA}$ | 3.84 | 4.3     | -    | V    |

| V <sub>OL</sub>   | Output LOW voltage                | $V_{\rm CC} = Min.$                                       | I <sub>OL</sub> = 20 µА      | -    | .001    | 0.1  | V    |

| *OL               | Output COW Voltage                | $V_{\rm IN} = V_{\rm IH}$                                 | $I_{\rm OL} = 4 \text{ mA}$  |      | 0.17    | 0.33 |      |

| $I_{\rm CC}$      | Quiescent power<br>supply current | $V_{\rm CC} = Max.$<br>$V_{\rm IN} = GND \text{ or } V_0$ | -                            | 2    | 10      | μA   |      |

**Fan-out** = min ( $\mathbf{I}_{OHmax} / \mathbf{I}_{IH}, \mathbf{I}_{OLmax} / \mathbf{I}_{IL}$ )

For HC family (5-volt) CMOS:

Fan-out = min ( I<sub>OHmax</sub> / I<sub>IH</sub>, I<sub>OLmax</sub> / I<sub>IL</sub> ) = min (0.02 mA / 0.001 mA, -0.02 mA / -0.001 mA) = 20

Q: Is a fan-out of 20 "good" or "bad"?

DC fan-out is considerably greater in this case if the output voltage swing is degraded ... *but* DCNM is lower and signal transitions times are longer, causing speed degradation

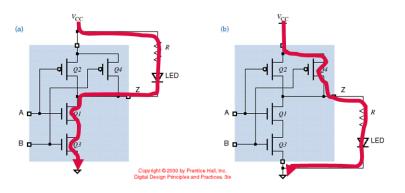

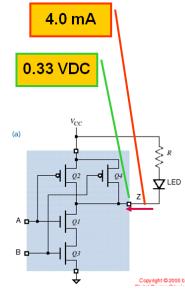

- driving LEDs

- LEDS represent "DC loads" and can be interfaced to a CMOS gate output either by sinking current (LOW output) or sourcing current (HIGH output)

Q: Which method is generally preferred (and *why*)?

• example: "worst case" souring and sinking analysis for driving an LED

#### sinking current

| Sym.            | Parameter             | Test                                 | Test Conditions <sup>(1)</sup> |      |       | Max. | Unit |

|-----------------|-----------------------|--------------------------------------|--------------------------------|------|-------|------|------|

| $V_{\rm IH}$    | Input HIGH level      | Guaranteed logic                     | 3.15                           | -    | _     | V    |      |

| VIL             | Input LOW level       | Guaranteed logic                     | -                              | -    | 1.35  | V    |      |

| I <sub>IH</sub> | Input HIGH current    | $V_{\rm CC} = Max., V_{\rm I}$       | -                              | -    | 1     | μΑ   |      |

| I <sub>IL</sub> | Input LOW current     | $V_{\rm CC} = { m Max.}, V_{\rm I}$  | -                              | -    | -1    | μΑ   |      |

| $V_{\rm IK}$    | Clamp diode voltage   | $V_{\rm CC} = { m Min., I_{ m N}} =$ | -                              | -0.7 | -1.2  | V    |      |

| IIOS            | Short-circuit current | $V_{\rm CC} = {\rm Max.}^{(3)}$      | ∕ <sub>O</sub> = GND           | -    | -     | -35  | mA   |

| 1/              | Output HIGH voltage   | where $V_{CC} = Min_{cc}$            |                                | 4.4  | 4.499 | -    | V    |

| V <sub>OH</sub> | Output HIGH Voltage   | $V_{\rm IN} = V_{\rm IL}$            | $I_{\rm OH} = -4 \text{ mA}$   | 3.84 | 4.3   | -    | V    |

| L/              | Output LOW and have   | $V_{\rm CC} = Min.$                  | I <sub>OL</sub> = 20 μA        | -    | .001  | 0.1  | V    |

| V <sub>OL</sub> | Output LOW voltage    | $V_{\rm IN} = V_{\rm IH}$            | $I_{OL} = 4 \text{ mA}$        |      | 0.17  | 0.33 |      |

| 1               | 0.1                   | V. Max                               |                                | -    | 0     | 10   |      |

$V_{R} = 5.0 - V_{LED} - V_{OL} = 5.0 - 1.9 - 0.33 = 2.77 V$

use "Max" value indicated for V<sub>OL</sub> of 0.33 V  $R = V_R/I_{OL} = 2.77/0.004 = 693 \Omega$   $P_R = R \times I_{OL}^2 = 693 \times (0.004)^2 = 11.1$  milliwatts Can also calculate power dissipation of resistor

#### sourcing current

| The fol         | lowing conditions appl | y unless otherwis                   | ER OPERATING RANGE<br>e specified:<br>/±5%; Military: T <sub>A</sub> = -5 | 1       | 5°C. V <sub>CC</sub> | = 5.0 V ± | 10% |

|-----------------|------------------------|-------------------------------------|---------------------------------------------------------------------------|---------|----------------------|-----------|-----|

| Sym.            | Parameter              | Test                                | Min.                                                                      | Тур.(2) | Max.                 | Unit      |     |

| VIII            | Input HIGH level       | Guaranteed logi                     | 3.15                                                                      | -       | _                    | V         |     |

| VIL             | Input LOW level        | Guaranteed logi                     | -                                                                         | -       | 1.35                 | V         |     |

| I <sub>IH</sub> | Input HIGH current     | $V_{\rm CC} = { m Max.}, V_{\rm I}$ | -                                                                         | -       | 1                    | μΑ        |     |

| IIL             | Input LOW current      | $V_{\rm CC} = { m Max.}, V_{\rm I}$ | -                                                                         | -       | -1                   | μΑ        |     |

| $V_{\rm IK}$    | Clamp diode voltage    | $V_{\rm CC}$ = Min., $I_{\rm N}$ =  | -                                                                         | -0.7    | -1.2                 | V         |     |

| IIOS            | Short-circuit current  | $V_{\rm CC} = {\rm Max.}^{(3)}$     | $V_{\rm O} = \rm GND$                                                     | -       | -                    | -35       | mA  |

| V <sub>OH</sub> | Output HIGH voltage    | $V_{\rm CC} = Min.,$                | $I_{OH} = -20 \ \mu A$                                                    | 4.4     | 4.499                |           | V   |

| *OH             | OH Output mon voitage  | $V_{\rm IN} = V_{\rm IL}$           | $I_{\rm OH} = -4 \text{ mA}$                                              | 3.84    | 4.3                  | -         | V   |

| VOL             | Output LOW voltage     | $V_{\rm CC} = Min.$                 | I <sub>OL</sub> = 20 µА                                                   | -       | .001                 | 0.1       | V   |

| "OL             | output cow voltage     | $V_{\rm IN} = V_{\rm IH}$           | $I_{OL} = 4 \text{ mA}$                                                   |         | 0.17                 | 0.33      |     |

$V_{R} = V_{OH} - V_{LED} = 3.84 - 1.9 = 1.94 V$ use "Min" value indicated for V<sub>OH</sub> of 3.84 V  $R = V_{R}/I_{OH} = 1.94/0.004 = 485 \Omega$  $P_{R} = R \times I_{OH}^{2} = 485 \times (0.004)^{2} = 7.8 \text{ milliwatts}$

- effects of excessive loading

- o in the LOW state, the output voltage (VoL) may increase beyond VoLmax

- $\circ$  in the HIGH state, the output voltage (V<sub>0</sub>H) may fall below V<sub>0Hmin</sub>

- output rise and fall times may increase beyond their specifications (details in next section)

- the operating temperature of the device may increase, thereby *reducing* the *reliability* of the device and eventually causing device *failure*

- <u>example</u>: a tale of two logic families

- $\circ \quad \mathbf{DCNM}, \mathbf{A} \rightarrow \mathbf{B}$

| Family "A"                                 |                                                             |  |                         |  |                            |                           |  |  |  |

|--------------------------------------------|-------------------------------------------------------------|--|-------------------------|--|----------------------------|---------------------------|--|--|--|

| $V_{CC} = 5 V$                             | $V_{\rm CC} = 5  \mathrm{V}$ $V_{\rm OH} = 4.4  \mathrm{V}$ |  | $V_{0L} = 0.40 V$       |  | $V_{IH} = 3.60 V$          | $V_{IL}$ = 1.60 V         |  |  |  |

| $V_{\rm TH} = (V_{\rm OH} - V_{\rm OL})/2$ | $I_{OH} = -4 \text{ mA}$                                    |  | $I_{OL} = 4 \text{ mA}$ |  | $I_{\rm IH} = 0.4 \ \mu A$ | I <sub>IL</sub> = -0.4 μA |  |  |  |

|                                            |                                                             |  |                         |  |                            |                           |  |  |  |

| - |    | 1.1 |    | (( <b>D</b> 11 |  |

|---|----|-----|----|----------------|--|

| F | aı | mı  | IV | " <b>''B</b> " |  |

| $V_{\rm CC} = 5 V$                         | $V_{\rm OH} = 3.3 V$      | $V_{OL} = 0.30 V$       | $V_{\rm IH} = 2.60  \rm V$ | $V_{IL} = 1.60 V$          |

|--------------------------------------------|---------------------------|-------------------------|----------------------------|----------------------------|

| $V_{\rm TH} = (V_{\rm OH} - V_{\rm OL})/2$ | I <sub>OH</sub> = -400 μA | $I_{OL} = 8 \text{ mA}$ | I <sub>III</sub> = 40 μA   | $I_{IL} = -0.4 \text{ mA}$ |

|                                            |                           |                         |                            |                            |

## DCNM<sub>A $\rightarrow$ B</sub> = min(4.4-2.6, 1.6-0.4) = 1.2V

$\circ \quad \mathbf{DCNM}, \mathbf{B} \rightarrow \mathbf{A}$

|          | /   |

|----------|-----|

| Family ' | •Δ″ |

| $V_{\rm CC} = 5 V$                         | $V_{OH} = 4.4 V$         | $V_{OL} = 0.40 V$       | $V_{\rm IH} = 3.60  \mathrm{V}$ | $V_{IL} = 1.60 V$         |

|--------------------------------------------|--------------------------|-------------------------|---------------------------------|---------------------------|

| $V_{\rm TH} = (V_{\rm OH} - V_{\rm OL})/2$ | $I_{OH} = -4 \text{ mA}$ | $I_{OL} = 4 \text{ mA}$ | $I_{\rm IH} = 0.4 \ \mu A$      | I <sub>IL</sub> = -0.4 μA |

|                                            |                          |                         |                                 |                           |

#### Family "B"

| $V_{CC} = 5 V$                             | $V_{OH} = 3.3 V$        | $V_{OL} = 0.30 V$ | $V_{\rm IH} = 2.60  \rm V$ | V <sub>IL</sub> = 1.60 V  |

|--------------------------------------------|-------------------------|-------------------|----------------------------|---------------------------|

| $V_{\rm TH} = (V_{\rm OH} - V_{\rm OL})/2$ | $I_{OH}$ = -400 $\mu A$ | $I_{OL} = 8 mA$   | I <sub>IH</sub> = 40 μA    | I <sub>IL</sub> = -0.4 mA |

## DCNM $_{B\to A}$ = min(3.3-3.6, 1.6-0.3) = -0.3V

- DCNM thought questions

- What is the consequence of a <u>negative</u> DCNM?

- What is the <u>minimum</u> DCNM required?

• <u>example</u>: a tale of two logic families, continued...

.. ....

$\circ$  Fan-out, A $\rightarrow$ B

| Family "A"                                 |                           |                         |                         |                            |

|--------------------------------------------|---------------------------|-------------------------|-------------------------|----------------------------|

| $V_{CC} = 5 V$                             | $V_{OH} = 4.4 V$          | $V_{OL} = 0.40 V$       | $V_{IH} = 3.60 V$       | $V_{IL} = 1.60 V$          |

| $V_{\rm TH} = (V_{\rm OH} - V_{\rm OL})/2$ | $I_{OH} = -4 \text{ mA}$  | $I_{OL} = 4 \text{ mA}$ | $I_{III} = 0.4 \ \mu A$ | I <sub>IL</sub> = -0.4 μA  |

| Family "B"                                 |                           |                         |                         |                            |

| $V_{\rm CC} = 5 V$                         | $V_{\rm OH} = 3.3$ V      | $V_{OL} = 0.30 V$       | $V_{\rm IH}$ = 2.60 V   | V <sub>IL</sub> = 1.60 V   |

| $V_{\rm TH} = (V_{\rm OH} - V_{\rm OL})/2$ | I <sub>OH</sub> = -400 μA | $I_{OL} = 8 \text{ mA}$ | $I_{IH} = 40 \ \mu A$   | $I_{IL} = -0.4 \text{ mA}$ |

|                                            |                           |                         | $\mathbf{V}$            | /                          |

## Fanout $_{A \to B} = min(\frac{4}{0.04}, \frac{4}{0.04}) = 10$

**CAUTION!! Current arrows for I**<sub>O</sub> and I<sub>I</sub> point in *opposite directions*

$\circ \quad Fan-out, B \rightarrow A$

| Family "A"                                 |                          |                         |                            |                           |

|--------------------------------------------|--------------------------|-------------------------|----------------------------|---------------------------|

| $V_{CC} = 5 V$                             | $V_{OH} = 4.4 V$         | $V_{OL} = 0.40 V$       | $V_{IH} = 3.60 V$          | $V_{IL} = 1.60 V$         |

| $V_{\rm TH} = (V_{\rm OH} - V_{\rm OL})/2$ | $I_{OH} = -4 \text{ mA}$ | $I_{OL} = 4 \text{ mA}$ | $I_{\rm IH} = 0.4 \ \mu A$ | I <sub>IL</sub> = -0.4 μA |

|                                            |                          |                         |                            |                           |

| Family "B"                                 |                         |                         |     |                          |     |                              |

|--------------------------------------------|-------------------------|-------------------------|-----|--------------------------|-----|------------------------------|

| $V_{\rm CC} = 5 V$                         | $V_{OH} = 3.3 V$        | $V_{OL} = 0.30 V$       | Уп  | $_{\rm H} = 2.60 { m V}$ | V   | $_{\rm IL} = 1.60 \ {\rm V}$ |

| $V_{\rm TH} = (V_{\rm OH} - V_{\rm OL})/2$ | $I_{OH}$ = -400 $\mu A$ | $I_{OL} = 8 \text{ mA}$ | III | <sub>I</sub> = 40 μA     | III | _=-0.4 mA                    |

|                                            |                         |                         |     |                          |     |                              |

### Fanout $_{B\to A}$ =min(400/0.4, 8/0.0004) = 1000

**CAUTION!! Current arrows for I**<sub>O</sub> and I<sub>I</sub> point in *opposite directions*

#### • Fan-out thought questions

- Is it possible for the fan-out to be <u>negative</u>?

- What is the <u>minimum</u> fan-out required?

| $V_{CC} = 5 V$                                                       | V <sub>OH</sub> = 3.50 V              | VOL - 0.50 V             | VIH - 2.50 V           | VIL = 1.00 V                |

|----------------------------------------------------------------------|---------------------------------------|--------------------------|------------------------|-----------------------------|

| $V_{\rm TH} = (V_{\rm OH} - V_{\rm OL})/2$                           | $I_{OH} = -5.0 \text{ mA}$            | $I_{OL} = 10 \text{ mA}$ | $I_{IH} = 500 \ \mu A$ | $I_{IL} = -2.0 \text{ m/s}$ |

| A. 0.50 V<br>B. 1.00 V<br>C. 1.50 V<br>D. 2.00 V<br>E. none of the a | above                                 |                          |                        |                             |

|                                                                      |                                       | Mar                      | Mu                     | Voi                         |

| DCNM = mir                                                           | I (VOH <sub>min</sub> -               | – VIH <sub>mine</sub>    | VILmax -               | VOLmax)                     |

| DCNM = mir                                                           | i <mark>(</mark> Voh <sub>min</sub> - | - VIH <sub>min</sub> ,   | VILmax -               | VOL <sub>max</sub>          |

| DC Characteristics of a Hypothetical Logic Family |                            |                          |                        |                            |  |

|---------------------------------------------------|----------------------------|--------------------------|------------------------|----------------------------|--|

| $V_{CC} = 5 V$                                    | V <sub>OH</sub> = 3.50 V   | V <sub>OL</sub> = 0.50 V | $V_{IH} = 2.50 V$      | V <sub>IL</sub> = 1.00 V   |  |

| $V_{TH} = (V_{OH} - V_{OL})/2$                    | $I_{OH} = -5.0 \text{ mA}$ | $I_{OL} = 10 \text{ mA}$ | $I_{IH} = 500 \ \mu A$ | $I_{IL} = -2.0 \text{ mA}$ |  |

- 2. The practical fanout for this logic family is:

- A. 1

- B. 2

- C. 5

- D. 10

- E. none of the above

Fan-out = min (  $IOH_{max}$  / IH,  $IOL_{max}$  / IL )

3. The nominal (minimum) case for the outputs of logic family "A" to be able to successfully drive the inputs of logic family "B" is:

- A. fanout<sub>A→B</sub>  $\leq$  1 and DCNM<sub>A→B</sub> < 0

- B. fanout<sub>A→B</sub>  $\leq$  0 and DCNM<sub>A→B</sub> < 1

- C. fanout<sub>A→B</sub>  $\geq$  1 and DCNM<sub>A→B</sub> > 0

- D.  $fanout_{A \rightarrow B} \ge 0$  and  $DCNM_{A \rightarrow B} > 1$

- E. none of the above

What is the minimum fan-out permissible?

What is the minimum DCNM permissible?

|                                | aracteristics of a         | **                       |                          |                            |

|--------------------------------|----------------------------|--------------------------|--------------------------|----------------------------|

| $V_{CC} = 5 V$                 | V <sub>OH</sub> = 3.50 V   | V <sub>OL</sub> = 0.50 V | $V_{IH} = 2.50 V$        | $V_{IL} = 1.00 V$          |

| $V_{TH} = (V_{OH} - V_{OL})/2$ | $I_{OH} = -5.0 \text{ mA}$ | $I_{OL} = 10 \text{ mA}$ | I <sub>IH</sub> = 500 μA | $I_{IL} = -2.0 \text{ mA}$ |

4. When interfacing an LED that has a forward voltage of 1.5 V to this logic family in a *current sourcing* configuration, maximum brightness will be achieved (within the rated specifications) using a current limiting resistor of the value:

| Α. 200Ω | Β. 300Ω | C. 400Ω | D. 500Ω | E. none of these |  |

|---------|---------|---------|---------|------------------|--|

|         |         |         |         |                  |  |

|         |         |         |         |                  |  |

|         |         |         |         |                  |  |

| $V_{TH} = (V_{OH} - V_{OL})/2$ $I_{OH} = -5$<br>5. When interfacing an L<br>to this logic family in a cu<br>brightness will be achiev<br>a current limiting resistor | LED that | t has a fo | orward vo   | oltage of 1.5 V |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------|-------------|-----------------|

| to this logic family in a cu<br>brightness will be achiev                                                                                                            | urrents  | sinking co | onfiguratio | -               |

| Α. 200Ω Β. 300Ω                                                                                                                                                      | c. 400   | value:     |             | E. none of th   |

#### Lecture Summary – Module 1-G Propagation Delay and Transition Time

**Reference:** Digital Design Principles and Practices 4<sup>th</sup> Ed. pp. 114-128, 5<sup>th</sup> Ed. pp. 764-778

- overview

- the *speed* and *power dissipation* of a CMOS device depend on the dynamic ("AC") characteristics of the device and its load

- logic designers must carefully examine the effects of output loading and redesign where the loading is too high

- speed (performance) depends on two characteristics:

- propagation delay

- transition time

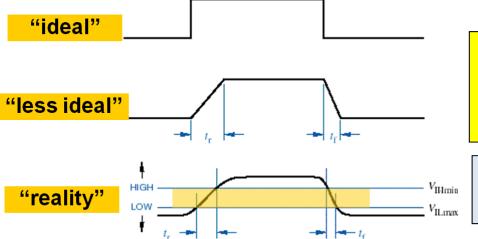

- logic gates require a certain amount of "think time" to produce a new output in response to changing inputs – referred to as the *propagation delay* of the gate

- logic gate outputs can not change from a low voltage to a high voltage (or vice-versa)

"instantaneously" referred to as the *transition time* of the gate

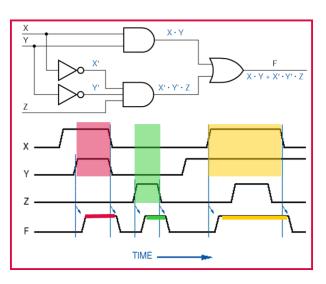

- a *timing diagram* can be used to show how a logic circuit responds to time-varying input signals

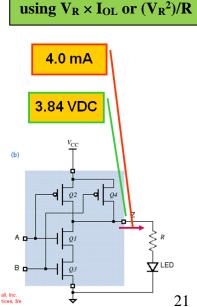

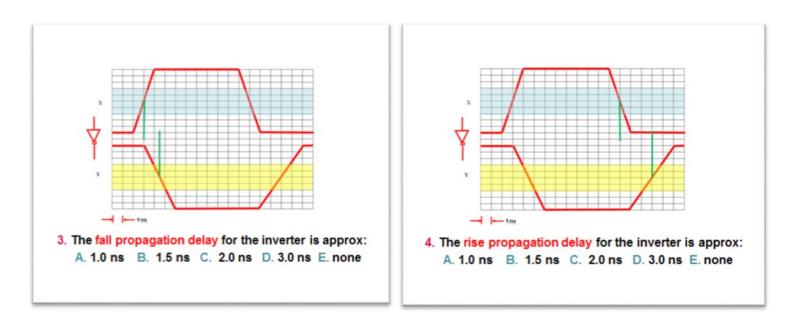

- propagation delay

- <u>definition</u>: the electrical path from a particular input signal of a logic element to its output signal is called a *signal path*

- $\circ$  <u>definition</u>: the amount of time it takes for a change in an input signal to cause a corresponding change in a gate's output signal is called the *propagation delay* (t<sub>p</sub>)

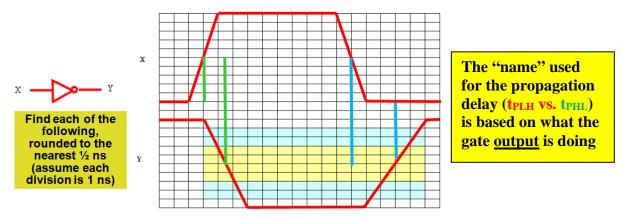

- the propagation delay for an output signal going from LOW-to-HIGH (t<sub>PLH</sub>) may be different than the propagation delay of that signal going from HIGH-to-LOW (t<sub>PHL</sub>)

The "name" used for the propagation delay (t<sub>PLH</sub> vs. t<sub>PHL</sub>) is based on what the gate <u>output</u> is doing

- propagation delay, continued...

- several factors lead to *non-zero* propagation delays in CMOS circuits:

- the rate at which transistors change state is influenced both by semiconductor physics and the circuit environment (input signal transition time, input capacitance, and output loading)

- multistage devices (e.g., non-inverting gates) may require several internal transistors to change state before the output can change state

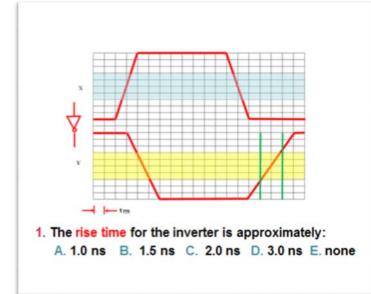

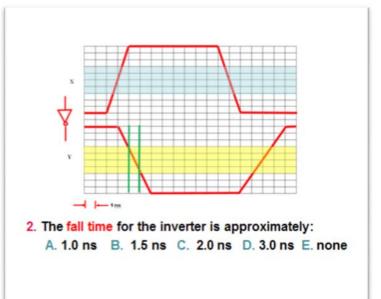

- o example: propagation delay measurement

Rise propagation delay  $(t_{PLH}) = 3$  ns Fall propagation delay  $(t_{PHI}) = 1.5$  ns

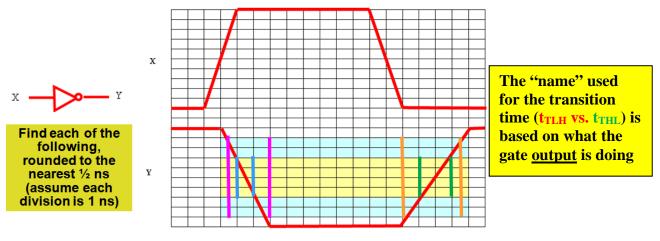

- transition time

- <u>definition</u>: the amount of time that the output of a logic circuit takes to change from one state to another

- rise time (tr or t<sub>TLH</sub>): the time an output signal takes to transition from low-tohigh

- fall time (t<sub>f</sub> or t<sub>THL</sub>): the time an output signal takes to transition from high-tolow

- gate outputs can *not* change state *instantaneously* (i.e., with a transition time of zero) because they need to *charge the stray capacitance* of the wires and other components they drive

The "name" used for the transition time (t<sub>TLH</sub> vs. t<sub>THL</sub>) is based on what the gate <u>output</u> is doing

The rise and fall times are typically *not* equal in value

- transition time, continued...

- to avoid difficulties in defining the endpoints, transition times are normally measured one of two different ways:

- at the boundaries of the valid logic levels (i.e., V<sub>IHmin</sub> and V<sub>ILmax</sub>)

- at the 10% and 90% points of the output waveform

- using the "valid logic level" convention (above), the rise and fall times indicate how long it takes for an output signal to pass through the (undefined) *indeterminate region* between LOW and HIGH

- <u>example</u>: transition time measurement / comparison of endpoints

Rise time  $(t_{TLH})$  based on Wakerly's (30%-70%) definition = 2 ns Rise time  $(t_{TLH})$  based on standard 10%-90% definition = 3.5 ns Fall time  $(t_{THL})$  based on Wakerly's (70%-30%) definition = 1 ns Fall time  $(t_{THL})$  based on standard 90%-10% definition = 2.5 ns

#### • transition time factors

- the transition times of a CMOS circuit depend mainly on two factors:

- the "on" transistor resistance

- the load capacitance

- stray capacitance (called an "AC load") arises from at least three different sources:

- output circuits including transistors, internal wiring, and packaging

- wiring that connects a gate output to other gate inputs

- input circuits including transistors, internal wiring, and packaging

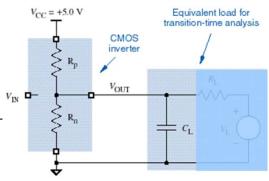

- o equivalent circuit

- a gate output's load can be modeled by an equivalent load circuit with three components:

- R<sub>L</sub> and V<sub>L</sub> represent the DC load they determine the steady state voltages and currents present and do not have much effect on transition times

- C<sub>L</sub> represents the AC (capacitive) load it determines the voltages and currents present while the output is changing, as well as how long it takes to change from one state to another

#### • transition time, continued...

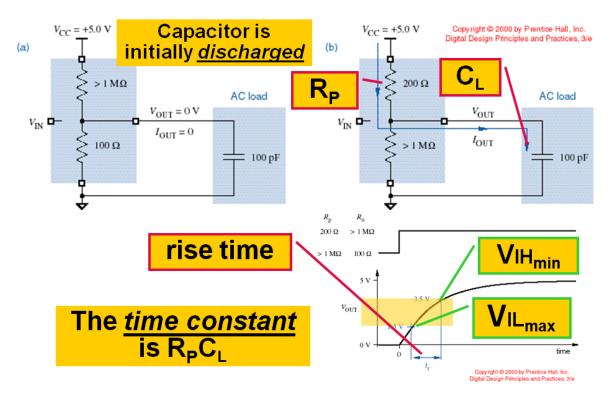

• model for low-to-high transition

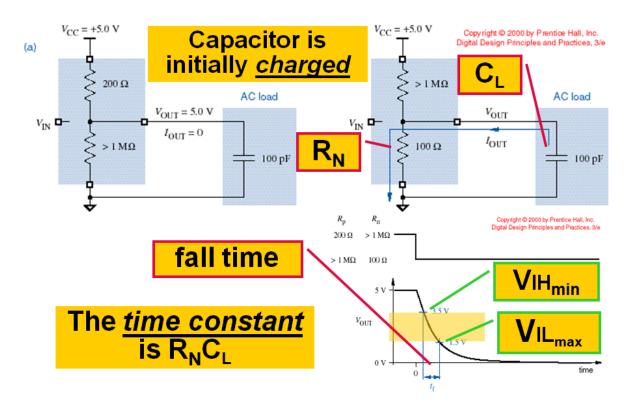

#### • model for high-to-low transition

- transition time, continued...

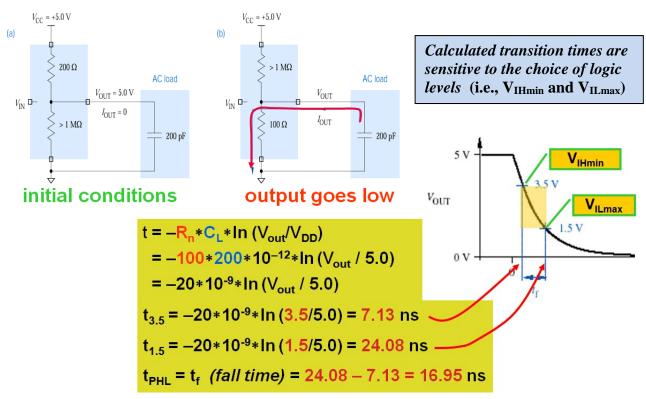

- <u>example</u>: given that a CMOS inverter's P-channel MOSFET has an ON resistance of 200Ω, that its N-channel MOSFET has an ON resistance of 100Ω, and that the capacitive (or AC) load  $C_L = 200$  pF, calculate the fall time

- transition time estimation ("rule of thumb") in practical circuits, the transition time can be *estimated* using the RC time constant of the charging or discharging circuit

- <u>example</u>: given that a CMOS inverter's P-channel MOSFET has an ON resistance of 200 $\Omega$ , that its N-channel MOSFET has an ON resistance of 100 $\Omega$ , and that the capacitive (or "A.C.") load C<sub>L</sub> = 200 pF, *estimate* the fall time and rise time

| Fall time estimate:                            | Rise time estimate:                            |

|------------------------------------------------|------------------------------------------------|

| R <sub>N</sub> X C <sub>L</sub> = 100 X 200 pF | R <sub>P</sub> X C <sub>L</sub> = 200 X 200 pF |

| = 1 X 10 <sup>2</sup> X 2 X 10 <sup>-10</sup>  | = 2 X 10 <sup>2</sup> X 2 X 10 <sup>-10</sup>  |

| = 2 X 10 <sup>-8</sup> = 20 X 10 <sup>-9</sup> | = 4 X 10 <sup>-8</sup> = 40 X 10 <sup>-9</sup> |

| = 20 ns                                        | = 40 ns                                        |

|                                                |                                                |

- capacitive load conclusions

- an increase in load capacitance causes an increase in the RC time constant and a corresponding increase in the output transition (rise/fall) times

- load capacitance must be *minimized* to obtain high circuit performance this can be achieved by:

- minimizing the number of inputs driven by a given signal

- creating multiple copies of the signal (using "buffers")

- careful *physical layout* of the circuit

### Lecture Summary – Module 1-H

Power Consumption and Decoupling

Reference: Digital Design Principles and Practices 4th Ed. pp. 122-124, 5th Ed. pp. 771-773

- overview

- <u>definition</u>: the power dissipation (consumption) of a CMOS circuit whose output is *not changing* is called *static* (*quiescent*) *power dissipation*

- o most CMOS circuits have very low static power dissipation

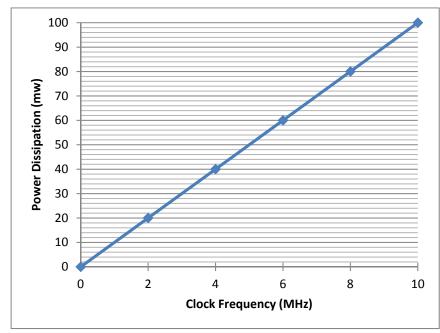

- CMOS circuits only dissipate a significant amount of power during *transitions* this is called *dynamic power dissipation*

- sources of dynamic power dissipation:

- $\circ$  the partial "short-circuiting" of the CMOS output structure (e.g., when the input voltage is not close to one of the power supply rails) called "P<sub>T</sub>" (power due to output transitions)

- $\circ$  the capacitive load on the output (power is dissipated in the "on" resistance of the active transistor to charge/discharge the capacitive load) called "P<sub>L</sub>" (power due to charging/discharging load)

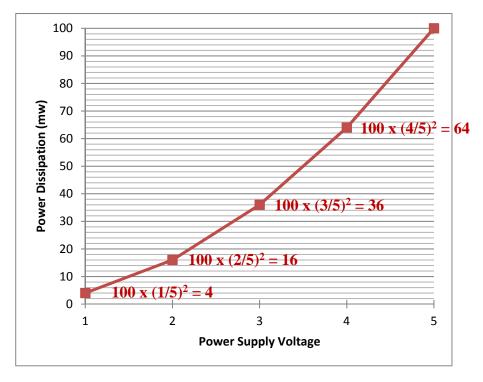

- $\circ$  total dynamic power dissipation (P<sub>T</sub> + P<sub>L</sub>) is proportional to the *square* of the power supply voltage times the transition frequency

- conclusions:

- power dissipation increases *linearly* as the frequency of operation increases

- reducing the power supply voltage results in a *quadratic* reduction of the power dissipation

- <u>example</u>: a microcontroller can operate over a frequency range of 0 Hz to 10 MHz, and dissipates 100 mW when operated at 10 MHz; plot its power dissipation over the specified frequency range

• <u>example</u>: a microcontroller can operate over a power supply range of 1 to 5 volts, and dissipates 100 mW when operated at 5 VDC; plot its power dissipation over the specified power supply range

- current spikes and decoupling

- when a CMOS gate output changes state, the P- and N-channel transistors are both partially on simultaneously, causing a *current spike*

- o current spikes often show up as *noise* on the power supply and ground connections

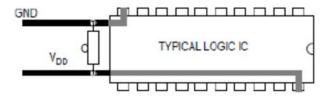

- *decoupling capacitors* (between Vcc and GND) must be distributed throughout a printed circuit board (PCB) to serve as a source of instantaneous current during output transitions *this helps mitigate noise and improve signal quality*

- decoupling capacitors should be located as *physically close* as possible to each IC

- $\circ~$  use 0.1  $\mu F$  decoupling capacitors for system frequencies up to 15 MHz; above 15 MHz, use 0.01  $\mu F$  decoupling capacitors

Assume a CMOS microprocessor dissipates 100 milliwatts of power when operated at a clock frequency of 100 MHz with a supply voltage of 5 V. If the frequency of operation is reduced from 100 MHz to 40 MHz (and the supply voltage remains 5 V), the power dissipation will be reduced to:

A. 16 mW B. 25 mW C. 40 mW D. 64 mW E. none of these

| when ope<br>5 V. If the<br>of operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CMOS microprocessor dissipates 100 milliwatts of power<br>erated at a clock frequency of 100 MHz with a supply voltage<br>supply voltage is reduced from 5 V to 4 V (and the frequence<br>on remains 100 MHz), the power dissipation will be reduced<br>W B. 25 mW C. 40 mW D. 64 mW E. none of these | у |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| A. 16 mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | V B. 25 mW C. 40 mW D. 64 mW E. none of these                                                                                                                                                                                                                                                         |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                       |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                       |   |

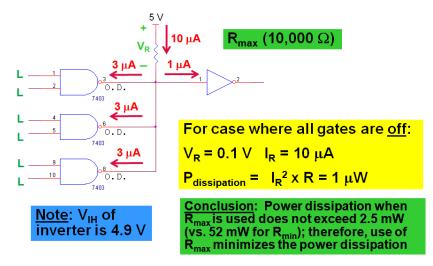

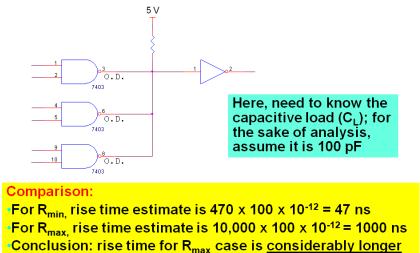

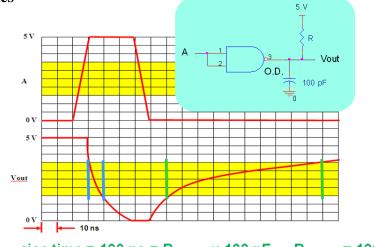

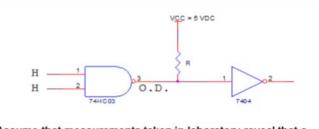

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                       | _ |