## Homework 8

Due at the beginning of your scheduled lab period

| Last Name (Printed): _ |                        | Lab Div: | Date: |

|------------------------|------------------------|----------|-------|

| E-mail:                | @purdue.edu Signature: |          |       |

<u>Printed</u> copies of these pages along with your <u>original</u> (hand-annotated, not photocopied) written solution in the <u>space provided</u> (unless otherwise indicated) are required in order to receive credit. NOTE: The purpose of homework is to provide an opportunity for practicing the kinds of problems you will be asked to solve on quizzes and exams – <u>copying the work of someone else does not accomplish this.</u>

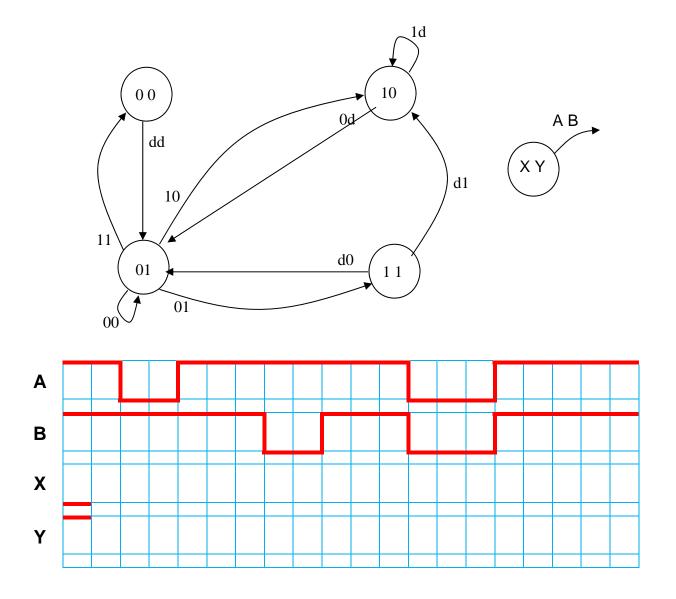

1. [4 pts] Given the following state transition diagram, complete the timing chart below.

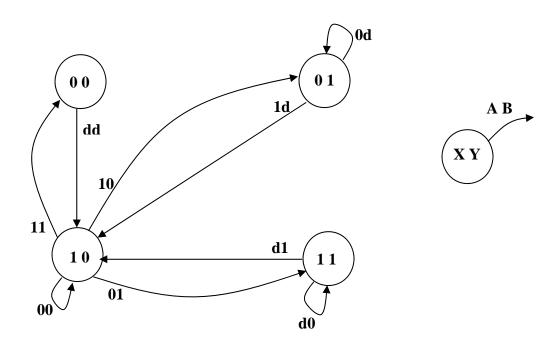

2. [6 pts] Given the following state transition diagram, determine the *next state equations* it represents in *minimum sum-of-products form*.

| Χ | Υ | Α | В | X* | Υ* |

|---|---|---|---|----|----|

| 0 | 0 | 0 | 0 |    |    |

| 0 | 0 | 0 | 1 |    |    |

| 0 | 0 | 1 | 0 |    |    |

| 0 | 0 | 1 | 1 |    |    |

| 0 | 1 | 0 | 0 |    |    |

| 0 | 1 | 0 | 1 |    |    |

| 0 | 1 | 1 | 0 |    |    |

| 0 | 1 | 1 | 1 |    |    |

| 1 | 0 | 0 | 0 |    |    |

| 1 | 0 | 0 | 1 |    |    |

| 1 | 0 | 1 | 0 |    |    |

| 1 | 0 | 1 | 1 |    |    |

| 1 | 1 | 0 | 0 |    |    |

| 1 | 1 | 0 | 1 |    |    |

| 1 | 1 | 1 | 0 |    |    |

| 1 | 1 | 1 | 1 |    |    |

X\* and Y\* are "shorthand" for the next state of X and Y

| ·  | X  | ζ′ | 2 | K  | _  |    | X  | <u> </u> | Σ | K  |    |

|----|----|----|---|----|----|----|----|----------|---|----|----|

|    |    |    |   |    | B′ |    |    |          |   |    | B' |

| A' |    |    |   |    | В  | A' |    |          |   |    | В  |

| Δ. |    |    |   |    | D  | Δ  |    |          |   |    | D  |

| A  |    |    |   |    | B' | A  |    |          |   |    | B' |

| I  | Y' | 7  | Y | Y' |    |    | Y' | Ŋ        | Y | Y' |    |

| <b>X</b> * = . | <br> |  |

|----------------|------|--|

| <b>Y</b> * = . | <br> |  |

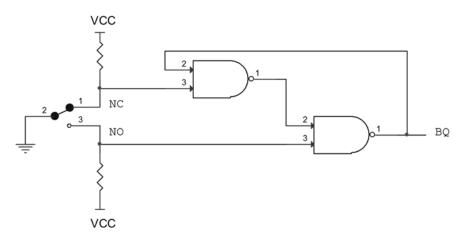

3. [4 pts] Write a Verilog code module that implements the following circuit:

```

module bounceless_switch(NC,NO,BQ);

input wire NC,NO;

output wire BQ;

endmodule

```

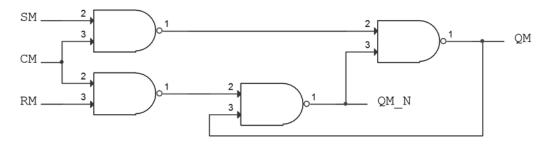

4. [6 pts] Write a Verilog code module that implements the following circuit:

```

module master_latch(SM,RM,CM,QM,QM_N);

input wire SM,RM,CM;

output wire QM,QM_N;

endmodule

```