1

## Homework 4

Due at the beginning of your scheduled lab period

| Last Name (Printed): | KEY                     | Lab Div: _ | Date: |

|----------------------|-------------------------|------------|-------|

| E-mail:              | @purdue.edu Signature:_ | 18         | PTS   |

<u>Printed</u> copies of these pages along with your <u>original</u> (hand-annotated, not photocopied) written solution in the <u>space provided</u> (unless otherwise indicated) are required in order to receive credit. NOTE: The purpose of homework is to provide an opportunity for practicing the kinds of problems you will be asked to solve on quizzes and exams – copying the work of someone else does not accomplish this.

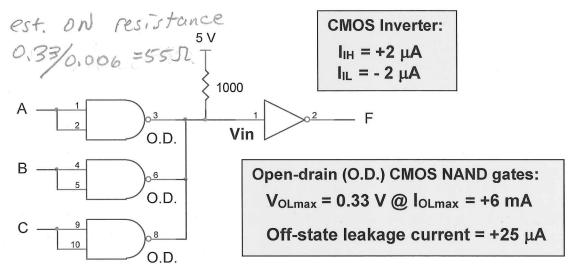

1. [12 pts] Given the circuit, below, calculate  $V_{in}$  (the CMOS inverter input voltage) for each of the cases indicated along with the current *individually* sunk by each active open drain gate. *Show your calculations*. (LOs 1-34 and 1-35).

| A   | В   | С   | O.D. Equivalent<br>ON Resistance | V <sub>in</sub> to<br>Inverter | Current Sunk by Each Active O.D. Gate |

|-----|-----|-----|----------------------------------|--------------------------------|---------------------------------------|

| 0 V | 0 V | 0 V |                                  | 4.923v                         | 25 uA - beakage                       |

| 5 V | 0 V | 0 V | 10552                            | 0,261V                         | 4.74 mA                               |

| 5 V | 5 V | 0 V | 1027.52                          | 0,1341                         | 2.43 mA                               |

| 5 V | 5 V | 5 V | 1018.3s                          | 0.090V                         | 1.64 mA                               |

leakage =  $3 \times 25 \mu A + I_{1H} = 77 \mu A$  $Vin = 5 - (77 \times 10^{-6}) \times 10^{3} = 4.923 V$

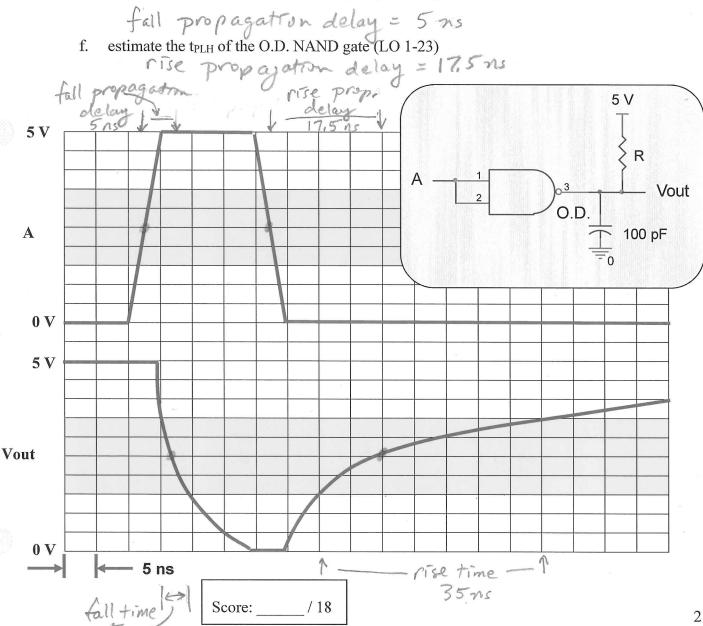

- [6 pts] Given the circuit, below, along with its Vi-Vo (input output voltage) relationship, determine the following (show calculations where applicable):

- estimate the ON resistance of the O.D. NAND gate (LO 1-25)

b. estimate the value of the pull-up resistor (LO 1-36)

estimate the t<sub>TLH</sub> of the O.D. NAND gate (LO 1-25)

d. estimate the  $t_{THL}$  of the O.D. NAND gate (LO 1-25)

e. estimate the t<sub>PHL</sub> of the O.D. NAND gate (LO 1-23)