## Homework 2

Due at the beginning of your scheduled lab period

| Last Name (Printed): | KEY                      | Lab Div: Date: |

|----------------------|--------------------------|----------------|

| E-mail:              | @purdue.edu Signature: _ | 28 pts Max     |

<u>Printed</u> copies of these pages along with your <u>original</u> (hand-annotated, not photocopied) written solution in the <u>space provided</u> (unless otherwise indicated) are required in order to receive credit. NOTE: The purpose of homework is to provide an opportunity for practicing the kinds of problems you will be asked to solve on quizzes and exams – copying the work of someone else does not accomplish this.

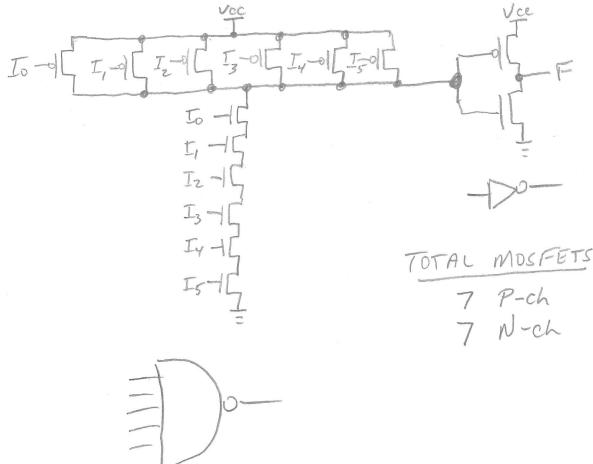

1. [ pts] Show a MOSFET-level diagram for a 6-input AND gate realized using a 6-input NAND gate followed by an inverter gate. Label the inputs I<sub>0</sub>...I<sub>5</sub> and the output F. Be sure to show the power (Vcc) and ground (GND) connections as well. Determine the total number of N- and P-channel MOSFETs required for this realization (LO 1-10).

8

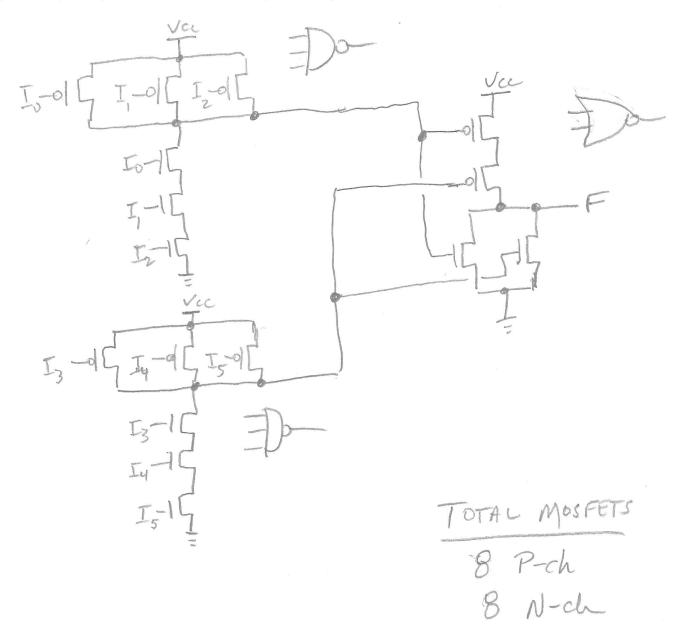

2. [ pts] Show a MOSFET-level diagram for a 6-input AND gate realized using two 3-input NAND gates on the first level and a (single) 2-input NOR gate on the second level. Label the inputs I<sub>0</sub>...I<sub>5</sub> and the output F. Determine the total number of N- and P-channel MOSFETs required for this realization. Be sure to show the power (Vcc) and ground (GND) connections as well (LO 1-12).

3. [4 pts] Read the section on *Fan-In* (5<sup>th</sup> Ed., pp. 741-742; 4<sup>th</sup> Ed., pp. 92-93) in the course text. Based on this material, list the tradeoffs between the two 6-input AND functions realized in problems 1 and 2, from a practical point of view. Then provide rationale for which realization would be preferable, based on the tradeoffs you have enumerated.

The additive "on" resistance of series transistors

(imits the fan-in of CMOS gates, typically

to 4 for NOZ gates and 6 for NAND gates,

The realization in problem I pushes this

(imit, but is still acceptable. The realization

in problem 2 is well within the fan-in constraints,

but requires 2 more transistors than

problem 1. Therefore, the realization in

problem 1 would be cheaper and therefore preferble.

4. [Opts] Given that the P-channel device in the circuit below has ON and OFF resistances

of 50 \( \Omega \) and 1 M\( \Omega \) (respectively) and that the N-channel device has ON and OFF

4. [In pts] Given that the P-channel device in the circuit below has ON and OFF resistances of 50  $\Omega$  and 1 M $\Omega$  (respectively) and that the N-channel device has ON and OFF resistances of 20  $\Omega$  and 2 M $\Omega$  (respectively), complete the table listing the output voltages obtained for each input combination as well as the power dissipation (in milliwatts). Show your calculations (LOs 1-10 and 1-11).

|           |    |    |                  |                   |           | r    | 5 V | DN/OFF                 |

|-----------|----|----|------------------|-------------------|-----------|------|-----|------------------------|

| 1         | A  | В  | V <sub>out</sub> | Power Dissipation | Series    | A —  |     | 50/1,000,000           |

| Noff, Pon | 0V | 0V | 4.999            | 12,5 MW           | 2,000,050 | ,  - |     |                        |

| both on   | 0V | 5V | 1,43             | 357 mw            | 50+20=70  |      | -   | <ul><li>Vout</li></ul> |

| both off  | 5V | 0V | 3,33             | 8.3 mW            | 3,000,000 | , L  |     | /                      |

| Non, Poff | 5V | 5V | .0001            | 25,0 jew          | 1,000,020 | в —  |     | 20/2,000,000           |

| ,         |    |    |                  |                   |           | '  - | 5   |                        |

|           |    |    |                  |                   |           |      | √G  | SND                    |