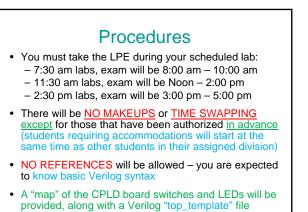

## What to Expect

You will be required to sign (and <u>abide by</u>) the following academic honesty statement:

"In signing this statement, I hereby agree NOT TO DISCUSS the contents of this exam with ANY OTHER STUDENT. I understand that, if I fail to honor this agreement, I will receive a score of **ZERO** for this exam and be subject to possible disciplinary action."

- You will be asked to write Verilog code that realizes the specified design

- · Each lab division will be assigned a randomly selected problem to solve (from the pool of available questions this semester)

- The LPE counts for 10% of your course grade

## How to Prepare for the LPE

- · Review the experiment descriptions and solutions that you have assembled in your Lab Noteboo

- Review the following topics:

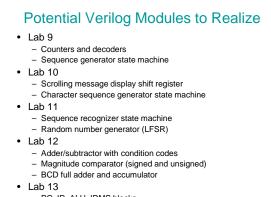

- structure/syntax of Verilog and coding strategies

- decoders, multiplexers, and priority encoders

- sequence generators

defining the pin assignments

- counters, shift registers, and state decoding

- sequence recognizers

- two's complement arithmetic, condition code generation, and magnitude comparators (both signed and unsigned)

- carry look-ahead adder realizations

- BCD full adder/accumulator realization

- arithmetic logic unit structure and realization

- personal simple computer realization (including Verilog modules that have been provided

- PC, IR, ALU, IDMS blocks

## Memory editor

## **IMPORTANT!**

Be sure you understand all the steps completed for each experiment, including code that you may have 'cut and paste" from the notes and/or code that has been provided.

NOTE: The last day to complete all lab makeups is the office hour session on Monday, April 22, 2019.