Note that "none of the above" MAY be a VALID ANSWER.

OUTCOME #3: "an ability to analyze and design sequential logic circuits."

## Place answers on the supplied BUBBLE SHEET only – nothing written here will be graded.

- 1. A new type of flip-flop, the BF ("Best Friend"), is described by the following PS-NS table. The characteristic equation for this flip-flop is:

- (A) **Q\* = F'•Q + B•Q**

- (B) **Q\* = F•Q + B'•Q'**

- (C) **Q**\* = **F**•**Q**' + **B**•**Q**

- (D) **Q**\* = **F**'•**Q**' + **B**'•**Q**

- (E) none of the above

- 2. The excitation required to effect a state transition of the BF flip-flop from "0" to "1" is:

- (A) **B=0, F=d**

- (B) **B=d, F=0**

- (C) **B=1, F=d**

- (D) **B=d, F=1**

- (E) none of the above

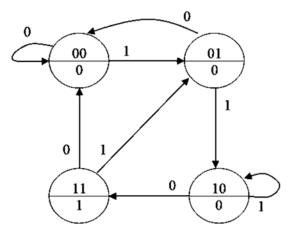

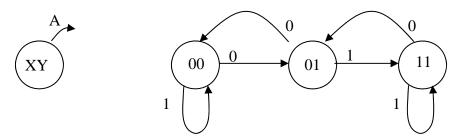

- 3. Assuming the state machine depicted in the given state transition diagram is initialized to state **00**, the input sequence **1101011100** will cause the following output sequence to be generated:

- (A) **001000010**

- (B) **000000000**

- (C) **001000001**

- (D) **0001000001**

- (E) none of the above

- 4. The **embedded binary sequence** recognized by this state machine is the pattern:

- (A) **001**

- (B) **011**

- (C) **100**

- (D) **110**

- (E) none of the above

BF Flip-Flop PS-NS Table for Questions 1 and 2

| B | F | Q | Q* |  |  |  |  |  |

|---|---|---|----|--|--|--|--|--|

| 0 | 0 | 0 | 1  |  |  |  |  |  |

| 0 | 0 | 1 | 0  |  |  |  |  |  |

| 0 | 1 | 0 | 1  |  |  |  |  |  |

| 0 | 1 | 1 | 1  |  |  |  |  |  |

| 1 | 0 | 0 | 0  |  |  |  |  |  |

| 1 | 0 | 1 | 0  |  |  |  |  |  |

| 1 | 1 | 0 | 0  |  |  |  |  |  |

| 1 | 1 | 1 | 1  |  |  |  |  |  |

|   |   |   |    |  |  |  |  |  |

State Transition Diagram for Questions 3 and 4

- 1 -

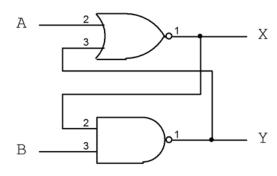

The following circuit applies to questions 5 through 9 (write the NS equations, complete the PS-NS table, and draw the state transition diagram before answering the questions):

- 5. The next state equation for Y is:

- (A)  $\mathbf{Y}^* = \mathbf{B}' \cdot \mathbf{X}'$

- (B) **Y**\* = **B**' + **X**'

- (C) **Y**\* = **B**' + **A** + **Y**

- (D) **Y**\* = **B**' · (**A** +**Y**)

- (E) none of the above

- 6. State **X=0**, **Y=1** is:

- (A) an initial state

- (B) a final state

- (C) a trap state

- (D) an accepting state

- (E) none of the above

- 7. The following state **cannot** occur:

- (A) **X=0, Y=0**

- (B) X=0, Y=1

- (C) X=1, Y=0

- (D) X=1, Y=1

- (E) none of the above

- Y X\* Y\* Х А В

- Based on the state transition diagram, if this feedback sequential circuit is initialized to state X=0, Y=0 and combination A=0, B=0 is (continuously) applied to its inputs, the (steady state) output combination will be:

- (A) X=0, Y=0

- (B) X=0, Y=1

- (C) X=1, Y=0

- (D) X=1, Y=1

- (E) unpredictable

- 9. Based on the state transition diagram, if this feedback sequential circuit is initialized to state **X=0**, **Y=0** and combination **A=0**, **B=1** is (continuously) applied to its inputs, the outputs will:

- (A) be unpredictable

- (B) stay at X=0, Y=0

- (C) change to X=1, Y=1

- (D) "oscillate" between X=0, Y=0 and X=1, Y=1

- (E) none of the above

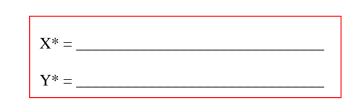

10. The **nominal setup time** provided for the D flip-flop, based on the excitation signals (D and CLK) depicted in the timing chart, is:

(A) 5 ns (B) 10 ns (C) 15 ns (D) 20 ns (E) none of the above

11. The **nominal hold time** provided for the D flip-flop, based on the excitation signals (D and CLK) depicted in the timing chart, is:

(A) 20 ns (B) 15 ns (C) 10 ns (D) 5 ns (E) none of the above

12. The  $\mathbf{t}_{\mathsf{PLH}(\mathsf{C}\to\mathsf{Q})}$  of the D flip-flop is:

(A) 5 ns (B) 10 ns (C) 15 ns (D) 20 ns (E) none of the above

13. The  $\mathbf{t}_{PHL(C \rightarrow Q)}$  of the D flip-flop is:

(A) 20 ns (B) 15 ns (C) 10 ns (D) 5 ns (E) none of the above

The following state transition diagram applies to questions 14 through 16:

- 14. If designed for **minimum** <u>cost</u>, the next state equation for **X** is:

- (A) **X\* = X + Y**

- (B) **X\* = A·Y**

- (C)  $X^* = Y + X \cdot A + X' \cdot A'$

- (D) **X\* = X + (X'+Y)·A'**

- (E) none of the above

- 15. If designed for **minimum** <u>cost</u>, the next state equation for **Y** is:

- (A) **Y**\* = X·A

- (B) **Y\* = A·Y**

- (C)  $\mathbf{Y}^* = \mathbf{Y} + \mathbf{X} \cdot \mathbf{A} + \mathbf{X}' \cdot \mathbf{A}'$

- (D)  $\mathbf{Y}^* = \mathbf{X} + \mathbf{Y} \cdot \mathbf{A} + \mathbf{Y}' \cdot \mathbf{A}'$

- (E) none of the above

- 16. Designing a state machine based on **minimum** <u>cost</u> means:

- (A) there are no "don't cares" in the excitation equations

- (B) there are no "don't cares" in the next state equations

- (C) there are no "don't cares" in the output equations

- (D) all of the above

- (E) none of the above

- 17. As a contestant on the hit TV series *Digital Dynasty*, you have been asked to "digitally dual" with your BECEFE (best ECE friend *evah*) over the phenomenon of metastability. You confidently explain that the <u>next state</u> of an edge-triggered D flipflop will most likely be **random** if:

- (A) its minimum setup time requirement is not met

- (B) its minimum hold time requirement is not met

- (C) its minimum clock pulse width requirement is not met

- (D) all of the above

- (E) none of the above

ECE 270 Learning Outcome 3

© 2019 by D. G. Meyer / Purdue University – may not be copied or reproduced, in any form or by any means.

module mystery\_seq1(CLK, Q); input wire CLK; output reg [2:0] Q; reg [2:0] next\_Q; always @ (posedge CLK) begin  $0 \leq next 0$ e al e end

(E) none of the above

Q1\* Q0\* **O2**\* Q2 Q1 **Q0** 0 0 0 0 1 0 1 0 0

100

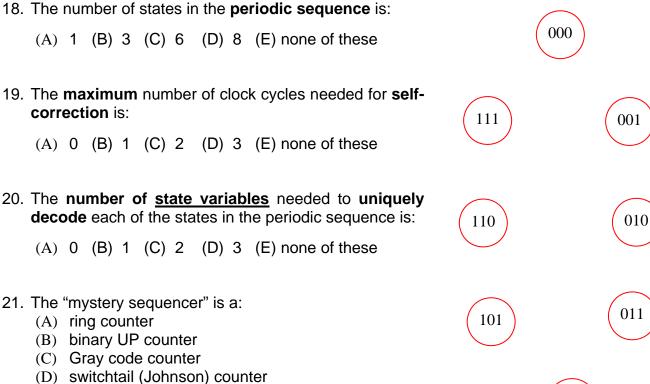

The following Verilog program applies to questions 18 through 21 (complete the PS-NS

table and draw the state transition diagram before answering the questions):

© 2019 by D. G. Meyer / Purdue University – may not be copied or reproduced, in any form or by any means.

Practice Exam B

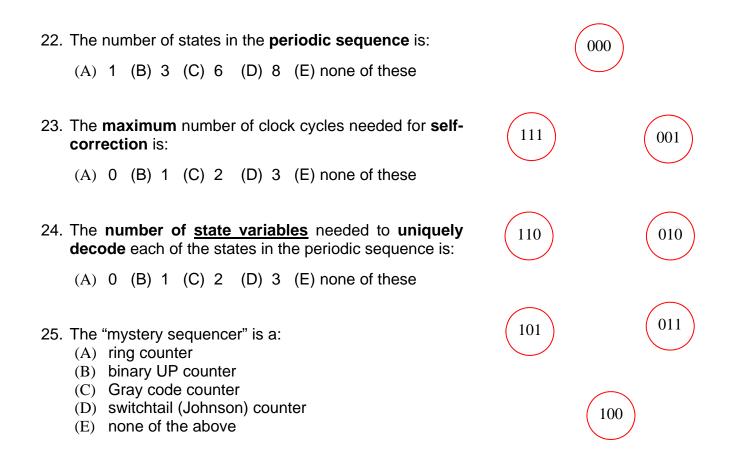

The following Verilog program applies to questions 22 through 25 (complete the PS-NS table and draw the state transition diagram before answering the questions):

```

module mystery_seq2(CLK, Q);

input wire CLK;

output reg [2:0] Q;

reg [2:0] next_Q;

always @ (posedge CLK) begin

Q <= next_Q;

end

always @ (Q) begin

next_Q[2] = Q[1] & (Q[2] | Q[0]);

next_Q[1] = Q[0];

next_Q[0] = ~Q[2];

end

endmodule

```

| Q2 | Q1 | Q0 | Q2* | Q1* | Q0* |

|----|----|----|-----|-----|-----|

| 0  | 0  | 0  |     |     |     |

| 0  | 0  | 1  |     |     |     |

| 0  | 1  | 0  |     |     |     |

| 0  | 1  | 1  |     |     |     |

| 1  | 0  | 0  |     |     |     |

| 1  | 0  | 1  |     |     |     |

| 1  | 1  | 0  |     |     |     |

| 1  | 1  | 1  |     |     |     |

The following Verilog program applies to questions 26 and 27:

```

module pmbc(CLK, D, Q);

input wire CLK;

input wire [3:0] D;

output reg [3:0] Q;

reg [3:0] next_Q;

always @ (posedge CLK) begin

Q <= next_Q;

end

always @ (Q) begin

if (Q == D) begin

next_Q = 4'b0000;

end

else begin

next_Q[0] = ~Q[0];

next_Q[1] = Q[1] ^ Q[0];

next_Q[2] = Q[2] \wedge (Q[1] \& Q[0]);

next_Q[3] = Q[3] ^ (Q[2] & Q[1] & Q[0]);

end

end

endmodule

```

26. To create a (4-bit) **binary** (i.e. **modulo 16**) counter, the data inputs D[3:0] should be: (A) 0 0 0 0

- $(\mathbf{n}) \quad \mathbf{0} \quad \mathbf{0}$

- (B) **1 0 0 1**

- (C) **1 0 1 0**

- (D) **1 1 1 1**

- (E) none of the above

27. To create a BCD (i.e. modulo 10) counter, the data inputs D[3:0] should be:

- $(A) \ \ \textbf{0} \ \ \textbf{0} \ \ \textbf{0} \ \ \textbf{0}$

- (B) **1 0 0 1**

- (C) **1 0 1 0**

- (D) 1 1 1 1

- (E) none of the above

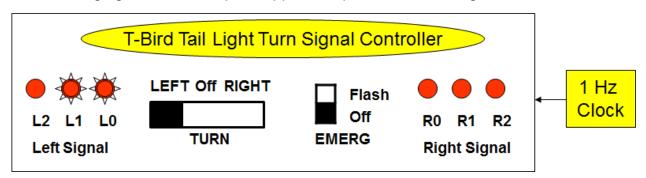

The following figure and description applies to questions 28 through 30:

Illustrated above is an automotive turn signal where each "tail light" consists of three LEDs, illuminated in a "building dot" mode to indicate the turn direction. The "left" or "right" turn direction is selected by a 3-position (single pole) switch with a "center off" position (like a "real" automotive turn signal). The left or right building dot sequence should continuously repeat as long as the LEFT or RIGHT input is asserted (note these inputs are *mutually exclusive* based on the physical construction of the switch); when LEFT and RIGHT are both negated (i.e., the TURN switch is in the "center off" position), all LEDs should be off. An "emergency flash" mode (in which all the tail lights alternate between the on and off states) is controlled by the EMERG input. If the "emergency flash mode" is selected, the six lights should alternate between the "all on" and "all off" states and the LEFT and RIGHT inputs should be ignored.

- 28. If designed as a **Mealy model** where the **minimum number of state variables possible** is used (per solution shown in the practice homework), the total number of **macrocells** needed to realize the turn signal controller will be:

- (A) **3**

- (B) **6**

- (C) **8**

- (D) **9**

- (E) none of the above

- 29. If designed as a **Moore model** where the **minimum number of state variables possible** is used (per solution shown in textbook on pp. 570-576), the total number of **macrocells** needed to realize the turn signal controller will be:

- (A) **3**

- (B) **6**

- (C) **8**

- (D) **9**

- (E) none of the above

- 30. If designed as a **Moore model** where the **output variables are the state variables**, the total number of **unused states** will be:

- (A) **56**

- (B) **64**

- (C) **256**

- (D) **512**

- (E) none of the above