#### **ECE 440**

#### **VCOs**

J. V. Krogmeier Purdue University, West Lafayette October 3, 2012

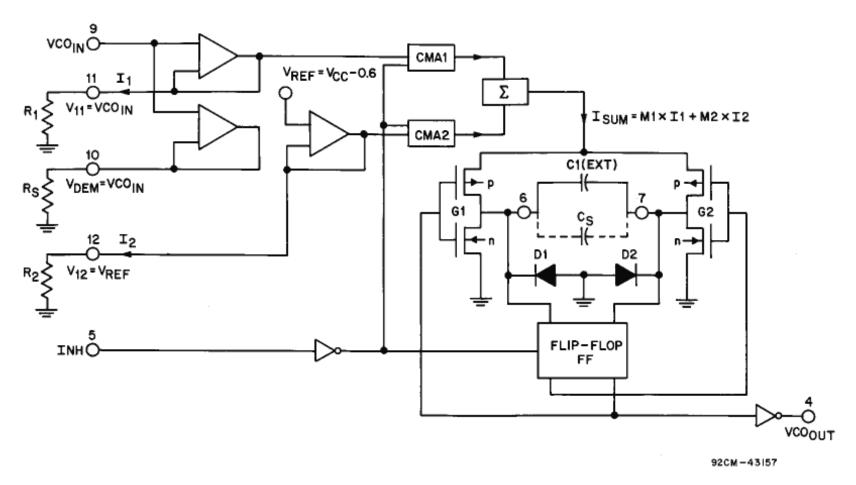

### From TI Application Report (Sept. 2002)

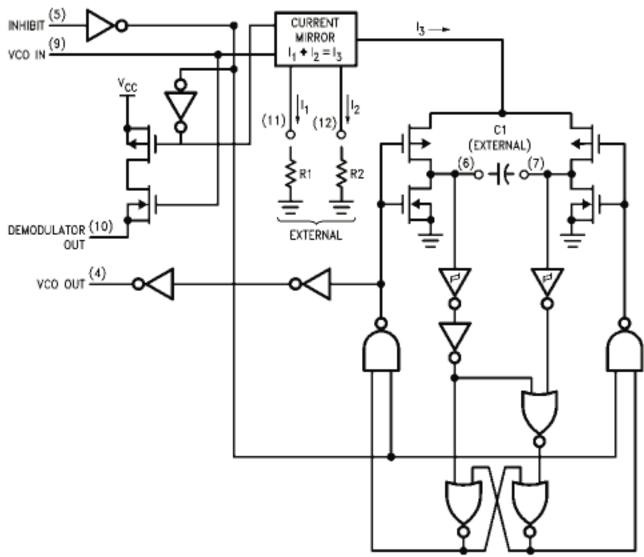

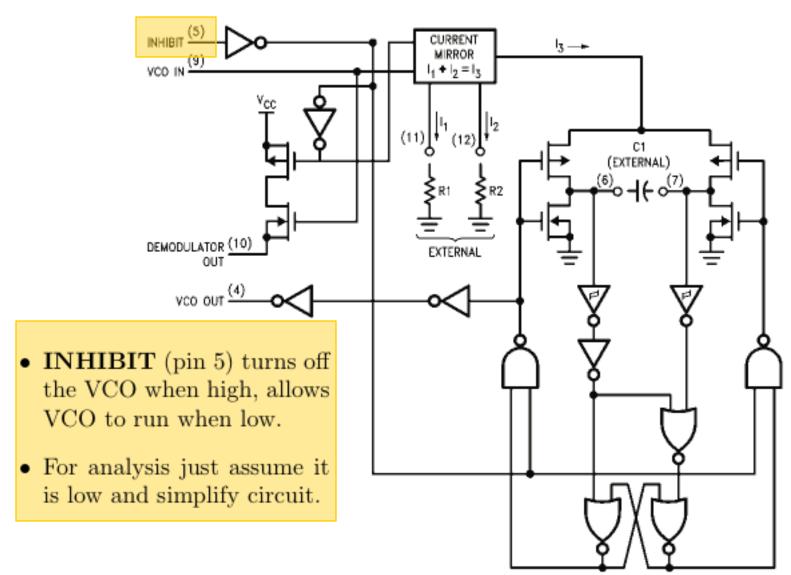

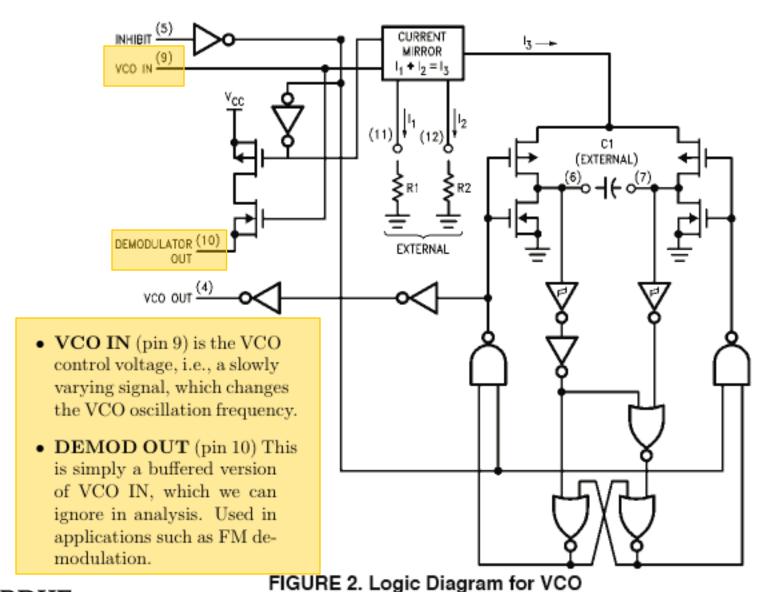

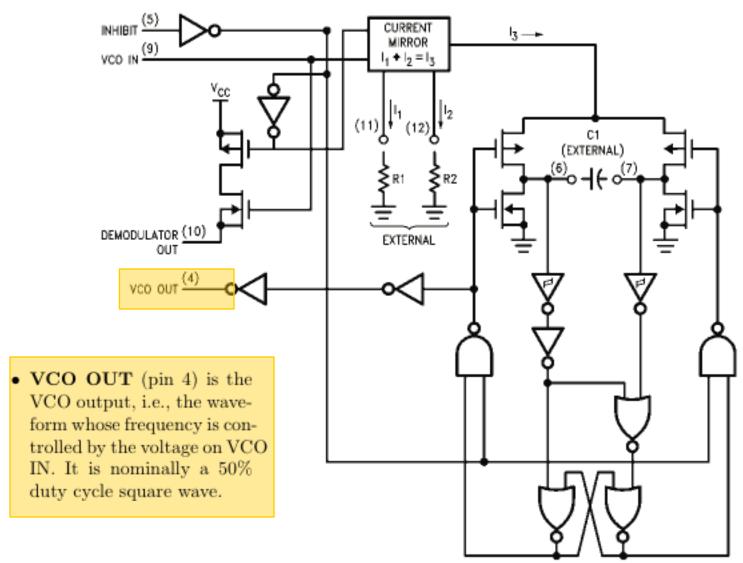

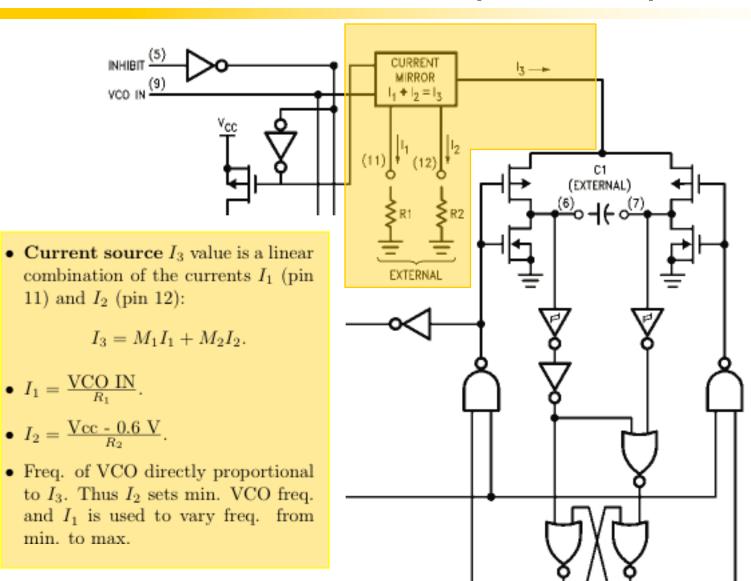

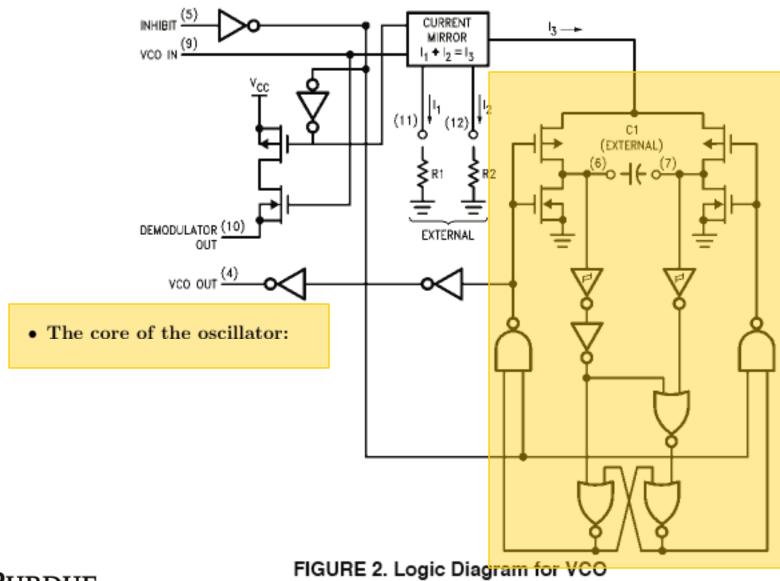

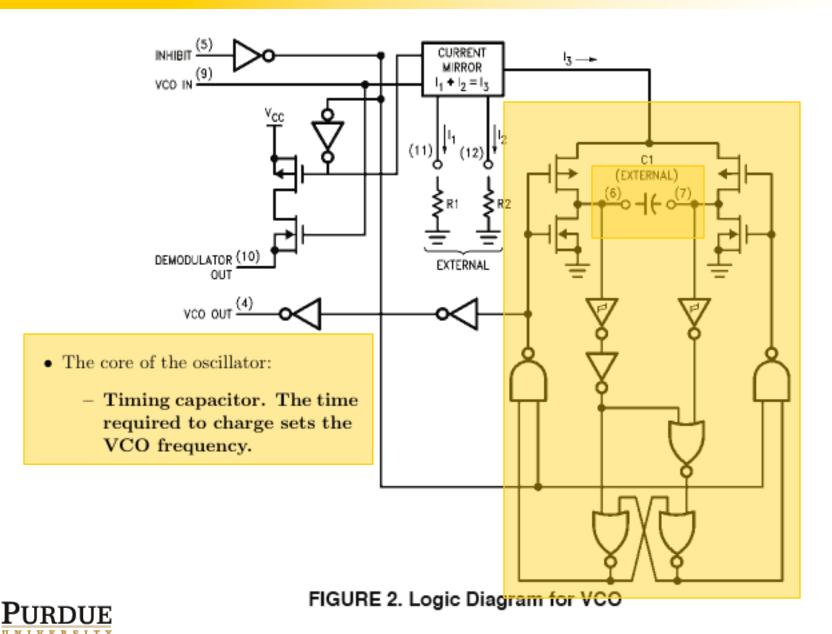

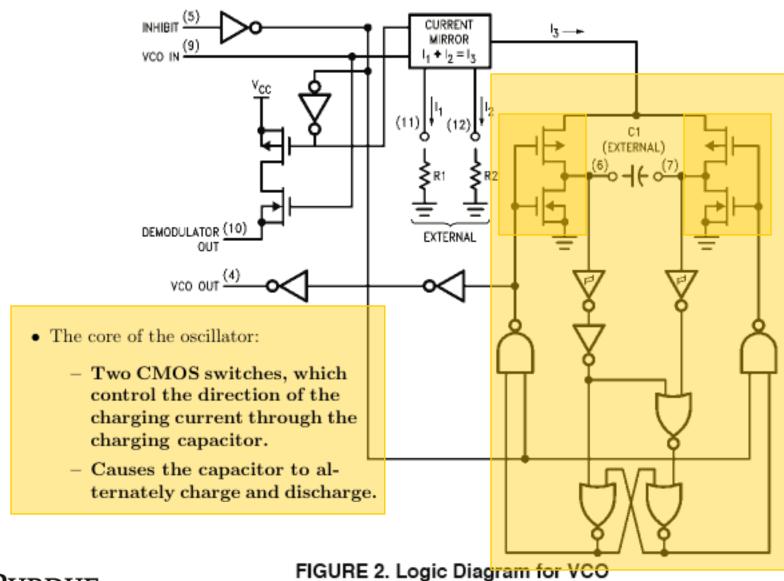

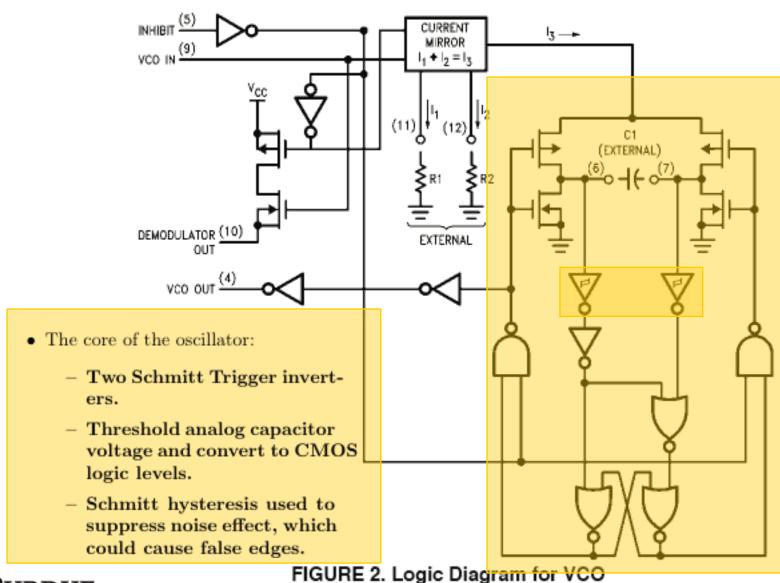

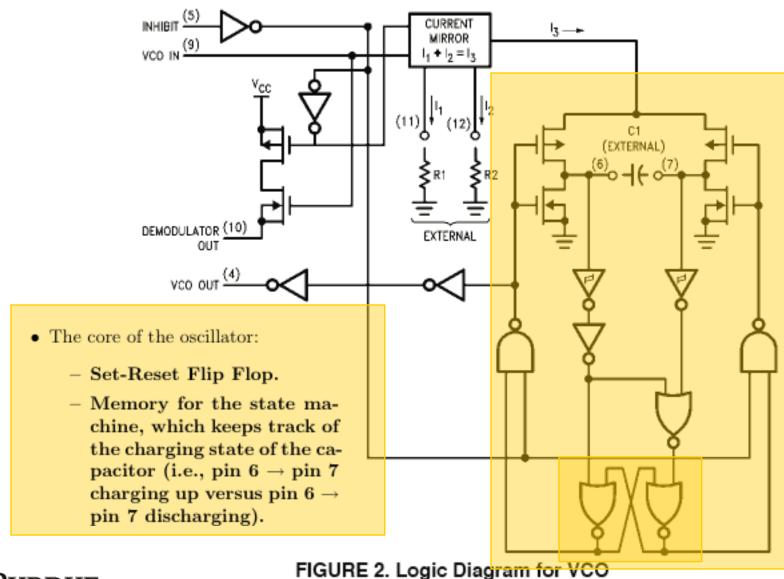

Figure 15. VCO Portion of CD74HC4046A/7046A Functional Block Diagram

CWSA

#### **Need Simple Model for Analysis**

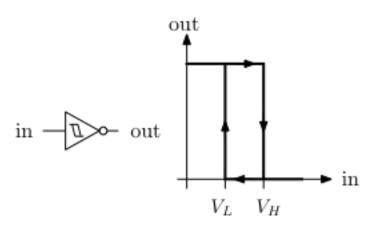

#### Model for Schmitt Trigger inverter

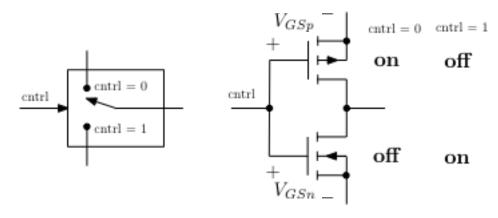

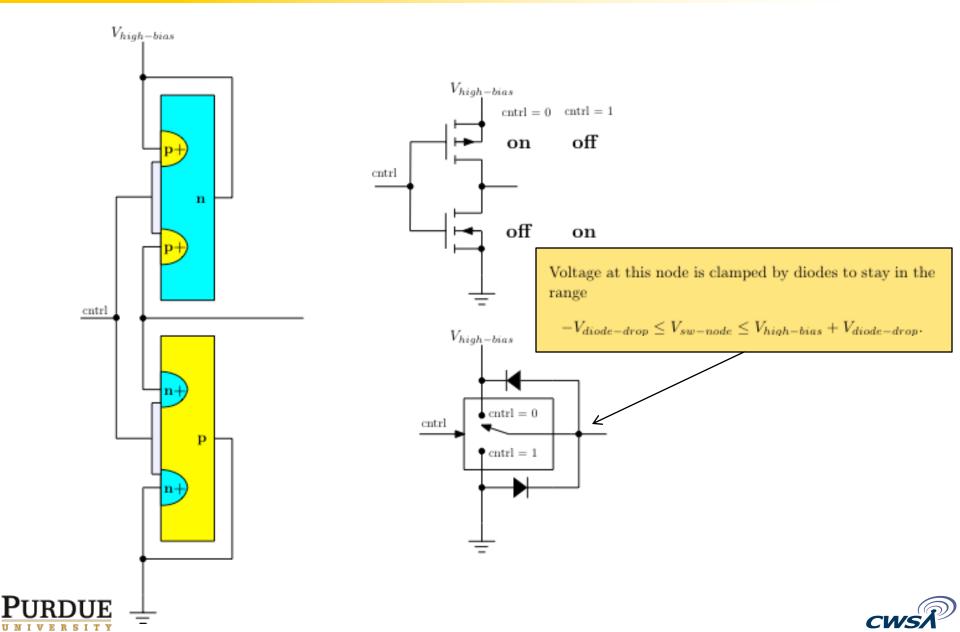

#### Model for CMOS switch

- Top transistor is p-channel enhancement mode.

- Therefore, is on for V<sub>GSp</sub> ≤ V<sub>tp</sub> < 0 V.</li>

- This happens when "cntrl" is low (a.k.a. 0).

- Bottom transistor is n-channel enhancement mode.

- Therefore, is on for V<sub>GSn</sub> ≥ V<sub>tn</sub> > 0 V.

- This happens when "cntrl" is high (a.k.a. 1).

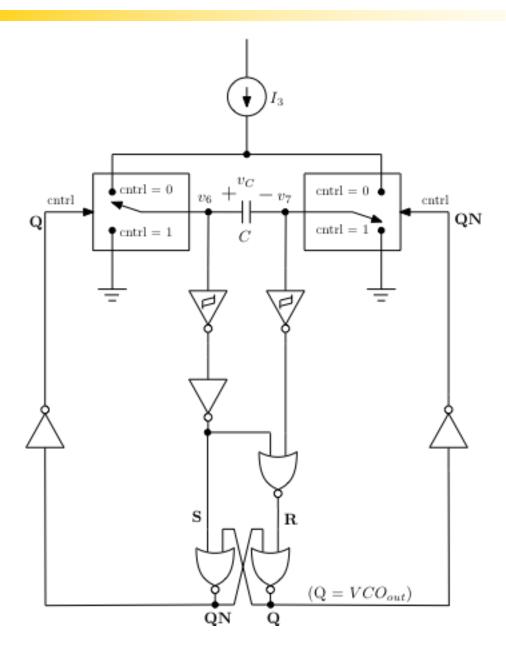

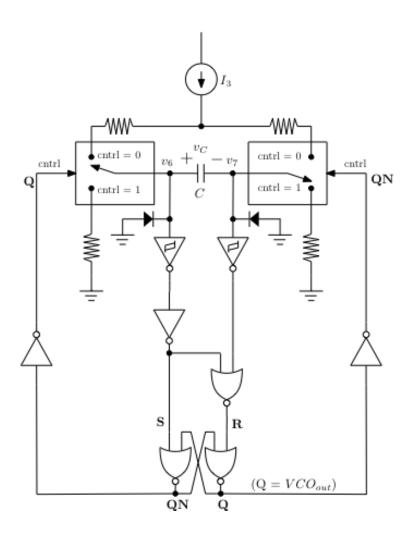

## **Simplest VCO Model**

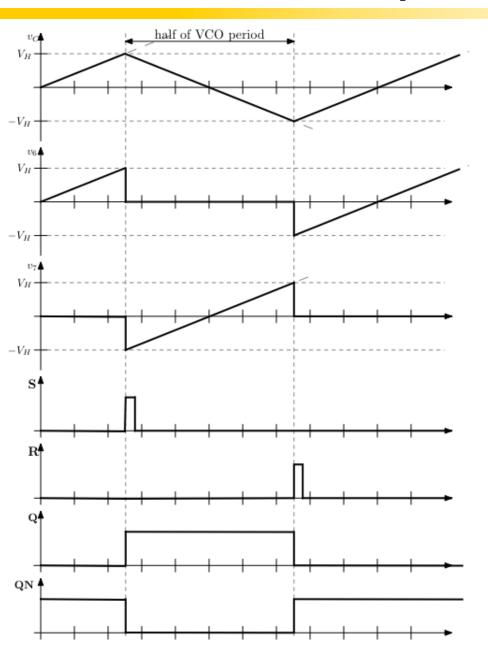

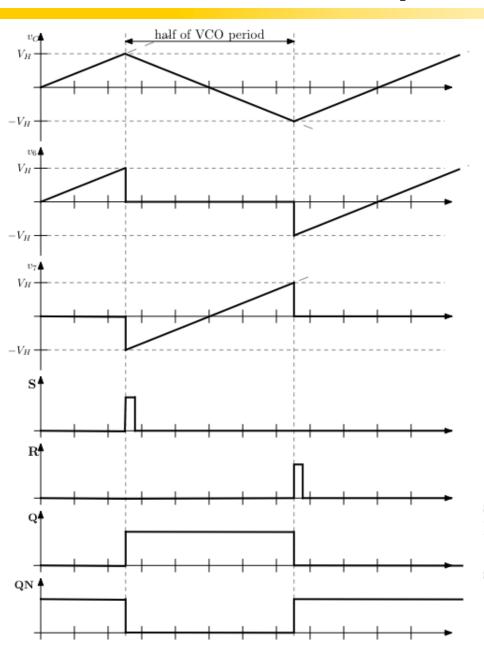

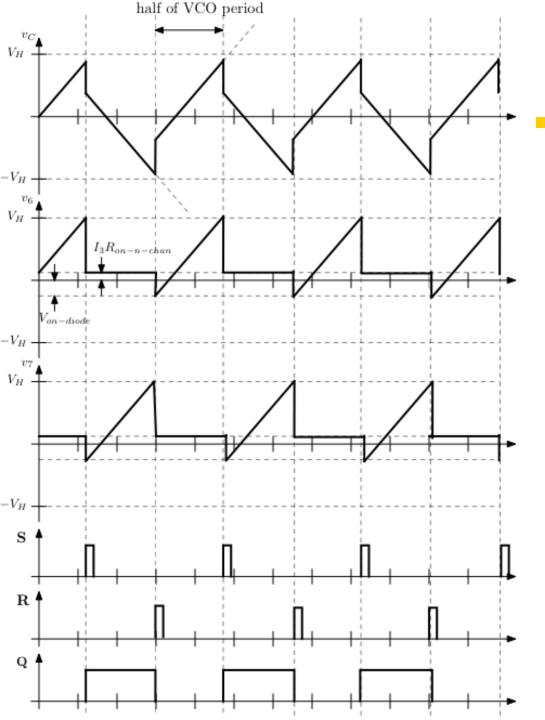

#### **Waveforms for Simplest Model**

Half of the  $Q = VCO_{out}$  period is time it takes to charge capacitor from  $-V_H$  to  $V_H$ with a constant current  $I_3$ :

$$2V_{H} = \frac{I_{3}}{C} \frac{T_{VCO}}{2}$$

$$\downarrow$$

$$T_{VCO} = \frac{4V_{H}C}{I_{3}}$$

$$f_{VCO} = \frac{I_{3}}{4V_{H}C}$$

#### **Waveforms for Simplest Model**

Half of the  $Q = VCO_{out}$  period is time it takes to charge capacitor from  $-V_H$  to  $V_H$ with a constant current  $I_3$ :

$$2V_{H} = \frac{I_{3}}{C} \frac{T_{VCO}}{2}$$

$$\downarrow$$

$$T_{VCO} = \frac{4V_{H}C}{I_{3}}$$

$$f_{VCO} = \frac{I_{3}}{4V_{H}C}$$

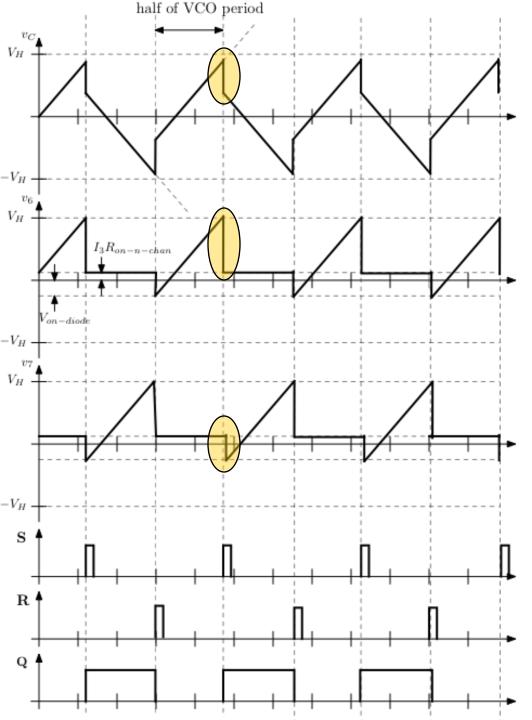

Only one problem with model: It's a bit too simple and the VCO waveforms do not look quite like these.

Issue is our overly simple model for the CMOS switches.

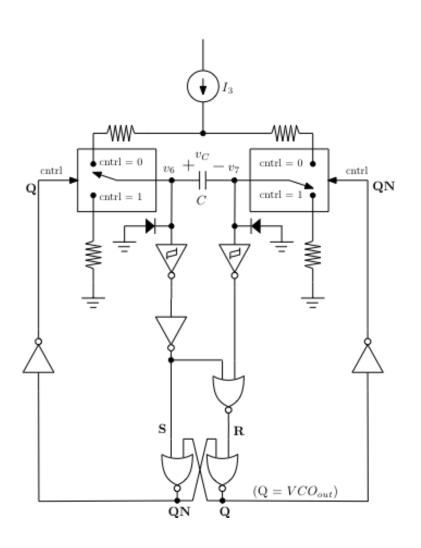

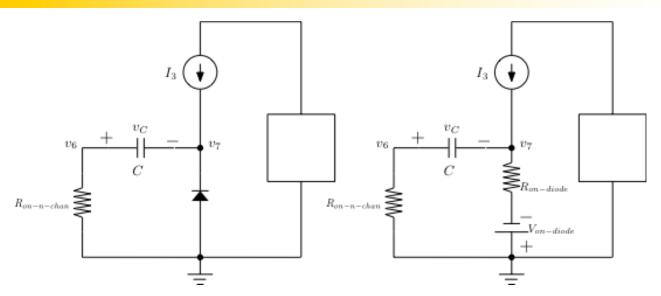

## **Improved Model of CMOS Switches**

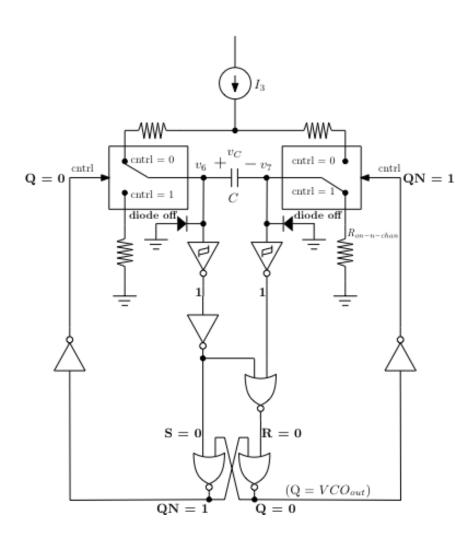

#### **Better VCO Model**

- Diodes from nMOS transistors included.

- Diodes from pMOS transitors not needed since they do not turn on in normal operation.

- □ nMOS on resistances are modeled ( $R_{on-n-chan}$  from bottom of switches to gnd).

- pMOS on resitances have no effect since in series with I<sub>3</sub> source.

# Better VCO Model – Summary of Operation Starting from Capacitor Uncharged and Q=0

- 1. Cap charges up until node 6 voltage reaches  $V_H > 0$  threshold. Node 7 voltage small positive constant.

- FF changes to Q = 1 causing switches to reverse. Node 7 is clamped to -0.7 V partially discharging cap.

- 3. Clamping diode turns off and cap continues to discharge (i.e., charge in opposite polarity) until node 7 voltage reaches  $V_H > 0$ . Node 6 voltage small positive constant.

- 4. FF changes to Q = 0 causing switches to reverse. Node 6 is clamped to -0.7 V partially discharging cap.

- Clamping diode turns off. GOTO step 1.

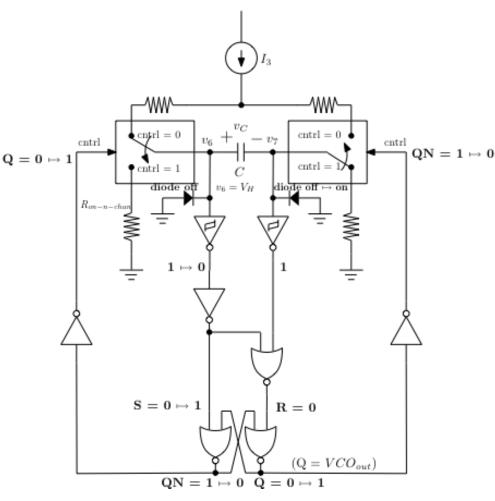

#### Better VCO Model – Charging Nodes 6 → 7

- 1. Cap charges up until node 6 voltage reaches  $V_H > 0$  threshold. Node 7 voltage small positive constant.

- FF changes to Q = 1 causing switches to reverse. Node 7 is clamped to -0.7 V partially discharging cap.

- 3. Clamping diode turns off and cap continues to discharge (i.e., charge in opposite polarity) until node 7 voltage reaches  $V_H > 0$ . Node 6 voltage small positive constant.

- 4. FF changes to **Q** = **0** causing switches to reverse. Node 6 is clamped to -0.7 V partially discharging cap.

- 5. Clamping diode turns off. GOTO step 1.

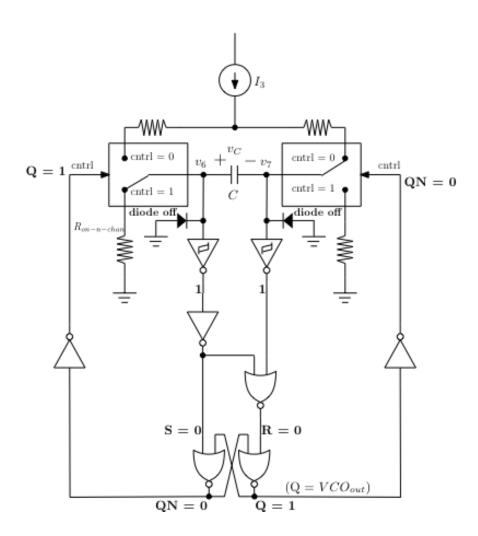

# Better VCO Model – Charging Nodes $6 \rightarrow 7$ to Discharging Nodes $6 \rightarrow 7$

- 1. Cap charges up until node 6 voltage reaches  $V_H > 0$  threshold. Node 7 voltage small positive constant.

- 2. FF changes to Q = 1 causing switches to reverse. Node 7 is clamped to -0.7 V partially discharging cap.

- 3. Clamping diode turns off and cap continues to discharge (i.e., charge in opposite polarity) until node 7 voltage reaches  $V_H > 0$ . Node 6 voltage small positive constant.

- 4. FF changes to Q = 0 causing switches to reverse. Node 6 is clamped to -0.7 V partially discharging cap.

- Clamping diode turns off. GOTO step 1.

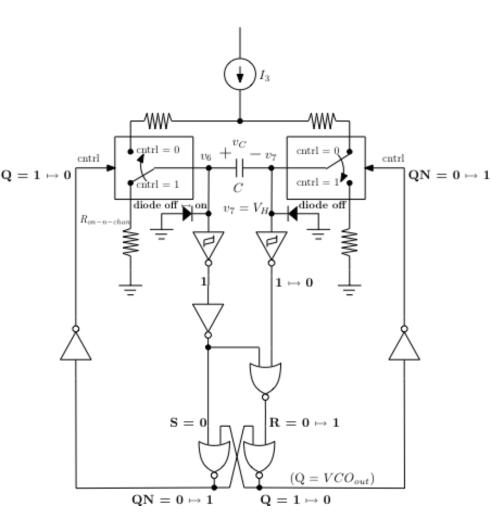

#### Better VCO Model – Discharging Nodes 6 → 7

- 1. Cap charges up until node 6 voltage reaches  $V_H > 0$  threshold. Node 7 voltage small positive constant.

- 2. FF changes to Q = 1 causing switches to reverse. Node 7 is clamped to -0.7 V partially discharging cap.

- 3. Clamping diode turns off and cap continues to discharge (i.e., charge in opposite polarity) until node 7 voltage reaches  $V_H > 0$ . Node 6 voltage small positive constant.

- 4. FF changes to **Q** = **0** causing switches to reverse. Node 6 is clamped to -0.7 V partially discharging cap.

- 5. Clamping diode turns off. GOTO step 1.

## Better VCO Model – Discharging Nodes $6 \rightarrow 7$ to Charging Nodes $6 \rightarrow 7$

- 1. Cap charges up until node 6 voltage reaches  $V_H > 0$  threshold. Node 7 voltage small positive constant.

- 2. FF changes to Q = 1 causing switches to reverse. Node 7 is clamped to -0.7 V partially discharging cap.

- 3. Clamping diode turns off and cap continues to discharge (i.e., charge in opposite polarity) until node 7 voltage reaches  $V_H > 0$ . Node 6 voltage small positive constant.

- 4. FF changes to Q = 0 causing switches to reverse. Node 6 is clamped to -0.7 V partially discharging cap.

- 5. Clamping diode turns off. GOTO step 1.

# VCO Frequency Calculation

Half of  $Q = VCO_{out}$  period is time it takes to charge capacitor through a voltage difference of  $V_H + 0.7$  V with a constant current  $I_3$ :

$$\begin{array}{rcl} V_{H} + 0.7 & = & \frac{I_{3}}{C} \frac{T_{VCO}}{2} \\ & \downarrow & \\ T_{VCO} & = & \frac{2(V_{H} + 0.7)C}{I_{3}} \\ f_{VCO} & = & \frac{I_{3}}{2(V_{H} + 0.7)C} \end{array}$$

# VCO Frequency Calculation

Further refinements come from modeling the time required to transition from charging to discharging, which includes two components:

- Propagation time in gates, flip-flop, and CMOS switches T<sub>pd</sub>.

- Effect of diode clamping and RC decay T<sub>RC</sub>.

For all but the highest VCO frequencies, these effects should be minimal.

$$T_{VCO} = \frac{2(V_H + 0.7)C}{I_3} + 2T_{pd} + 2T_{RC}$$

$f_{VCO} = 1/T_{VCO}$

#### Estimation of 2<sup>nd</sup> Order Refinements

- For this it is easiest to use some reasonable numbers from the datasheets:

- $T_{pd} = 10$  to 14 ns.

- $V_{cc} = 5 \text{ V}.$

- $R_1 = R_2 = 10 \text{ k}\Omega$ .

- $VCO_{in} = 3 \text{ V} \rightarrow I_1 = 0.3 \text{ mA}$

- $V_{ref} = V_{cc}$  0.6 V = 4.4 V  $\rightarrow I_2$  = 0.44 mA

- $M_1 = M_2 = 7 \rightarrow I_3 = 5.2 \text{ mA}$

- Voltage drop due to nMOS on resistance about 0.15 V  $\rightarrow$   $R_{on-n-1}$   $C_{chan} = 30 \ \Omega$

- $V_H = 1.1 \text{ V}$

- □ Then can use simple model for clamping diode to calculate  $T_{BC}$ .

#### Calculation of $T_{RC}$

- For simplicity assume  $R_{on-diode} = 0 \Omega$ .

- Assume switching occurs at t = 0. Circuit shown above is for t > 0.

- Summary at  $t = 0^-$ :

$$-v_6(0^-) = 1.1 \text{ V}$$

$$-v_7(0^-) = 0.15 \text{ V}$$

$$-i_C(0^-) = I_3 = 5.2 \text{ mA}$$

$$-v_C(0^-) = 0.95 \text{ V}$$

**PURDUE** • Summary at  $t = 0^+$ :  $v_C(0^+) = 0.95 \text{ V}$

### Calculation of $T_{RC}$ (cont'd.)

While the diode is forward biased can show:

$$- v_6(t) = 0.25e^{-t/1.5\text{ns}} \text{ V}$$

$$- v_7(t) = -0.7 \text{ V}$$

$$- i_C(t) = -8.3e^{-t/1.5\text{ns}} \text{ mA}$$

$$- v_C(t) = 0.7 + 0.25e^{-t/1.5\text{ns}} \text{ V}$$

$$- i_{diode}(t) = 8.3e^{-t/1.5\text{ns}} - 5 \text{ mA}$$

- Diode turns off at the time  $t_*$  where  $i_{diode}(t_*) = 0$ , which is  $t_* = -1.5 \ln(5/8.3) = 0.76$  ns.

- At  $t = t_*$ :

$$-v_6(t_*) = 0.15 \text{ V}$$

$$-v_7(t_*) = -0.7 \text{ V}$$

$$-i_C(t_*) = -5 \text{ mA}$$

$$-v_C(t_*) = 0.85 \text{ V}$$

$$-i_{diode}(t_*) = 0 \text{ mA}$$

### Calculation of $T_{RC}$ (cont'd.)

- For t > t\*, the capacitor continues to discharge owing to the dc current source I3 = 5 mA.

- That is

$$v_C(t) = -\left(100 \frac{\text{mV}}{\text{ns}}\right) (t - 0.76 \text{ns}) + 850 \text{ mV}$$

- To summarize: The above calculation yields T<sub>RC</sub> = 0.76 ns, which is insignificant in comparison to propagation delays T<sub>pd</sub>.

- Note that modeling the diode on resistance will increase the RC time.

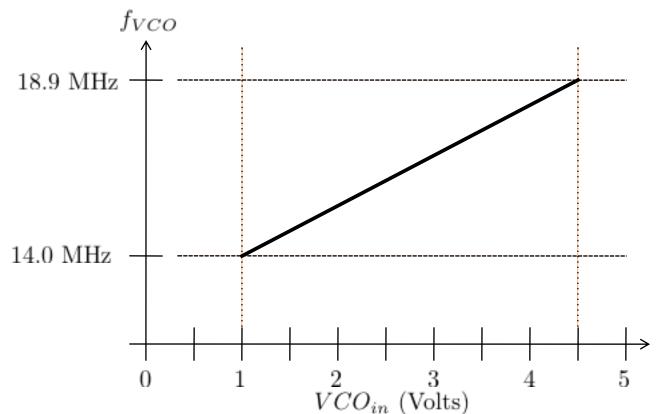

### **VCO Frequency Characteristic**

- For the circuit parameters previously given the nominal oscillator frequency is  $f_{VCO} = 16.6 \text{ MHz}$ .

- If we vary the VCO input voltage over the allowed range from 1.0 V to 4.5 V we have

14.0 MHz

$$\leq f_{VCO} \leq 18.9$$

MHz.