# Chapter 13 Small-Signal Modeling and Linear Amplification

#### Microelectronic Circuit Design

Richard C. Jaeger Travis N. Blalock

## Chapter Goals

#### Understanding of concepts related to:

- Transistors as linear amplifiers

- dc and ac equivalent circuits

- Use of coupling and bypass capacitors and inductors to modify dc and ac equivalent circuits

- Concept of small-signal voltages and currents

- Small-signal models for diodes and transistors

- Identification of common-source and common-emitter amplifiers

- Amplifier characteristics such as voltage gain, input and output resistances, and linear signal range

- Rule-of-thumb estimates for the voltage gain of common-emitter and common-source amplifiers.

## Introduction to Amplifiers

- Amplifiers usually use electronic devices operating in the Active Region

- A BJT is used as an amplifier when biased in the forward-active region

- The FET can be used as amplifier if operated in the pinch-off or saturation region

- In these regions, transistors can provide high voltage, current and power gains

- Bias is provided to stabilize the operating point (the Q-Point) in the desired region of operation

- Q-point also determines

- Small-signal parameters of transistor

- Voltage gain, input resistance, output resistance

- Maximum input and output signal amplitudes

- Power consumption

## **BJT Amplifier Concept**

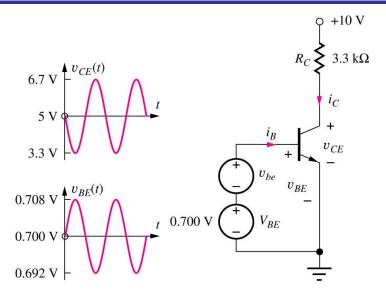

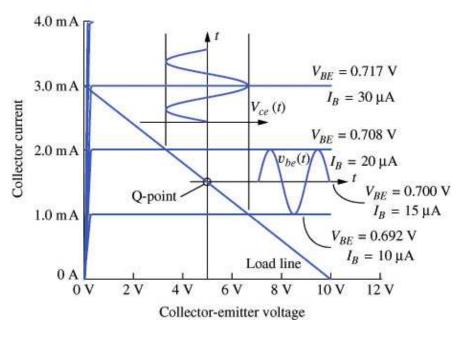

The BJT is biased in the active region by dc voltage source  $V_{BE}$ . Q-point is set at  $(I_C, V_{CE}) = (1.5 \text{ mA}, 5 \text{ V})$  with  $I_B = 15 \text{ }\mu\text{A}$   $(\beta_F = 100)$

Total base-emitter voltage is:  $v_{BE} = V_{BE} + v_{be}$

Collector-emitter voltage is:  $v_{CE} = 10 - i_C R_C$  This is the load line equation.

#### BJT Amplifier (cont.)

8 mV peak change in  $v_{BE}$  gives 5  $\mu$ A change in  $i_B$  and 0.5 mA change in  $i_C$ .

0.5 mA change in  $i_C$  produces a 1.65 V change in  $v_{CE}$ .

If changes in operating currents and voltages are small enough, then  $i_C$  and  $v_{CE}$  waveforms are undistorted replicas of the input signal.

A small voltage change at the base causes a large voltage change at collector. Voltage gain is given by:

$$A_{v} = \frac{V_{ce}}{V_{be}} = \frac{1.65 \angle 180^{\circ}}{0.008 \angle 0^{\circ}} = 206 \angle 180^{\circ} = -206$$

Minus sign indicates 180° phase shift between th einput and output signals.

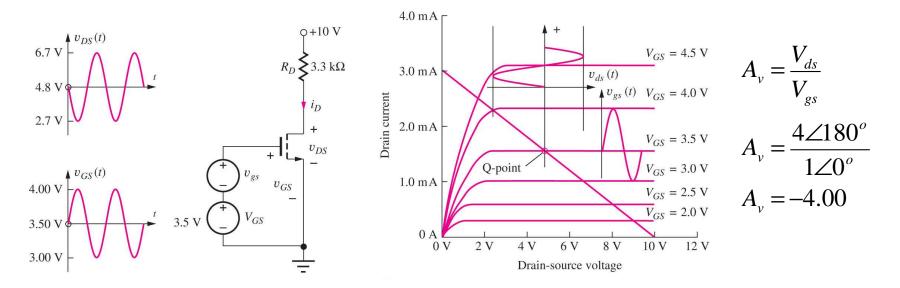

#### **MOSFET Amplifier Concept**

MOSFET is biased in active region by dc voltage source  $V_{GS}$ . Q-point is set at  $(I_D, V_{DS}) = (1.56 \text{ mA}, 4.8 \text{ V})$  with  $V_{GS} = 3.5 \text{ V}$

Total gate-source voltage is:  $v_{GS} = V_{GS} + v_{gs}$

1  $V_{p-p}$  change in  $v_{GS}$  yields 1.25  $mA_{p-p}$  change in  $i_D$  and a 4  $V_{p-p}$  change in  $v_{DS}$

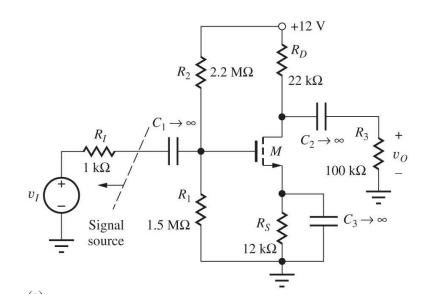

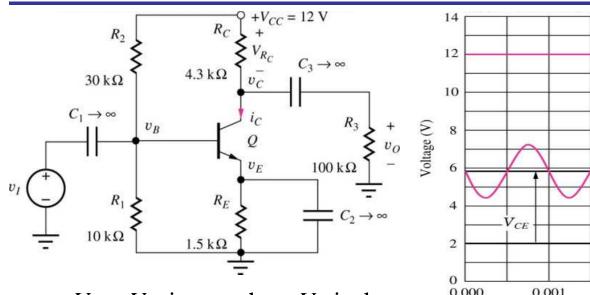

### Coupling and Bypass Capacitors

ac coupling through capacitors is used to inject ac input signal and extract output signal without disturbing Q-point Capacitors are designed to provide negligible impedance at frequencies of interest and provide open circuits at dc.

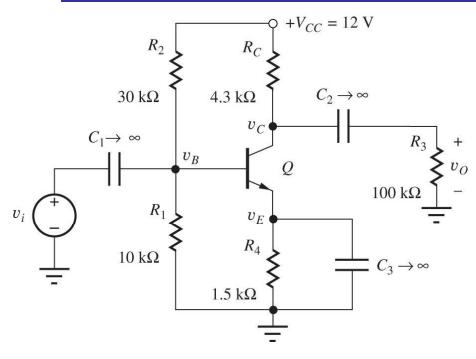

$C_1$  and  $C_2$  are low impedance coupling capacitors or dc blocking capacitors whose reactance at the signal frequency is designed to be negligible.

$C_3$  is a bypass capacitor that provides a low impedance path for ac current from emitter to ground, thereby removing  $R_{\rm E}$  (required for good Q-point stability) from the circuit when ac signals are considered.

## dc and ac Analysis – Two Step Analysis

#### dc analysis:

- Find dc equivalent circuit by replacing all capacitors by open circuits and inductors by short circuits.

- Find Q-point from dc equivalent circuit by using appropriate large-signal transistor model.

#### ac analysis:

- Find ac equivalent circuit by replacing all capacitors by short circuits, inductors by open circuits, dc voltage sources by ground connections and dc current sources by open circuits.

- Replace transistor by its small-signal model

- Use small-signal ac equivalent to analyze ac characteristics of amplifier.

- Combine end results of dc and ac analysis to yield total voltages and currents in the network.

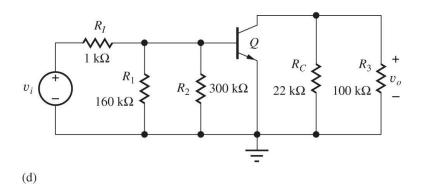

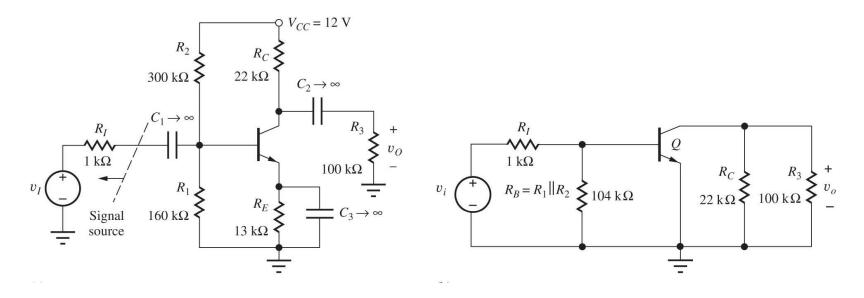

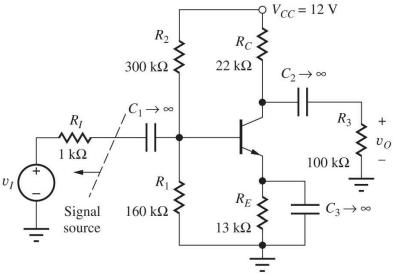

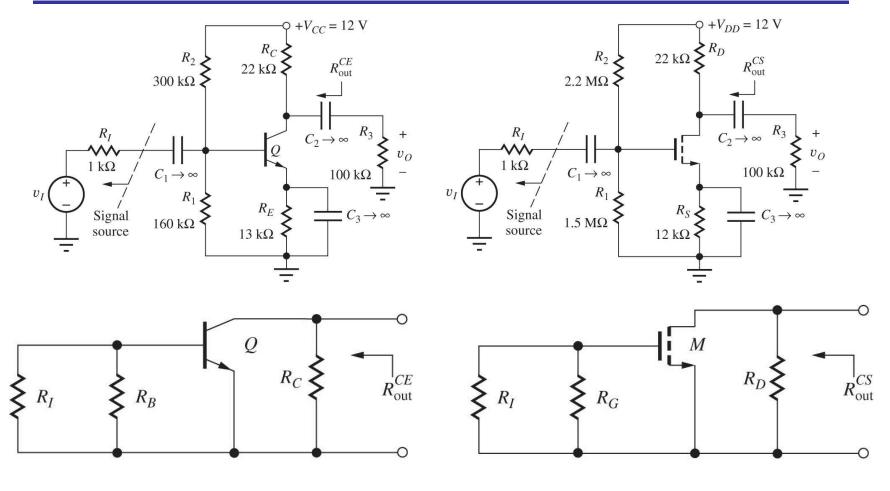

#### dc Equivalent Circuit for BJT Amplifier

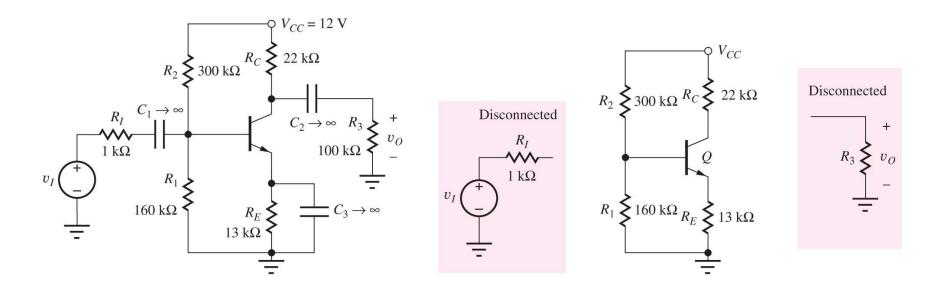

• All capacitors in the original amplifier circuit are replaced by open circuits, disconnecting  $v_I$ ,  $R_I$ , and  $R_3$  from circuit.

### ac Equivalent Circuit for BJT Amplifier

Capacitors are replaced by short circuits

$$R_B = R_1 || R_2 = 100 \text{k}\Omega || 300 \text{k}\Omega$$

$$R = R_C || R_3 = 22 \text{k}\Omega || 100 \text{k}\Omega$$

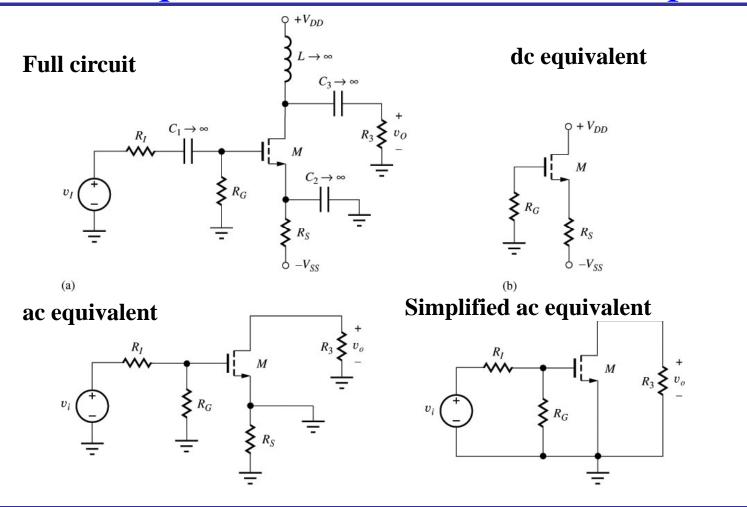

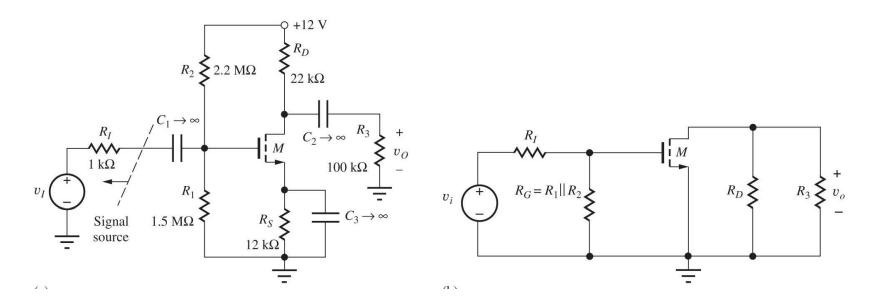

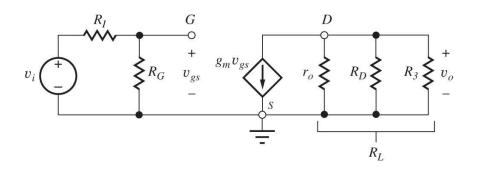

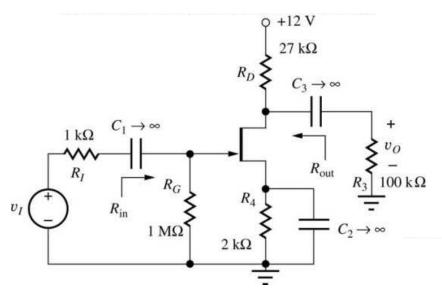

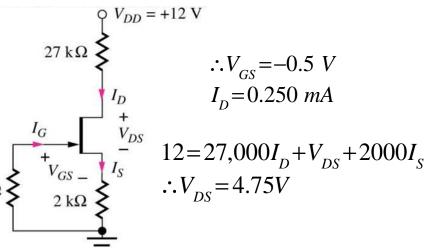

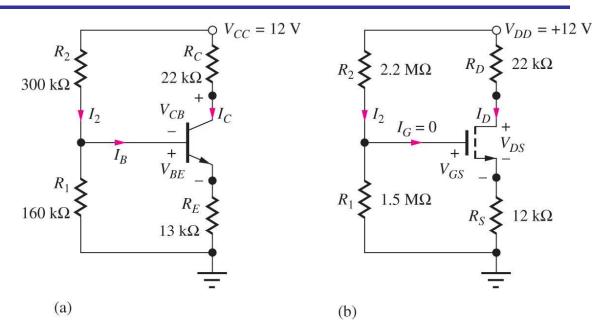

## dc and ac Equivalents for a MOSFET Amplifier

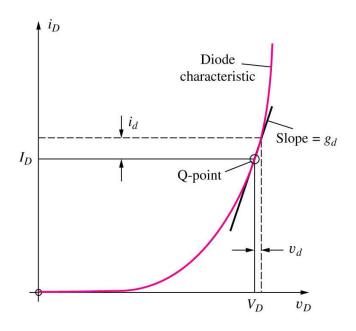

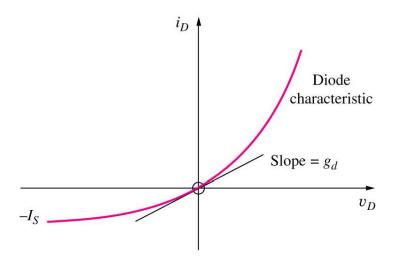

#### Diode Small-Signal Model

$$v_D = V_D + v_d$$

$$v_D = V_D + v_d$$

$$v_d \begin{cases} i_d \\ v_d \\ - \\ 0 \end{cases}$$

• The slope of the diode characteristic at the Q-point is called the **diode conductance** and is given by:

$$g_d = \frac{\partial i_D}{\partial v_D} \bigg|_{Q-point} = \frac{I_S}{V_T} \exp\left(\frac{V_D}{V_T}\right) = \frac{I_D + I_S}{V_T}$$

$$g_d \approx \frac{I_D}{V_T} \approx \frac{I_D}{0.025 \text{V}} = 40I_D \quad \text{for } I_D >> I_S$$

• **Diode resistance** is given by:

$$r_d = \frac{1}{g_d}$$

#### Diode Small-Signal Model (cont.)

$$v_D = V_D + v_d$$

$$v_D = V_D + v_d$$

$$v_d \begin{cases} i_d \\ v_d \\ - \\ 0 \end{cases}$$

- $g_d$  is small but non-zero for  $I_D = 0$  because slope of diode equation is nonzero at the origin.

- At the origin, the diode conductance and resistance are given by:

$$g_d = \frac{I_S}{V_T}$$

and  $r_d = \frac{V_T}{I_S}$

#### Definition of a Small-Signal

Now let's determine the largest magnitude of  $v_d$  that represents a small signal.

$$i_{D} = I_{S} \left[ \exp \left( \frac{v_{D}}{V_{T}} \right) - 1 \right] \qquad \therefore I_{D} + i_{d} = I_{S} \left[ \exp \left( \frac{V_{D} + v_{d}}{V_{T}} \right) - 1 \right]$$

$$I_{D} + i_{d} = I_{S} \left[ \exp \left( \frac{V_{D}}{V_{T}} \right) - 1 \right] + I_{S} \exp \left( \frac{v_{D}}{V_{T}} \right) \left[ \frac{v_{d}}{V_{T}} + \frac{1}{2} \left( \frac{v_{d}}{V_{T}} \right)^{2} + \frac{1}{6} \left( \frac{v_{d}}{V_{T}} \right)^{3} + \dots \right]$$

Subtracting  $I_D$  from both sides of the equation,

$$i_d = (I_D + I_S) \left| \frac{v_d}{V_T} + \frac{1}{2} \left( \frac{v_d}{V_T} \right)^2 + \frac{1}{6} \left( \frac{v_d}{V_T} \right)^3 + \dots \right|$$

For  $i_d$  to be a linear function of signal voltage  $v_d$ ,  $v_d << 2V_T = 0.05$  V or  $v_d \le 5$  mV. Thus  $v_d \le 5$  mV represents the requirement for small-signal (linear) operation of the diode.

$$: i_d = (I_D + I_S) \left( \frac{v_d}{V_T} \right) = g_d v_d \implies i_D = I_D + g_d v_d$$

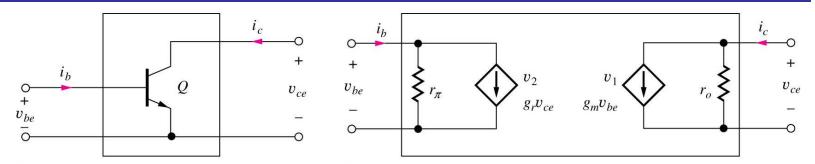

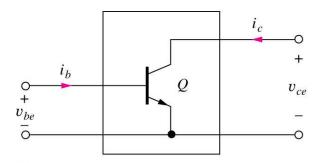

#### BJT Small-Signal Model (The Hybrid-Pi Model)

The bipolar transistor is assumed to be operating in the Forward-Active Region:

$$i_C \cong I_S \exp\left(\frac{v_{BE}}{V_T}\right) \left(1 + \frac{v_{CE}}{V_A}\right)$$

and  $i_B \cong \frac{i_C}{\beta_F}$   $\left(V_{CE} \ge V_{BE}\right)$

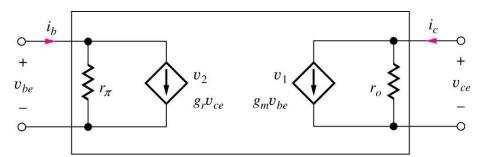

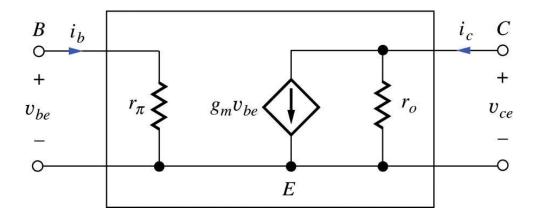

Using a two-port *y*-parameter network:

$$i_c = g_m v_{be} + g_o v_{ce}$$

$$i_b = g_\pi v_{be} + g_r v_{ce}$$

The port variables can represent either time-varying part of total voltages and currents or small changes in them away from Q-point values.

### BJT Small-Signal Model (The Hybrid-Pi Model)

$$i_c = g_m v_{be} + g_o v_{ce}$$

$$i_b = g_\pi v_{be} + g_r v_{ce}$$

$$i_C \cong I_S \exp\left(\frac{v_{BE}}{V_T}\right) \left(1 + \frac{v_{CE}}{V_A}\right)$$

$i_B \cong \frac{i_C}{\beta_E}$

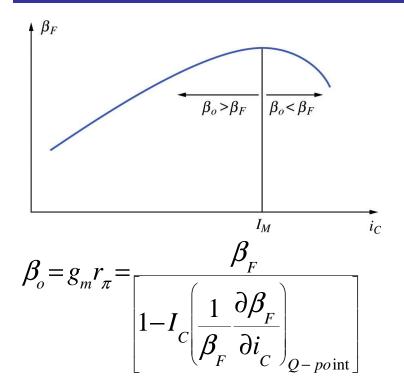

$\beta_o$  is called the **small-signal commonemitter current gain** of the BJT.

$$g_m = \frac{i_c}{v_{be}}\Big|_{v_{ce=0}} = \frac{\partial i_C}{\partial v_{BE}}\Big|_{Q\text{-point}} = \frac{I_C}{V_T}$$

$$g_o = \frac{i_c}{v_{ce}}\Big|_{v_{be=0}} = \frac{\partial i_C}{\partial v_{CE}}\Big|_{\text{Q-point}} = \frac{I_C}{V_A + V_T}$$

$$g_{\pi} = \frac{i_b}{v_{be}}\Big|_{v_{ce=0}} = \frac{\partial i_B}{\partial v_{BE}}\Big|_{\text{Q-point}} = \frac{I_C}{\beta_o V_T}$$

$$g_r = \frac{i_b}{v_{ce}}\Big|_{v_{be}=0} = \frac{\partial i_B}{\partial v_{CE}}\Big|_{Q\text{-point}} = 0$$

#### Current Gain & Intrinsic Voltage Gain

$\beta_o > \beta_F$  for  $i_C < I_M$ , and  $\beta_o < \beta_F$  for  $i_C > I_M$ . However, for simplicity  $\beta_F$  and  $\beta_o$  will be assumed to be equal Intrinsic voltage gain is defined by:

$$\mu_f = g_m r_o = \frac{I_C}{V_T} \left( \frac{V_A + V_{CE}}{I_C} \right) = \frac{V_A + V_{CE}}{V_T}$$

For  $V_{CE} \ll V_A$

$$\mu_f \cong \frac{V_A}{V_T} \cong 40V_A$$

$\mu_f$  represents the maximum voltage gain an individual BJT can provide and does not change with operating point.

#### BJT Hybrid-Pi Model - Summary

- The hybrid-pi small-signal model is the intrinsic representation of the BJT.

- Small-signal parameters are controlled by the Q-point and are independent of geometry of the BJT

Transconductance:

$$g_m = \frac{I_C}{V_T} \cong 40I_C$$

Input resistance:

$$r_{\pi} = \frac{\beta_o V_T}{I_C} = \frac{\beta_o}{g_m}$$

or  $\beta_o = g_m r_{\pi}$

Output resistance:

$$r_o = \frac{V_A + V_{CE}}{I_C} \cong \frac{V_A}{I_C}$$

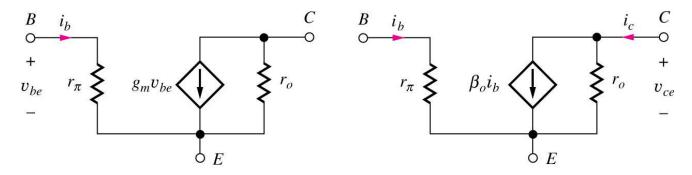

#### **Equivalent Forms of Small-Signal Model**

• Voltage-controlled current source  $g_m v_{be}$  can be transformed into current-controlled current source,

$$v_{be} = i_b r_{\pi}$$

$$g_m v_{be} = g_m i_b r_{\pi} = \beta_o i_b$$

$$i_c = \beta_o i_b + \frac{v_{ce}}{r_o} \cong \beta_o i_b$$

• Basic relationship  $i_c = \beta i_b$  is useful in both dc and ac analysis when the BJT is in the forward-active region.

#### **Small-Signal Definition**

$$\begin{split} i_C &= I_S \exp\left(\frac{v_{BE}}{V_T}\right) = I_S \exp\left(\frac{V_{BE} + v_{be}}{V_T}\right) & \therefore i_C = I_C + i_c = I_S \exp\left(\frac{V_{BE}}{V_T}\right) \exp\left(\frac{v_{be}}{V_T}\right) = I_C \exp\left(\frac{v_{be}}{V_T}\right) \\ I_C &+ i_c = I_C \left[1 + \left(\frac{v_{be}}{V_T}\right) + \frac{1}{2}\left(\frac{v_{be}}{V_T}\right)^2 + \frac{1}{6}\left(\frac{v_{be}}{V_T}\right)^3 + \cdots\right] \\ & \therefore i_c = I_C \left[\left(\frac{v_{be}}{V_T}\right) + \frac{1}{2}\left(\frac{v_{be}}{V_T}\right)^2 + \frac{1}{6}\left(\frac{v_{be}}{V_T}\right)^3 + \cdots\right] \end{split}$$

For linearity,  $i_c$  should be proportional to  $v_{be}$  with  $v_{be} \ll 2V_T$  or  $v_{be} \leq 0.005$  V.

$$i_C \cong I_C \left( 1 + \frac{v_{be}}{V_T} \right) = I_C + I_C \frac{v_{be}}{V_T} = I_C + g_m v_{be}$$

The change in  $i_c$  that corresponds to small-signal operation is:

$$\frac{i_c}{I_C} = \frac{v_{be}}{V_T} \le \frac{0.005V}{0.025V} = 0.200$$

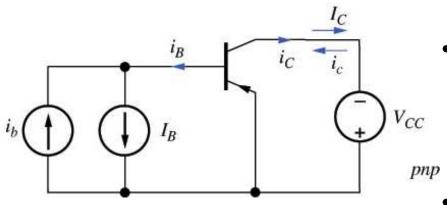

#### Small-Signal Model for pnp Transistor

• For the *pnp* transistor

$$i_B = I_B - i_b$$

$$i_C = I_C - i_c = \beta_F I_B - \beta_F i_b$$

- Signal current injected into base causes decrease in total collector current which is equivalent to increase in signal current entering collector.

- So the small-signal models for the npn and pnp devices are identical!

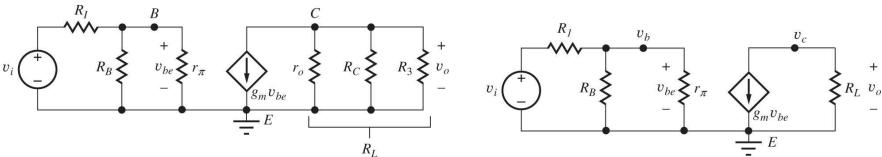

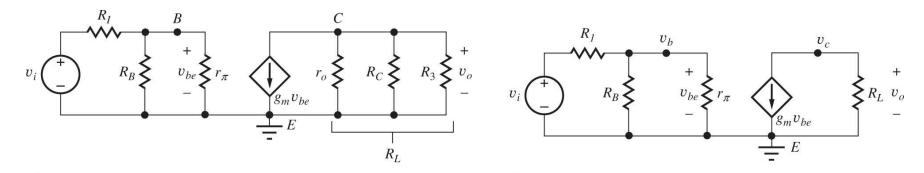

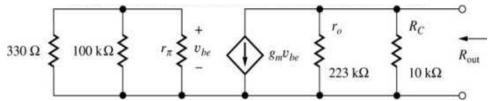

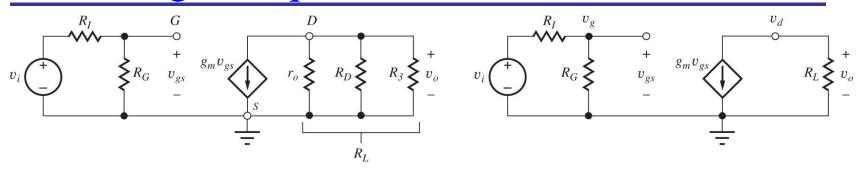

## Small-Signal Analysis - ac Equivalent Circuit

- ac equivalent circuit is constructed by assuming that all capacitances have zero impedance at signal frequency and dc voltage sources are ac ground.

- Assume that Q-point is already known.

## Small-Signal Equivalent Circuit

- Input voltage is applied to the base terminal

- Output signal appears at collector terminal

- Emitter is *common* to both input and output signals

Thus circuit is termed a Common-Emitter (C-E) Amplifier.

- The terminal gain of the C-E amplifier is the gain from the base terminal to the collector terminal

$$A_{vt}^{CE} = \frac{v_c}{v_b} = -g_m R_L$$

$R_L = r_o ||R_C|| R_3$

#### Input Resistance and Signal Source Gain

Define  $R_{iB}$  as the input resistance looking into the base of the transistor:

$$R_{iB} = \frac{v_b}{i_b} = r_{\pi}$$

The input resistance presented to  $v_i$  is:

$$R_{in} = R_I + R_B \| R_{iB} = R_I + R_B \| r_{\pi}$$

The signal source voltage gain is:

$$A_{v}^{CE} = \frac{v_{o}}{v_{i}} = \frac{v_{o}}{v_{b}} \frac{v_{b}}{v_{i}} = A_{vt}^{CE} \frac{R_{B} \| r_{\pi}}{R_{I} + R_{B} \| r_{\pi}}$$

#### "Rule of Thumb" Design Estimate

$$A_{v}^{CE} = A_{vt}^{CE} \frac{R_{B} \| r_{\pi}}{R_{I} + R_{B} \| r_{\pi}} \cong A_{vt}^{CE} \qquad A_{vt}^{CE} = -g_{m}R_{L} \qquad R_{L} = r_{o} \| R_{C} \| R_{3}$$

Typically:  $r_o >> R_C$  and  $R_3 >> R_C$   $A_v^{CE} \cong -g_m R_C = -40I_C R_C$

$I_{C}R_{C}$  represents the voltage dropped across collector resistor  $R_{C}$

A typical design point is  $I_C R_C = \frac{V_{CC}}{3}$

$$\therefore A_{\nu}^{CE} \cong -40 \frac{V_{CC}}{3} = 13.3 V_{CC}$$

To help account for all the approximations and have a number that is easy to remember, our "rule-of-thumb" estimate for the voltage gain becomes

$$A_{v}^{CE} \cong -10V_{CC}$$

#### Voltage Gain Example

- **Problem:** Calculate voltage gain, input resistance and maximum input signal level for a common-emitter amplifier with a specified Q-point

- Given data:  $\beta_F = 100$ ,  $V_A = 75$  V, Q-point is (0.245 mA, 3.39 V)

- **Assumptions:** Transistor is in active region,  $\beta_O = \beta_F$ . Signals are low enough to be considered small signals. Room temperature.

**Analysis:**

$$g_m = 40I_C = 40(0.245mA) = 9.80 \text{ mS}$$

$$g_m = 40I_C = 40(0.245mA) = 9.80 \ mS$$

$r_\pi = \frac{\beta_o}{g_m} = \frac{100}{9.8mS} = 10.2 \ k\Omega$

$$r_o = \frac{V_A + V_{CE}}{I_C} = \frac{75V + 3.39V}{0.245mA} = 320 \ k\Omega$$

$R_B = R_1 || R_2 = 160k\Omega || 300k\Omega = 104 \ k\Omega$

$$R_B = R_1 || R_2 = 160k\Omega || 300k\Omega = 104 k\Omega$$

$$R_L = r_o \|R_C\|R_L = 320k\Omega\|22k\Omega\|100k\Omega = 17.1 \ k\Omega$$

$R_B \|r_{\pi} = 104k\Omega\|10.2k\Omega = 9.29 \ k\Omega$

$$R_B || r_{\pi} = 104k\Omega || 10.2k\Omega = 9.29 \ k\Omega$$

#### Voltage Gain Example (cont.)

#### **Analysis (cont):**

$$A_{v} = -g_{m}R_{L} \left( \frac{R_{B} \| r_{\pi}}{R_{L} + R_{B} \| r_{\pi}} \right) = -9.8mS(17.1k\Omega) \left( \frac{9.29k\Omega}{1k\Omega + 9.29k\Omega} \right) = -168(0.903) = -151$$

$$R_{in} = R_I + R_B || r_{\pi} = 10.3 \ k\Omega$$

$$v_{be} = v_i \left( \frac{R_B \| r_{\pi}}{R_I + R_B \| r_{\pi}} \right)$$

$\therefore v_{be} \le 0.005V \to v_i \le 5mV \left( \frac{10.3k\Omega}{9.29k\Omega} \right) = 5.54 \ mV$

Check the rule-of-thumb estimate:  $A_{\nu}^{CE} \cong -10(12) = -120$  (ballpark estimate)

What is the maximum amplitude of the output signal:  $v_o \le 5.54 mV (-151) = 0.837 V$

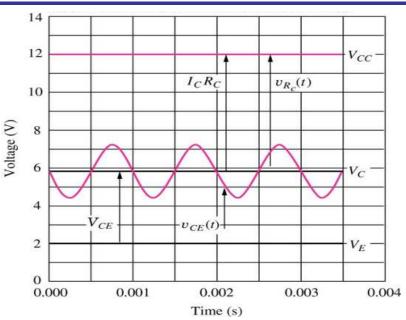

## Voltage Gain Example (cont.)

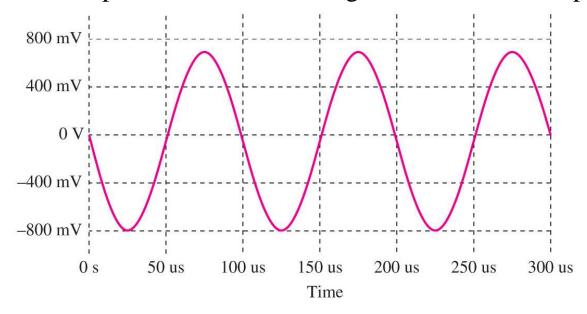

**Simulation Results:** The graph below presents the output voltage for an input voltage that is a 5-mV, 10-kHz sine wave.

Note that although the sine wave at first looks good, the positive and negative peak amplitudes are different indicating the presence of distortion. The input is near our small-signal limit for linear operation.

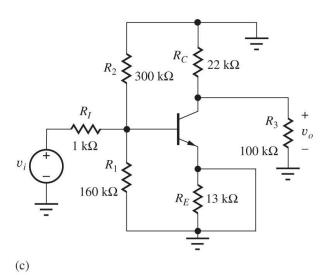

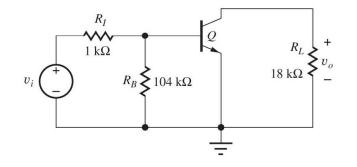

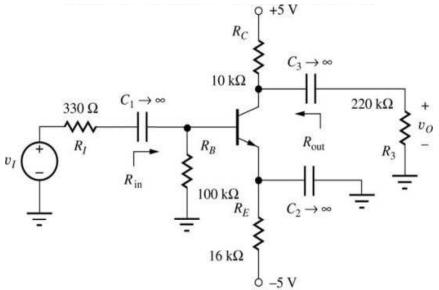

#### **Dual Supply Operation - Example**

- **Problem:** Find voltage gain, input and output resistances for the circuit above

- **Given data:**  $\beta_F = 65$ ,  $V_A = 50 \text{ V}$

- **Assumptions:** Active-region operation,  $V_{BE} = 0.7$  V, small signal operating conditions.

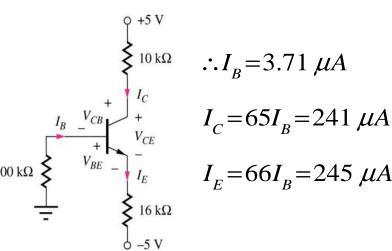

**Analysis:** To find the Q-point, the dc equivalent circuit is constructed.

$$10^{5}I_{B}+V_{BE}+(\beta_{F}+1)I_{B}(1.6\times10^{4})=5$$

$$5-10^4I_C-V_{CE}-(1.6\times10^4)I_E-(-5)=0$$

$$\therefore V_{CF} = 3.67 V$$

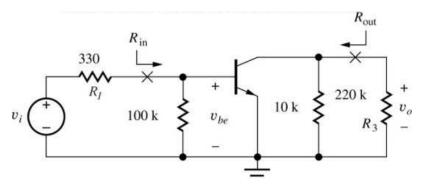

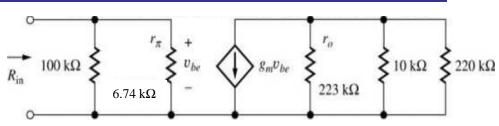

#### Dual Supply Operation - Example (cont.)

Next we construct the ac equivalent and simplify it.

$$g_{m} = 40I_{C} = 9.64 \times 10^{-3} S$$

$$r_{\pi} = \frac{\beta_{o}}{40I_{C}} = 6.74 k\Omega$$

$$r_{o} = \frac{V_{A} + V_{CE}}{I_{C}} = 223 k\Omega$$

$$R_{in} = R_B || r_{\pi} = 6.31 k\Omega$$

$$R_{out} = R_C || r_o = 9.57 \text{ k}\Omega$$

$$A_{v}^{CE} = \frac{v_{o}}{v_{i}} = -g_{m} \left( R_{out} \| R_{3} \right) \left( \frac{R_{in}}{R_{I} + R_{in}} \right) = -84.0$$

Gain Estimate:

$$A_v^{CE} \cong -10(V_{CC} + V_{EE}) = -100$$

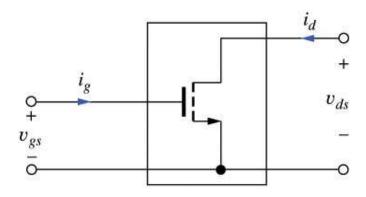

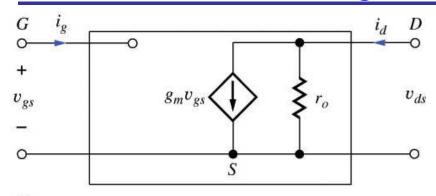

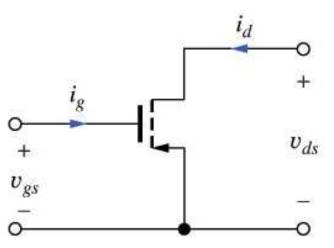

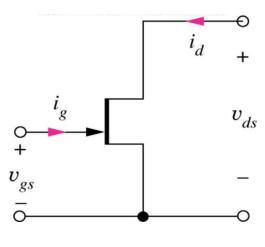

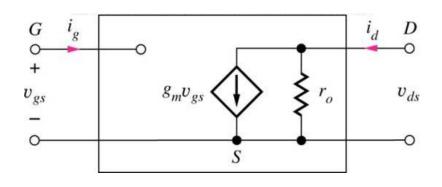

## **MOSFET Small-Signal Model**

Using a two-port y-parameter network,

$$i_g = g_\pi v_{gs} + g_r v_{ds}$$

$$i_d = g_m v_{gs} + g_o v_{ds}$$

The port variables can represent either time-varying part of total voltages and currents or small changes in them away from Q-point values.

$$g_{\pi} = \frac{i_g}{v_{gs}} \bigg|_{v_{ds}=0} = \frac{\partial i_G}{\partial v_{GS}} \bigg|_{\text{Q-point}}$$

$$g_r = \frac{i_g}{v_{ds}}\bigg|_{v_{ds}=0} = \frac{\partial i_G}{\partial v_{DS}}\bigg|_{\text{Q-point}}$$

$$g_m = \frac{i_d}{v_{gs}}\bigg|_{v_{ds}=0} = \frac{\partial i_D}{\partial v_{GS}}\bigg|_{\text{Q-point}}$$

$$g_o = \frac{i_d}{v_{ds}}\bigg|_{v_{ds}=0} = \frac{\partial i_D}{\partial v_{DS}}\bigg|_{\text{Q-point}}$$

$$I_G = 0$$

$$I_D = \frac{K_n}{2} \left( V_{GS} - V_{TN} \right)^2 \left( 1 + \lambda V_{DS} \right)$$

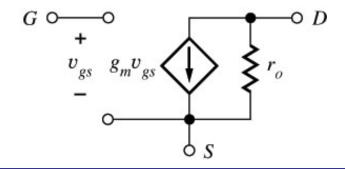

#### MOSFET Small-Signal Model (cont.)

$$i_g = g_{\pi} v_{gs} + g_r v_{ds}$$

$$i_d = g_m v_{gs} + g_o v_{ds}$$

$$I_G = 0$$

$$I_D = \frac{K_n}{2} \left( V_{GS} - V_{TN} \right)^2 \left( 1 + \lambda V_{DS} \right)$$

$$\begin{vmatrix} v_{ds} \\ - \end{vmatrix} g_{\pi} = \frac{\partial i_{G}}{\partial v_{GS}} \bigg|_{\text{Q-point}} = 0$$

$$g_r = \frac{\partial i_G}{\partial v_{DS}}\Big|_{\Omega\text{-point}} = 0$$

$$g_{m} = \frac{\partial i_{D}}{\partial v_{GS}} \bigg|_{\text{Q-point}} = \frac{K_{n}}{2} \left( V_{GS} - V_{TN} \right) \left( 1 + \lambda V_{DS} \right) = \frac{2I_{D}}{V_{GS} - V_{TN}}$$

$$g_o = \frac{\partial i_D}{\partial v_{DS}} \bigg|_{\text{Q-point}} = \lambda \frac{K_n}{2} (V_{GS} - V_{TN})^2 = \frac{\lambda I_D}{1 + \lambda V_{DS}} = \frac{I_D}{\frac{1}{\lambda} + V_{DS}}$$

## MOSFET Small-Signal Model - Summary

- Since gate is insulated from channel by gate-oxide input resistance of transistor is infinite.

- Small-signal parameters are controlled by the Q-point.

- For the same operating point, MOSFET has lower transconductance and an output resistance that is similar to the BJT.

Transconductance:

$$g_m = \frac{2I_D}{V_{GS} - V_{TN}} = \sqrt{2K_n I_D}$$

Output resistance:

$$r_o = \frac{1}{g_o} = \frac{1 + \lambda V_{DS}}{\lambda I_D} \cong \frac{1}{\lambda I_D}$$

Amplification factor for  $\lambda V_{DS} << 1$ :

$$\mu_f = g_m r_o = \frac{1 + \lambda V_{DS}}{\lambda I_D} \cong \frac{1}{\lambda} \sqrt{\frac{2K_n}{I_D}}$$

## **MOSFET Small-Signal Operation**

#### **Small-Signal Definition**

Assume

$$\lambda v_{DS} \ll 1$$

. Then

Assume

$$\lambda v_{DS} \ll 1$$

. Then  $i_D \cong \frac{K_n}{2} (v_{GS} - V_{TN})^2$  for  $v_{DS} \geq v_{GS} - V_{TN}$

For

$$v_{GS} = V_{GS} + v_{gs}$$

,

$$i_D = I_D + i_d = \frac{K_n}{2} \left[ \left( v_{GS} - V_{TN} \right)^2 + 2v_{gS} \left( V_{GS} - V_{TN} \right) + v_{gS}^2 \right]$$

$$\therefore i_d = \frac{K_n}{2} \left[ 2v_{gs} \left( V_{GS} - V_{TN} \right) + v_{gs}^2 \right]$$

For linearity,  $i_d$  should be proportional to  $v_{gs}$  and we require  $v_{gs}^2 << 2v_{gs}(V_{GS} - V_{TN})$

or

$$v_{gs} << 2(V_{GS} - V_{TN})$$

$\rightarrow$   $v_{gs} \le 0.2(V_{GS} - V_{TN})$

Since the MOSFET can be biased with  $(V_{GS} - V_{TN})$  equal to several volts, it can handle much larger values of  $v_{gs}$  than corresponding the values of  $v_{be}$  for the BJT.

The change in drain current that corresponds to small-signal operation is:

$$\frac{i_d}{I_D} = \left(\frac{g_m}{I_D}\right) v_{gs} \le \frac{2}{V_{GS} - V_{TN}} \left[ 0.2 \left(V_{GS} - V_{TN}\right) \right] \longrightarrow \frac{i_d}{I_D} \le 0.4$$

# **MOSFET Small-Signal Operation**

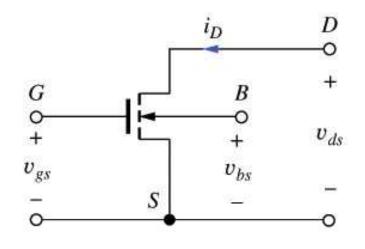

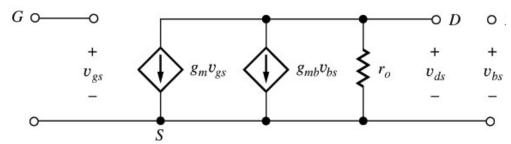

#### Body Effect in Four-terminal MOSFETs

Drain current depends on threshold voltage which in turn depends on  $v_{SB}$ . Back-gate transconductance is:

$$g_{mb} = \frac{\partial i_{D}}{\partial v_{BS}} \bigg|_{\text{Q-point}} = -\frac{\partial i_{D}}{\partial v_{SB}} \bigg|_{\text{Q-point}}$$

$$g_{mb} = -\left(\frac{\partial i_{D}}{\partial V_{TN}}\right) \left(\frac{\partial V_{TN}}{\partial v_{SB}}\right) \bigg|_{\text{Q-point}} = -(-g_{m}\eta) = g_{m}\eta$$

$0 < \eta < 3$  is called the back-gate transconductance parameter.

The bulk terminal is a reverse-biased diode. Hence, no conductance from the bulk terminal to other terminals.

# **MOSFET Small-Signal Operation**

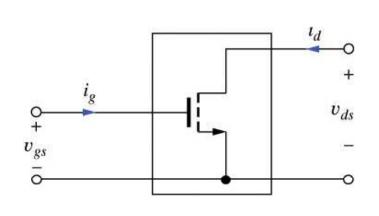

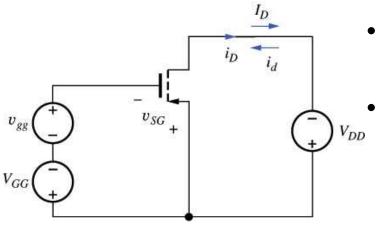

## Small-Signal Model for PMOS Transistor

- For a *PMOS* transistor  $v_{SG} = V_{GG} v_{gg}$   $i_D = I_D i_d$

- Positive signal voltage  $v_{gg}$  reduces sourcegate voltage of the PMOS transistor causing decrease in total current exiting the drain, equivalent to an increase in the signal current entering the drain.

- The NMOS and PMOS small-signal models are the same!

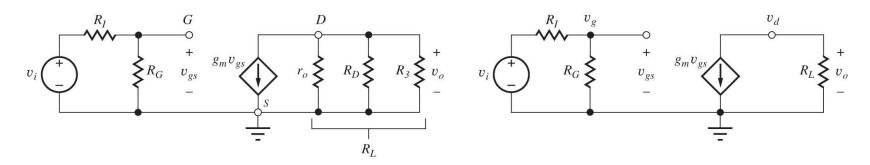

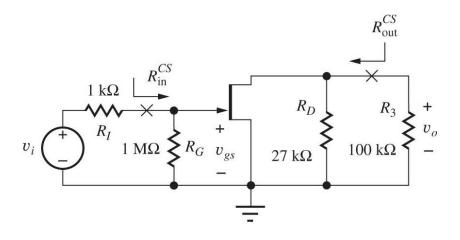

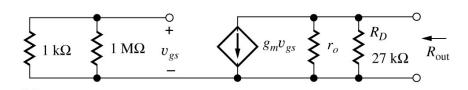

### Small-Signal Analysis - ac Equivalent Circuit

• ac equivalent circuit is constructed by assuming that all capacitances have zero impedance at signal frequency and dc voltage sources are ac ground.

#### Small-Signal Equivalent Circuit

- Input voltage is applied to the gate terminal

- Output signal appears at the drain terminal

- Source is *common* to both input and output signals Thus circuit is termed a Common-Source (C-S) Amplifier.

- The terminal gain of the C-S amplifier is the gain from the gate terminal to the drain terminal

$$A_{vt}^{CE} = \frac{v_d}{v_g} = -g_m R_L$$

$R_L = r_o ||R_D|| R_3$

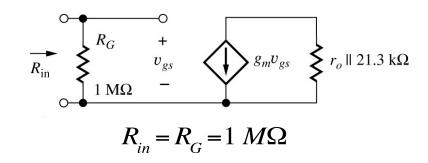

#### Input Resistance and Signal-Source Gain

Define  $R_{iG}$  as the input resistance looking into the base of the transistor.  $R_{in}$  is the resistance presented to  $v_i$ .

$$R_{iG} = \frac{v_g}{i_i} = R_G$$

$$R_{in} = R_I + R_G$$

The signal source voltage gain is:

$$A_{v}^{CS} = \frac{v_{o}}{v_{i}} = \frac{v_{o}}{v_{g}} \frac{v_{g}}{v_{i}} = A_{vt}^{CS} \frac{R_{G}}{R_{I} + R_{G}}$$

$$A_{v}^{CS} = -g_{m}R_{L} \left(\frac{R_{G}}{R_{I} + R_{G}}\right)$$

#### "Rule of Thumb" Design Estimate

$$A_{v}^{CS} = -g_{m}R_{L} \left( \frac{R_{G}}{R_{I} + R_{G}} \right) \cong A_{vt}^{CS} \qquad A_{vt}^{CS} = -g_{m}R_{L} \qquad R_{L} = r_{o} \|R_{D}\|R_{3}$$

Typically:

$$r_o >> R_D$$

and  $R_3 >> R_D$

$$A_v^{CS} \cong -g_m R_D = -\frac{I_D R_D}{\left(\frac{V_{GS} - V_{TN}}{2}\right)}$$

$I_D R_D$  represents the voltage dropped across drain resistor  $R_D$

A typical design point is

$$I_D R_D = \frac{V_{DD}}{2}$$

with  $V_{GS} - V_{TN} = 1 V$

$$\therefore A_{v}^{CS} \cong -V_{DD}$$

Our rule-of-thumb estimate for the C-S amplifier:

the voltage gain equals the power supply voltage.

Note that this is 10 times smaller than that for the BJT!

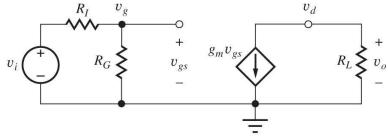

#### Voltage Gain Example

- Problem: Calculate voltage gain, input resistance and maximum input signal level for a common-source amplifier with a specified Q-point

- Given data:  $K_n = 0.50 \text{ mA/V}^2$ ,  $V_{TN} = 1 \text{ V}$ ,  $\lambda = 0.0133 \text{ V}^{-1}$ ,

Q-point is (0.241 mA, 3.81 V)

• **Assumptions:** Transistor is in the active region. Signals are low enough to be considered small signals.

Analysis:

$$g_m = \sqrt{2K_n I_D (1 + \lambda V_{DS})} = 0.503 \ mS$$

$r_o = \frac{\lambda^{-1} + V_{DS}}{I_D} = 328 \ k\Omega$

$R_G = R_1 || R_2 = 892 \ k\Omega$   $R_L = r_o || R_D || R_3 = 17.1 \ k\Omega$

#### Voltage Gain Example (cont.)

$$g_m = 0.503 \ mS$$

$r_o = 328 \ k\Omega$   $R_G = 892 \ k\Omega$   $R_L = 17.1 \ k\Omega$

$$R_G = 892 \ k\Omega$$

$$R_{I} = 17.1 k\Omega$$

$$A_{v}^{CS} = -g_{m}R_{L} \left( \frac{R_{G}}{R_{I} + R_{G}} \right) = -0.503mS(17.1k\Omega) \left( \frac{892k\Omega}{1k\Omega + 892k\Omega} \right) = -8.60(0.999) = -8.59$$

$$R_{in} = R_I + R_G = 893 \ k\Omega$$

$$R_{in} = R_I + R_G = 893 \text{ k}\Omega$$

$$v_{gs} = v_i \left(\frac{R_G}{R_I + R_G}\right) \rightarrow \left|v_i\right| \left(\frac{R_G}{R_I + R_G}\right) \leq 0.2 \left(V_{GS} - V_{TN}\right)$$

$$V_{GS} - V_{TN} \cong \sqrt{\frac{2I_D}{K_n}} = 0.982 \ V$$

Check the rule-of-thumb estimate:  $A_v^{CS} \cong -V_{DD} = -12 \ V$  (ballpark estimate)

$$A_{v}^{CS} \cong -V_{DD} = -12 V$$

#### Voltage Gain Example (cont.)

**Simulation Results:** The graph below presents the output voltage for an input voltage that is a 0.15-V, 10-kHz sine wave. The expected output voltage amplitude is |vo| = 8.59(0.15) = 1.29 V.

Note that although the sine wave at first looks good, the positive and negative peak amplitudes are different indicating the presence of distortion, and the amplitude is actually larger than expected. The input is near our small-signal limit for linear operation.

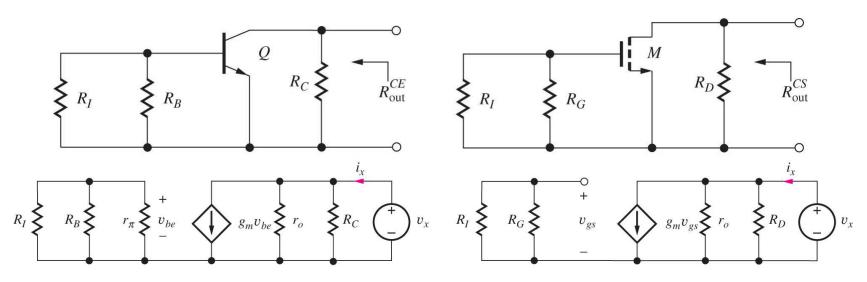

# C-E and C-S Amplifiers

# Output Resistance

# C-E and C-S Amplifiers

#### Output Resistance (cont.)

Apply test source  $v_x$  and find  $i_x$  (with  $v_i = 0$ )

$$v_{be} = 0 \rightarrow g_{m}v_{be} = 0$$

$$\therefore R_{out} = \frac{v_{x}}{i_{x}} = R_{C} \| r_{o}$$

$$R_{out} \cong R_{C} \text{ for } r_{o} >> R_{C}$$

$$v_{gs} = 0 \rightarrow g_{m}v_{gs} = 0$$

$$\therefore R_{out} = \frac{v_{x}}{i_{x}} = R_{D} \| r_{o}$$

$$R_{out} \cong R_{D} \text{ for } r_{o} >> R_{D}$$

For comparable bias points, output resistances of C-S and C-E amplifiers are similar.

# JFET Small-Signal Operation

#### **Small-Signal Model**

$$i_D = I_{DSS} \left( 1 - \frac{v_{GS}}{V_P} \right)^2 \left( 1 + \lambda v_{DS} \right)$$

for  $V$

$$i_G = I_{SG} \left[ \exp \left( \frac{v_{GS}}{V_T} \right) - 1 \right]$$

$$g_g = \frac{1}{r_g} = \frac{\partial i_G}{\partial v_{GS}} \bigg|_{\text{Q-point}} = \frac{I_G + I_{SG}}{V_T} \cong 0 \text{ for } I_G = 0$$

$$g_m = \frac{\partial i_D}{\partial v_{GS}}\Big|_{\text{Q-point}} = \frac{2I_D}{V_{GS} - V_P} \cong 2\frac{I_{DSS}}{V_P^2} (V_{GS} - V_P)$$

$$i_{D} = I_{DSS} \left( 1 - \frac{v_{GS}}{V_{P}} \right)^{2} \left( 1 + \lambda v_{DS} \right)$$

$$for \quad v_{DS} \ge v_{GS} - V_{P}$$

$$g_{o} = \frac{1}{r_{o}} = \frac{\partial i_{D}}{\partial v_{DS}} \Big|_{Q-point} = \frac{I_{D}}{\frac{1}{\lambda} + V_{DS}}$$

# JFET Small-Signal Operation

#### Small-Signal Model (cont.)

Since JFET is normally operated with gate junction reverse-biased,

$$I_{G} = -I_{SG}$$

$$r_{g} = \infty$$

For small-signal operation, the input signal limit is:

$$v_{gs} < 0.2(V_{GS} - V_P)$$

The amplification factor is given by:

$$\mu_{f} = g_{m} r_{o} = 2 \frac{\frac{1}{\lambda} + V_{DS}}{V_{GS} - V_{P}} \approx \frac{2}{\lambda |V_{P}|} \sqrt{\frac{I_{DSS}}{I_{D}}}$$

#### JFET Example

**Analysis:** De equivalent circuit is constructed.  $I_G = 0$ ,  $I_S = I_D$ .

$$V_{GS} = -2000I_D$$

$$V_{GS} = -(2 \times 10^3)(1 \times 10^{-3}) \left(1 - \frac{V_{GS}}{(-1)}\right)^2$$

Choose  $V_{GS}$  less negative than  $V_P$ .

- **Problem:** Find voltage gain, input and output resistances.

- **Given data:**  $I_{DSS} = 1 \text{ mA}, V_P = -1V,$   $\lambda = 0.02 \text{ V}^{-1}$

- **Assumptions:** Pinch-off region of operation.

#### JFET Example (cont.)

Next we construct the ac equivalent and simplify it.

$$g_{m} = \frac{2}{|V_{P}|} \sqrt{I_{DSS} I_{DS} (1 + \lambda V_{DS})} = 1.05 \text{ mS}$$

$$r_{o} = \frac{1 + \lambda V_{DS}}{\lambda I_{DS}} = 219 \text{ k}\Omega$$

$$R_{out} = r_o || R_D = 24.0 \text{ k}\Omega$$

$$A_v = \frac{v_o}{v_i} = -g_m (R_{out} || R_3) \left[ \frac{R_{in}}{R_I + R_{in}} \right] = -20.3$$

# BJT and FET Small-Signal Model Summary

#### **TABLE 13.3**

**Small-Signal Parameter Comparison**

| PARAMETER                                                                                                                                             | BIPOLAR<br>TRANSISTOR                                     | MOSFET                                                                                                             | JFET                                                                                                                     |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| Transconductance $g_m$                                                                                                                                | $rac{I_C}{V_T}$                                          | $rac{2I_D}{V_{GS}-V_{TN}}\cong \sqrt{2K_nI_D}$                                                                    | $rac{2I_D}{V_{GS}-V_P}\congrac{2}{ V_P }$                                                                              |  |

| Input resistance                                                                                                                                      | $r_{\pi} = \frac{\beta_o}{g_m} = \frac{\beta_o V_T}{I_C}$ | $\infty$                                                                                                           | $\infty$                                                                                                                 |  |

| Output resistance $r_o$                                                                                                                               | $\frac{V_A + V_{CE}}{I_C} \cong \frac{V_A}{I_C}$          | $rac{rac{1}{\lambda} + V_{DS}}{I_D} \cong rac{1}{\lambda I_D}$                                                  | $rac{rac{1}{\lambda} + V_{DS}}{I_D} \cong rac{1}{\lambda I_D}$                                                        |  |

| Intrinsic voltage gain $\mu_f$                                                                                                                        | $rac{V_A + V_{CE}}{V_T} \cong rac{V_A}{V_T}$            | $\frac{2\left(\frac{1}{\lambda} + V_{DS}\right)}{V_{GS} - V_{TN}} \cong \frac{1}{\lambda} \sqrt{\frac{2K_n}{I_D}}$ | $\frac{2\left(\frac{1}{\lambda} + V_{DS}\right)}{V_{GS} - V_P} \cong \frac{2}{\lambda  V_P } \sqrt{\frac{I_{DSS}}{I_D}}$ |  |

| Small-signal requirement                                                                                                                              | $v_{be} \leq 0.005 \text{ V}$                             | $v_{gs} \le 0.2(V_{GS} - V_{TN})$                                                                                  | $v_{gs} \le 0.2(V_{GS} - V_P)$                                                                                           |  |

| dc i-v active region expressions for use with Table 13.3:                                                                                             |                                                           |                                                                                                                    |                                                                                                                          |  |

| BIT: $I_C = I_S \left[ \exp \left( \frac{V_{BE}}{V_{BE}} \right) - 1 \right] \left[ 1 + \frac{V_{CE}}{V_{CE}} \right] \qquad V_T = \frac{kT}{V_{CE}}$ |                                                           |                                                                                                                    |                                                                                                                          |  |

BJT:

$$I_C = I_S \left[ \exp \left( \frac{V_{BE}}{V_T} \right) - 1 \right] \left[ 1 + \frac{V_{CE}}{V_A} \right] \qquad V_T = \frac{kT}{q}$$

MOSFET:

$$I_D = \frac{K_n}{2} (V_{GS} - V_{TN})^2 (1 + \lambda V_{DS}) \qquad K_n = \mu_n C_{\text{ox}} \frac{W}{L}$$

JFET:

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2 (1 + \lambda V_{DS})$$

# Common-Emitter/Common-Source Amplifiers Summary

|                                      | COMMON-EMITTER AMPLIFIER                                                                                                         | COMMON-SOURCE AMPLIFIERS                      |  |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--|

| Terminal gain $A_{vt}$               | $-g_m R_L$                                                                                                                       | $-g_m R_L$                                    |  |

| Rule-of-thumb estimate for $g_m R_L$ | $-10V_{CC}$                                                                                                                      | $-V_{DD}$                                     |  |

| Voltage gain $A_v$                   | $A_v = \frac{\mathbf{v}_o}{\mathbf{v}_i} = -g_m(R_{\text{out}}    R_3) \left( \frac{R_{\text{in}}}{R_I + R_{\text{in}}} \right)$ |                                               |  |

| Input resistance $R_{\rm in}$        | $R_B \  r_\pi$                                                                                                                   | $R_G$                                         |  |

| Output resistance $R_{\text{out}}$   | $R_C \  r_o \cong R_C$                                                                                                           | $R_D \  r_o \cong R_D$                        |  |

| Input signal phase                   | 0.005 V                                                                                                                          | $0.2(V_{GS} - V_{TN})$ or $0.2(V_{GS} - V_P)$ |  |

# **Amplifier Power Dissipation**

Static power dissipation in amplifiers is found from their dc equivalent circuits.

(a) Total power dissipated in the C-B and E-B junctions is:

$$P_D = V_{CE}I_C + V_{BE}I_B$$

where  $V_{CE} = V_{CB} + V_{BE}$

Total power supplied is:

$$P_S = V_{CC}I_C + V_{EE}I_E$$

(b) Total power dissipated in the transistor is:

$$P_D = V_{DS}I_D + V_{GS}I_G = V_{DS}I_D$$

Total power supplied is:

$$P_S = V_{DD}I_D + V_{DD}^2/(R_I + R_2)$$

# Amplifier Signal Range

$v_{CE} = V_{CE} - V_m \sin \omega t$  where  $V_m$  is the output signal. Active region operation requires  $v_{CE} \ge v_{BE}$  So:  $V_m \le V_{CE} - V_{BE}$  Also:  $v_{R_c}(t) = I_C R_C - V_m \sin \omega t \ge 0$   $\therefore V_m \le \min \left[ I_C R_C, \left( V_{CE} - V_{BE} \right) \right]$

Similarly for MOSFETs and JFETs:

$$V_{M} \leq \min \left[ I_{D} R_{D}, (V_{DS} - (V_{GS} - V_{TN})) \right]$$

$$V_{M} \leq \min \left[ I_{D} R_{D}, (V_{DS} - (V_{GS} - V_{P})) \right]$$

# End of Chapter 13