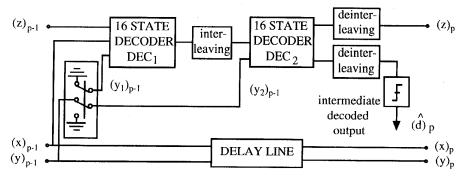

Fig. 8. Decoding module (level p).

With the feedback decoder, the LLR  $\Lambda_1(d_k)$  generated by decoder DEC<sub>1</sub> is now equal to

$$\Lambda_1(d_k) = \frac{2}{\sigma^2} x_k + \frac{2}{\sigma_z^2} z_k + W_{1k}$$

(44)

where  $W_{1k}$  depends on sequence  $\{z_n\}_{n\neq k}$ . As indicated above, information  $z_k$  has been built by decoder DEC<sub>2</sub>. Therefore  $z_k$  must not be used as input information for decoder DEC<sub>2</sub>. Thus decoder DEC<sub>2</sub> input sequences will be sequences  $\{\tilde{\Lambda}_1(d_n)\}$  and  $\{y_{2k}\}$  with

$$\tilde{\Lambda}_1(d_n) = \Lambda_1(d_n)_{z_n = 0}. (45)$$

Finally, from (40), decoder DEC<sub>2</sub> extrinsic information  $z_k = W_{2k}$  after deinterleaving can be written as

$$z_k = W_{2k} = \Lambda_2(d_k)|_{\tilde{\Lambda}_1(d_k) = 0}$$

(46)

and the decision at the decoder DEC output is

$$\hat{d}_k = \operatorname{sign}[\Lambda_2(d_k)]. \tag{47}$$

The decoding delays introduced by the component decoders, the interleaver and the deinterleaver imply that the feedback piece of information  $z_k$  must be used through an iterative process.

The global decoder circuit is made up of P pipelined identical elementary decoders. The pth decoder DEC (Fig. 8) input, is made up of demodulator output sequences  $(x)_p$  and  $(y)_p$  through a delay line and of extrinsic information  $(z)_p$  generated by the (p-1)th decoder DEC. Note that the variance  $\sigma_z^2$  of  $(z)_p$  and the variance of  $\tilde{\Lambda}_1(d_k)$  must be estimated at each decoding step p.

For example, the variance  $\sigma_z^2$  is estimated for each  $M^2$  interleaving matrix by the following:

$$\sigma_z^2 = \frac{1}{M^2} \sum_{k=1}^{M^2} (|z_k| - m_z)^2$$

(48a)

where  $m_z$  is equal to

$$m_z = \frac{1}{M^2} \sum_{k=1}^{M^2} |z_k|.$$

(48b)

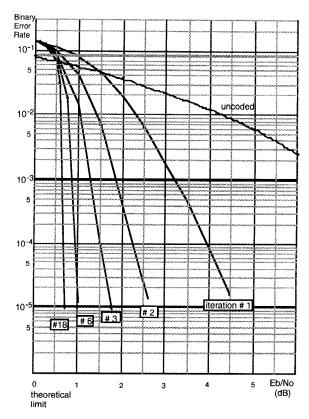

Fig. 9. BER given by iterative decoding  $(p=1,\cdots 18)$  of a rate R=1/2 encoder, memory  $\nu=4$ , generators  $G_1=37, G_2=21$ , with interleaving  $256\times 256$ .

## B. Interleaving

The interleaver is made up of an  $M \cdot M$  matrix and bits  $\{d_k\}$  are written row by row and read following the nonuniform rule given in Section III-B2. This nonuniform reading procedure is able to spread the residual error blocks of rectangular form, that may set up in the interleaver located behind the first decoder  $\mathrm{DEC}_1$ , and to give a large free distance to the concatenated (parallel) code.

For the simulations, a 256.256 matrix has ben used and from (19), the addresses of line  $i_r$  and column  $j_r$  for reading are the following:

$$i_r = 129(i+j) \qquad \mod \cdot 256$$

nal Codes

f the decoding trellis. Thus, tial dependence of decoding application of the Viterbi since the branch complexity ce more time to decode. This eliminated using a technique

erbi algorithm by employing it must be performed at each used to do the operations in 2<sup>ν</sup> operations serially. Thus, s a factor of  $2^{\nu}$  advantage in 2<sup>v</sup> times as much hardware. about 1/3 for a large subclass compare-select-add (CSA) ls of this differential Viterbi

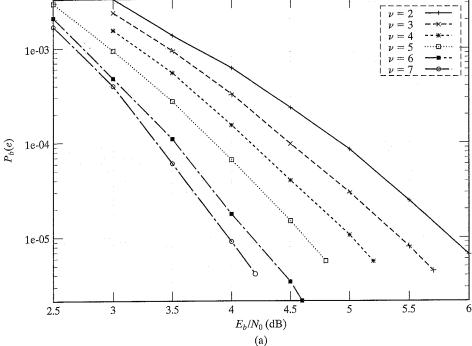

sults illustrating the perfor-Figure 12.17. The bit-error des with constraint lengths as a function of the bit SNR channel in Figure 12.17(a). d-quantized (Q = 2) channel mory was  $\tau = 32$ . Note that of soft decisions (unquantized 2). This improvement is illuse of the optimum constraint ο (unquantized outputs) and .2.17(c) is the uncoded curve es shows real coding gains of IB in the quantized (Q = 8) $= \infty$ ) soft-decision case at a only about 0.2-dB difference id the unquantized  $(Q = \infty)$ h to gain by using more than (d), the performance of this and  $\infty$  (no truncation) for a itput. Note that in both cases ance by about 1.25 dB, that at  $\tau = 32 = 8\nu$  performs the 1/2 codes.) The performance engths  $\nu = 3, 5$ , and 7 listed a continuous-output AWGN than the corresponding rate 1 0.25 dB and 0.5 dB. This is l  $d_{free}$  in decibels, is larger al

Implementation and Performance of the Viterbi Algorithm 555 Section 12.4

(b)

FIGURE 12.17: Simulation results for the Viterbi algorithm.