### **LETTER**

### Silicon acoustoelectronics with thin film lithium niobate

To cite this article: Umesh Kumar Bhaskar et al 2019 J. Phys. D: Appl. Phys. 52 05LT01

View the <u>article online</u> for updates and enhancements.

## IOP ebooks™

Bringing you innovative digital publishing with leading voices to create your essential collection of books in STEM research

Start exploring the collection - download the first chapter of every title for free.

#### https://doi.org/10.1088/1361-6463/aaee59

### Letter

# Silicon acoustoelectronics with thin film lithium niobate

### Umesh Kumar Bhaskar<sup>®</sup>, Sunil Ashok Bhave and Dana Weinstein

Purdue University, School of Electrical and Computer Engineering, West Lafayette, IN, United States of America

E-mail: umeshkbhaskar@gmail.com

Received 14 September 2018, revised 20 October 2018 Accepted for publication 26 October 2018 Published 23 November 2018

### **Abstract**

We report on the acoustoelectric (AE) interaction in heterogeneously integrated thin-film lithium niobate on standard resistivity and high resistivity silicon substrates (LNOSs). The monolithic LNOS platform delivers acoustic waves with a large electromechanical coupling coefficient ( $K^2$ ) and draws on standard metal-oxide semiconductor field effect techniques to maximise AE interaction by impedance matching the acoustic wave with the semiconductor carriers. Preliminary results are obtained on AE attenuation (4 dB cm<sup>-1</sup>) and AE gain (6 dB cm<sup>-1</sup>). With further improvement of the LN/Si interface, the LNOS platform can be expected to give rise to an era of non-reciprocal silicon acoustoelectronics.

1

Keywords: acoustoelectric, acoustic wave, piezoelectric, semiconductor

Supplementary material for this article is available online

### 1. Introduction

The electric potential of an acoustic wave (AW) travelling at a piezoelectric/semiconductor interface induces a periodic modulation in the energy band levels of the semiconductor. Charge redistribution in response to these evanescent piezoelectric fields confines electrons to the minima, and holes to the maxima, of the AW potential [1]. This interaction, termed the acoustoelectric effect (AE) [2-11], results in an acoustically driven current [12] and attenuation of the AW. The direction of momentum transfer can also be reversed and amplification of the AW is achieved by applying an electric field to make the carriers confined in the AW minima drift faster than the acoustic wave velocity. The result is non-reciprocal wave propagation or selective amplification/attenuation of acoustic waves depending on whether the waves propogate in/against the direction of the electric field. AE amplification is thus highly sought-after to recover propagation loss in acoustic transmission lines and to design fundamentally nonreciprocal circuits. Furthermore, designing AE devices with silicon provides a route to integrate high-gain analog amplifiers and signal processing devices [13] with IC technology.

The AE effect is at its strongest when a 2D semiconducting layer with high mobility and low carrier density is placed in close proximity with a high  $K^2$  acoustic wave [14–17]. Fundamental investigations on AE have focused on surface acoustic waves (SAW, or Rayleigh waves) in the GaAs/AlGaAs heterostructure due to the intrinsic piezoelectricity of GaAs and the high quality of the modulation doping induced 2DEG [18, 19]. Electrostatically constricting the GaAs/AlGaAs 2DEG along the acoustic beam width results in quantization of the number of electrons transported in each SAW minimum [20]. It has been shown that AWs can shuttle a continuous stream of single electrons, confined and isolated from each other as individual quantum dots [19]. These 'dynamic quantum dots' have been routed for widespread applications as single photon sources, and more importantly as a quantum bus for manipulation of spin-qubits [21]. Recently, complentary metal oxide semiconductor (CMOS) based gate-defined quantum dots [22], and isotropically purified Si lattices [23, 24], along with Si/SiGe heterostructures [25], have emerged as the leading contenders for quantum computing application with spin-qubits. The absence of intrinsic piezoelectricity in these heterostructures restricts the investigation of AE

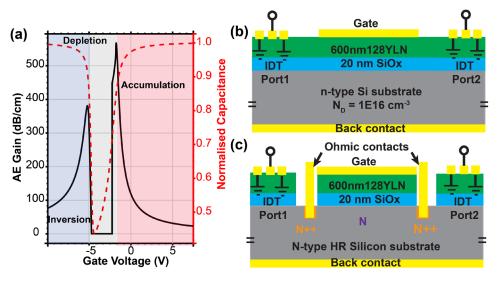

Figure 1. (a) Theoretical estimation of AE gain at the LNOS heterostructure for a carrier drift velocity of  $1 \times 10^6$  cm s<sup>-1</sup>. Parameters are  $K^2 = 5\%$ , oxide thickness = 75 nm, dopant density =  $1 \times 10^{16}$  cm<sup>-3</sup>, and AW frequency = 680 MHz; (b) cross section of the LNOS-C structure and the metal/LN/SiO<sub>2</sub>/Si/metal MOSCAP; (c) cross section of the LNOS device fabricated with Ohmic contacts realized by n + implantation of HR Si.

interactions. In this work, we report on the first demonstration of gate-tunable AE interaction in heterogeneously integrated lithium niobate thin films on silicon substrate (LNOS). The intrinsically large coupling coefficient ( $K^2$ ) of LNOS provides a promising path towards CMOS compatible silicon acousto-electronics, for high gain, non-reciprocal RF components, as well as qubit manipulation.

### 2. AE interactions in LNOS

AE interaction ( $\alpha$ ) is expressed as [2]:

$$\alpha = 0.5kK^2 \frac{y}{(1 + y^2(1+b)^2)} \tag{1}$$

where  $y = \frac{\sigma/k}{(\epsilon_p + \epsilon_s)(\nu_d - \nu_s)}$ ,  $b = \frac{k^2(\epsilon_p + \epsilon_s)D}{\sigma}$ , k is the AW wavenumber,  $\epsilon_p$  is the piezoelectric permittivity,  $K^2$  is the effective electromechanical coupling coefficient of the AW, D is the diffusion coefficient,  $v_s$  is the velocity of the AW,  $v_d$  is the drift velocity of free carriers, and  $\sigma$  and  $\epsilon_s$  are the conductivity and permittivity of the semiconductor, respectively. The ratio y describes the Kramers-Kronig relationship [26] between the AE effect and the AW velocity. Renormalization of the AW velocity is induced, in response to varying the electrostatic boundary condition at the piezoelectric-semiconductor interface. The AW velocity continuously changes between its two extreme values corresponding to unscreened ( $v_s$ ) and metallic screening of the piezoelectric fields at the interface  $(\frac{v_s}{(1+0.5K^2)})$ . In contrast, the AE effect is non-existent for both boundary values and is at its strongest when AW velocity is midway  $(\frac{v_s}{(1+0.25K^2)})$  between its extreme values [12]. This critical conductivity of the semiconductor corresponds to a regime where the semiconductor carrier density is maximally modulated by the displacement charge density of the AW potential. Mathematically, the maximum AE interaction happens for a semiconductor sheet conductance

$$\sigma_m = k * (\epsilon_p + \epsilon_s) * (\nu_d - \nu_s). \tag{2}$$

Typical  $\sigma_m$  values lie between  $1 \times 10^{-6}$  and  $1 \times 10^{-4}$  mho sq<sup>-1</sup> [12, 27].

In the LNOS heterostructure, the desired semiconductor conductance can, in principle, be attained by impurity doping the silicon lattice or by using standard field effect techniques. Controlling the carrier concentration by impurity doping becomes challenging in lowly-doped Si nanostructures [28], which are prone to the influence of surface states [29] at the LN/Si interface. Thus, in addition to controlling the Si dopant concentration, control over surface state density at the interface is necessary to optimize AE interaction. Alternatively, a gate electrode deposited on the top surface of the high permittivity LN film can be used to provide an electrostatically tunable 2D inversion or accumulation layer for AE interaction on a high resistivity (HR) substrate. The larger acoustic velocity of silicon, compared to LN, confines the AW energy and electrostatic potential to the LN/Si interface. Hence, the presence of a metallic gate on the top surface of the LN film does not significantly affect the AW electrostatic potential at the LN-Si interface.

The application of an electrostatic potential at the LN-Si interface allows one to tune the surface potential of Si [23, 30, 31] and hence, dynamically control the AE interaction. Figure 1(a) shows the plot of AE gain, at a carrier drift velocity of  $1 \times 10^6$  cm s<sup>-1</sup>, as a function of the surface potential of an n-type, standard resistivity ( $\sim 1 \times 16$  phosphorous dopants per cm<sup>3</sup>) silicon wafer [13, 32]. For comparison, the surface potential of silicon is expressed in terms of a back-gate voltage. As alluded to earlier, maximum AE gain occurs when the semiconductor sheet conductance is comparable to  $\sigma_m$ . This happens close to the flat band and weak inversion for majority and minority carriers in a standard doped n-type Si wafer. The maximum around flat-band can be understood from the fact that, around the flat-band, AE interaction decreases for both accumulation (when the carrier density is increased,

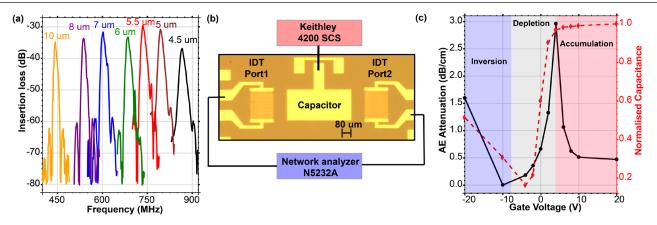

**Figure 2.** (a) Time-gated insertion loss of IDTs fabricated on LNOS-C substrates with wavelengths varying from 10  $\mu$ m to 4.5  $\mu$ m; (b) optical image of AE delay line with MOSCAP and schematic of the measurement setup; (c) experimental characterization of AE attenuation with respect to the applied gate voltage for a 680 MHz ( $\lambda = 6~\mu$ m) device. The measured capacitance is also shown to identify the electronic regime of operation.

and screening length is decreased) and depletion (when the static space charge region also contributes to the screening of the AW). The expected AE attenuation for a high resistivity, n-type wafer is plotted as a function of the gate voltage in the supplementary information, figure S1 (stacks.iop.org/JPhysD/52/05LT01/mmedia).

### 3. Experimental design and characterization

### 3.1. Passive AE devices for capacitance measurements on standard doped silicon substrates (LNOS-C)

$128^{\circ}\,Y\text{-cut}\,LN$  thin films were transferred onto standard doped (n-type  $1\times10^{16}~\text{cm}^{-3})$  silicon substrates. These substrates can be used to study AE attenuation by simply integrating a metal oxide semiconductor capacitor (MOSCAP) in the AW delay line (figure 1(b)). In this case, the MOSCAP is a hybrid metal/LN/SiO<sub>2</sub>/Si/metal capacitor. The thin silicon dioxide film (20 nm) acts as a buffer between the LN film and silicon, reducing the interface charge density. The gate voltage is applied between the top electrode on the LN film and the bottom electrode at the back of the substrate.

### 3.2. Active AE devices on HR silicon substrates

In this case, the starting material is an n-type, high resistivity (>5000  $\Omega$  cm) Si substrate (figure 1(c)). An implantation mask is lithographically defined to selectively dope regions (~300 nm deep, ~5 ×  $10^{19}$  cm<sup>-3</sup>), which would be used later for Ohmic contacts. After implantation and dopant activation, 128° Y-cut LN thin films were transferred onto the substrates using 'ion-slicing' technology [33]. After bonding, Ti/Au electrodes are deposited and patterned by lift-off on the LN surface for the IDT and the gate electrode. Ohmic contacts are subsequently made to the heavily doped contact regions by opening windows in LN by RIE and depositing Al. Thermal oxide on the back-side of the wafer is removed by BOE and Al is deposited for back-gating. A final post-metallization anneal is conducted at 430 °C in forming gas ambient for 20 min.

A detailed schematic of the process flow is provided in the supplementary information, figure S2.

### 4. Results and discussion

### 4.1. Acoustic wave measurements

On standard doped silicon substrates (LNOS-C), electromagnetic feedthrough coupling between the two IDT ports dominates the transmission data. Hence, the frequency response of the AW delay lines is time-gated to isolate the acoustic mode. This procedure is not necessary to identify the acoustic mode in the case of HR silicon substrates (LNOS) but is still used for consistency. The time-gated insertion loss of Rayleigh mode devices fabricated with an IDT pitch corresponding to wavelengths between 4.5 and 10  $\mu$ m deposited on LNOS-C is shown in figure 2(a). The insertion loss of Rayleigh devices fabricated on LNOS substrates is provided in the supplementary information, figure S3. The frequency dispersion of the SAW velocity,  $K^2$  on LNOS-C substrates and their comparison with COMSOL simulation is discussed in an earlier publication [34].

### 4.2. AE attenuation on LNOS-C

The integration of MOSCAPs in the middle of the AW delay line allows us to tune electrostatically the surface carrier concentration of the silicon substrate. Figure 2(b) shows the optical image of a 680 MHz SAW delay line with a MOSCAP, as well as the measurement setup. An approximate  $K^2$  of 0.9% is extracted from fitting the corresponding dip in the reflection (S11) spectra [35]. The measured AE attenuation, manifested through the change in the peak transmission of the mode as a function of the gate voltage, is plotted in figure 2(b). The normalized capacitance is also plotted for comparison to clearly identify the electronic regime of device operation. Maximum AE interaction is expected for a sheet conductance corresponding to the substrate dopant concentration  $(1 \times 10^{16} \text{ cm}^{-3})$ . Hence, maximum AE attenuation can

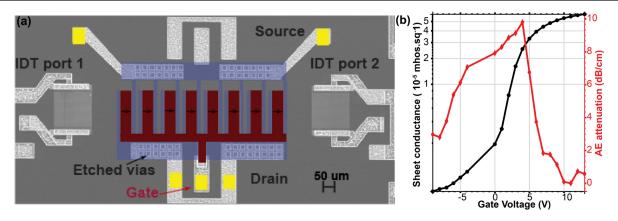

**Figure 3.** (a) SEM micrograph of an interdigitated array of gated channel (GC) regions designed to obtain tunable gain. Implanted regions are colored in blue, while the GC regions are colored in red; (b) AE attenuation of the GC region studied as a function of the gate voltage. The measured sheet conductance of the device is also plotted for comparison.

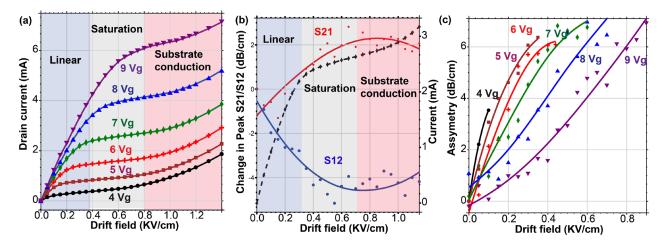

Figure 4. (a) Output characteristics of a gated-segmented LNOS device; (b) the time-gated peak of  $S_{12}$  and  $S_{21}$  of a 680 MHz gated-segmented LNOS device is plotted as a function of bias, showing clear non-reciprocity. The dots correspond to experimental measurement and the line is a guide to the eye. The measured current is also plotted for comparison; (c) measurement of non-reciprocal asymmetry is plotted as a function of drift field for different gate voltages.

be expected to occur close to the flat-band for LNOS-C substrates. Capacitance measurements reveal a shift in the flat-band voltage, indicating a negative charge density has been induced at the interface due to the bonding process. Hence, at zero gate bias, the Si surface is in depletion and the AE interaction is at a minimum. The maximum attenuation measured is about 4 dB cm<sup>-1</sup> and occurs when the positive gate bias can compensate the shift in flat-band from trapped charges. The magnitude of AE interaction expected (figure S4) by assuming a  $K^2$  of 0.9% is 16 dB cm<sup>-1</sup>, which is significantly larger than the measured value. The discrepancy is expected to be due to a large fraction of AW induced displacement charge being compensated by traps and localized interface charge sites, rather than the semiconductor space charge [36, 37].

### 4.3. AE attenuation and gain on LNOS

It can be inferred from measurements on the LNOS-C substrates that ion doping the Si substrate does not guarantee the carrier concentration desired for AE interaction. Hence, standard field effect techniques are used to achieve carrier control for AE interactions in the LNOS substrates. The HR substrate

used in the LNOS heterostructure eliminates electromagnetic feedthrough coupling between the IDT ports and provides an intrinsically higher mobility for free carriers than standard doped wafers. Regions with n+nn+ doping were defined at the surface of the substrate by heavily doping with phosphorus ions (n+ regions are coloured blue in figure 3(a)). Standard MOSFET techniques were used for control of the carrier density and velocity in the channel region.

An SEM micrograph of the device used for LNOS measurements is shown in figure 3(a). The device is basically an AW delay line with eight pairs of gated n+nn+channel (GC) regions chained together in the middle of the delay line. The GC structure is a simple array of interdigitated 50  $\mu$ m channels whose edges are defined with heavily doped 10  $\mu$ m silicon regions. The alternating polarity of the interdigitated leads correspond to the source and drain terminals. A top gate (coloured red in figure 3(a)) deposited on alternating channel regions provides electrostatic control to create the desired carrier concentration in one half of the interdigitated pattern, while surface depletion eliminates the drift of carriers in the other half of the pattern corresponding to the opposite electric field direction. The gated segmented regions are designed to

provide two major benefits: (1) switchable AE interaction by control of impedance presented by the semiconductor to the acoustic wave; (2) small channel length (50  $\mu$ m) to reach the required drift velocities at small voltages and, hence, operate within the linear regime of the transistor.

AE attenuation of the GC regions is demonstrated by plotting the change in the peak of the mode as a function of the gate voltage applied to VG in figure 3(b). A clear peak in the AE attenuation is observed at around 4VG, corresponding to a sheet conductance of  $5 \times 10^{-6}$  mho sq<sup>-1</sup>. The magnitude of peak AE attenuation is about an order of magnitude smaller than analytical estimation (figure S5). The difference in measured and estimated data is further evidence of weak coupling at the LN/Si interface. Indeed, a large interface state density can be expected to partially screen the piezoelectric fields and drastically reduce the AE interaction.

In contrast to AE attenuation, obtaining AE amplification in a gated structure is less straightforward. The addition of a large drift field significantly distorts the uniformity of carrier density under the gated region. To enable direct comparison with two terminal measurements, it is important to limit operation of the device in the linear or quadratic regime. It can be seen in figure 4(a) that by using sufficiently short channels (50  $\mu$ m), we are able to reach electric fields (up to ~0.5 kV cm<sup>-1</sup>) required to demonstrate AE non-reciprocity in the linear regime. At larger applied fields, in addition to saturation effects, the measured current becomes dominated by parasitic contribution from conduction paths through the bulk n-type HR substrate. This happens because below the threshold operation of the GC regions makes the HR substrate conductivity comparable with the surface conductivity. In future devices, the surface conductivity can be easily isolated from substrate conductivity by switching to an inversion layer regime of operation. For these accumulation mode devices, AE was studied at small fields close to the linear regime of device operation. Figure 4(b) shows clear non-reciprocity observed between S<sub>12</sub> and S<sub>21</sub> for 7 V bias to the gate electrode and electric fields from 0 KV cm<sup>-1</sup> to 0.5 KV cm<sup>-1</sup>. For larger gate biases, and hence larger sheet conductance, an increased linearity is observed but with a decreased strength of AE interaction. This trend can be expected from theory [2]. However, the magnitude of the change is about an order of magnitude smaller, which could be attributed to poor interface quality and any non-uniformity of carrier concentration in the GC regions. Observation of AE effects at larger electric fields is limited by device design, Joule heating, and non-uniformity in surface potential due to channel pinch-off effects.

### 5. Conclusion

The large  $K^2$ , in combination with gated control of carrier density offered by the LNOS material platform promises to overcome past hurdles to AE technology, enabling a new era of gate-controlled, non-reciprocal RF devices. Additionally, the flexibility of LNOS heterostructures allow straightforward integration of AE devices with CMOS transistors as well as ambipolar quantum dots fabricated on HR silicon wafers [38,

39]. However, further understanding of trap states at the LN/Si interface is required to realize the full potential of the LNOS heterostructure.

### **Acknowledgments**

The author acknowledges insightful discussions with Matthew Storey, and Siddhartha Ghosh. This work was funded through the DARPA MTO SPAR program (Grant 108712). LNOS substrates were prepared by Dr Payam Rabiei at Partow Technologies, LLC. Fabrication was performed at the Pritzker Nanofabrication Facility of the Institute for Molecular Engineering at the University of Chicago, which receives support from Soft and Hybrid Nanotechnology Experimental (SHyNE) Resource (NSF ECCS-1542205).

### **ORCID iDs**

Umesh Kumar Bhaskar https://orcid.org/0000-0002-6260-4198

#### References

- [1] De Lima M M and Santos P V 2005 Modulation of photonic structures by surface acoustic waves *Rep. Prog. Phys.* 68 1639–701

- [2] Hutson A R, McFee J H and White D L 1961 Ultrasonic amplification in CDS Phys. Rev. Lett. 7 237–9

- [3] Yoshida K and Yamanishi M 1968 Interaction between surface elastic waves and drifting carriers in layered system *Japan*. *J. Appl. Phys.* 7 1143–4

- [4] Collins J H, Lakin K M, Quate C F and Shaw H J 1968 Amplification of acoustic surface waves with adjacent semiconductor and piezoelectric crystals *Appl. Phys. Lett.* 13 314–6

- [5] Sharma J N, Sharma K K and Kumar A 2010 Surface waves in a piezoelectric–semiconductor composite structure *Int. J. Solids Struct.* 47 816–26

- [6] Zaitsev B D and Kuznetsova I E 1996 Surface acoustic waves in a gallium arsenide-conducting layer structure *IEEE Trans. Ultrason. Ferroelectr. Freq. Control* 43 1130–2

- [7] Gulyaev Y V and Pustovoit V I 1965 Amplification of surface waves in semiconductors Sov. Phys.—JETP 20 1508–9

- [8] White D L 1962 Amplification of ultrasonic waves in piezoelectric semiconductors J. Appl. Phys. 33 2547–54

- [9] Vyun V A 1992 Self-sustained acoustoelectric and photoelectric oscillations in systems with relaxation *IEEE International Frequency Control Symp.*, pp 509–13

- [10] Yang J S and Zhou H G 2004 Acoustoelectric amplification of piezoelectric surface waves Acta Mech. 172 113–22

- [11] Zhu H and Rais-Zadeh M 2017 Non-reciprocal acoustic transmission in a GaN delay line using the acoustoelectric effect *IEEE Electron Device Lett.* **38** 802–5

- [12] Rotter M, Kalameitsev A V, Govorov A O, Ruile W and Wixforth A 1999 Charge conveyance and nonlinear acoustoelectric phenomena for intense surface acoustic waves on a semiconductor quantum well *Phys. Rev. Lett.* 82 2171–4

- [13] Reeder T M and Kino G S 1971 Normal mode theory for the Rayleigh IEEE Trans. Electron Devices 18 909–20

- [14] Wixforth A, Scriba J, Wassermeier M, Kotthaus J P, Weimann G and Schlapp W 1989 Surface acoustic waves

- on  $GaAs/Al_xGa_{1-x}As$  heterostructures *Phys. Rev.* B **40** 7874–87

- [15] Zheng S et al 2016 Acoustic charge transport induced by the surface acoustic wave in chemical doped graphene Appl. Phys. Lett. 109 183110

- [16] Insepov Z, Emelin E, Kononenko O, Roshchupkin D V, Tnyshtykbayev K B and Baigarin K A 2015 Surface acoustic wave amplification by direct current-voltage supplied to graphene film Appl. Phys. Lett. 106 023505

- [17] Zaitsev B D, Joshi S G, Kuznetsova I E and Borodina I A 2001 Influence of conducting layer and conducting electrode on acoustic waves propagating in potassium niobate plates IEEE Trans. Ultrason. Ferroelectr. Freq. Control 48 624–6

- [18] Wixforth A, Kotthaus J P and Weimann G 1986 Quantum oscillations in the surface-acoustic-wave attenuation caused by a two-dimensional electron system *Phys. Rev. Lett.* 56 2104–6

- [19] Hermelin S *et al* 2011 Electrons surfing on a sound wave as a platform for quantum optics with flying electrons *Nature* 477 435–8

- [20] Mcneil R P G et al 2011 On-demand single-electron transfer between distant quantum dots Nature 477 439–42

- [21] Ford C J B 2017 Transporting and manipulating single electrons in surface-acoustic-wave minima *Phys. Status Solidi* b 254 1600658

- [22] Maurand R et al 2016 A CMOS silicon spin qubit Nat. Commun. 7 3–8

- [23] Nicollian E H and Brews J R 1982 MOS (Metal Oxide Semiconductor) Physics and Technology (New York: Wiley) pp 1–3

- [24] Veldhorst M *et al* 2014 An addressable quantum dot qubit with fault-tolerant control-fidelity *Nat. Nanotechnol.* **9** 981–5

- [25] Watson T F et al 2018 A programmable two-qubit quantum processor in silicon Nature 555 633–7

- [26] O'Donnell M, Jaynes E T and Miller J G 1981 Kramers– Kronig relationship between ultrasonic attenuation and phase velocity J. Acoust. Soc. Am. 69 696–701

- [27] Preciado E et al 2015 Scalable fabrication of a hybrid fieldeffect and acousto-electric device by direct growth of monolayer MoS<sub>2</sub>/LiNbO<sub>3</sub> Nat. Commun. 6 8593

- [28] Bhaskar U K, Pardoen T, Passi V and Raskin J-P 2013 Surface states and conductivity of silicon nano-wires J. Appl. Phys. 113 134502–8

- [29] Bardeen J 1947 Surface states and rectification at a metal semi-conductor contact *Phys. Rev.* **71** 717–27

- [30] Ralston R W 1975 Stable CW operation of gap-coupled silicon-on-sapphire to LiNbO<sub>3</sub> acoustoelectric amplifiers *Ultrasonics Symp.* pp 217–22

- [31] Khuri-Yakub B T and Kino G S 1974 A monolithic zinc-oxide-on-silicon convolver Appl. Phys. Lett. 25 188–90

- [32] Gautier H and Kino G S 1977 A detailed theory of the acoustic wave semiconductor convolver *IEEE Trans. Sonics Ultrason.* **24** 23–33

- [33] Rabiei P, Ma J, Khan S, Chiles J and Fathpour S 2013 Heterogeneous lithium niobate photonics on silicon substrates Opt. Express 21 25573

- [34] Bhaskar U K, Storey M J and Weinstein D 2018 Acoustoelectric effect with Rayleigh waves in a monolithic thin film lithium niobate on silicon heterostructure *IEEE Micro Electro Mechanical Systems (MEMS)* pp 759–62

- [35] Hines J H and Malocha D C 1993 A simple transducer equivalent circuit parameter extraction technique *Proc. IEEE Ultrasonics Symp.* pp 173–7

- [36] Stern E 1985 Acoustoelectronic rayleigh wave devices\* Rayleigh-Wave Theory Appl. 2 219–37

- [37] Kino G S and Coldren L A 1973 Noise figure calculation for the Rayleigh wave amplifier Appl. Phys. Lett. 22 50–2

- [38] Mueller F, Konstantaras G, Spruijtenburg P C, Van Der Wiel W G and Zwanenburg F A 2015 Electron-hole confinement symmetry in silicon quantum dots *Nano Lett.* 15 5336–41

- [39] Betz A C, Gonzalez-Zalba M F, Podd G and Ferguson A J 2014 Ambipolar quantum dots in intrinsic silicon Appl. Phys. Lett. 105 153113