# NANOELECTROMECHANICAL RELAYS WITH DECOUPLED ELECTRODE AND SUSPENSION

*R. Parsa<sup>1</sup>, M. Shavezipur<sup>2</sup>, W.S. Lee<sup>1</sup>, S. Chong<sup>1</sup>, D. Lee<sup>1</sup>, H.-S. P. Wong<sup>1</sup>, R. Maboudian<sup>2</sup>, R.T. Howe<sup>1</sup>* <sup>1</sup>Stanford University, Stanford, California, USA <sup>2</sup>University of California Berkeley, Berkeley, California, USA

# ABSTRACT

This paper reports on the modeling, fabrication, and testing of cantilever- and parallel plate-based laterally actuated platinum-coated polysilicon nanoelectromechanical (NEM) relays. The polysilicon acts as the structural layer, while the platinum serves as a conducting contact material, as well as a local routing layer. The two-part cantilever design utilizes a source made of a compliant beam in series with a stiff bridged perimeter electrode to reduce the secondary pull-in of the source to the gate. The parallelplate-based relay also uses stiffened electrodes in addition to serpentine structures that reduce the actuation voltage. Overdrive gate voltage in excess of 100% without failure and sharp release of the relay from output are achieved for polysilicon relays with 50nm platinum coating and 500nm actuation gap.

# **INTRODUCTION**

CMOS scaling has been very successful in generating small, fast, and low-cost electronics. However, in advanced CMOS nodes, the total power consumption is dominated by the static power dissipation, which is caused by gate leakage, short channel effects, and finite subthreshold slope. Further scaling of CMOS only exacerbates these problems. NEM relays are promising devices for low power logic applications due to their zero leakage current, infinite subthreshold slope, and scalable actuation voltage [1-3]. SRAM cells [4] and FPGA blocks, where low switching speed and limited number of cycles are acceptable [5], are two attractive near-term applications for NEM relays.

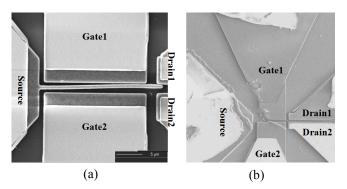

Laterally actuated relays require a single lithography step, which simplifies the fabrication process. More importantly, they enable sidewall coating, greater design space, and higher packing density compared to vertically actuated relays. However, laterally actuated relays suffer from high actuation voltages due to gap distances and widths limited by photolithography. Reducing the operational voltage is desirable, as it enables hybrid CMOS and NEM relay systems in addition to low power digital circuits. To reduce the operational voltage, the beam length is often increased, since the minimum gap and thickness for a laterally actuated relay are set by lithography limits. However, increasing the beam length, while keeping other parameters constant leads to catastrophic pull-in of the beam to the gate, as shown in Figure 1.

In this work, we propose two designs: clamped-free and clamped-clamped structures. For both designs, the mechanical and the electrostatic domains are separated, yielding individual control of the pull-in voltage and

Figure 1: (a) Actuated relay under SEM showing beam-gate shorting. (b) SEM of a 5-terminal relay after electrostatic actuation. High current flow between the beam and gate after shorting causes irreversible damage.

electrode displacements, enabling the device to be more robust against the shorting of the beam to gate.

#### **DESIGN AND MODELING**

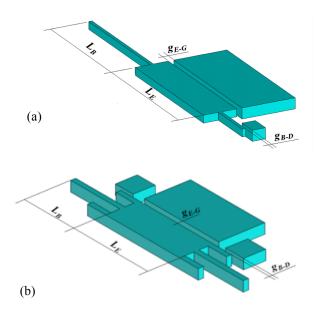

Three-terminal relays consist of a cantilever beam (source), a gate electrode, and a drain electrode. The beam acts as both the electrostatic and structural elements: the bias between the gate and beam creates an electrostatic force, which is balanced by the stored mechanical force in the beam. Important design parameters include the beam length, the beam-to-drain gap, the beam-to-gate gap, and the gate-to-drain spacing. The designs reported in this work have separate electrostatic and structural elements for the source, allowing independent control of the electrostatic and mechanical properties. Figure 2 shows the schematics for two designs. In Figure 2a, the source is made of an electrode that is supported by a cantilever beam from one side, while in Figure 2b the source consists of an electrode that is supported by two cantilever beams from both sides. The flexible beams restore mechanical energy while the rigid electrode is used for electrostatic actuation. The lengths of the gate and the electrode are the same, while the beam lengths can take different values. The electrode width is increased compared to the beam to ensure enough rigidity. A small extension connected to the end of the electrode is used for contact to the drain.

To investigate the behavior of the clamped-free relays under electrostatic actuation, finite element simulations were performed using ANSYS® multiphysics. The simulation iteratively solves the electrostatic and structural physics until the solution converges to the static equilibrium. The model also determines the mechanical

Figure 2: The geometry of the proposed NEM relays: (a) clamped-free design; (b) clamped-clamped design. The design parameters:  $L_B$ : length of the beam,  $L_E$ : length of the electrode,  $g_{E-G}$ : electrode-to-gate gap, and  $g_{B-D}$ : beam-to-drain gap.

contact between the electrode extension and the drain. The structural domain includes geometric nonlinearity that takes into account the effect of large displacements and coupled bending-axial deformations. The electrostatic and structural domains are meshed using SOLID122 and SOLID186 elements, respectively. The contact between the extension tip and the drain is modeled using CONTA170 and TARGE174 elements. A DC voltage is applied between the gate and the source electrode (including the electrode, beam, and extension).

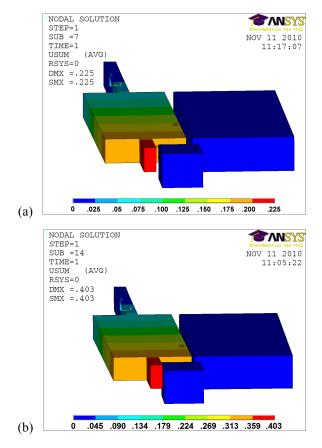

Figure 3 displays the deformations of the beamelectrode just before pull-in and after applying 50% overdrive bias voltage. The design parameters used in the simulations are presented in Table 1. The thickness of the beam/electrode is  $1.2\mu m$ , and the width of the beam is  $0.5\mu m$ . The sidewalls of the beam, electrode, gate and drain are covered with a 50nm-thick platinum layer. The simulated pull-in voltage is 12.35V.

As shown in Figure 3, the minimum electrode-gate gap is still about 150nm even when high overdrive voltage is applied, and the electrode remains rigid. To quantitatively study the behavior of the relay especially after pull-in, the

Table 1: The dimensions used in ANSYS® simulations.

| Design parameter | Value  |

|------------------|--------|

| $L_B$            | 10 µm  |

| $L_E$            | 15 μm  |

| $g_{E\_G}$       | 0.5 µm |

| $g_{B\_D}$       | 0.4 µm |

Figure 3: The results of FEM simulations. The displacements of the beam-electrode (a) just before pull-in, V = 12.35V and (b) at 50% overdrive, V = 19V.

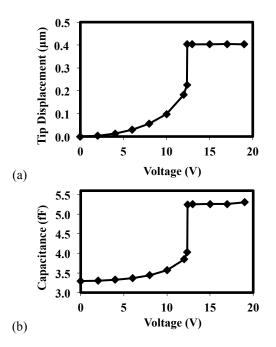

Figure 4: (a) tip-displacement-voltage (d-V) and (b) capacitance-voltage (C-V) responses of the NEMS relay obtained from FEM simulations.

tip displacement-voltage (*d-V*) and the capacitance-voltage (*C-V*) curves are plotted in Figures 4a and 4b, respectively. While both figures clearly show the pull-in and the initiation of contact between the electrode extension and the drain, only the *C-V* response can be used to quantify the displacement of the electrode after pull-in. As shown in Figure 4b, the capacitance value has negligible increase even at 50% overdrive (V = 19V), demonstrating that the proposed design can completely eliminate the short circuit between the electrode and the gate.

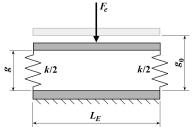

A similar concept is exploited to develop clampedclamped relays, where the structure is simply a conventional parallel-plate capacitor as shown in Figure 5. The electrode suspended by the two beams forms a pair of parallel-plate electrodes with the gate. To study the behavior of the relay, a simple and well-known model can be used, where the beams are assumed to be mechanical springs with nonlinear stiffness [6], and the rigid electrode and the gate have the common area of A and initial gap of  $g_0$ . The static equilibrium is obtained by equating the electrostatic force,  $F_{e}$ , and the springs balancing force:

$$\frac{\varepsilon_0 A V^2}{2g^2} - k(g_0 - g) = 0$$

(1)

In (1), the pull-in occurs at  $g = 1/3g_0$ . This nonlinear equation can be solved for different actuation voltage, V, to obtain the gap between the electrode and the gate, g.

Figure 5: Schematic of the clamped-clamped NEMS relay.

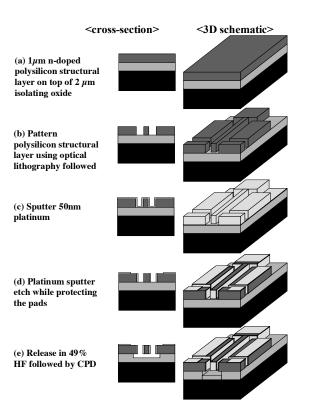

### FABRICATION

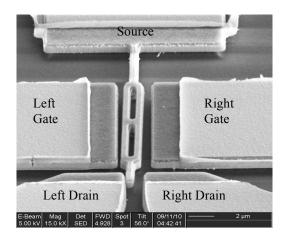

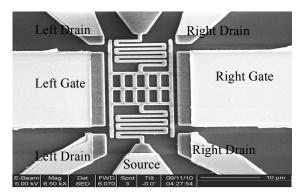

The fabrication process for the relays is shown in Figure 6. It begins with building a SiO<sub>2</sub>-polysilicon stack, followed by patterning the polysilicon beam and electrodes via optical lithography. Structures are then dipped in 50:1 HF, to remove the native SiO<sub>2</sub> and are immediately coated conformally with platinum using RF-sputter deposition. Using a second mask to protect the pads, an anisotropic etch electrically isolates the electrodes, leaving the metal on the sidewalls and top of the pads intact. Finally, the device is released in 49% HF, followed by a critical point drving (CPD) step. The sidewall coating decreases the contact resistance and the actuation gap in comparison to polysilicon relays. The addition of native oxide removal step and avoiding a liftoff step [7] result in a higher yield process. Figure 7 shows the SEM of a fabricated clampedfree device, while Figure 8 shows an SEM of a clampedclamped design. Figures 7 and 8 demonstrate the wide variety of laterally actuated structures that can be fabricated using the same mask and process flow.

Figure 6: 3D and 2D cross section view (taken along A-A' at all steps) of the process flow (not drawn to scale).

Figure 7: SEM of a fabricated clamped-free design.

#### RESULTS

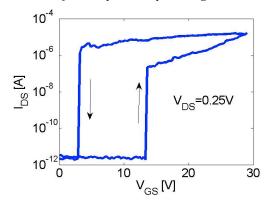

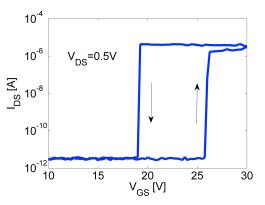

Electrical tests were performed in a nitrogen ambient without current compliance. The fabricated clamped-free relay survived after applying more than 100% overdrive voltage on the gate as shown in Figure 9. Figure 10 shows the electrical characteristics of the clamped-clamped design. High actuation voltage is observed due to the larger spring constant, k. At the same time, this high k results in sharper pull-out.

Figure 8: SEM of a clamped-clamped design.

Figure 9: Pull-in and pull-out characteristics of a clampedfree relay with the following design parameters:  $L_B=5\mu m$ ,  $L_E=15\mu m$ . Relay with pull-in voltage of 14V is operational after applying 100% over-drive on the gate (28V) with  $V_{DS}=0.25V$ .

Figure 10: Pull-in and pull-out characteristics of the clamped-clamped design showing sharper transition at pullin and pull-out.  $L_B=18\mu m$ ,  $L_E=15\mu m$ .

# CONCLUSIONS

Platinum-coated laterally actuated polysilicon NEM relays with serpentine and bridged perimeter based structures were modeled, fabricated, and tested. By successful decoupling of the electrode and the suspension through design, sustained functionality were demonstrated despite large overdrive voltages for the clamped-free and sharper pull-out characteristics for the clamped-clamped designs.

#### ACKNOWLEDGEMENTS

Fabrication work was performed at the Stanford Nanofabrication Facility (a member of the National Nanotechnology Infrastructure Network) supported by the NSF under Grant ECS-9731293, its lab members, and the industrial members of the Stanford Center for Integrated Systems. This work was supported by the DARPA MTO program "Nano Electro Mechanical Computers (NEMS)" (Contract number: NBCH 1090002, Program manager: Dr. T. Akinwande). The authors would like to thank Dr. J Provine, Chen Chen, and KyeongranYoo for helpful discussions and Srikanth Iyer and Joel Jean for extensive testing. M. Shavezipur would like to acknowledge the Natural Sciences and Engineering Research Council of Canada (NSERC) for financial support.

#### REFRENCES

- [1] F. Chen, M. Spencer, R. Nathanael, C. Wang,H. Fariborzi, A. Gupta, H. Kam, V. Pott,J. Jeon, T.-J. King Liu, D. Markovic,V. Stojanovic, and E. Alon, "Demonstration of Integrated Micro-Electro-Mechanical Switch Circuits for VLSI Applications", IEEE ISSCC 2010, pp. 150-152.

- [2] K. Akarvardar, D. Elata, R. Parsa, G. C. Wan, K. Yoo, J Provine, P. Peumans, R. T. Howe, and H.–S. P. Wong, "Design Considerations for Complementary Nanoelectromechanical Logic Gates", IEDM 2007, pp. 299-302.

- [3] D. A. Czaplewski, G. A. Patrizi, G. M. Kraus, J. R. Wendt, C. D. Nordquist, S. L. Wolfley, M. S. Baker, and M. P. de Boer "A Nanoelectromechanical Switch for Integration with CMOS Logic", Journal of Micromechanics and Microengineering, vol. 19, 2009.

- [4] S. Chong, K. Akarvardar, R. Parsa, J.-B. Yoon, R. T. Howe, S. Mitra, and H.-S. P. Wong, "Nanoelectromechanical (NEM) Relays Integrated with CMOS SRAM for Improved Stability and Low Leakage", ICCAD 2009, pp. 478-484.

- [5] C. Chen, R. Parsa, N. Patil, S. Chong, K. Akarvardar, J. Provine, D. Lewis, J. Watt, R. T. Howe, H.-S. P. Wong, and S. Mitra, "Efficient FPGAs using Nanoelectromechanical Relays", ACM Intl. Symp. FPGA 2010, pp. 273-282.

- [6] Shavezipur, M., Khajepour, A., and Hashemi, S. M., "The application of structural nonlinearity in development of linearly tunable MEMS capacitors", J. of Micromech. and Microeng., 18(3), 2008, pp. 035016-1-8.

- [7] R. Parsa, S. Chong, N. Patil, K. Akarvardar, J Provine, D. Lee, D. Elata, S. Mitra, H.-S. P. Wong, and R. T. Howe, "Composite polysilicon-platinum lateral nanoelectromechanical relays", Solid-State Sensors, Actuators, and Microsystems Workshop, Hilton Head 2010, pp. 7 – 10.