# ROBUST MICROMACHINING OF COMPLIANT MECHANISMS BY NICKEL SILICIDE

K. Khosraviani, J. Bahari, and A. M. Leung Simon Fraser University, Burnaby, BC, CANADA

## **ABSTRACT**

We are introducing an innovative sacrificial surface micromachining process that enhances the robustness of freestanding microstructures and compliant mechanisms. Fabrication of a compliant mechanism using conventional sacrificial surface micromachining results in a non-planar structure with a step between the structure and its anchor. During mechanism actuation or assembly, accumulation at the structure step can easily pass the yield strength of the material and lead to structure failure. Our process overcomes this problem by eliminating the step between the structure and its anchor, and achieves planarization without using Chemical Mechanical Polishing (CMP). The process is based on low temperature and post-CMOS compatible nickel silicide technology. We use a layer of amorphous silicon (a-Si) as the sacrificial layer. High etch selectivity between silicon and nickel silicide in the XeF<sub>2</sub> gas enables us to use the silicide to anchor the structures to the substrate. The sacrificial layer is locally converted to nickel silicide to form the anchors. The formed silicide has the same thickness as the sacrificial layer; therefore, the structure is virtually flat. The maximum measured step between the anchor and the sacrificial layer is about 10nm on a 300nm thick sacrificial layer.

#### **KEYWORDS**

Nickel silicide, Surface Micromachining, planarization, Xenon Difluoride, Chemical Mechanical Polishing (CMP)

## INTRODUCTION

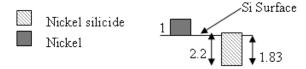

Silicides have been extensively used in the CMOS technology to reduce the series and contact resistance to the gate, source and drain regions [1]. The Lower formation temperature and lower silicon consumption of nickel silicide has overcome the limitations of the CoSi2, and made the nickel silicide the first choice for technologies below 65nm [2]. Nickel silicide formation has different phases, but numerous reports agree that the predominant phases are Ni<sub>2</sub>Si, NiSi, and NiSi<sub>2</sub> [2]. The Ni<sub>2</sub>Si forms at the temperature range of 250-300°C but it transitions rapidly to NiSi above 300°C. At higher temperatures (above 600°C) the mono-silicide transforms to NiSi<sub>2</sub> [3]. For mono-silicide (NiSi) the ratio of nickel thickness to silicide thickness and silicon consumption is 1:2.2 and 1:1.83 respectively. After formation, as it is shown in Figure 1, only 16.8% of the total silicide thickness grows above the initial silicon surface [3].

The mechanical properties and the possible applications of the nickel silicide in the microelectromechanical systems have been studied by a few researchers [4-6]. However, we were the first group who introduced a surface micromachining process using nickel silicide [7]. Nickel silicide etch rate is very low or almost zero in most acids and chemicals [4]. The close to zero etch

rate of the nickel silicide in XeF<sub>2</sub> gas makes it a good candidate for selectively etching the sacrificial layer in our process. The diffusion rate of nickel into silicon dioxide and nitride is extremely low. Therefore, these films can be used as a masking material to selectively diffuse nickel into silicon.

Conventionally, the fabrication of a freestanding structure starts with the deposition and patterning of a sacrificial layer. The structural layer is deposited afterwards. The structural layer is anchored to the substrate through the opening of the sacrificial layer. This process results in a non-planar structure with a step between the structure and its anchors. The step height is equal to the thickness of the sacrificial layer. The non-planar structures have less mechanical robustness compare to the planar structures. A fabricated compliant mechanism by this process is more likely to fail during the assembly phase because of the stress accumulation at the structure step. Furthermore, the deposition process of the structural layer requires conformal step coverage; otherwise, poor step coverage would further deteriorate the structure mechanical robustness.

In this paper, we report a novel sacrificial surface micromachining process that eliminates the step between the structural layer and its anchor, and results in virtually flat structures. Instead of opening windows in the sacrificial layer to anchor the structure to the substrate, we locally modify the property of the sacrificial layer. The modified sacrificial layer is highly etch resistant to the sacrificial layer etchant. This process creates patches of highly etch resistant material in the sacrificial layer. During the release step (etching the sacrificial layer), the structure remains anchored to the substrate through these patches. The modified sacrificial layer has the same thickness as the original layer which results in a planar structure.

Figure 1: The thickness ratio between nickel, nickel silicide, and silicon consumption in the nickel mono-silicide (NiSi).

# **FABRICATION PROCESS**

Low temperature processing is crucial in developing a post-CMOS compatible process. Silicon can be deposited at relatively low temperatures by taking advantage of PECVD technique. Table 1 compares the crystalline properties of the nickel silicide at its different phases [3]. The silicon rich nickel silicide has the largest silicon consumption ratio among the predominant phases. This is advantageous when thick layer of silicon has to be converted to silicide.

Table 1: Crystalline properties of nickel silicide phases

| Phase              | Silicide t/ | Silicon consumed / |

|--------------------|-------------|--------------------|

|                    | Ni t        | Ni t               |

| Ni <sub>2</sub> Si | 1.47        | 0.91               |

| NiSi               | 2.2         | 1.83               |

| NiSi <sub>2</sub>  | 3.61        | 3.66               |

Although the larger silicon consumption ratio of the NiSi<sub>2</sub> facilitates our process, the high formation temperature of this phase (above 600°C) is undesirable. At 350°C the film consist mostly of NiSi. This temperature is low enough for a post-CMOS compatible process and amorphous silicon can be easily deposited at this temperature too.

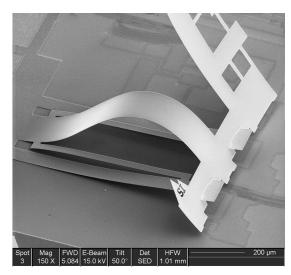

Figure 2 shows the SEM of a fabricated compliant mechanism using our process. The structure is part of a 3-D thermal accelerometer, and provides thermal insulation from the substrate for the sensor-plate. The structure has been buckled out of the plane and locked in place. The 3-layer symmetrical structure consists of two layers of PECVD oxide on top and bottom of a nichrome film. The symmetry of the structure minimizes its deformation due to the stress mismatch of the different layers. We used XeF<sub>2</sub> gas to etch the sacrificial layer and release the structure. XeF<sub>2</sub> is a white crystal that sublimes with a vapor pressure around 4Torr at room temperature. The XeF<sub>2</sub> gas is an isotropic etchant for silicon. The etch selectivity between silicon and silicon dioxide in XeF<sub>2</sub> gas is better than 1:2000. This rate is much higher for most of the metals and the silicides [8-9].

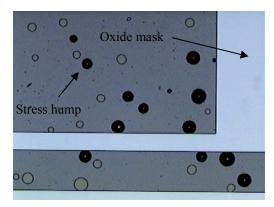

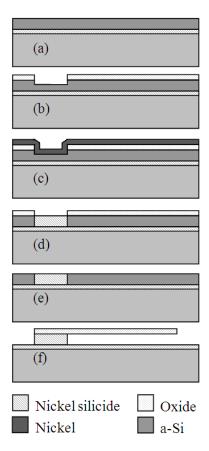

Figure 4 shows the different steps of the fabrication process. A very thin layer of NiSi has to be formed on the substrate before the a-Si deposition. This layer plays two crucial roles. It forms the etch-stop layer during the release step, and promotes adhesion between top silicide layer (the anchor) and the substrate. Without this layer, the stress induced by the nickel, and the formed silicide during annealing, could cause the film to delaminate from the substrate and form stress-humps. Stress-hump formation becomes a major issue with relatively thick sacrificial layers (a few hundred nanometres). To apply our process to structures with dimensions larger than one hundred microns, and in order to facilitate the structure release process, we have to increase the sacrificial layer thickness to hundreds of nanometres. Even with implementing etch holes in the structure design, releasing a large structure with a very thin sacrificial layer (100nm), could be very time consuming, and sometimes impossible.

Lack of sufficient adhesion between the etch-stop and the top silicide layer limits the maximum thickness of the sacrificial layer. A thin layer of silicide has much better adhesion to the top silicide layer compare to the other films such as oxide and nitride; therefore we used it as the etchstop material. Figure 3 shows the formed stress-humps on a sample without the bottom silicide layer.

Figure 2: SEM image of a compliant mechanism fabricated by our process. The structure has been buckled out of the plane and locked in place.

Figure 3: Stress induced humps on silicide sample after annealing at 350°C. There is no stress-hump over the areas covered by the oxide diffusion mask

The thin etch-stop silicide layer is formed by evaporating 10nm nickel on the silicon substrate followed by thermal annealing at 350°C in forming gas atmosphere for 10 minutes. 300nm thick layer of PECVD a-Si is then deposited on the bottom silicide layer using silane chemistry at 350°C. After sacrificial layer deposition, a 200nm thick layer of PECVD oxide is deposited to act as a diffusion mask for the silicidation process. The first mask is used to open the anchor windows into the oxide layer. To compensate the growth of the nickel silicide above the original a-Si surface, part of the a-Si is etched by RIE. The a-Si etch depth is equal to the amount that the silicide grows above the surface. This guarantees that the silicide layer has

Figure 4: The process steps: (a) sacrificial layer with bottom silicide layer, (b) partially etched a-Si layer with oxide mask, (c) evaporated nickel on a-Si before annealing, (d) formed silicide after annealing, un-reacted nickel removed, (e) a-Si and silicide after striping the oxide, (f) deposited, patterned, and released structure.

the same thickness as the a-Si layer. To form the silicide and make the anchors, 200nm thick nickel film is evaporated and annealed. We anneal the film in forming gas (5% hydrogen in nitrogen) atmosphere at 350°C for 45 minutes. The nickel layer is thermally evaporated with pre-deposition pressure of 1e<sup>-7</sup> Torr and deposition rate of 1Å/s. The non-reacted nickel is etched by a mixture of H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub> at 70°C for 5 minutes and the oxide layer is etched by BOE. Then, the structural layers are deposited, patterned and released to form the structure.

We used thermal evaporation to deposit nickel because the sputtered nickel requires more thermal effort to form NiSi compare to the evaporated nickel [10]. The evaporated nickel easily forms silicide with composition close to 50% silicon and 50% nickel at temperatures around 350°C. The sputtered nickel film has to be annealed at temperatures as high as 600°C to form the mono-silicide [10].

## RESULT AND DISCUSSION

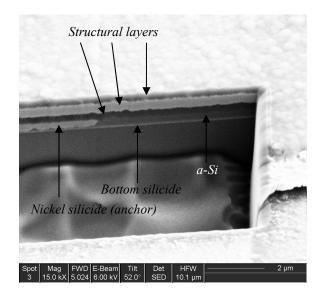

Cross section of the structure and its anchor, before releasing, is illustrated in Figure 5. The figure shows that the anchor and the sacrificial layer have the same thickness,

and that the structural layers are virtually planar. The maximum measured step between the anchor and the original a-Si surface is about 10nm.

This step could be a result of the processes variation during a-Si etching, or the inconsistency in composition of the nickel silicide. The final thickness of the silicide layer is defined by the original thickness of the a-Si, because nickel completely consumes the silicon to form the anchors. If the etch depth of the a-Si by RIE is not equal to the desired calculated depth, the final surface of the silicide could be lower or higher compare to the original a-Si surface. The other reason for this discrepancy could be the real composition of the silicide layer. Our process calculations are based on formation of a perfectly mono-silicide film after annealing. If the annealed film partially contains the other phases of the silicide, the final silicide thickness and the amount that it grows above the initial a-Si surface will be different. However, the actual thickness of the silicide layer and its growth above the initial silicon surface can be measured and be used to compensate the processes variations.

Figure 5: A milled trench into the substrate using FIB reveals the cross section of different layers. Notice that the anchor and sacrificial layer have the same thickness, and the structural layers are virtually planar.

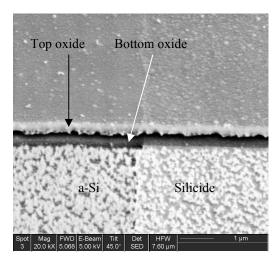

The formed silicide has rougher surface compare to the original a-Si surface. Therefore, part of the oxide that lies above the silicide has rougher surface compare to the part that is over the a-Si film. Figure 6 shows the surface roughness difference between the a-Si and the formed silicide layer. We noticed that the film surface roughness is a function of annealing temperature. Higher temperature results in a rougher surface. The stress of the film is also a function of temperature. At temperatures below 350°C, the film stress is compressive but above it the film stress becomes tensile and increases by temperature [4]

Figure 6: anchor, sacrificial layer and the structural layers before release step. The silicide surface is rougher than the a-Si layer.

## **CONCLUSION**

We have reported a novel sacrificial surface micromachining process that uses the nickel silicide to enhance the fabrication of the freestanding structures and the compliant mechanisms in two ways: I) Increasing the stiffness and mechanical robustness of the structures by eliminating the step between the structure and its anchor. II) Inherently eliminating the step coverage issue related to the deposition processes. The height difference between the structure and its anchor can be reduce significantly to less than 5% of the original sacrificial layer thickness. By a well controlled process, a virtually flat structure could be fabricated.

## REFERENCES

[1] D. Xua, S.R. Dasa, C.J. Petersb, L.E. Ericksona, "Material aspects of nickel silicide for ULSI applications", *Thin Solid Films*, 326 (1998) 143–150

- [2] J. Foggiatoa, W. S. Yooa, M. Ouakninea, T. Murakamib, T. Fukadab, "Optimizing the formation of nickel silicide", *Materials and Science Engineering B*, 114-115 (2004), p56-60

- [3] L.J. Chen, "Silicide Technology for Integrated Circuits", Institution of electrical Engineers, London, 2004

- [4] M. Qin, M.C. Poon, C.Y. Yuen, "A study of nickel silicide film as a mechanical material", *Sensors and Actuators A*, 87 (2000), p 90–95

- [5] M. Qin, V. M. C. Poon, "Young's modulus measurement of nickel silicide film on crystal silicon by a surface profiler", *Journal of Materials Science Letters*, 19 (2000), p 2243-5

- [6] M Bhaskaran, S Sriram, LW Sim, "Nickel silicide thin films as masking and structural layers for silicon bulk micro-machining by potassium hydroxide wet etching", J. Micromech. Microeng. 18 (2008) 095002

- [7] K. Khosraviani, and A. M. Leung, "The NanoGap Pirani — A Pressure Sensor with Superior Linearity in Atmospheric Pressure Range", J. Micromech. Microeng. 19 (2009) 045007.

- [8] I.W.T. Chan, K.B. Brown, R.P.W. Lawson, A.M. Robinson, Y. Ma, and D. Strembicke, "Gas Phase Pulse Etching of Silicon For MEMS With Xenon Difluoride", *Proceedings of the IEEE Canadian Conference on Electrical and Computer Engineering*, 1999, p 1637-42

- [9] N.H. Tea, V. Milanovi'c, C.A. Zincke, J.S. Suehle, M. Gaitan, M.E. Zaghloul, and J. Geist, "Hybrid Postprocessing Etching for CMOS-Compatible MEMS", *Journal of Microelectromechanical Systems*, vol. 6, no. 4, 1997, p 363-72

- [10] M. Bhaskaran, S. Sriram, J. du Plessis and A.S. Holland, "Composition analysis of nickel silicide formed from evaporated and sputtered nickel for microsystem devices", *Electronics Letters*, 12, 2007, Vol. 43, No. 8