## 23.4 A Filtering Technique to Lower Oscillator Phase Noise

Emad Hegazi, Henrik Sjöland, Asad Abidi

Electrical Engineering Department, University of California, Los Angeles, CA

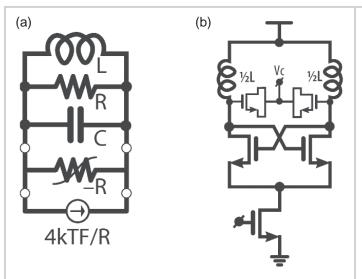

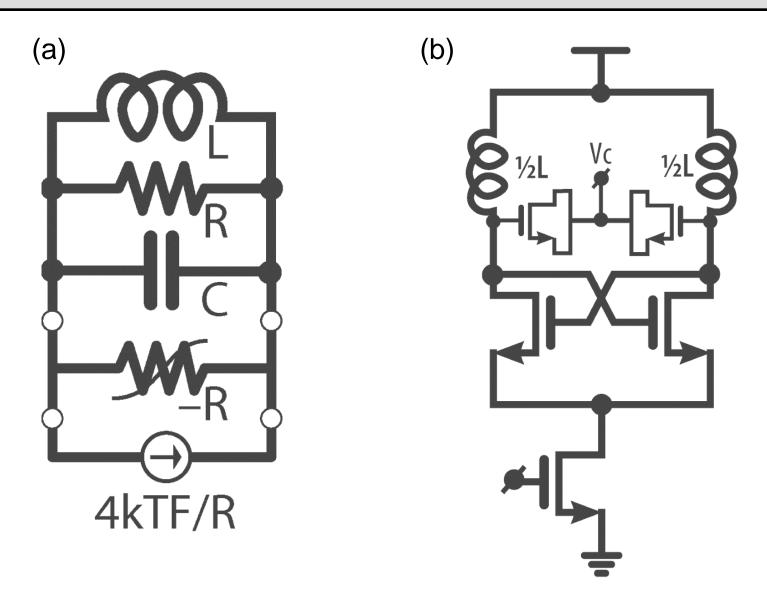

Wireless applications are pushing the required phase noise in integrated oscillators to ever lower levels. Integrated oscillator circuits published so far use tuning inductors that are either fully integrated, partly integrated, or discrete, with quality factors spanning a large range. However, lacking a clear understanding of the physical processes of phase noise, it is difficult to compare the relative merits of these VCOs in a normalized sense. An LC oscillator consists of a lossy resonator, and an active circuit across it to overcome this loss (Figure 23.4.1). In steady-state, the active circuit presents a large-signal negative resistance equal to the equivalent parallel loss resistance R across the resonator. The phase noise sidebands around the oscillation frequency are given by:

$$L(w_m) = \frac{4FkTR}{V^2_{RMS}} \left(\frac{\omega_0}{2Qw_m}\right)^2 \tag{1}$$

where the active circuit noise density is F-1 times the resonator noise, and VRMS is the RMS oscillation amplitude. If the negative resistor generates the same noise as the resonator loss resistor, F=2. In reality, the active circuit realizing the negative resistor may generate less noise. The resulting F defines a fundamental lower limit on oscillator phase noise.

A recently-developed physical model of phase noise in the differential LC VCO [1] shows that during current-limited operation, that is, for amplitudes where the current source FET remains in saturation, F consists of the following terms arising from the resonator loss, the commutating differential pair, and the current source:

$$F = 1 + \frac{4\gamma RI}{\pi V_0} + \gamma \frac{8}{9} g_{mbias} R \tag{2}$$

I is the bias current,  $\gamma$  is the FET noise factor (2/3 for long channels), and  $g_{mbias}$  refers to the current source FET. The analysis [1] gives two important insights. First, the middle term in 3) signifying phase noise induced by differential pair thermal noise is independent of the specifics of the transistors in the pair. Second, the commutating differential pair translates noise originating in the current source at frequencies around the  $2^{nd}$  harmonic to the oscillation frequency and to the  $3^{rd}$  harmonic. Half of the translated noise at the fundamental contributes phase noise. The differential pair also upconverts baseband noise in the current source into amplitude noise across the resonator [1].

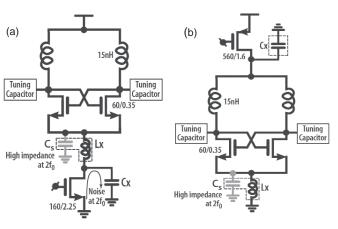

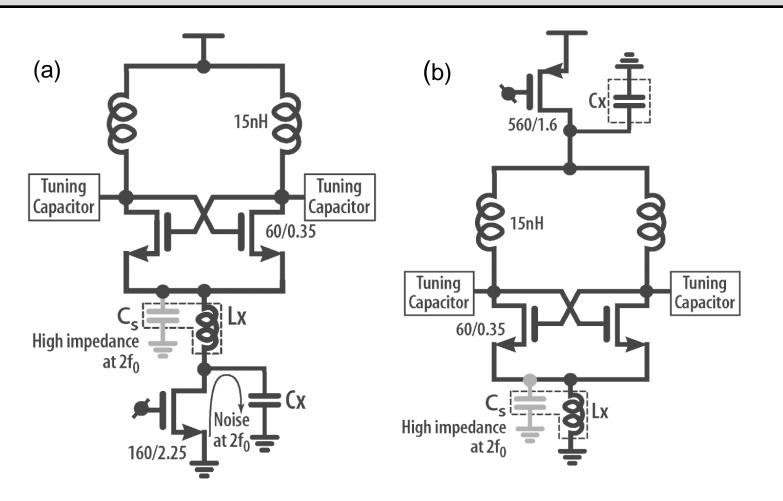

Now the oscillator circuit may be designed for least phase noise. Equation 2 shows that the relative contribution of the resonator loss is fixed. In the current-limited regime, the amplitude is proportional to IR, so the differential pair contributes a constant  $2\gamma$  to the middle term of F. However, the higher the amplitude, the lower the phase noise. In most oscillators the third term in Equation 2 accounts for about 75% to the total noise factor, F. The current source plays a dual role in the circuit: it defines the bias current, and it also gives a high AC impedance to ground so that when the oscillation voltage crosses  $V_t$  and forces one differential pair FET into triode, the quality factor does not degrade. A properly-designed LC network (Figure 23.4.2) can preserve these two roles of the current source but essentially eliminate its contribution to phase noise. A capacitor, Cx, and

inductor, Lx, in series with the current source form a lowpass filter which shunts noise at  $2f_0$  from the current source FET to ground. Furthermore, Lx is chosen to resonate at  $2f_0$  in parallel with the capacitance Cs at the common source of the differential pair, approximating a high impedance current source at  $2f_0$ . With this network present, the oscillator noise factor F is lowered by more than 2x, and the noise factor in (2) approaches the fundamental lower limit of  $(1+\gamma)$ . In the top-biased VCO, this filter is realized by a capacitor (Cx) shunting the current source FET, and an inductor (Lx) in series with the common source of the differential pair to ground.

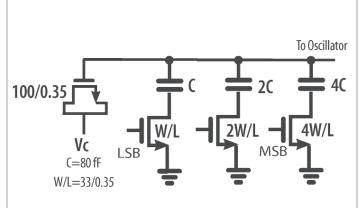

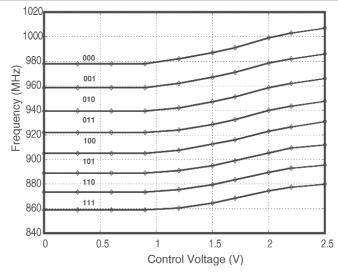

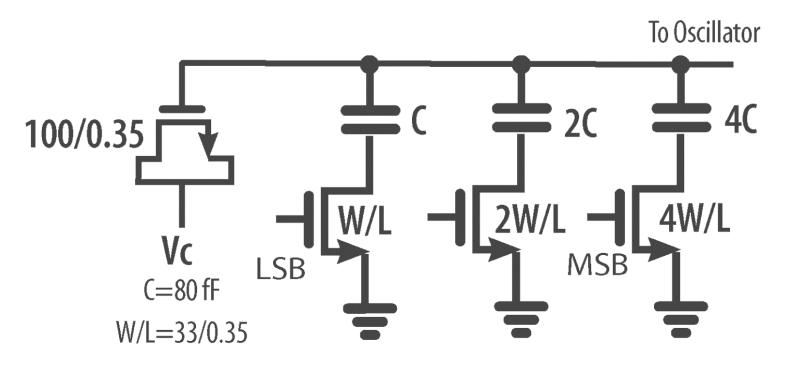

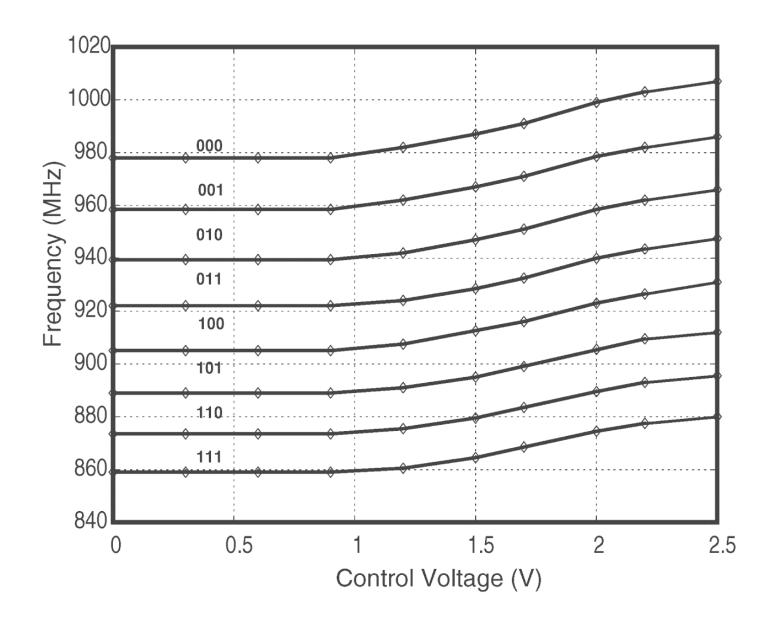

This LC network does not filter low frequency noise in the current source, which appears as amplitude noise around the oscillation frequency. A voltage-dependent tuning capacitor will convert this into phase noise. To suppress this effect, the VCO is coarsely tuned by an array of switchable fixed binary-weighted capacitors, shunted by a small MOS varactor to interpolate between the discrete steps (Figure 23.4.3) [2]. Overlap between the steps guarantees continuous frequency coverage, even with component tolerances (Figure 23.4.4). A mixed-signal PLL for this discretely tuned oscillator is described elsewhere [3].

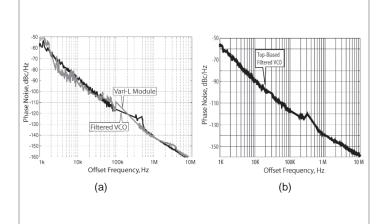

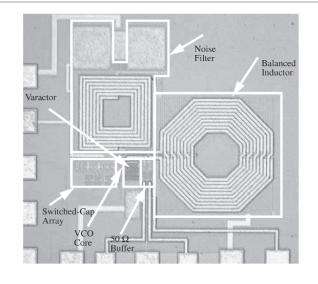

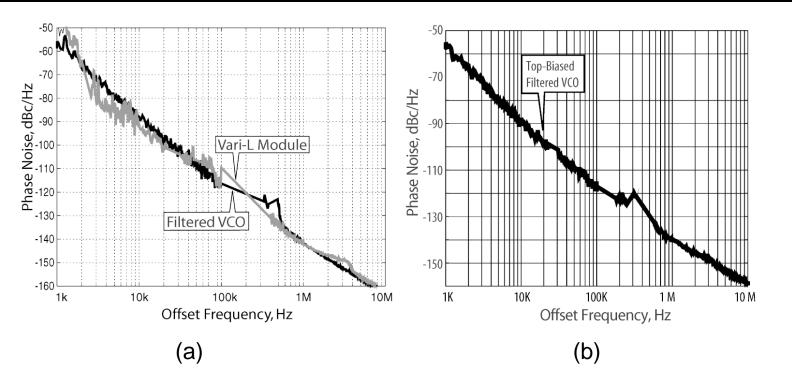

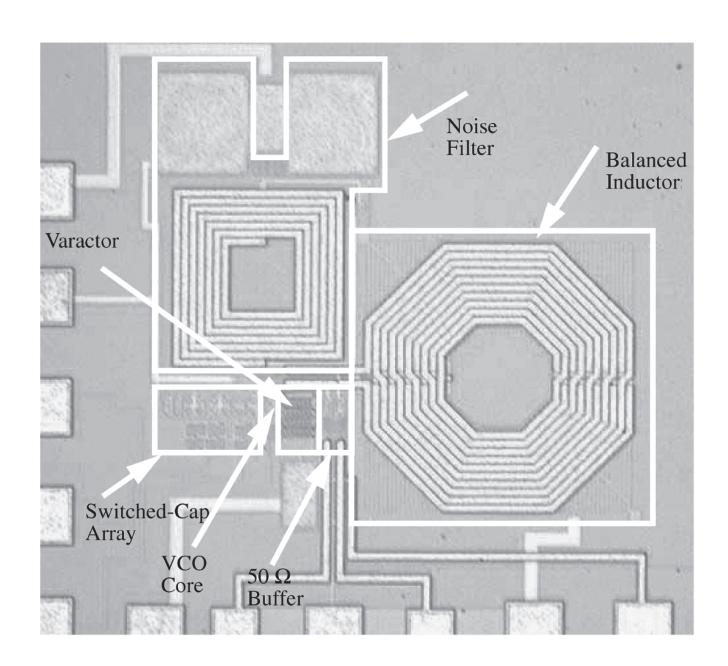

Three test oscillators are implemented using the noise filtering schemes described above: a top-biased and a tail-biased VCO for the 1GHz band, and a tail-biased VCO for the 2.2GHz band. These CMOS circuits are fabricated in the STMicroelectronics BiCMOS 6M process, whose substrate resistivity is 15 $\Omega$ -cm. The 1GHz oscillators use a 15nH octagonal differential inductor with a Metal-1 ground shield with estimated Q is 10. The noise filters use a square spiral inductor Lx=10nH, and an MIM capacitor Cx=40pF. Measured phase noise at 3MHz offset from a 1GHz carrier is -148.5 and -152dBc/Hz (Figure 23.4.5) for the topbiased and tail-biased VCO, respectively, both biased at 3.65mA from 2.5V. The 2.2GHz VCO gives a measured phase noise of -148dBc/Hz at 15MHz offset from a 2.1GHz carrier. A 5.5nH octagonal differential inductor with a poly-shield is used for the tank, and a 4.9nH square spiral is used in the filter. Phase noise is measured on an HP E5500 frequency discriminator with calibrated FM rate and deviation. A delay line of 31ns resolves the low levels of phase noise.

For comparison, the phase noise of the widely used Vari-L VCO190-100AT module oscillating at 1GHz is also measured on the same setup. The module consumes 11.6mA from 5V, and includes a 50 $\Omega$  buffer to deliver –1dBm output. It is assumed that one third of the total current biases the VCO core. The fully integrated VCO with noise filter achieves slightly better phase noise than the module at half the power consumption. The filtering technique described here arises from an understanding of phase noise mechanisms, and leads to oscillators that perform close to the fundamental limit set by intrinsic quality factor of the resonator. With noise filtering, fully-integrated CMOS VCOs can outstrip the phase noise of conventional oscillator modules (Table 23.4.1).

## References:

[1] J. J. Rael and A. A. Abidi, "Physical Processes of Phase Noise in Differential LC Oscillators," in Custom IC Conf., Orlando, FL, pp. 569-572, 2000.

[2] A. Kral et al., "RF-CMOS oscillators with switched tuning," in Custom IC Conf., Santa Clara, CA, pp. 555-558, 1998.

[3] F. Behbahani et al., "A broad-band tunable CMOS channel-select filter for a low-IF wireless receiver," IEEE J. of Solid-State Circuits, vol. 35, no. 4, pp. 476-89, 2000.

Figure 23.4.1: (a) Fundamental noise source in an oscillator. (b) Conventional differential oscillator circuit with MOS tuning varactor.

Figure 23.4.2: (a) Tail-biased and (b) top-biased differential oscillators, showing noise filter (Lx, Cx).

Figure 23.4.3: Tuning capacitor consists of switched binary-weighted capacitor array, and small MOS varactor.

Figure 23.4.4: Measured tuning characteristics of tail-biased VCO. Segments correspond to 3b control word settings on switched capacitor array.

Figure 23.4.5: Phase noise at 1GHz measured on (a) tail-biased VCO and (b) top-biased VCO, both with noise filters. Superimposed on (a) is phase noise of Vari\_L module, also at 1GHz, measured on the same instrument.

Figure 23.4.6: Chip micrograph.

|                       | Oscillator Circuit<br>(Tech./Resonator) | f <sub>。</sub><br>(GHz) | Vdd<br>(V) | ldd<br>(mA) | £<br>(dBc/Hz) | Offset<br>(MHz) | FoM<br>(dB) |

|-----------------------|-----------------------------------------|-------------------------|------------|-------------|---------------|-----------------|-------------|

| This Work Tail-Biased | CMOS/Int. LC                            | 1                       | 2.5        | 3.65        | -152          | 3               | 192.9       |

| This Work Top-Biased  | CMOS/Int. LC                            | 1                       | 2.5        | 3.65        | -148.5        | 3               | 189.4       |

| Vari-L190             | Module                                  | 1                       | 5          | ~3.8        | -150          | 3               | 187.7       |

| Svelto, CICC 2000     | CMOS/Bondwire                           | 1.9                     | 2          | 1           | -120.5        | 0.6             | 187         |

| Lin, ISSCC 2000       | Bipolar/Int. LC                         | 1.5                     | 1.9        | 20          | -148          | 3               | 186         |

| Orsatti, CICC 1999    | CMOS/Ext LC                             | 0.9                     | 3          | 1.6         | -112.7        | 0.1             | 185.3       |

Table 23.4.1: Comparison of noise-filtered VCOs with other recent VCOs and modules. Figure of merit (FOM) normalizes phase noise to frequency, offset, and power consumption.

Figure 23.4.1: (a) Fundamental noise source in an oscillator. (b) Conventional differential oscillator circuit with MOS tuning varactor.

Figure 23.4.2: (a) Tail-biased and (b) top-biased differential oscillators, showing noise filter (Lx, Cx).

Figure 23.4.3: Tuning capacitor consists of switched binary-weighted capacitor array, and small MOS varactor.

Figure 23.4.4: Measured tuning characteristics of tail-biased VCO. Segments correspond to 3b control word settings on switched capacitor array.

Figure 23.4.5: Phase noise at 1GHz measured on (a) tail-biased VCO and (b) top -biased VCO, both with noise filters. Superimposed on (a) is phase noise of Vari\_L module, also at 1GHz, measured on the same instrument.

Figure 23.4.6: Chip micrograph.

|                       | Oscillator Circuit<br>(Tech./Resonator) | f <sub>。</sub><br>(GHz) | Vdd<br>(V) | ldd<br>(mA) | Ω<br>(dBc/Hz) | Offset<br>(MHz) | FoM<br>(dB) |

|-----------------------|-----------------------------------------|-------------------------|------------|-------------|---------------|-----------------|-------------|

| This Work Tail-Biased | CMOS/Int. LC                            | 1                       | 2.5        | 3.65        | -152          | 3               | 192.9       |

| This Work Top-Biased  | CMOS/Int. LC                            | 1                       | 2.5        | 3.65        | -148.5        | 3               | 189.4       |

| Vari-L190             | Module                                  | 1                       | 5          | ~3.8        | -150          | 3               | 187.7       |

| Svelto, CICC 2000     | CMOS/Bondwire                           | 1.9                     | 2          | 1           | -120.5        | 0.6             | 187         |

| Lin, ISSCC 2000       | Bipolar/Int. LC                         | 1.5                     | 1.9        | 20          | -148          | 3               | 186         |

| Orsatti, CICC 1999    | CMOS/Ext LC                             | 0.9                     | 3          | 1.6         | -112.7        | 0.1             | 185.3       |

Table 23.4.1: Comparison of noise-filtered VCOs with other recent VCOs and modules. Figure of merit (FOM) normalizes phase noise to frequency, offset, and power consumption.