# LOW POWER TRANSISTORS AND QUANTUM PHYSICS

## BASED ON LOW DIMENSIONAL MATERIALS

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Fan Chen

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

Jan 2017

Purdue University

West Lafayette, Indiana

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF DISSERTATION APPROVAL

Dr. Gerhard Klimeck Co-Chair

Department of Electrical and Computer Engineering

Dr. Michael J. Manfra Co-Chair

Department of Physics and Astronomy

Dr. Zhihong Chen

Department of Electrical and Computer Engineering

Dr. Yong P. Chen

Department of Physics and Astronomy

Dr. Supriyo Datta

Department of Electrical and Computer Engineering

Dr. John R. Peterson

Department of Physics and Astronomy

### Approved by:

Dr. John P. Finley

Head of the Department of Physics and Astronomy Graduate Program

This Thesis is Dedicated to my Parents and Family.

For their endless love, support, encouragement and sacrifices.

#### ACKNOWLEDGMENTS

I would like to express my gratitude to my advisor, Professor G. Klimeck, for the valuable insights he provided for this research and the continuous support throughout my PhD. I would like to thank him for providing all the necessary computing resources. He introduced me to the world of high performance computing. I also want to provide great thanks to my co-advisor, Professor M. Manfra, for the mentoring, useful advices and the physics insights he provided throughout my Ph.D.

I would also like to thank Professor Z. Chen, Professor Y. Chen, Professor S. Datta, Professor J. Peterson for serving on my advisory committee. They have provided key insights in the discussion and improved the quality of my Ph.D work.

I am grateful to Prof. R. Rahman, Prof. Z. Chen, Prof. J. Appenzeller and Prof. T. Kubis who provided a lot of support during the past few years of my PhD. They provided great help to improve the quality of my work in many aspects. The problem solving skills in Physics and Engineering will be invaluable experience in my future career pursuits.

I am also thankful to Dr. Hesameddin Ilatikhameneh, Dr. Luis A. Jauregui and Dr. Yaohua Tan who provided great intellectual support to my projects. I would also like to thank our research faculties team of Prof. Jim Fonseca, Dr. Bozidar Novakovic, Dr. Jun Huang and Prof. Michael Povolotskyi who offered support. I want also to provide great thanks to Dr. Hesameddin Ilatikhameneh, Dr. Luis A. Jauregui, Dr. Yaohua Tan, Dr. Tao Chu, Tarek Ameen, Chinyi Chen, Daniel Valencia and Md Sharafat Hossain who have worked closely with me, which not only provides the insights of the work but also greatly improves my collaboration, teamwork and

also mentoring skills.

I want to offer my special thanks to my best friend Archana Tankasala, who offered great support and encouragement during my tough times throughout my Ph.D. I would also like to thank other group friends Kai Miao, Dr. Yaohua Tan, Dr. Matthias Tan, Dr. Mehdi Salmani, Tarek Ameen, Dr. Hesameddin Ilatikhameneh and my friends from physics department, Dr. Mayra D Cervantes, Dr. Lingshan Xu, Dr. Yunlong Zi, Dr. Jiuning Hu, Dr. Tailung Wu, Mridula Damodaran, Peter Anderson, Wonjun Park, Jack Chung, Yang Xu, Tianli Feng not only for the emotional support and useful advice but also for the colorful life they made it being in Purdue.

I would like to greatly thank Dr. Yu He, Dr. Zhengping Jiang, James Chales, Prasad Sarangapani, Daniel Mejia, Pengyu Long, Yu Wang, Yuling Hsueh, Daniel Valencia, Yuanchen Chu and KuangChung Wang for all the technical support provided and interesting and helpful discussions. A lot of work cannot be done without their support.

I would like to thank all my colleagues from the NCN and the Klimeck group for providing a stimulating and fun environment to learn and grow. Lastly, and most importantly, I wish to thank my parents, my family and also my boyfriend Siwei Fan for their love and support.

# TABLE OF CONTENTS

|    |       |         |                                                                     | Page |

|----|-------|---------|---------------------------------------------------------------------|------|

| LI | ST O  | F TAB   | BLES                                                                | ix   |

| LI | ST O  | F FIG   | URES                                                                | X    |

| 1  | Intro | oductio | n                                                                   | 1    |

|    | 1.1   | Challe  | enge of Device Scaling                                              | 1    |

|    | 1.2   | Challe  | enge of Tunnel FET                                                  | 1    |

|    | 1.3   | 2D ma   | aterials                                                            | 2    |

|    | 1.4   | Topol   | ogical Insulators                                                   | 4    |

| 2  | Bila  | yer Gra | phene                                                               | 5    |

|    | 2.1   | Introd  | luction                                                             | 5    |

|    | 2.2   | Tight   | Binding Model                                                       | 6    |

|    |       | 2.2.1   | Vertical Strain                                                     | 8    |

|    |       | 2.2.2   | Tunable Band Gap                                                    | 9    |

|    |       | 2.2.3   | Transport                                                           | 12   |

|    | 2.3   | Bilaye  | er Graphene p-n tunneling junction                                  | 15   |

|    |       | 2.3.1   | Device Fabrication                                                  | 18   |

|    |       | 2.3.2   | One Gate Measurement                                                | 18   |

|    |       | 2.3.3   | Two gates Measurement                                               | 20   |

|    | 2.4   | Simul   | ation Work of BLG p-n junction                                      | 21   |

|    |       | 2.4.1   | Simulation of p-n junction two gate measurement                     | 21   |

|    |       | 2.4.2   | Density of States and Explanation                                   | 23   |

|    |       | 2.4.3   | Towards Steep Slope                                                 | 25   |

|    | 2.5   | _       | Performance Bilayer Graphene Electrostatically Doped -Tunnel device | 27   |

|    |       | 2.5.1   |                                                                     | 29   |

|   |       |          |                                                                | Page |

|---|-------|----------|----------------------------------------------------------------|------|

|   |       | 2.5.2    | Device Operation                                               | 29   |

|   |       | 2.5.3    | IV performance                                                 | 31   |

|   |       | 2.5.4    | Geometry Sensitivity                                           | 33   |

|   | 2.6   | Concl    | usion                                                          | 34   |

| 3 | Thic  | kness E  | Engineered Tunnel Field-Effect Transistors based on Phosphoren | e 35 |

|   | 3.1   | Introd   | luction                                                        | 35   |

|   | 3.2   | The a    | dvantages of Thickness Engineered TFETs                        | 35   |

|   | 3.3   | Simul    | ation Details                                                  | 38   |

|   | 3.4   | TE-T     | FET Device Performance                                         | 38   |

|   | 3.5   | Device   | e Scaling                                                      | 40   |

|   | 3.6   | Capac    | citance and Charge Distribution                                | 42   |

|   | 3.7   | Energ    | y Delay Product                                                | 43   |

|   | 3.8   | Concl    | usion                                                          | 45   |

| 4 | Inter | rlayer T | TFETs                                                          | 47   |

|   | 4.1   | Interla  | ayer TFETs from vertically stacked 2D materials                | 47   |

|   | 4.2   | Gr/hI    | BN/Gr Resonant Tunneling                                       | 49   |

|   |       | 4.2.1    | Vertical Tunneling Model                                       | 51   |

|   |       | 4.2.2    | Negative Differential Resistance (NDR)                         | 51   |

|   |       | 4.2.3    | Calibrating to Experiments                                     | 52   |

|   |       | 4.2.4    | Conclusion                                                     | 54   |

|   | 4.3   | MoS2-    | -WTe2 Interlayer TFETs                                         | 55   |

|   |       | 4.3.1    | The advantages of interlayer TFETs                             | 56   |

|   |       | 4.3.2    | Approach                                                       | 57   |

|   |       | 4.3.3    | Device Operation Mechanism                                     | 60   |

|   |       | 4.3.4    | The importance of extension region                             | 62   |

|   |       | 4.3.5    | Negative Capacitance                                           | 62   |

|   |       | 4.3.6    | Device Scaling and energy delay product                        | 65   |

|   |       | 4.3.7    | Conclusion                                                     | 66   |

|    |           |                                                           | Page |

|----|-----------|-----------------------------------------------------------|------|

| 5  | Topo      | ological Insulator                                        | 68   |

|    | 5.1       | Introduction to Topological Insulators                    | 68   |

|    | 5.2       | Method                                                    | 71   |

|    | 5.3       | Aharonov-Bhom Effect in TI nanowires                      | 73   |

|    | 5.4       | Surfaces of Different Atomic Compositions in TI nanowires | 75   |

|    | 5.5       | Different Fermi Velocities for Different Surfaces         | 76   |

|    | 5.6       | In-surface Confinement of Wavefunctions                   | 79   |

|    | 5.7       | Conclusion                                                | 80   |

| RI | EFER      | ENCES                                                     | 86   |

| VI | $T\Delta$ |                                                           | 96   |

# LIST OF TABLES

| Tabl | le                                                                                                                                                                                                                                                                    | Page |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1  | Bilayer graphene material properties: in-plane and inter-plane hopping parameters $\gamma_0$ and $\gamma_1$ , maximum bandgap Eg, electron effective mass me*, in-plane and out-plane relative dielectric constant $\sigma_r^{in}$ and $\sigma_r^{out}$ , inter-layer |      |

| 3.1  | distance c                                                                                                                                                                                                                                                            | 1    |

|      | plane relative dielectric constant $\epsilon^{in}$ and $\epsilon^{out}$                                                                                                                                                                                               | 39   |

# LIST OF FIGURES

| Figu | re                                                                                                                                                                                                                  | Page |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

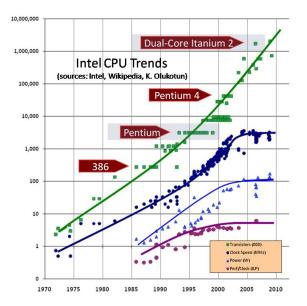

| 1.1  | Intel CPU Trends. (Source: [1])                                                                                                                                                                                     | 2    |

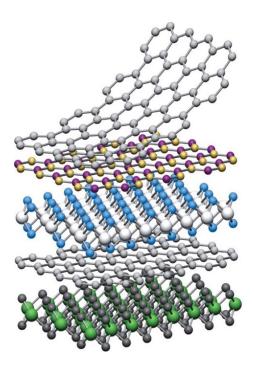

| 1.2  | Stacking 2D materials. (Source: [2])                                                                                                                                                                                | 3    |

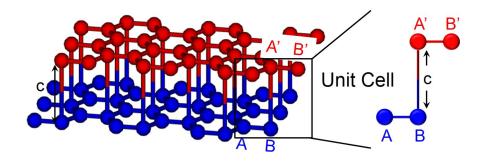

| 2.1  | Atomic structure and unit cell of bilayer graphene                                                                                                                                                                  | 6    |

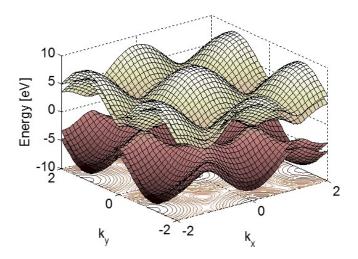

| 2.2  | Bilayer graphene band diagram in 2D k space                                                                                                                                                                         | 7    |

| 2.3  | Bandgap of bilayer graphene changing with a vertical electric field. The bandgap increases with an increasing field up to a saturation point                                                                        | 8    |

| 2.4  | Bandgap of bilayer graphene changing with a vertical electric field from [25]. The bandgap increases with an increasing field up to a saturation point                                                              | 10   |

| 2.5  | Tunable band gap in BLG as a function of the displacement field from [26].                                                                                                                                          | 10   |

| 2.6  | Band structure of strained bilayer graphene without (a) and with (b) vertical field $[V/nm]$ . Left, middle and right figures correspond to band structures of bilayer graphene with different strain values        | 11   |

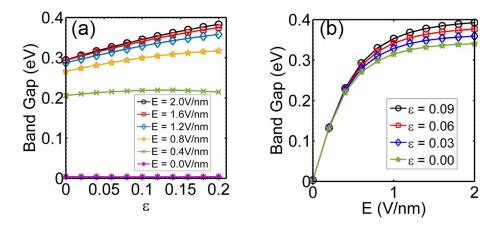

| 2.7  | (a) Band gap changes with strain applied in different vertical fields $E[V/nm]$ (b) Band gap increases with vertical field. Saturation band gap increases with larger strain                                        | . 12 |

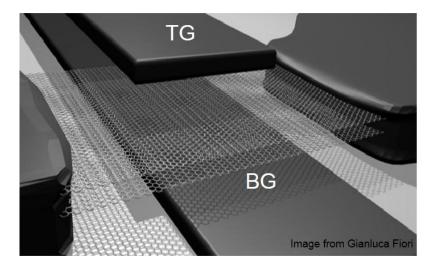

| 2.8  | Double layer device structure with one top gate and one bottom gate.                                                                                                                                                | 13   |

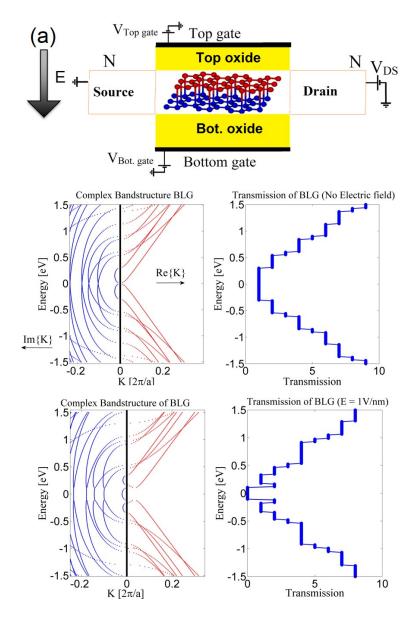

| 2.9  | (a): Bilayer graphene FET device and atomic structure. Bandgap and transmission for a BLG device in a small (b) and large (c) electric field.                                                                       | 14   |

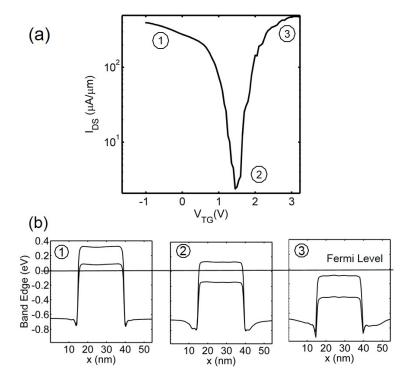

| 2.10 | (a): V shaped transfer characteristics of bilayer graphene double gate FET. (b): band edge plot along transport direction for the ON, OFF and ON state                                                              | 15   |

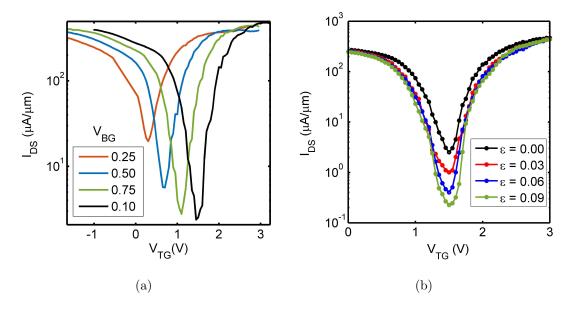

| 2.11 | (a) A shift in the valley of the V shaped transfer characteristics due to the change of bottom gate voltage $V_{BG}$ .(b) IV curves for double gate bilayer graphene devices applied with different vertical strain | 16   |

| 2.12 | Bandgap of bilayer graphene changing with a vertical electric field. The bandgap increases with an increasing field up to a saturation point                                                                        | 19   |

| 2.13 | Bilayer Graphene PN junction one gate measurement                                                                                                                                                                   | 21   |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.14 | Bilayer graphene PN junction two gate measurement                                                                                                                                                                                                                                                                                                                                                                                                      | 21   |

| 2.15 | Electrically doped BLG PN junction structure used in simulation                                                                                                                                                                                                                                                                                                                                                                                        | 22   |

| 2.16 | I-V characteristics of electrically doped BLG PN junction for different $V_{TG2}$ . Each curve differs from previous one by $0.2V$                                                                                                                                                                                                                                                                                                                     | 22   |

| 2.17 | Density of states (DOS) plot with energy resolved current aligned at four different $V_{TG1}$ for a fixed $V_{TG2}$ value                                                                                                                                                                                                                                                                                                                              | 24   |

| 2.18 | (a) A comparison of potential profiles and current for two different $V_{TG2}$ values. (b, c) Density of states (DOS) plot with energy resolved current aligned at local maximum (3) at these two different $V_{TG2}$ values                                                                                                                                                                                                                           |      |

| 2.19 | BLG PN junction with steep slope                                                                                                                                                                                                                                                                                                                                                                                                                       | 26   |

| 2.20 | Energy resolved current aligned with band diagram at the ON and OFF of BLG PN junction with steep slope                                                                                                                                                                                                                                                                                                                                                | 27   |

| 2.21 | a) Physical structure of an electrically doped p-i-n BLG TFET. The band diagram in the OFF state of BED-TFET as a b) N-TFET, c) P-TFET.                                                                                                                                                                                                                                                                                                                | 28   |

| 2.22 | Energy-Delay comparison of BED-TFET (pink dot) with Dielectric Engineered (DE) WTe2 TFET (brown dot) [52], Nitride TFET (green dots) [53], TMD TFETs (red dots) [54–56] and Si MOSFET (blue dots) [51,57]                                                                                                                                                                                                                                              |      |

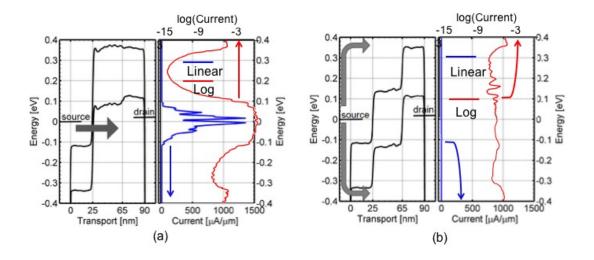

| 2.23 | The band diagram along the transport direction (left) and the energy resolved current (right) in (a) ON state and (b) OFF state                                                                                                                                                                                                                                                                                                                        | 31   |

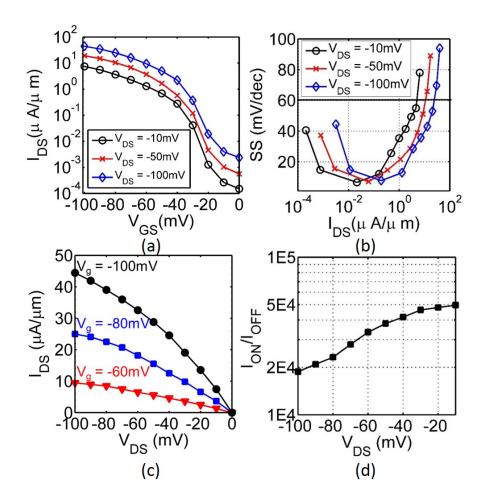

| 2.24 | a) Transfer characteristics of the BED-TFET with different drain-to-source voltages $V_{DS}$ . b) SS-Id plot with different drain-to-source voltages $V_{DS}$ . c) Output characteristics of the TFET at several gate voltages Vg. d) ON/OFF ratio with source-drain voltage $V_{DS}$ for the BED-TFET. $L_C$ , $L_D$ and S are kept at 40nm, 25nm and 0nm, respectively                                                                               |      |

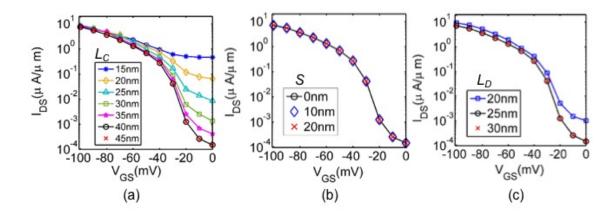

| 2.25 | $L_D$ , $L_C$ and $L_D$ are the gate length of the left/middle/right region in Fig. 1(a) (doping region/channel/doping region), respectively. The spacing between the gates is S. Transfer characteristics of the TFET with different a) channel length $L_C$ ( $L_D=25\mathrm{nm}$ , S=0nm), b) spacing S ( $L_C=40\mathrm{nm}$ , $L_D=25\mathrm{nm}$ ) and c) doping region length $L_D$ ( $L_C=40\mathrm{nm}$ , S=0nm).                             |      |

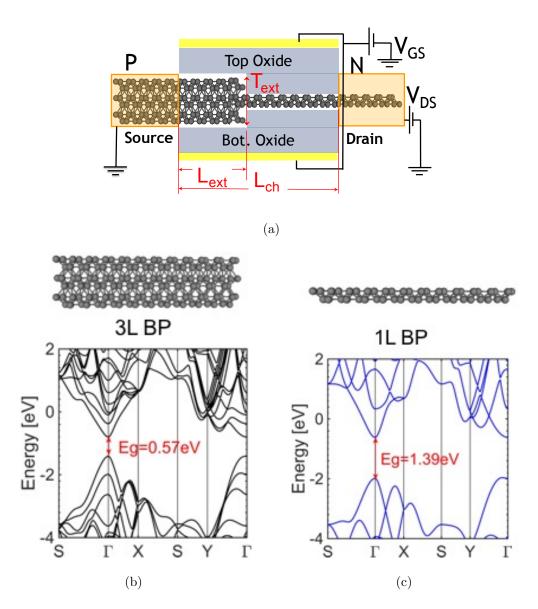

| 3.1  | (a) The cross-sectional device structure of layer engineered TFET (TE-TFET) based on phosphorene. It has a small Eg region at the source and the channel region near the source and a large Eg region in the rest of the device. The layer thickness of the length of the small band gap region inside channel is denoted by $L_{ext}$ and $T_{ext}$ . The band structure of (b) 3L phosphorene with Eg = 0.57eV; (c) 1L phosphorene with Eg = 1.39eV. | :    |

| Figu | ire                                                                                                                                                                                                                                                                                                                                                                               | Page |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

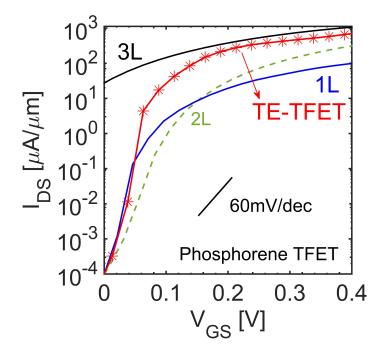

| 3.2  | The transfer characteristics of TE-TFET compared with different layer thickness TFET based on phosphorene.                                                                                                                                                                                                                                                                        | 40   |

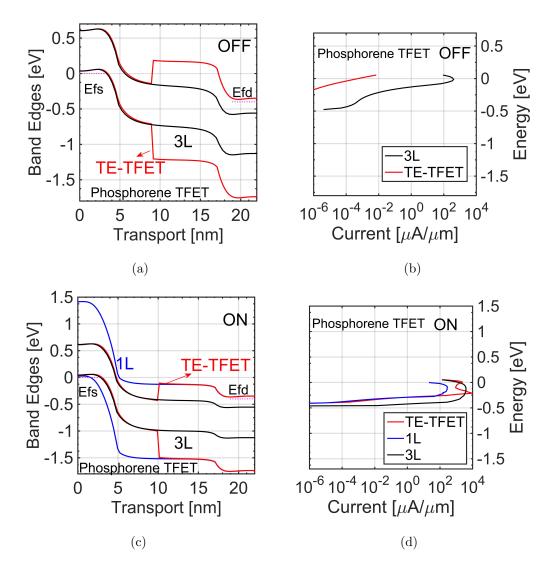

| 3.3  | The band edges of (a) TE-TFET with 3L TFET at OFF state and (b) TE-TFET with 1L and 3L TFET at ON state aligned with the energy resolved current (c) and (d) respectively                                                                                                                                                                                                         | 41   |

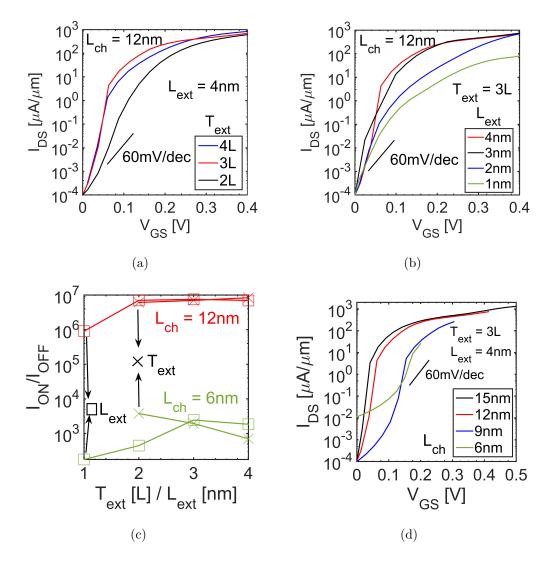

| 3.4  | Id-Vg curves for TE-TFETs of $L_{ch} = 12nm$ with different (a) $T_{ext}$ and (b) $L_{ext}$ . (c) The $I_{ON}/I_{OFF}$ change with respect to $T_{ext}$ and $L_{ext}$ for $L_{ch} = 12nm$ and $6nm$ . (d)The transfer characteristics with $L_{ch}$ of TE-TFETs with constant field scaling ( $E = V_{DD}/L_{ch} = 30 \text{V/nm}$ ) from 15nm to 6nm                             |      |

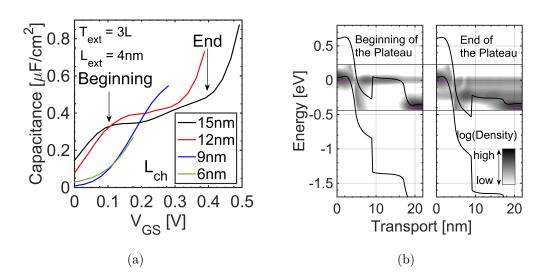

| 3.5  | (a) The transfer characteristics and (b) C-V of with $L_{ch}$ of TE-TFETs with constant field scaling ( $E=V_{DD}/L_{ch}=30\mathrm{V/nm}$ ) from 15nm to 6nm.                                                                                                                                                                                                                     | 44   |

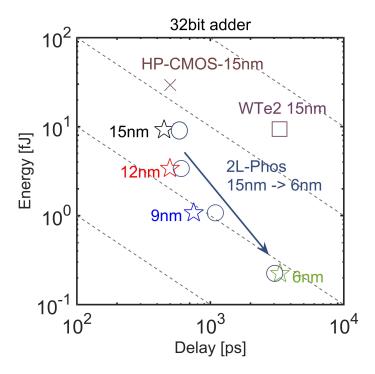

| 3.6  | Energy-Delay product of TE-TFETs in comparison 2L-TFETs [72] with their $L_{ch}$ scaled from 15nm to 6nm and a 15nm WTe2 TFET                                                                                                                                                                                                                                                     | 45   |

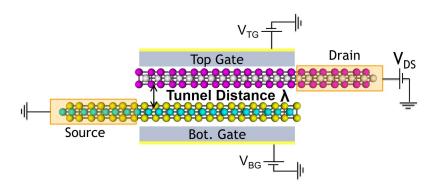

| 4.1  | Schematic diagram illustrating the cross-sectional view of 2D Vertical Hetero-structure TFET                                                                                                                                                                                                                                                                                      | 49   |

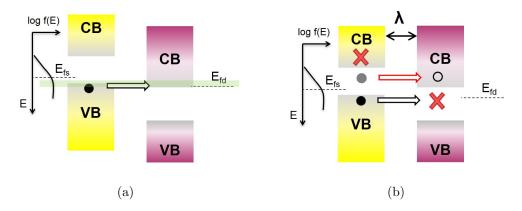

| 4.2  | Band diagrams along the vertical direction in Fig. 4.1 are shown in (a) ON and (b) OFF status                                                                                                                                                                                                                                                                                     | 50   |

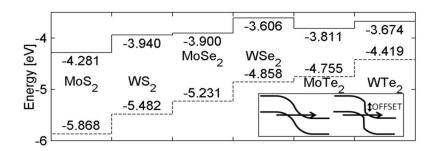

| 4.3  | The band alignments of different TMD materials based on electron affinity. Figure from [85]                                                                                                                                                                                                                                                                                       | 50   |

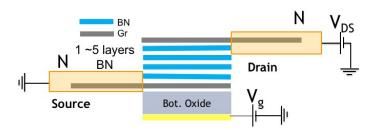

| 4.4  | The Structure of Gr/hBN/Gr Resonance Tunneling Devices. The number of BN layers can vary from 1 to 5 in the simulation study in order to compare with experiments.                                                                                                                                                                                                                | 50   |

| 4.5  | (a) Id-Vg curve for different gate voltage of a Gr/2 Layer hBN/Gr structure. We can see the NDR peaks. (b)-(c) Alignment of the potential of top and bottom layer where the the NDR peak is observed and the corresponding transmission. (d)-(e) The Dirac Cone of top and bottom layer alignment. When two dirac cones do not have momentum mismatch, the resonance peak appears |      |

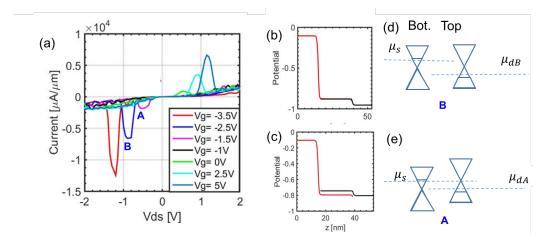

| 4.6  | (a-d) Current vs drain voltage for different barrier thickness starting from one layer hBN to four layer hBN. (e) Current vs drain voltage is compared for simulation, empirical model and experimental results. Our empirical model could accurately explain the experimental results                                                                                            |      |

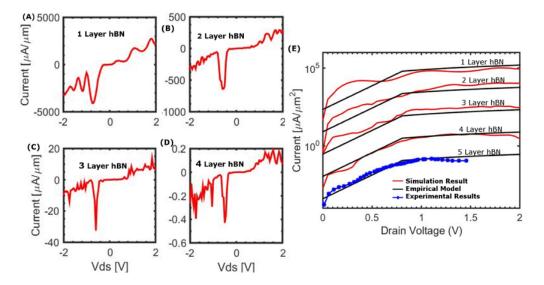

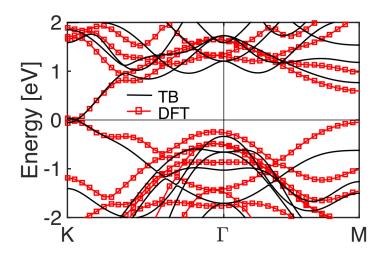

| 4.7  | A comparison of band structure plots for vertical MoS2-WTe2 hetero-<br>junction from tight binding (TB) and density function theory (DFT). They<br>match well along the band edge at K point.                                                                                                                                                                                     | 57   |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                       | Page |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

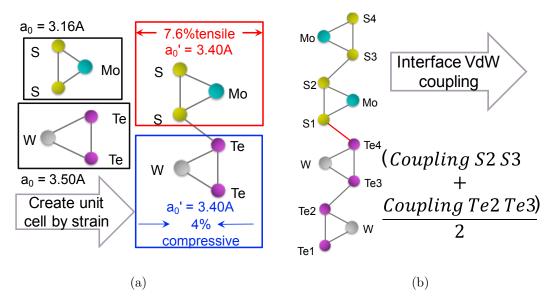

| 4.8  | (a) Assumption I : MoS2 and WTe2 layers have been strained to the same lattice constant to be registered. (b) Assumption II : Interface VdW coupling of vertical MoS2-WTe2 hetero-junction is the average of the VdW coupling of the two materials                                                                                                                       | 59   |

| 4.9  | A comparison of band structure plots for vertical MoS2-WTe2 heterojunction from tight binding (TB) and density function theory (DFT). They match well along the band edge at K point                                                                                                                                                                                     | 59   |

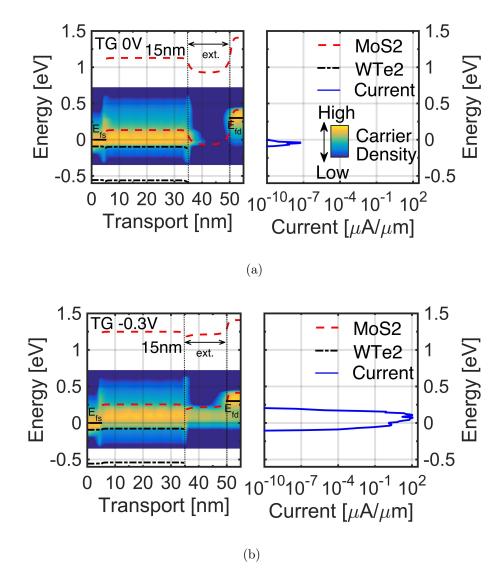

| 4.10 | The band edges of a MoS2-WTe2 interlayer TFET at OFF (a) and ON (b)state aligned with the energy resolved transmission respectively. At ON state, WTe2 Ev is higher than MoS2 Ec. This opens a window for electrons to flow and it has a non-zero transmission. At OFF state, WTe2 Ev is lower than MoS2 Ec. No electrons can go through and it has a zero transmission. | 61   |

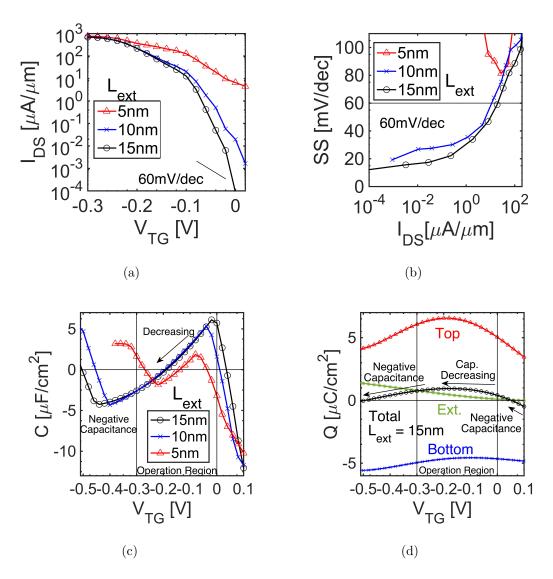

| 4.11 | (a) The transfer characteristics $(Id-Vg)$ ; (b) The SS-Id plot and (c) The capacitance-voltage plot of a MoS2-WTe2 interlayer TFET with the extension length $L_{ext}$ ranging from 5 to 15nm. (d) The Charge-voltage plot of a MoS2-WTe2 interlayer TFET with $L_{ext}=15nm.$                                                                                          | 63   |

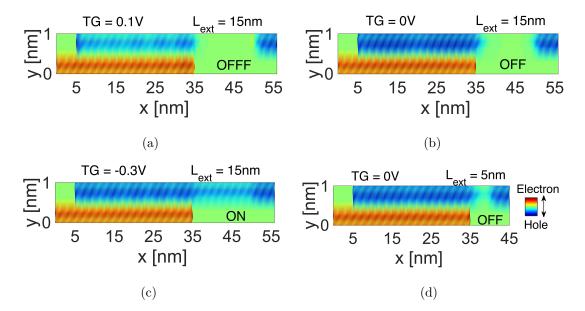

| 4.12 | Position resovled electron/hole density for MoS2-WTe2 interlayer TFETs with $L_{ext}=15nm$ at (a) OFFF state when $V_{TG}=0.1V$ (outside device operation region); (b) OFF state when $V_{TG}=0.0V$ ; and (c) ON state when $V_{TG}=-0.3V$ ; (d) with $L_{ext}=5nm$ at OFF state when $V_{TG}=0.0V$ . Red and blue represents the electron and hole density respectively | 64   |

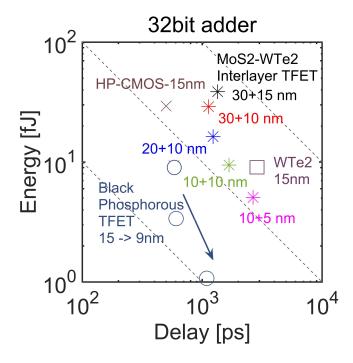

| 4.13 | Energy-Delay product of MoS2-WTe2 interlayer TFETs with device channel scaled down from 55nm to 15nm in comparison BP-TFETs [12,72] with their $L_{ch}$ scaled from 15nm to 9nm, a 15nm WTe2 TFET [56] and high performance CMOS                                                                                                                                         | 66   |

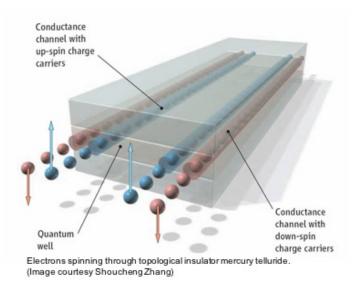

| 5.1  | The edge states of a topological insulator. The surface states usually has the spin momentum lock, in which electron transport in one direction can only have one spin direction. Figure from [103]                                                                                                                                                                      | 68   |

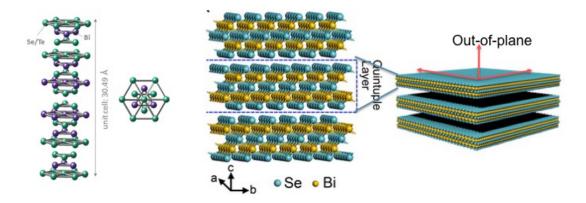

| 5.2  | Atomistic structure and the quintuple layers of Bi2Se3 (similiar to Bi2Te3). Firgure come from [117]                                                                                                                                                                                                                                                                     | 70   |

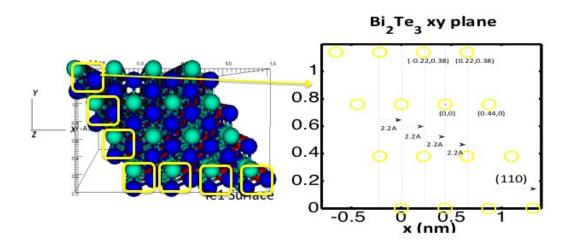

| 5.3  | The crystal direction [110] for Bi2Te3                                                                                                                                                                                                                                                                                                                                   | 70   |

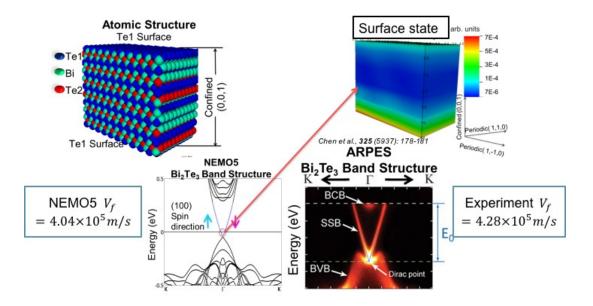

| 5.4  | The band structure and the spin momentum lock of 3D TI material Bi2Te3. The Fermi Velocity calcuated from NEMO5 is matching the result from ARPES [119]                                                                                                                                                                                                                  | 72   |

| Figu | ire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Page |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

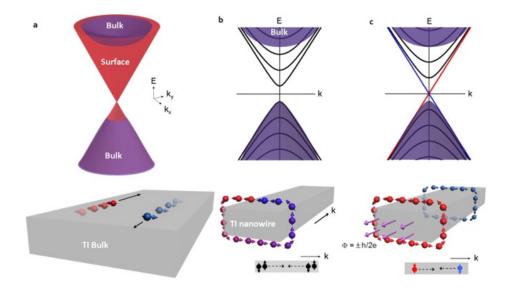

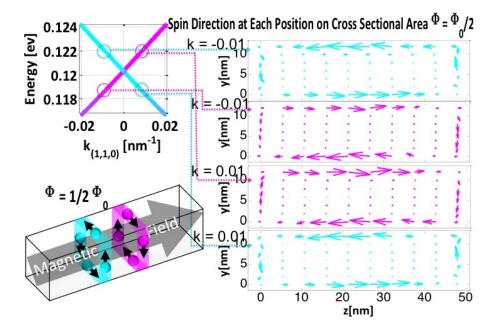

| 5.5  | Topological surface band evolution in TI nanowires. (a) Top: Schematic band structure of bulk topological insulator. Surface states (red) exist in parallel with bulk conduction/valence band (purple). Bottom: electrons in the surface band are moving in two-dimensional surface, of which spin is defined by electron momentum (no spin degeneracy). (b) Top: band structure of a topological insulator nanowire (with no magnetic field). Topological surface band transforms to discrete 1D subbands (black color bands) with spin degeneracy. Bottom: electron spin is constrained in the tangent plane picking up a $\pi$ Berry's phase by a $2\pi$ rotation of electrons along the perimeter, which opens a gap in the 1D modes. (c) Top: band structure of a topological insulator nanowire (with magnetic flux $\Phi = \pm h/2e$ ). The gapless bands (red and blue) is not spin degenerated and topologically nontrivial, referred as 1D helical mode. Bottom: electrons of opposite spin orientations propagate in an opposite manner. Figure from [121] | 74   |

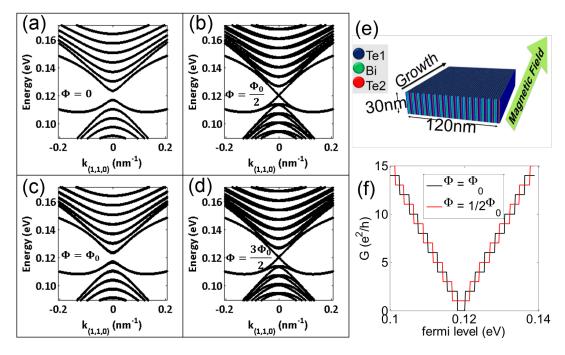

| 5.6  | Bandstructures of $12 \times 48nm^2$ Bi2Te3 nanowires (type I) with varying magnetic field along the wire axis. The wire banstructure without a magnetic field (a) or with a magnetic field corresponding to the magnetic flux quantum (c) has the largest band gap and every state is double degenerate. Bandstructures with magnetic fields corresponding to 0.5 (b) and 1.5 (d) magnetic flux quanta have disappearing band gap and are only degenerate at k=0.(e) Device structure of a Bi2Te3 with a cross sectional area of $30 \times 120nm^2$ . The direction of the magnetic field is in parallel with the growth direction [110]. (f) The conductance of (e) with different magnetic fields                                                                                                                                                                                                                                                                                                                                                                 |      |

| 5.7  | 1D helical surface states of a $48 \times 12nm^2$ Bi2Te3 nanowire with a magnetic field of 3.5949T solved with NEMO5 for the two (E,k) tuple as indicated in the bandstructure in (a). The color represents different spin orientations in (b). Electrons of the same energy and opposite spin orientation propagate into opposite direction as illustrated in (c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

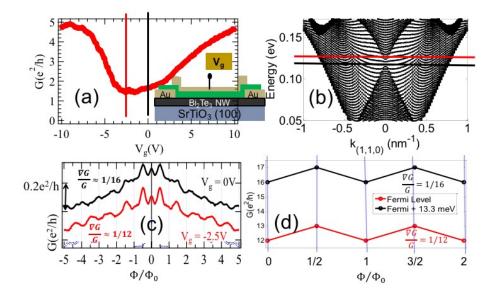

| 5.8  | (a) Experimental measurement of conductance as a function of gate voltage by shifting Fermi level. (b) The conductance minima corresponds to the gate voltage that aligns the Fermi level to the Dirac Point. (c) Experimental Magnetoconductance as function of magnetic flux $\Phi$ in units of magnetic flux quanta $\Phi_0 = h/e$ for magnetic fields applied parallel to the axis of the nanowire in Ref. [116, 122] at two different gate voltages. NEMO5 simulation results (d) agree qualitatively with (c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 77   |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                    | Page |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

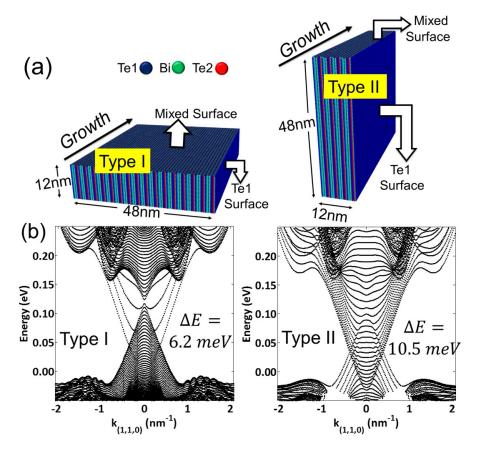

| 5.9  | (a) Atomic structures of 12x48 nm2 Bi2Te3 nanowires grown along the [110] direction in the two possible surface configurations. In the type I wire, the pure Te1 facet is much smaller than in the type II configuration. (b) Bandstructures of the nanowires of (a) show different quantization energies for the surface states at k=0                                               | 78   |

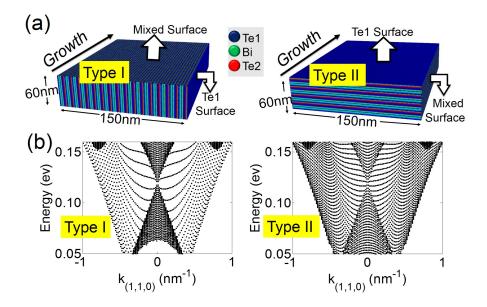

| 5.10 | (a) Atomic structures of $60 \times 150 nm^2$ Bi2Te3 nanowires grown along the 110 direction. The facets with only Te1 atoms are larger in type I than in type II wires. (b) Bandstructures of the nanowires of (a)                                                                                                                                                                   | 79   |

| 5.11 | Surface state quantization energies as a function of the inverse wire perimeter for Bi2Te3 nanowires grown in [110] direction (a) and in [001] direction (b). Different facets of [110] wires differ in their chemistry and give different quantization energies. This is in contrast to [001] wires. Surface Fermi velocities result from linear approximations to these data        | 80   |

| 5.12 | Surface state quantization energies as a function of the inverse wire perimeter for Bi2Te3 nanowires grown in [110] direction with different cross sectional areas. Different facets of [110] wires differ in their chemistry and give different quantization energies. This is in contrast to [001] wires. Surface Fermi velocities result from linear approximations to these data. | 81   |

| 5.13 | Surface state quantization energies as a function of the inverse wire perimeter for Bi2Te3 nanowires grown in [001] direction with different cross sectional areas. Surface Fermi velocities result from linear approximations to these data                                                                                                                                          | 82   |

| 5.14 | (a) Contour plot of the absolute squared wavefunctions of the 3 surface states right above the Dirac point of the type I Bi2Te3 nanowire of Fig.2(a) for the momentum $k=0.025nm^{-1}$ in corresponding to the energy points in the EK diagram                                                                                                                                        | 83   |

| 5.15 | (a) Contour plot of the absolute squared wavefunctions of the 3 surface states right above the Dirac point of the type I Bi2Te3 nanowire of Fig.2(a) for the momentum $k=0.025nm^{-1}$ . (b) Unit-cell average of the surface states in (a) along the [001] wire coordinate. "n" represents the subband index and the number of maxima of the surface states envelope                 | 84   |

| 5.16 | (a) Schematic surface state bandstructure of Bi2Te3 nanowires grown in                 |

|------|----------------------------------------------------------------------------------------|

|      | (110) direction as shown in Fig. 5.9(b) with different Fermi velocities for            |

|      | the pure Te1 and the mixed surfaces. The different Fermi velocities cause              |

|      | an effective potential offset between the two surfaces for finite momenta              |

|      | (highlighted with $V_{eff}$ ). (b) The effective potential $V_{eff}$ (red line) of (a) |

|      | along the unfolded nanowire perimeter confines the surface states predom-              |

|      | inantly on the mixed surface (illustrated with schematic wavefunctions in              |

|      | black)                                                                                 |

85

#### 1. INTRODUCTION

#### 1.1 Challenge of Device Scaling

The continuous improvement of modern electronics has been sustained by the scaling of silicon based MOSFETs over the last 4 decades. Fig. 1.1 [1] shows the CPU trends from Intel, in clock speed and number of transistors per unit until 2010. The number of the transistors continues to go up as Moore predicted. However, the clock speed, the frequency of the processors has been saturated since 2005. This prevents us from improving the performance of the processors further, the major reason being the difficulty in dissipating heat from the chips.

The power consumption has already reached the cooling capability limit (  $100W/cm^2$ ). To reduce this power consumption, the transistors need to have a smaller supply voltage  $V_{DD}$  at ON state and still maitain a small leakage current at OFF state.

#### 1.2 Challenge of Tunnel FET

MOSFETs are turned OFF by increasing the thermionic barrier. In this way, how fast they can be turned on by gate voltage (Vg) is limited by the Fermi-Dirac distribution. This limits the subthreshold swing (SS, describes how much gate voltage needs to be applied for the current to change by a decade) to be greater than 60mV/dec. Limited by the lower limit of SS, the MOSFET switches cannot have a smaller supply voltage  $V_{DD}$  without increasing the leakage current. This prevents CMOS from further reducing the power consumption.

Figure 1.1. Intel CPU Trends. (Source: [1])

Unlike MOSFETs, Tunnel Field-Effect-Transistors (TFETs) are turned on by tunneling current. This allows TFETs to have a SS smaller than 60 mV/dec. Breaking this SS limit in TFETs makes it a possible solution to power dissipation problems. Although, SS;60 has been demonstrated experimentally in conventional TFETs, they suffer from low ON current, orders of magnitude lower than MOSFETs. The ON current is usually degraded to 0.1 to 100  $\mu A/\mu m$ , compared to 1000  $\mu A/\mu m$  in MOSFETs. Hence achieving high ON-current and performance requires novel device structures.

#### 1.3 2D materials

The WKB approximation of the transmission through a triangular well tells us a larger tunnel current would result from a smaller 1. tunnel length  $\lambda$ ; 2. band gap Eg; 3. effective mass  $m^*$  of the channel material.

A smaller tunnel length  $\lambda$  can result from a smaller channel thickness  $t_{channel}$ . This brings the emerging 2D material into attention. Low dimensional materials have unique features which can be used to solve the challenges of TFETs.

Figure 1.2. Stacking 2D materials. (Source: [2])

Fig. 1.2 shows the different 2D materials stacking together and the connecting bonds are Van Der Waals. The advantages of this stacking structure are 1) Low density of interface defects due to very small amount of dangling bonds at surface; 2) Immunity to energy band gap increasing from vertical quantization due to the 2D nature; 3) Excellent electrostatic control due to the sub-nanometer thickness.

High performance TFET designs based on bilayer graphene in Chapter2, black phosphorous in Chapter 3 published in and vertically stacked 2D materials in Chapter 4 are proposed and studied in this thesis. The quantum physics involved in the transport study is discussed in detail in each chapter.

#### 1.4 Topological Insulators

Topological insulator (TI) materials such as Bi2Te3 have extraordinary surface properties [3–5]. These make them a unique class of materials for applications also as low power electronic devices [6], spintronics [5], and quantum computation [7,8]. TIs host surface states with the spin perpendicular to the surface normal, spin-locked relative to the electronic in-plane momentum. Backscattering of such surface electrons requires spin-flip processes. In TI devices that are free of magnetic impurities, surface electron backscattering is therefore unlikely.

Such unique properties of TI surfaces make this material also interesting for low power applications. The surface transport in TI nanowires, the Aharonov-Bohm effect and also some novel findings on the surface Fermi Velocites are discussed in chapter 5.

The vertical strain of bilayer graphene work in section 2.2 has been published in [9]; the electrical doping effect on bilayer graphene is published in [10]; the bilayer graphene TFET design is published in [11]. Thickness Engineered TFET based on phosphorene discussed in chapter 3 is published in [12]. The method of modeling MoS2-WTe2 interlayer TFETs in section 4.3.2 has been published in [13], this abstract has won the best student poster award when presented in 2016 ICPS. The work about topological insulator Bi2Te3 nanowire in chapter 5 is published in [14,15]. The rest results including the transport based on tunable band gap in bilayer graphene in section 2.2.2; the bilayer graphene PN junction collaboration with experimental group work in section 2.3; the NDR results from Gr/BN/Gr structure in section 4.2; the operation mechanism in section 4.3.3 and 4.3.4 of MoS2-WTe2 interlayer TFETs; the capacitance in section 4.3.5 and the device performance study of MoS2-WTe2 interlayer TFETs in section 4.3.6 are still under the process of publishing and are not available online up to date.

#### 2. BILAYER GRAPHENE

#### 2.1 Introduction

Being a two-dimensional material, graphene has attracted great interest for its extraordinary physical, chemical, and electrical properties [16–18]. Its many unique features include high mobility, excellent electrostatic control due to 2D nature, and ease of top-down fabrication. All these make it a promising candidate for many electronic and optoelectronic applications. Due to the lack of a bandgap, however, graphene transistors cannot be completely turned off. By adding one more graphene layer with specific AB stacking order and applying a vertical electric field across the two layers, a sizable bandgap in the range of 0 to 300 meV can be achieved in bilayer graphene (BLG), in agreement with previously published reports [19, 20]. It is then of our interest to investigate the transport properties of bilayer graphene FETs in the presence of the dynamically tuned bandgap.

This report first evaluates the bandgap of the BLG from tight-binding calculations. A bandgap is created by an electric field in this zero bandgap semiconductor up to 300 meV at a displacement field of 6V/nm. A saturation of the bandgap is observed at larger fields. A BLG transistor with a top and a bottom gate is then considered to exploit the tunable band gap behavior. The electric field is created through the voltage difference of these two gates. The transmission of this transistor is shown to follow the corresponding electric-field dependent band structure. This verifies that the tunable band gap behavior is captured in the transport model.

The simulation data reveal the following: 1) an on/off ratio of 100 can be achieved in the double gated BLG FET, in contrast to a ratio of 10 for a similar FET without

the tunable band gap effect; and 2) a shift of the current-voltage (I-V) characteristics as a result of the electrostatic control by the back gate. Similar work can be found in [21, 22], however our paper focuses on the performance of the tunable band gap effect in the BLG FET.

#### 2.2 Tight Binding Model

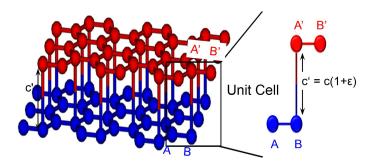

Here, the AB (Bernal) stacked BLG is shown in Fig. 2.1, with 4 atoms A, B, A' and B' in each unit cell, and the inter-plane distance c.

Figure 2.1. Atomic structure and unit cell of bilayer graphene

Hamiltonian is constructed based on the  $p_z$  orbital nearest-neighbor atomistic tight-binding model, which contains only in-plane and inter-plane hopping terms,  $\gamma_0$  and  $\gamma_1$ .

$$H = \begin{pmatrix} +V & \hbar v_f k e^{i\phi(k)} & \gamma_1 & 0\\ \hbar v_f k e^{-i\phi(k)} & +V & 0 & 0\\ \gamma_1 & 0 & -V & \hbar v_f k e^{-i\phi(k)}\\ 0 & 0 & \hbar v_f k e^{i\phi(k)} & -V \end{pmatrix}$$

$\phi(k)$  equals to  $\pi/6$  at Dirac point.  $v_f$  is the Fermi velocity of graphene,  $1 \times 10^6 m/s$ . This gives the inner-plane coupling  $\gamma_0$ .

The hopping paramters and material properties of BLG under vertical field extracted from bandstructure for the maximum band gap Eg are list in the table below.

Table 2.1.

Bilayer graphene material properties: in-plane and inter-plane hopping parameters  $\gamma_0$  and  $\gamma_1$ , maximum bandgap Eg, electron effective mass me\*, in-plane and out-plane relative dielectric constant  $\sigma_r^{in}$  and  $\sigma_r^{out}$ , inter-layer distance c.

| Parameters       | $\gamma_0 \; (\mathrm{eV})$ | $\gamma_1 \text{ (eV)}$ | Eg (meV) | $m_e (m_0)$ | $\sigma_r^{in}$ | $\sigma_r^{out}$ | c (nm) |

|------------------|-----------------------------|-------------------------|----------|-------------|-----------------|------------------|--------|

| Bilayer Graphene | 2.75                        | 0.3                     | 275      | 0.038       | 3               | 3.3              | 0.335  |

Fig. 2.2 plots out the eigenvalues in the 2D k space of bilayer graphene. We are going to focus on the Dirac cone of bilayer graphene in the text later.

Figure 2.2. Bilayer graphene band diagram in 2D k space

#### 2.2.1 Vertical Strain

Perpendicular strain  $\epsilon$ , associated with a change from the interlayer distance c to  $c' = c(1+\epsilon)$ , is applied to bilayer graphene. The atomic structure change and unit cell is shown in Fig. 2.3.

Figure 2.3. Bandgap of bilayer graphene changing with a vertical electric field. The bandgap increases with an increasing field up to a saturation point.

The associated change is in included in the Hamiltonian below:

$$H = \begin{pmatrix} +V + c\frac{\partial V}{\partial c}\epsilon & \hbar v_f k e^{i\phi(k)} & \gamma_1 + c\frac{\partial \gamma_1}{\partial c}\epsilon & 0\\ \hbar v_f k e^{-i\phi(k)} & +V & 0 & 0\\ \gamma_1 + c\frac{\partial \gamma_1}{\partial c}\epsilon & 0 & -V + c\frac{\partial V}{\partial c}\epsilon & \hbar v_f k e^{-i\phi(k)}\\ 0 & 0 & \hbar v_f k e^{i\phi(k)} & -V \end{pmatrix}$$

The variation of hopping parameter  $\gamma_1$  with interlayer distance c,  $\frac{\partial \gamma_1}{\partial c}$  is estimated using Boykin's model [23].  $\frac{\partial V}{\partial c}$  is evaluated in Ref. [24]. All the other parameters can be found in 5.1.

In the Hamiltonian presented above, the change of onsite energy of different layers due to vertical electric field is presented by the constant +V and -V. In the four

atom unit cell, vertical strain breaks the symmetry of the two atoms within a layer since only one of these two atoms is connected to the other layer. Interestingly, the Hamiltonian displays a possibility of opening a strain induced band gap. Verberck et al. examined this possibility and found out that in specific conditions strain by itself can open a band gap:  $|c\frac{\partial V}{\partial c}\epsilon| > \gamma_1 + c\frac{\partial \gamma_1}{\partial c}\epsilon$  [24].

#### 2.2.2 Tunable Band Gap

The vertical strain in this section is a direct copy of ref. [9]. The rest about tunnable band gap in bilayer graphene without strain is unpublished.

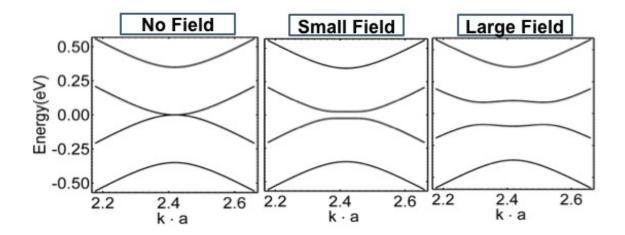

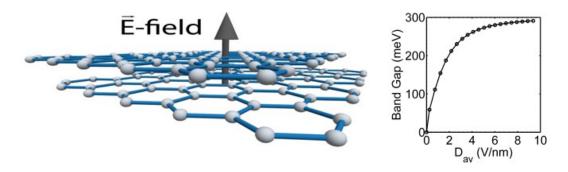

Fig. 2.4 shows how the band structure of BLG changes with a vertical electric field applied between the two graphene layers. The bandgap increases linearly with the small electric fields and saturates at 300meV for high electric fields. Notice that the band edge without electric field is at K point. However, band edges moves away from K-point by increasing the field.

Fig. 2.5 presents the bandgap as a function of the displacement field. The bandgap of BLG can be adjusted from zero up to 300meV and saturates at a displacement field of 6V/nm. The average displacement field in simulation and experiment are calculated differently. In the simulation, the effect of electric field is calculated by setting constants +V and -V as the onsite energies of the top and bottom layer atoms. Average vertical displacement field,  $D_{av}$ , then equals 2V/c. c is the interlayer distance, equals to 0.335nm here. Experimentally, the average displacement field of top and bottom gates are considered:

$$D_{av} = \frac{1}{2} \left[ \epsilon_o x \frac{\dot{V_{TG}}}{t_{topoxide}} - \epsilon_o x \frac{\dot{V_{BG}}}{t_{botoxide}} \right]$$

Figure 2.4. Bandgap of bilayer graphene changing with a vertical electric field from [25]. The bandgap increases with an increasing field up to a saturation point.

Figure 2.5. Tunable band gap in BLG as a function of the displacement field from [26].

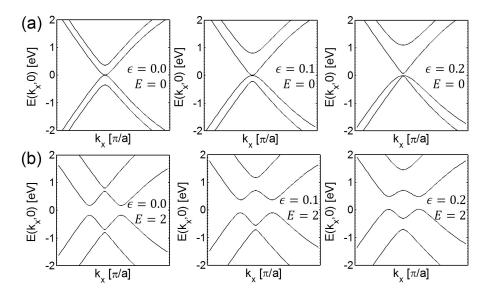

As shown in Fig. 2.6, strain has two major impacts on the band structure of BLG.

1) Producing asymmetric conduction and valence bands. This is due to the fact that in the presence of vertical strain, the onsite energies of the in-plane carbon atoms in each layer of graphene become asymmetric. 2) Creating a larger band gap in the presence of a vertical electric field. Electric field here is evaluated using the inter-

plane distance c' after straining.

Based on the band structure calculations, one can open a larger band gap by pulling apart the two layers of graphene in the existence of vertical electric field. Similar conclusion can also be found in Ref. [24].

Figure 2.6. Band structure of strained bilayer graphene without (a) and with (b) vertical field [V/nm]. Left, middle and right figures correspond to band structures of bilayer graphene with different strain values.

The effect of strain and vertical field are demonstrated in Fig. 2.7 more clearly. Fig. 2.7a shows that the application of strain can increase the band gap when the vertical field is higher than 0.4V/nm. Moreover, the impact of strain is more significant in the higher vertical field values. Fig. 2.7b shows the band gap as a function of vertical field for different strain values; higher the strain, larger the maximum value of the band gap. This effect indicates that with a vertical strain, it is possible to achieve a higher ON/OFF ratio in bilayer graphene transistors.

Figure 2.7. (a) Band gap changes with strain applied in different vertical fields E[V/nm]. (b) Band gap increases with vertical field. Saturation band gap increases with larger strain.

#### 2.2.3 Transport

Bilayer graphene FETs have been simulated using the self-consistent Poisson-Non-Equilibrium Green's Function (NEGF) method in our Nano-Electronic MOdeling (NEMO5) tool [13-15].

If not stated otherwise, all the transport results are for the double gate bilayer graphene device structure demonstrated as Fig. 2.8.

Fig. 2.9 shows the transmission results from NEGF and the corresponding band structures. Two scenarios are presented: 1) Without an electric field, the transmission through the zero bandgap BLG is finite. 2) In contrast, a bandgap opens up with an electric field of 1V/nm and results in zero transmission through the bandgap. This verifies the formation of a transport gap besides the optical gap in BLG under vertical field.

Fig. 2.10 shows the transfer characteristics of BLG FET at temperature of 300 K obtained from Poisson-NEGF method.  $V_{DS}$  is 10mV, and the Fermi level is fixed

Figure 2.8. Double layer device structure with one top gate and one bottom gate.

to 0eV. The back gate voltage  $V_{BG}$  is set to 2V. Despite the band gap increasing with the top gate voltage ( $V_{TG}$ ), the device is ON, then OFF, and ON again (marked as 1, 2 and 3 respectively) with the sweeping of top gate and generates a V shaped I-V characteristic. From the potential energy at top and bottom graphene layers, extracted from self-consistent simulations, one can calculate the conduction and valence band edges which are called "local band structure" here. "Local band structure" is plotted in Fig. 2.10 by extracting the band edges for each unit cell. Not only does an increase in the top gate bias pull down the band edges in the channel, but it also increases the bandgap. Despite this monotonic increase in the bandgap, the OFF state occurs when the middle of the bandgap aligns with the Fermi level (shown as (2) in Fig. 2.10). Further increase in  $V_{TG}$  and consequently the band gap does not decrease the current since the band gap is not blocking the thermal window (shown as (3) in Fig. 2.10).

Graphene transistor usually has an ON/OFF ratio of 10, it is clear that, having the tunable band gap effect can increase the device ON/OFF ratio from 10 to 100. The larger the effective bandgap in the OFF state, the smaller the OFF current. Since the bandgap is controlled by both the top and the bottom gates, the change of back gate voltage  $(V_{BG})$ , also affects the top gate voltage  $(V_{TG})$  needed to align with

Figure 2.9. (a): Bilayer graphene FET device and atomic structure. Bandgap and transmission for a BLG device in a small (b) and large (c) electric field.

the Fermi level. Thus,  $V_{BG}$  would cause a shift of the valley of the V shaped IV as shown in Fig. 2.11(a).

Fig. 2.11(b) shows the transfer characteristics of a double gated bilayer graphene transistor. The devices with higher applied strain can achieve a higher ON/OFF

Figure 2.10. (a): V shaped transfer characteristics of bilayer graphene double gate FET. (b): band edge plot along transport direction for the ON, OFF and ON state.

ratio. A 9 percent strain leads to ON/OFF ratio of  $10^3$ , compared to  $10^2$  without strain. Notice that the strain mainly reduces the OFF current and keeps ON current intact since the strain impacts the band gap.

# 2.3 Bilayer Graphene p-n tunneling junction

It has been experimentally challenging to realize a tunnel FET (TFET) with high on-current and a steep subthreshold slope simultaneously, especially with a low supply voltage ( $V_{DD}$  about 10mV).

Figure 2.11. (a) A shift in the valley of the V shaped transfer characteristics due to the change of bottom gate voltage  $V_{BG}$ .(b) IV curves for double gate bilayer graphene devices applied with different vertical strain.

The high current can be achieved by bringing the transmission probability through the source-channel tunneling barrier close to unity, which can be achieved by bringing the effective mass of the channel material and the screening length across the tunnel barrier [27,28]. Regarding the requirement of small effective mass, bilayer graphene (BLG) is almost an ideal candidate. However, despite its small effective mass, impressive mobility and initial promise for high performance electronic devices [29,30], a lack of intrinsic bandgap prevents graphene transistors from switching off.

Although sizeable bandgaps were demonstrated in graphene nano-ribbons (GNRs) [31–33], the edge roughness and device-to-device variations due to the lack of atomic level control in top fabrication pose a tremendous challenge for technology development [33–36].

On the other hand, BLG can have a tunable bandgap larger than 200meV created by an electric field [37,38]. BLG hetero-structures can thus be artificially created by applying different effective electric fields at different regions [21,39,40]. Avoiding edge roughness effects, BLG appears to be a better TFET channel material than GNRs.

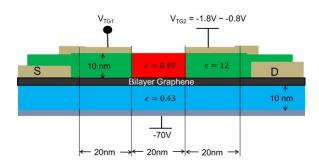

Single layer and BLG p-n junction devices with one local top gate have been demonstrated [41,42]. Without a bandgap in the single layer graphene or un-gated bilayer region, this so-called p-n junction relies on local gate control of carrier type and density. A BLG p-n junction is fabricated which has two top gates with an extremely scaled gap of 20nm in-between together with the global bottom gate. By applying different gate voltages on the two top gates ( $V_{TG1}$  and  $V_{TG2}$ ), a BLG p-n junction with electrically induced band gap is created.

Experimentally, the current of this BLG p-n junction is demonstrated to have a non-linear behavior with  $V_{TG1}$ . This non-linear behavior is shown to be consistent at various  $V_{TG2}$ . Simulation results of Id- $V_{TG1}$  at different  $V_{TG2}$  values are first demonstrated to be able to catch the experimental trend. Detailed simulation density of states (DOS) plots are then presented to show this non-linear current behavior is the result of tunnel current changing with the tunnel length. Simulation effort is also demonstrated in showing a BLG p-n junction with small SS should have separate back gates.

To conclude, an experimental observation of tunnel current in this BLG p-n junction with electrically induced band gap is reported here. In order to have a small SS device, back gates should be separated in each region of the p-n junction.

#### 2.3.1 Device Fabrication

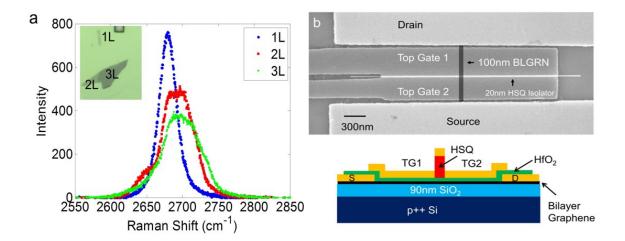

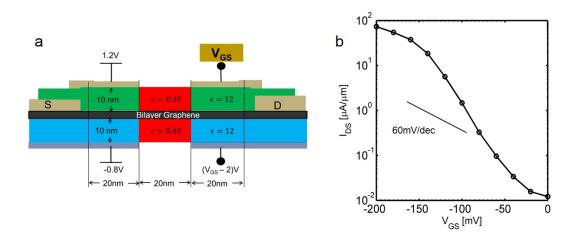

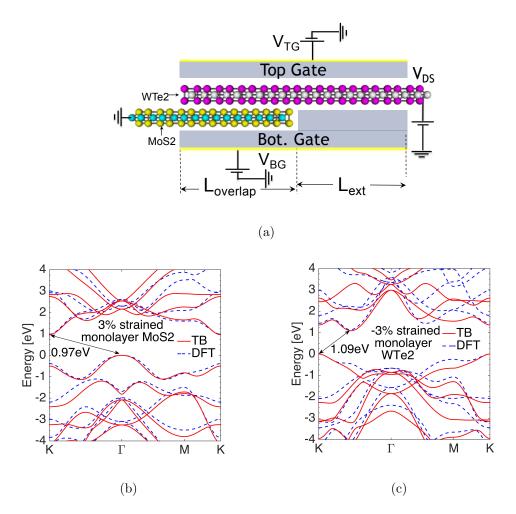

Fig. 2.12 shows the device configuration we investigate. It consisted of BLG channel sandwiched between bottom and top gates. BLG channel is defined as 100nm ribbon structure to suppress the percolation current [38]. 20nm HSQ (one type of SiO2) bar with height of 80nm electrically isolated the two top gates and can stand a voltage difference up to 5V. The fabrication process of our devices is similar to what has been described earlier [43].

The BLG is micromechanically cleaved from natural graphite on 90nm SiO2 substrate. The layer number is first identified by optical contrast and then verified by AFM and Raman [44]. Contact electrodes are made by e-beam lithography and e-beam evaporated Ti/Pd/Au metal stack (1nm/20nm/30nm). The top-gate oxide is 10nm HfO2 by ALD. Afterwards, one more e-beam lithography step is to define the 20nm HSQ bar. Then a Ti/Au metal (5nm/15nm) stack is e-beam evaporated perpendicularly onto the sample.

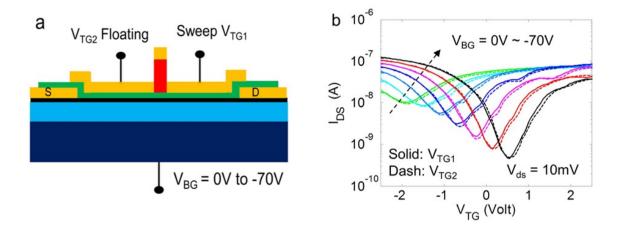

#### 2.3.2 One Gate Measurement

Conventional measurements using one single top gate, either top gate 1 or top gate 2, as shown in Fig. 2.13a. Fig. 2.13b shows the  $I_DV_{TG}$  transfer characteristics with back gate as a constant potential at 77K for conventional measurement. The on/off ratio of  $I_DV_{TG}$  at  $V_{BG}$  =-70V(Dav 3.1V/nm) is 300 at 77K and the activated gap size is 50meV smaller compared with the bandgap extracted from optical measurements

As reported previously [45], transport in band gap is dominated by hopping, and there existed numerous inter-band states induced by disorder. These inter-band states also provide a feasible path for direct tunneling of band gap. The mean free path

Figure 2.12. Bandgap of bilayer graphene changing with a vertical electric field. The bandgap increases with an increasing field up to a saturation point.

in the bulk of the channel, mean free path lm > 100nm, was extracted from the relationship between conductivity and momentum. As lm is smaller than the gap region between the two gates, we expect a significant portion of ballistic transport in the gap region. Without much scattering, the conductance is mainly determined by the tunneling transmission probability trough the energy barrier and the density of state (DOS) of the BLG p-n junction.

In absence of gating, the pristine electronic structure of BLG near the Fermi level features conduction bands above touch valence bands below. The bandgap is zero. Upon electrical gating perpendicular to the channel, a bandgap can be introduced and continuously tuned.

$I_DV_{TG}$  curve swept by top gate 1 are almost identical to that of top gate 2. This indicates the unintentional chemical doping of graphene channel regions under top gate 1 and 2 are uniform and the device hysteresis is small. With VBG changing

from 0V to -70V, the  $I_DV_{TG}$  curves shift from negative to positive top gate voltages with increasing p-type (hole) currents. In addition to this electrostatic effect, average electric field Dav becomes larger when the top and back gate voltage difference increases, resulting in a continuous decrease of the device off-currents. The slightly asymmetry in the current levels of n and p branch is likely associated with the P/N junction induced by the contact metal. In the interface between graphene and Pd metal contact, there is a p-p junction for hole branch and p-n junction for electron branch [46].

Note there are several plateau features appearing in the measured IV curves and become apparent for the large Dav. And these plateaus are observed mainly in the electron branches with nearly equal spacing. This is probably due to the formation of 1D sub-bands in graphene ribbon [47]. The bandgap significantly reduces the off-state current and makes the plateau features more pronounced. In contrast to the single layer graphene ribbon, in which the plateau features are symmetric in both electron and hole branches, they are asymmetric for BLG ribbon. This asymmetry can be understood by the distinct electronic structure of BLG, especially under a large vertical electrical field or a disorder enhanced interlayer screening [47] associated with a three dimensional structure of BLG [48].

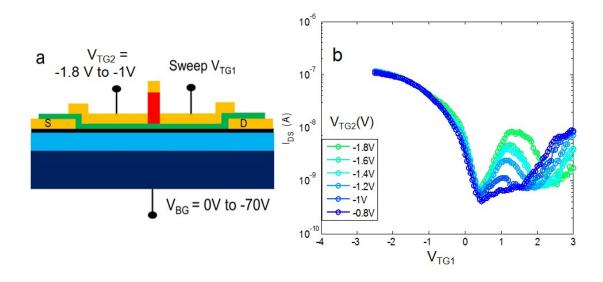

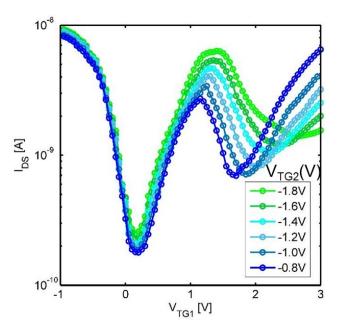

#### 2.3.3 Two gates Measurement

Transport of BLG p-n junction is studied by tuning two top gates, fixing the bottom gate. The measurement configuration is described as following: The bottom gate voltage is constantly -70V and by combining with a top gate voltage, a band gap is expected to be open in both side of p-n junction. The voltages of TG1 region near the source contact are set as a constant for every single  $I_D$ - $V_{TG2}$  curve and vary from -1.8V to 1V with a step of 0.2V.

Figure 2.13. Bilayer Graphene PN junction one gate measurement

Figure 2.14. Bilayer graphene PN junction two gate measurement

# 2.4 Simulation Work of BLG p-n junction

# 2.4.1 Simulation of p-n junction two gate measurement

Electrically doped p-i-n BLG structure used in simulation shown in Fig. 2.15. Oxide thickness are all scaled down to 10 nm. EOT are kept the same if the thickness

is changed from experimental setup. Middle region is of 20nm to be consistent with experiment. Right and left region are scaled from 1um to 20nm since 20nm is the enough to block direct tunneling.

Figure 2.15. Electrically doped BLG PN junction structure used in simulation.

Fig. 2.16 shows I - V characteristics of electrically doped BLG PN junction for different  $V_{TG2}$ . Each curve differs from previous one by 0.2V.

Figure 2.16. I-V characteristics of electrically doped BLG PN junction for different  $V_{TG2}$ . Each curve differs from previous one by 0.2V

## 2.4.2 Density of States and Explanation

Firstly, the IV results from simulation (Fig. 2.16) is shown to be in agreement with experiments (Fig. 2.14), two valleys are observed from Id-Vg when sweeping  $V_{TG1}$  and keeping  $V_{TG2}$  constant.

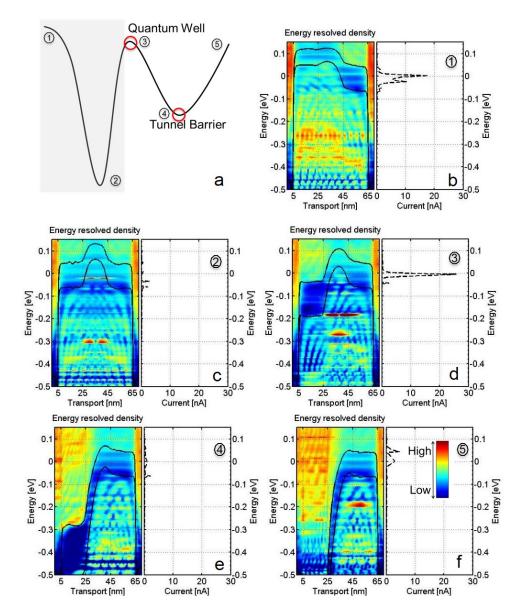

Fermi level has been kept at 0eV, Vds equals to 10 meV. Temperature is 77K. A fermi window from -0.1eV to 0.1eV is sufficient for quantum transport. Density of states (DOS) plot with energy resolved current aligned at five different  $V_{TG1}$  points are illustrated in Fig. 2.17(a). From DOS plots, inside the Fermi window, the role change of TG1 and HSQ from a quantum well to a tunnel barrier in different periods (1-5 as marked in Fig. 2.17(a) are the reason this non-linear behavior in Id-Vg. Details for 1-5 periods are in Fig. 2.17(b)-(f).

Within the Fermi window, the situations for different periods are as illustrated in Fig. 2.17(b)-(f):

- (1) (3): TG1 area is a simple double gate device with the sweep of  $V_{TG1}$ .

- (3) (4): Middle HSQ region is pulled down by  $V_{TG1}$ . It changes from a quantum well to tunnel barrier. Total current drops due to the blocking of this region.

- (4) (5): Tunnel barrier width of HSQ region decreases. This results in an increase in current.

In summary, with the sweeping of  $V_{TG1}$ , TG1 becomes a tunnel barrier and later HSQ. The two distinct valleys (2) and (4) are the results of a tunnel barrier from TG1 and middle HSQ respectively. The amplitude of each valley is determined by the length of tunnel barrier length in total. When the HSQ region became as a tunnel barrier, the barrier length is shorter than TG1 barrier. This is why the amplitude of second valley is smaller.

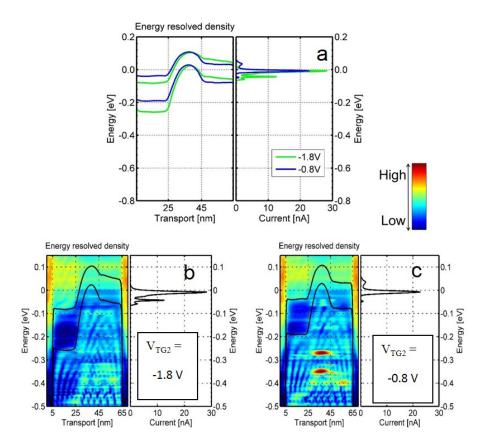

Secondly, in consistent with experimental measurements. As the  $|V_{TG2}|$  goes smaller, both local maximum (3) and second minimum (4) happen at a smaller  $V_{TG1}$

Figure 2.17. Density of states (DOS) plot with energy resolved current aligned at four different  $V_{TG1}$  for a fixed  $V_{TG2}$  value.

value with a smaller current.

Fig. 2.18 shows with a decreasing  $|V_{TG2}|$ , the electrostatic potential of region TG2 is pulled down. Thus it severs as a stronger confinement for HSQ quantum well. For the middle HSQ quantum well right region, TG2 forms a stronger confinement. In

this way, the confinement needed on the left side is comparably smaller for confining the same level state. This is why (3) and (4) happens at a smaller  $V_{TG1}$  value. With a smaller  $V_{TG1}$  value, the density of states that aligned with fermi level is smaller. This causes (3) and (4) to have a smaller current. This is shown in Fig. 2.18b-c.

Figure 2.18. (a) A comparison of potential profiles and current for two different  $V_{TG2}$  values. (b, c) Density of states (DOS) plot with energy resolved current aligned at local maximum (3) at these two different  $V_{TG2}$  values

# 2.4.3 Towards Steep Slope

We proved an observation of tunnel current in BLG PN junction device. Our goal is to achieve steep slope devices. What is the key element here that prevents us to get steep slope? In this section, we show to achieve steep slope, a single gate structure

should be avoided.

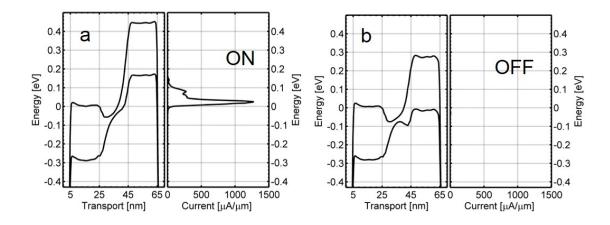

BLG PN junction structure shown in Fig. 2.19a, we separate the single back gate by putting a low EOT oxide in between the two bottom gates. By carefully adjusting the voltages applied on each gate, steep slope can be achieved as shown in Fig. 2.19b.

Figure 2.19. BLG PN junction with steep slope.

In Fig. 2.20, we show the band diagram and energy resolved current for both ON and OFF states of a carefully designed steep slope PN junction. The band of P and N regions aligned around Fermi level and formed a large effect barrier that blocks thermal current at OFF state. In the ON state, a gap opens in between the bands from P and N region, allowing a tunnel current to go through.

Figure 2.20. Energy resolved current aligned with band diagram at the ON and OFF of BLG PN junction with steep slope.

# 2.5 High Performance Bilayer Graphene Electrostatically Doped -Tunnel FET device

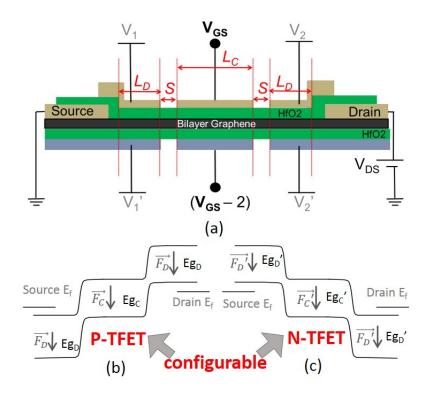

This section is a modified version of ref. [11]. In this section, a bilayer graphene based electrostatically doped tunnel field-effect transistor (BED-TFET) is proposed. Unlike graphene nanoribbon TFETs in which the edge states deteriorate the OFF-state performance, BED-TFETs operate based on bandgaps induced by vertical electric fields in the source, channel, and drain regions without any chemical doping. The performance of the transistor is evaluated by self-consistent quantum transport simulations. This device has several advantages: 1) ultra-low power  $(V_{DD}=0.1V)$ , 2) high performance  $(I_{ON}/I_{OFF}>10^4)$ , 3) steep subthreshold swing (SS<10mv/dec), and 4) electrically configurable between N-TFET and P-TFET post fabrication. The operation principle of the BED-TFET and its performance sensitivity to the device design parameters are presented.

Here, BED-TFET as a high performance steep SS device which enables  $V_{DD}$  to scale down below 0.1V is proposed. Accordingly, an excellent energy-delay product is

obtained in this device. Compared to previous bilayer graphene TFET designs [21,40], BED-TFET has the following advantages: 1) Being electrostatically configurable post fabrication between a P-TFET and a N-TFET. 2) Avoiding the experimentally challenging chemical doping in 2D materials (i.e. bilayer graphene). 3) Being immune to threshold variations due to dopant fluctuations which is critical for low threshold voltages. 4) Avoiding dopant states within the bandgap which deteriorates the OFF-state performance of the TFETs [49]. 5) Providing an artificial heterostructure without interface states.

The device structure is shown in Fig. 2.21(a). The left and right regions are con-

Figure 2.21. a) Physical structure of an electrically doped p-i-n BLG TFET. The band diagram in the OFF state of BED-TFET as a b) N-TFET, c) P-TFET.

trolled by  $V_1, V_1'$  and  $V_2, V_2'$ , respectively, and act as the electrostatically doped source and drain regions for the TFET. By adjusting  $V_1 \cdots V_2'$ , the proposed device is configurable between an N-TFET and a P-TFET as shown in Fig. 2.21(b) and Fig. 2.21(c).

The bandgap size of each region is also tunable by the voltage difference  $(\delta V)$  between the top and the bottom gates in that region. The induced band gaps are denoted by  $Eg_C$  and  $Eg_D$ . Accordingly, an artificial heterostructure can be made as long as the electric fields of different regions are different,  $(F_D \neq F_C)$ . Advanced workfunction engineering techniques [50] may be used to reduce the number of gates, however, a detailed investigation of such technique are beyond the scope of this thesis.

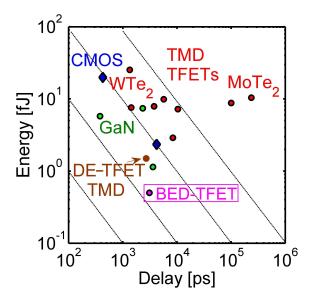

## 2.5.1 Energy Delay comparison

One of the main advantages of the BED-TFET is its very low energy-delay product. Fig. 2.22 benchmarks the energy-delay of a 32 bit adder [51] based on different steep devices. The benchmarking methodology is described in [51] for beyond-CMOS devices. The BED-TFET has the least energy-delay product among the studied devices. This is due to the steep IV and high ION obtained in the BED-TFET even with a low  $V_{DD}$  of 0.1V. This shows the importance of low band gap materials for low  $V_{DD}$  steep devices. Notice that the parasitic capacitances between the gates can be significantly reduced by using a low-k dielectric  $\epsilon_s$  between the gates [52] and increasing the spacing (S); e.g. a 10nm air gap spacer can reduce parasitic capacitances about 2 orders of magnitude smaller than gate capacitance ( $\epsilon_s/S \ll \epsilon_{ox}/t_{ox}$ ).

#### 2.5.2 Device Operation

The BED-TFET shown in Fig. 2.21(a) is composed of a bilayer graphene layer sandwiched between two layers of 3nm thick HfO2 with a relative dielectric constant of  $\epsilon_r = 20$ . The maximum field within HfO2 in current BED-TFET design is about 3MV/cm which is less than the breakdown field of HfO2 (8.5MV/cm) [58]. The three gated regions from left to right have lengths of 25, 40 and 25 nm.  $\delta V$  in the middle region is fixed to 2V to reach the maximum bandgap (i.e. 275meV in BLG).

Figure 2.22. Energy-Delay comparison of BED-TFET (pink dot) with Dielectric Engineered (DE) WTe2 TFET (brown dot) [52], Nitride TFET (green dots) [53], TMD TFETs (red dots) [54–56] and Si MOS-FET (blue dots) [51,57]

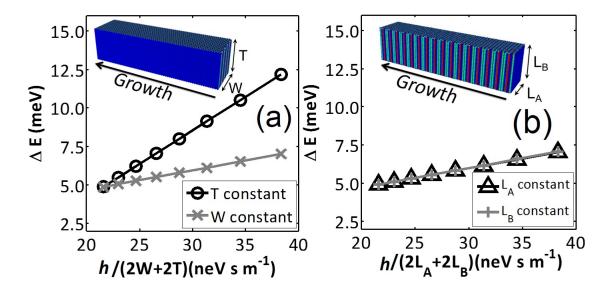

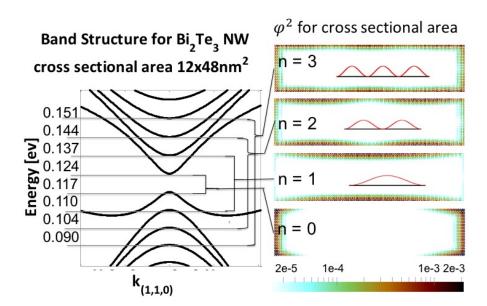

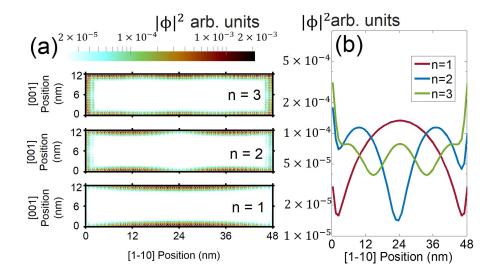

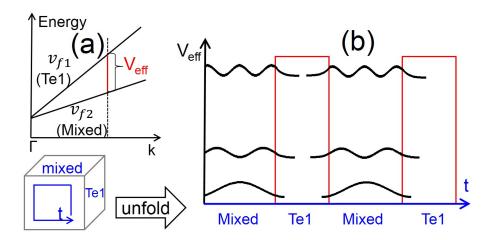

Notice that,  $V_1 \dots V_2'$  are fixed throughout the device operation to achieve the desired electrostatically doping. Only the gate voltages in the middle region are swept to switch the device between ON and OFF.