# MULTI-SCALE SIMULATIONS FOR HIGH EFFICIENCY LOW POWER NANOELECTRONIC DEVICES

A Dissertation

Submitted to the Faculty

of

Purdue University

by

**Zhengping Jiang**

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

December 2015

Purdue University

West Lafayette, Indiana

This thesis is dedicated to my parents and my wife for their love, endless support and encouragement.

#### **ACKNOWLEDGEMENTS**

As I am approaching the end of the long journey to pursue the Ph.D. degree, I would like to express my sincere gratitude to my adviser, Prof. Gerhard Klimeck. Even after so many years, I still remember the first interview with him in the Electrical Engineering building in 2008. Although at that time I was not experienced in this field and, from my point of view, not well qualified, Prof. Klimeck generously provided me the financial support and more importantly the opportunity to study in the group. I appreciate his patience for me to develop myself over these years and his guidance on my career development. I admire his passion and dedication to work and life. I am thankful for all the "hard times" and critical ideas he gave during my research which eventually makes my profile stronger. The experience at Purdue has made me a real professional and I will bear his guidance for my future career pursuits.

I would like to thank Prof. Timothy Boykin for serving on my advisory committee. I consider it great fortune to work with him from the very early stage of my career. His knowledge and rigorousness have inspired me since the first year of my Ph.D.

I would like to thank Prof. Michael Povolotskyi for serving on my advisory committee. He provided invaluable suggestions to ensure the success of my research. I am deeply impressed by his passion to science and innovation. I always learn new knowledge from the technical discussions with him. I consider him a great mentor and friend.

I would like to thank Prof. Alejandro Strachan for serving on my advisory committee. He introduced me to the area of molecular dynamics. I am thankful for his supports and advices during the CBRAM project.

I would like to thank Prof. Zhihong Chen for serving on my advisory committee. I am very grateful for her trust and patience. I consider it a great honor to have the opportunity to defend my work in front of her.

I would like to pay my respect to Prof. Mark Lundstrom and Prof. Supriyo Datta for offering great courses. Their insightful lectures have endowed me with the knowledge on quantum transport and modern device physics.

I am grateful to Dr. Hong Hyun Park, Prof. Tillmann Kubis, Dr. Dmitri Nikonov and Dr. Sebastian Steiger for various discussions and instructions on my research projects. I would like to thank Dr. Jim Fonseca, Dr. Bozidar Novakovic, Dr. Rajib Rahman and Dr. Jun Huang for their supports on NEMO5 development.

I would like to thank Dr. Glenn Martyna, Dr. Dennis Newns and Dr. Marcelo Kuroda for providing me the opportunity to work in IBM. I am grateful for their support during my stay in IBM and the continuous support after my return to Purdue.

I would like to thank Dr. Behtash Behin-Aein and Dr. Zoran Krivokapic for providing me the opportunity to work in GLOBALFOUNDARIES and their instructions.

I would like to thank Dr. Woosung Choi and Dr. Jing Wang for providing me the opportunity to work in Samsung Semiconductor and their instructions. I would like to thank my colleagues Dr. Nuo Xu, Dr. Yang Lu, Dr. Seonghoon Jin and Dr. Anh-Tuan Pham in Samsung Semiconductor Inc. for valuable discussions.

I would like to thank Dr. Nicolas Onofrio and David Guzman for their help on molecular dynamics. I would like to thank Daniel Mejia, Santiago Perez and Daniel Valencia on their support on NEMO5 development. I would like to thank Yaohua Tan, Dr. Yu He for their valuable discussions; Dr. Saumitra Mehrotra, Dr. Mehdi Salmani, Dr. Matthias Tan, Dr. Seung Hyun Park, Dr. Ganesh Hegde, Dr. Parijat Sengupta, Hesameddin Ilatikhameneh, Junzhe Geng, Kai Miao, Dr. Sung Geun Kim for their help when working on different projects; all the other group members for their support. I would like to thank Dr. Sunhee Lee and Dr. Hoon Ryu for their help on quantum computing and for sharing their experiences on career development, Dr. Neerav Kharche, Dr. Samarth Agarwal for their help and guidance during my earlier stay in the group.

I would like to thank Dr. Xufeng Wang, Dr. Yunfei Gao, Dr. Libo Wang, Dr. Xing Su, Dr. Jing Pan, Dr. Chao Lv and Dr. Qian Huang for their help during my stay at Purdue.

I would like to thank all my colleagues and staffs from the NCN and the Klimeck group for providing a stimulating and fun environment in which to learn and grow.

Finally, I would like to thank my parents and my wife Xiaosi Yang for their love and support. I would like to express my apology to my parents for not being able to stay with them for so many years. Without the understanding and encouragement from family I am not able to finish all the works.

# TABLE OF CONTENTS

|        |          |                                                      | Page  |

|--------|----------|------------------------------------------------------|-------|

| LIST C | F TABI   | LES                                                  | ix    |

| LIST C | F FIGU   | RES                                                  | X     |

| ABSTE  | RACT     |                                                      | xviii |

| 1. INT | TRODU    | CTION                                                | 1     |

| 1.1    | Scalin   | ng of MOSFET and requirements for low power devices  | 1     |

|        | 1.1.1    | Short channel effects                                | 2     |

|        | 1.1.2    | Complex bandstructure and tunneling current          | 3     |

| 1.2    | 2 Emerg  | ging logic devices                                   | 4     |

|        | 1.2.1    | Tunneling FET                                        |       |

|        | 1.2.2    | Piezoelectronic transistor                           | 5     |

| 1.3    | B Emer   | ging memory devices                                  | 6     |

|        |          | onic Bandstructures                                  |       |

|        | 1.4.1    | Density Functional Theory                            | 7     |

|        |          | Empirical Pseudo-potential Method                    |       |

|        |          | Extended Hückel Theory                               |       |

|        |          | Empirical tight binding                              |       |

| 1.5    |          | performance computation                              |       |

|        | •        | NEMO5 and nanoHUB.org                                |       |

|        |          | Parallel computing                                   |       |

| 1.6    |          | ibutions of the present work and thesis organization |       |

|        |          | e of published work                                  |       |

| 2. SC  | ALING    | OF INGAAS FINFET                                     | 14    |

| 2.1    | Metho    | ods for alloy simulation                             | 14    |

| 2.2    | 2 Scalin | ng of InGaAs DG MOSFET                               | 17    |

|        |          | Scaling of gate length                               |       |

|        |          | Comparison with Si DGUTB                             |       |

|        |          | Source Starvation                                    |       |

|    |      |                                                                | Page |

|----|------|----------------------------------------------------------------|------|

|    |      | 2.2.4 Comparison of 3D and 2D geometries                       | 26   |

|    | 2.3  | Atomic simulations of alloy scattering                         |      |

|    |      | 2.3.1 Effects of alloy scattering to transport                 | 26   |

|    |      | 2.3.2 Random alloy in InGaAs nanowire                          |      |

|    |      | 2.3.2.1 VFF Relaxation                                         | 31   |

|    |      | 2.3.2.2 Local bandstructure                                    | 32   |

|    | 2.4  | Summary and outlook                                            | 35   |

| 3. | OPT  | IMIZATION OF LSHAPED TFET                                      | 36   |

|    | 3.1  | Overview                                                       | 36   |

|    |      | 3.1.1 Electron-hole duality                                    | 38   |

|    | 3.2  | Simulation methods                                             | 39   |

|    |      | Simulation of L-shaped TFETs                                   |      |

|    |      | 3.3.1 Band offset                                              |      |

|    |      | 3.3.2 Comparison with dynamic nonlocal path band-to-band model | 42   |

|    |      | 3.3.3 Effects of drain contact doping and geometry             |      |

|    |      | 3.3.4 Summary and Outlook                                      |      |

|    | 3.4  | Comparison to other types of geometries                        |      |

|    |      | 3.4.1 Simulations of gate-recessed vertical nTFETs             |      |

|    |      | 3.4.2 Performance benchmarking with UTB and NW TFETs:          |      |

|    |      | 3.4.3 Conclusions:                                             |      |

| 4. | PIEZ | ZOELECTRONIC DEVICES                                           | 53   |

|    | 4.1  | Introduction                                                   | 53   |

|    | 4.2  | Methods                                                        | 54   |

|    |      | Results                                                        |      |

|    |      | 4.3.1 Parameterization                                         |      |

|    |      | 4.3.2 Quantum transport                                        |      |

|    | 4.4  | Summary and outlook                                            |      |

| 5. | MUI  | LTIDIMENSIONAL SIMULATION ON CBRAM                             | 61   |

|    | 5.1  | Working principles of CBRAM                                    | 61   |

|    | 5.2  | Multi-scale, multi-physics simulation                          |      |

|    | 5.3  | Methods                                                        |      |

|    |      | 5.3.1 Molecular dynamics                                       |      |

|    | 5.4  | Material Parameterization and properties                       |      |

|    |      | 5.4.1 Amorphous SiO <sub>2</sub>                               |      |

|    |      | 5.4.2 Cu                                                       |      |

|    |      | 5.4.2.1 Confinement effects on Cu filaments                    |      |

|    |      | 5.4.3 Validation of Cu parameters in Grain boundary study      |      |

|    |      | 5.4.4. Cu oxides                                               | 80   |

|                                                   | Page |

|---------------------------------------------------|------|

| 5.5 Quantum transport                             | 85   |

| 6. FUTURE WORK                                    | 87   |

| 6.1 Relaxation and transport in disordered system | 87   |

| 6.1.1 Ordering structure in SiGe and InGaAs       | 87   |

| 6.2 Validation of the Modeling Approach for CBRAM | 89   |

| LIST OF REFERENCES                                | 90   |

| A. CU PARAMETERS                                  | 99   |

| B. COPYRIGHT                                      | 100  |

| VITA                                              | 109  |

# LIST OF TABLES

| Table Page                                                                                                                                                                                                                        | e |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 1.1 Mobility of different materials[3, 4]                                                                                                                                                                                         | 1 |

| 1.2 ITRS 2013 emerging memory technologies. Green color shows the advantages and red color shows major drawbacks                                                                                                                  | 6 |

| 1.3 Quantum chemistry softwares used in this work with major features (Hartree-Fock (HF); molecular mechanics (Mol. mech.))                                                                                                       | 8 |

| 3.1 Summary TFETs doping and performance ( ${}^*I_{nw}$ ( $\mu A/\mu m$ ) normalized by diameter)5                                                                                                                                | 2 |

| 5.1 Short-range structural characteristics of glass samples. The average pair distances are reported with standard deviation for the simulated values. [95]6                                                                      | 7 |

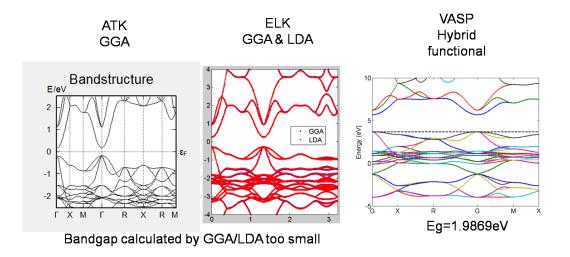

| 5.2 Bandgap for SiO <sub>2</sub> obtained from ref. [98]. Most results based on LDA/GGA will underestimate experimental bandgap (8.9eV for α-quartz)[100]. A study based on Hatree-Fock over estimate bandgap significantly [101] | 8 |

| 5.3 Resistivity calculated by DFT from Ref. [120] and by 2 <sup>nd</sup> nearest neighbor TB and 3 <sup>rd</sup> nearest neighbor EHT models in this work                                                                         | 6 |

# LIST OF FIGURES

| Fig | ure Page                                                                                                                                                                                                                                                                                                                                                  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1 | Power consumption of top 10 supercomputer (Nov. 2013). Source: http://www.top500.org/                                                                                                                                                                                                                                                                     |

| 1.2 | Electron and hole mobility versus lattice constant. The impact of biaxial strain is indicated by an arrow representing increasing compressive biaxial strain.[1] Reprinted by permission from Macmillan Publishers Ltd: Nature (479, 317–323 doi:10.1038/nature10677), copyright (17 November 2011)                                                       |

| 1.3 | Effects of DIBL. (a) IV for InGaAs and Si UTB MOSFET with different Vd. Shift of threshold voltage shows effects of DIBL. (b) Lowering of barrier due to Vd                                                                                                                                                                                               |

| 1.4 | Complex bandstructure of In <sub>0.53</sub> GaAs and Si in 5nm UTB. (a) A single imaginary band will connect conduction and valence band. (b) Imaginary bands cross over each other. A single band could not be separated from other bands                                                                                                                |

| 1.5 | Comparison of MOSFET and TFET density of states (logarithm scale) and current spectrum (logarithm scale) at $V_d$ =0.2V.                                                                                                                                                                                                                                  |

| 1.6 | Nearly 250,000 users participate in nanoHUB, an online meeting place for simulation, research, collaboration, teaching, learning and publishing. The red dots indicate users of online lectures, seminars, courses and teaching materials, while yellow dots indicate simulation users. (Photo illustration by Office of the Vice President for Research) |

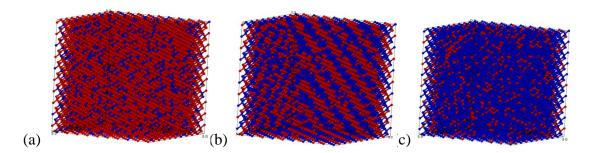

| 2.1 | Illustration of InGaAs in random alloy and VCA. (a) Random alloy crystal with In atoms replaced by Ga. (b) VCA crystal with two types of atom: As and virtual atom InGa                                                                                                                                                                                   |

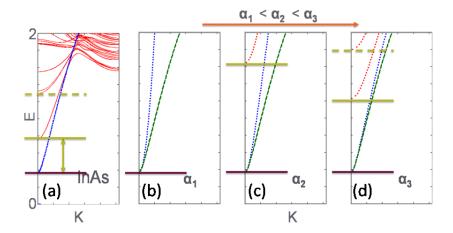

| 2.2 | Effects of non-parabolic parameters for InAs under confinement. (a) Bulk band structure (blue) and 3×3nm NW band structure (red) simulated by VCA. (b-d) Bulk band structure simulated with VCA (green) compared with bulk (blue) and NW (red) band structure simulated by EM with different non-parabolic parameters.                                    |

| Fig | ure Pa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ıge |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

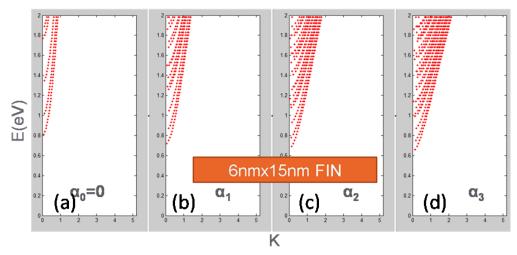

| 2.3 | Effects of non-parabolic in FinFET. Number of subband is affected by non-parabolicity of InAs in FinFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .16 |

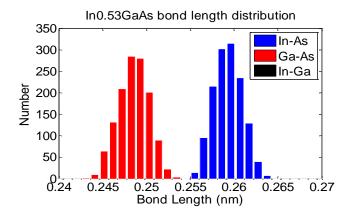

| 2.4 | Bond length distribution for InGaAs after relaxation by VFF. The lengths of the In-As and Ga-As bonds are close to the values in binary materials InAs and GaAs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .17 |

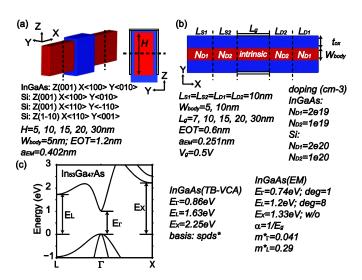

| 2.5 | Simulated device geometries and In <sub>53</sub> Ga <sub>47</sub> As parameters. (a) Left: 3D FinFET dimensions with simulated crystal directions for InGaAs and Si. Right: Cross section of FinFET showing gate position. (b) DGUTB dimensions and doping densities for InGaAs and Si. (c) In <sub>53</sub> Ga <sub>47</sub> As bulk bandstructure calculated by VCA with $sp^3d^5s^*$ basis and extracted band parameters defined in the figure. Also parameters used for different valleys in effective mass approximation for InGaAs. Difference in bandgap between two models is due to ignoring spin orbit coupling in TB-VCA.                                                                                 | .18 |

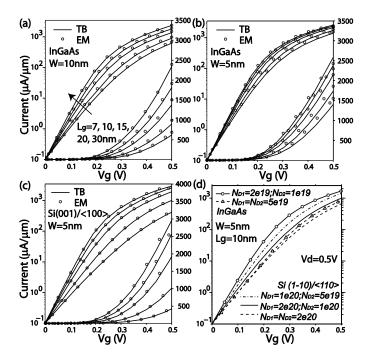

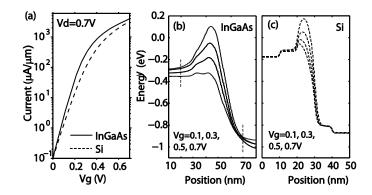

| 2.6 | Effects of gate length scaling from $L_g$ =30nm to $L_g$ =7nm for different body widths, directions and materials. Calculations are done with TB and compared with MVEM in (a-c). (a) InGaAs UTB with $W_{body}$ =10nm. (b) InGaAs UTB with $W_{body}$ =5nm. (c) Si (001)/<100> UTB with $W_{body}$ =5nm. (100) (d) Comparison between InGaAs (line with markers) and Si(1-10)/<110> (solid and dashed lines) DGUTBs at different doping conditions. $W_{body}$ =5nm, $L_g$ =10nm calculated with TB for all devices.                                                                                                                                                                                                |     |

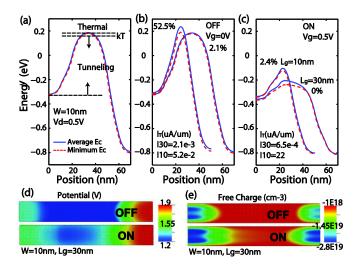

| 2.7 | Performance degradation for InGaAs UTB with $W_{body}$ =10nm. Analysis on potential profile and tunneling leakage. (a) Bandedge profile calculated with average potential ( $V_{ave}$ ) and maximum potential ( $V_{max}$ ) at each slab. Tunneling current is defined as current flowing kT below top of barrier calculated with $V_{max}$ . (b) Bandedge profiles for $L_g$ =10nm and $L_g$ =30nm at $V_g$ =0 $V$ with magnitude and proportion of tunneling current. (c) Bandedge profiles for $L_g$ =10nm and $L_g$ =30nm at $V_g$ =0.5 $V$ with magnitude and proportion of tunneling current. (d) 2D potential at ON ( $V_g$ =0.5 $V$ ) and OFF ( $V_g$ =0 $V$ ). (e) Charge density2D profile for ON and OFF. | .22 |

| 2.8 | Performance improvement due to scaling of $W_{body}$ in InGaAs UTB. Bandedge profile comparison between $W_{body}$ =5nm and $W_{body}$ =10nm and respective tunneling current information. (a) Bandedge profile with $L_g$ =30nm at $V_g$ =0V (OFF). (b) Bandedge profile with $L_g$ =10nm at $V_g$ =0V (OFF). (c) Bandedge profile with $L_g$ =10nm at $V_g$ =0.5V (ON)                                                                                                                                                                                                                                                                                                                                             | .23 |

| Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

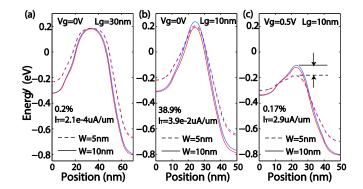

| 2.9 Comparison of Si and InGaAs UTB gate length scaling at $W_{body}$ =5nm. (a-d) Band edge profiles for (001)/<100> Si UTB with $L_g$ =10nm and 30nm at $V_g$ =0V and 0.5V, compared with InGaAs at the same $L_g$ and $V_g$ . Deviation for two potential profiles is bigger for Si due to higher channel charge density (Blue: Ec- $V_{ave}$ , red: Ec- $V_{max}$ ). (e) Effects of DIBL for Si (dashed line) and InGaAs (solid line) UTBs. (f) Si and InGaAs UTBs I-V at different $V_d$ . Shifting of $V_{th}$ indicates stronger DIBL for Si. |

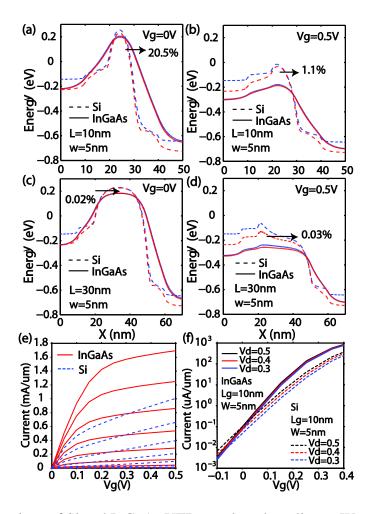

| 2.10 Source starvation in InGaAs DGUTB. (a) Comparison of IV characteristics at $V_d$ =0.7V. (b-c) Band profiles for InGaAs and Si DGUTB at $V_g$ =0.1, 0.3, 0.5, 0.7V. Because of higher drain bias, high doping regions of InGaAs with $N_{D1}$ are increased to 30nm. Device length for InGaAs DGUTB is 90nm                                                                                                                                                                                                                                     |

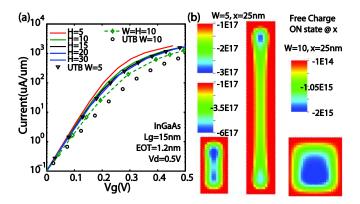

| 2.11 Comparison of InGaAs 2D UTB and 3D FinFET with different heights at Lg=15nm. (a) InGaAs FinFET with W=5nm and W=10nm at different heights. Current of FinFET normalized by height to compare with UTB at the same width. (b) Charge profiles for FinFET with different height and width at TOB at Vg=0.5V.                                                                                                                                                                                                                                     |

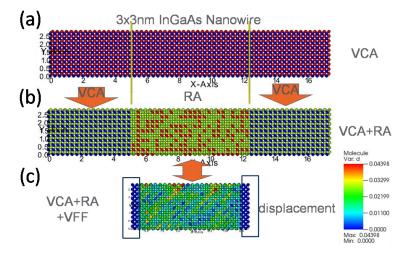

| 2.12 Geometries of InGaAs nanowire for VCA and random alloy. (a) Cross section of 3×3 InGaAs nanowire for VCA. (b) VCA for contacts and random alloy for channel. (c) Displacement of atoms in channel which is relaxed by VFF27                                                                                                                                                                                                                                                                                                                    |

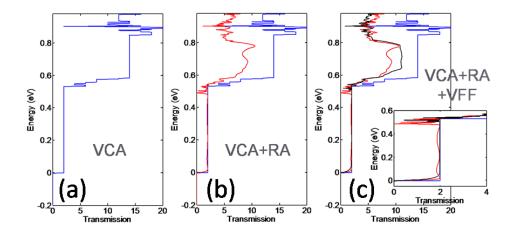

| 2.13 Transmission of InGaAs nanowires shown in Figure 2.12. (a) Transmission of pure VCA. Transmission is integer number which corresponds to the number of modes at the energy. (b) With random alloy, the transmission is reduced due to alloy scattering and reflection at the VCA-RA boundaries. (c) Transmission after relaxation in the RA region.                                                                                                                                                                                            |

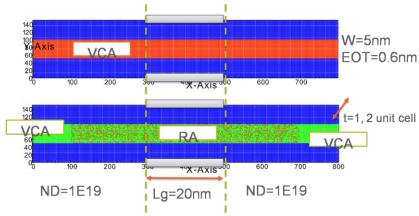

| 2.14 Geometry of InGaAs MOSFET simulated with VCA and with RA at channel. When RA is included in device, the thickness in periodic direction is defined with 1 and 2 unit cells                                                                                                                                                                                                                                                                                                                                                                     |

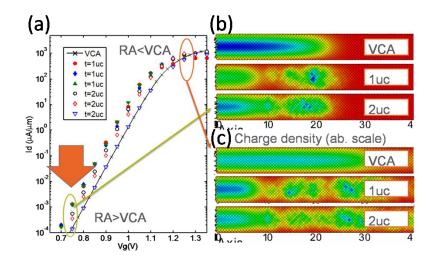

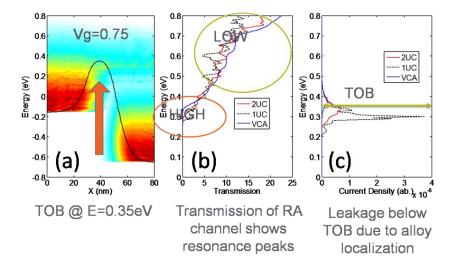

| 2.15 Results calculated with semiclassical potential. (a) IV characteristics for InGaAs MOSFET with VCA and RA of different seeds. (b) Charge density for OFF state. Only half of the device is shown. (c) Charge density for ON state. Only half of the device is shown.                                                                                                                                                                                                                                                                           |

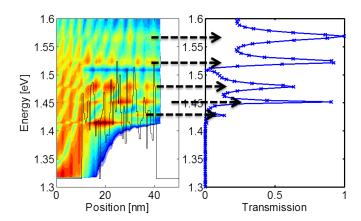

| 2.16 Transmission and current spectrum at OFF state. (a) Electron density for one of the 1uc device. Band profile is calculated with VCA band edges. (b) Transmission is reduced at higher energies due to alloy scattering. Transmission is increased at lower energies due to tunneling. (c) Current spectrum shows tunneling peaks due to random alloy                                                                                                                                                                                           |

| Figu  | re Page                                                                                                                                                                                                                                                                                                                                                                              |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

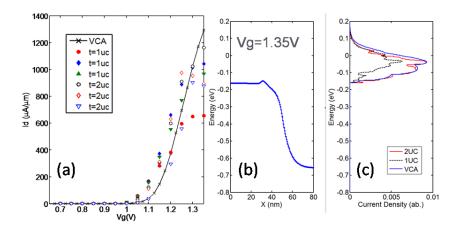

| 2.17  | (a) IV characteristics in linear scale. (b) The semiclassical band profile at ON state. (c) Current spectrum from the VCA and two examples for the 1UC and 2UC cases which show lower current than the VCA                                                                                                                                                                           |

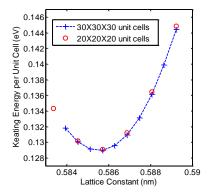

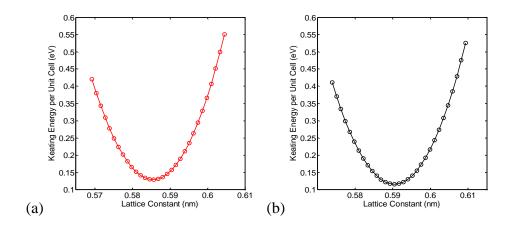

| 2.18  | Calculate equilibrium lattice constant for InGaAs. Results are converged with respect to supercell sizes                                                                                                                                                                                                                                                                             |

| 2.19  | Equilibrium lattice constant calculated for (a) In <sub>53</sub> Ga <sub>47</sub> As and (b) In <sub>65</sub> Ga <sub>35</sub> As. The values predicted by VFF match well with experimental values32                                                                                                                                                                                 |

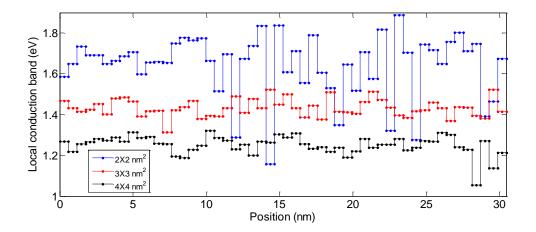

| 2.20  | Local conduction band minimum for InGaAs nanowire of different diameters33                                                                                                                                                                                                                                                                                                           |

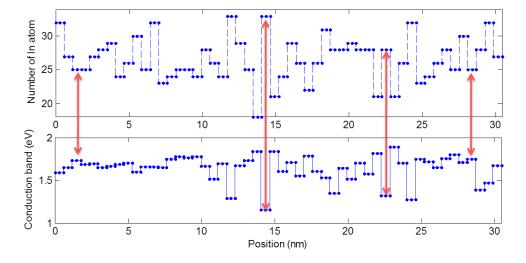

| 2.21  | Local band minimum and number of In atoms in each slab                                                                                                                                                                                                                                                                                                                               |

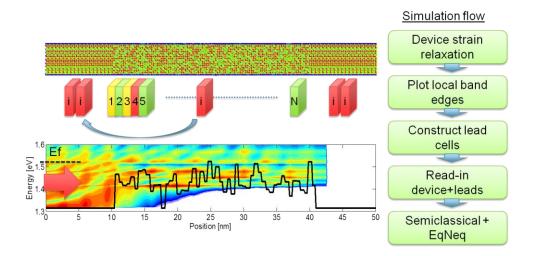

| 2.22  | Simulation flow and the local electron density for 3nm ×3nm nanowire34                                                                                                                                                                                                                                                                                                               |

| 2.23  | Transmission function for structure in Figure 2.22. The transmission through random alloy nanowire shows resonance tunneling features                                                                                                                                                                                                                                                |

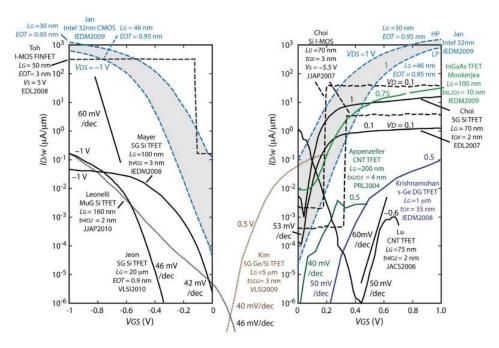

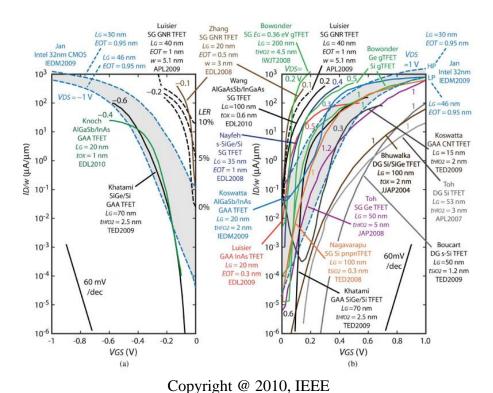

| 3.1 . | Comparison of published TFET channel current per unit width versus gate-to-source voltage for (a) p-channel [40, 41] and (b) n-channel [39, 42-46] transistors. Dashed lines bordering the shaded area indicate measured high-performance (HP) and low-power (LP) 32-nm node MOSFET technology[47]. The black dashed lines are measured characteristics for I-MOS transistors. [7]37 |

| 3.2   | Comparison of simulated TFET channel current per unit width versus gate-to-source voltage for (a)p-channel and (b)n-channel transistors. [7]                                                                                                                                                                                                                                         |

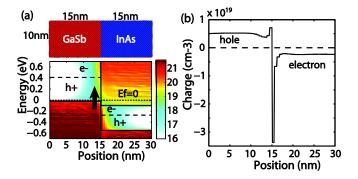

| 3.3 I | llustration of electron-hole duality and convergence issure for full quantum self-consistent simulation.(a) Geometry of 10nm width UTB and local density of states under homogeneous potential. (b) Charge density normalized for each slab showing inhomogeneous charge distribution near the interface due to density penetration into bandgap.                                    |

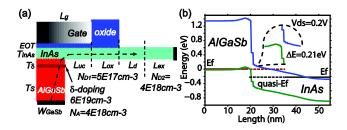

| 3.4 ( | (a) Device geometry of L shaped TFET. (b) Band profile plotted along dashed line in (a). 4nm InAs and 10nm AlGaSb keeps staggered band alignment at interface                                                                                                                                                                                                                        |

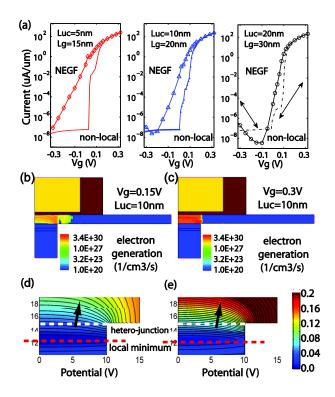

| 3.5 ( | Comparison of quantum transport between DNL model and NEGF shows effects of tunneling model. (a) IV characteristic for different undercut lengths. (b) Band to band electron generation rate for $L_{uc}$ =10nm at $V_g$ =0.15V and $V_g$ =3V. (c) Potential for tunneling junction at $V_g$ =0.15V and $V_g$ =3V. Contour lines are spaced at equal spacing.                        |

| Figure Page                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

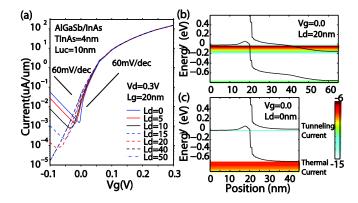

| 3.6 Effects of underlap (Ld) length. (a) IV characteristics with different drain length. (b) Current spectrum for $L_d$ =20nm at $V_g$ =0. (c) Current spectrum for $L_d$ =0 at $V_g$ =0                                                                                                                                                                                                                                  |

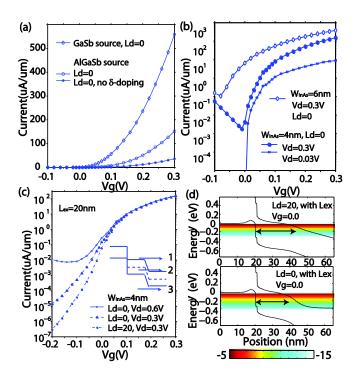

| 3.7 Ambipolar current mechanisms and optimizations on doping, material, geometry. (a) Effects of source materials and source doping profile. (b) Effects of drain width and drain voltage. (c) Effects of supply voltage and high doping extension. Current is higher at $L_d$ =0 than $L_d$ =20nm at OFF state after including $L_{ex}$ . (d) Current spectrum after including high doping extension at drain contacts47 |

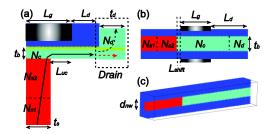

| 3.8 (a) Structure for gate-recessed vTFETs. Arrows show current flow with (dash black) and without (dash red) vertical drain contact. (b-c) UTB and NW TFETs.                                                                                                                                                                                                                                                             |

| 3.9 Simulated gate-recessed vTFETs compared with experimental measurements and effects of serial resistance                                                                                                                                                                                                                                                                                                               |

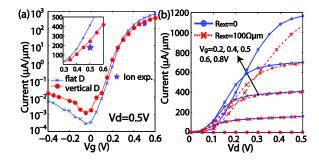

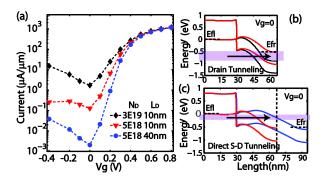

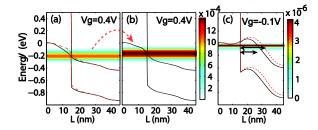

| 3.10 (a) Effects of drain doping and drain extension length at V <sub>d</sub> =0.5V. Leakage currents result from parasitic (b) ambipolar tunneling and (c) direct source-drain tunneling                                                                                                                                                                                                                                 |

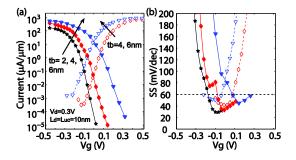

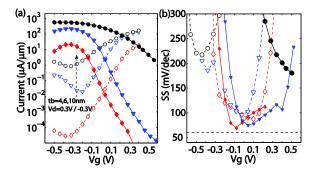

| 3.11 (a) IV characteristics for n-type and p-type L-shaped TFETs shown in Fig. 1a. (b) Extracted SS                                                                                                                                                                                                                                                                                                                       |

| 3.12 (a) IV characteristics of n-type and p-type TFETs with double gate UTB structures. (b) Extracted SS                                                                                                                                                                                                                                                                                                                  |

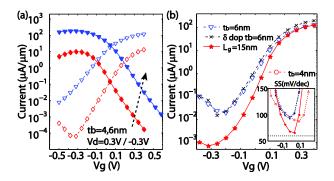

| 3.13 (a) IV-characteristics for single gate UTB TFETs. (b) Performance improvements of UTB TFETs due to δ doping, shifted gate position and increased gate length                                                                                                                                                                                                                                                         |

| 3.14 Band diagrams illustrating effects of $\delta$ doping and gate length in the UTB TFETs shown in Fig. 6                                                                                                                                                                                                                                                                                                               |

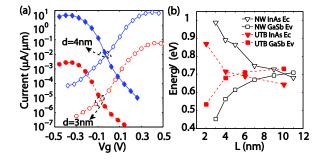

| 3.15 (a) IV characteristics for NW TFETs. (b) Modification of band edges with body thickness in UTB and diameters in NW                                                                                                                                                                                                                                                                                                   |

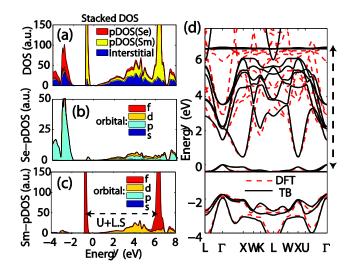

| 4.1 Stacked DFT DOS and DFT/TB bandstructure comparison. (a) DOS within muffin-tin radius of Sm/Se and interstitial DOS. (b) DOS within Se atom decomposed by angular momentum. (c) DOS within Sm atom decomposed by angular momentum. (d) Band structure by spdfs*_SO TB model without strain (black) and DFT band structure without strain (red). E=0 at top of valence band57                                          |

| Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

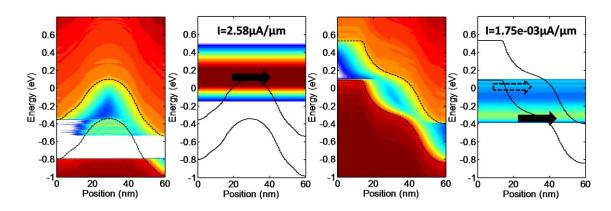

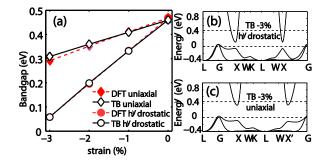

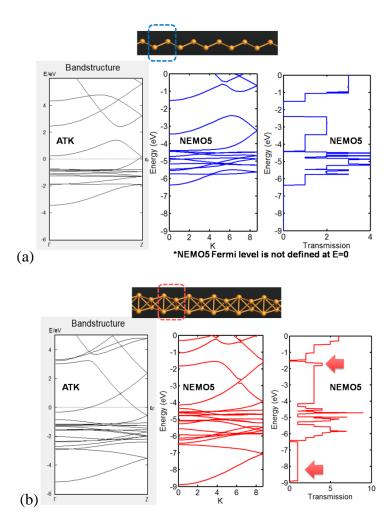

| 4.2 Comparison of bandgap modulations with strain calculated by DFT and TB. (a) Bandgap extracted from DFT and TB bandstructure under hydrostatic and uniaxial strain. (b) TB bandstructure with $\epsilon$ =-3% compressive hydrostatic strain $(a_x=a_y=a_z=(1+\epsilon)\times a_0)$ . (c) TB bandstructure with $\epsilon$ =-3% compressive uniaxial strain in growth direction $(a_x=(1+\epsilon)\times a_0;\ a_y=a_z=a_0)$ . Dashed lines show bulk band edges in (b, c). |

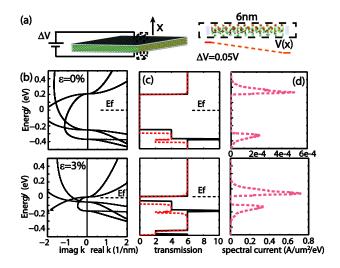

| 4.3 Transport simulation for SmSe with hydrostatic strain. (a) Simulated structure in and 6nm channel super cell in transport simulation. (b) Real and imaginary band structure for 0% and -3% hydrostatic strain. (c) Transmission with 0V and 0.05V linear drop potential. (d) Vd=0.05V, spectral current, <i>dJ/dE</i> , with linear drop potential.                                                                                                                        |

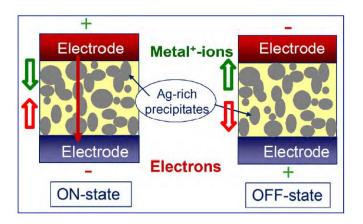

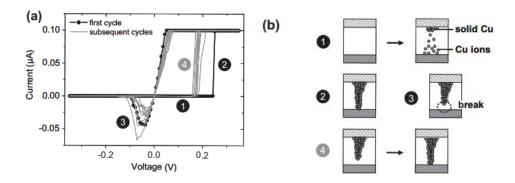

| 5.1 Principle of CBRAM. Directions of metal ion diffusion and electron conduction.  [73]                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.2 Typical IV characteristics of CBRAM showing bipolar asymmetric programming/erase feature. [75] Reprinted from Microelectronic Enginnering, 88 (5), pp814-816, Y. Bernard,V.T. Renard,P. Gonon,V. Jousseaume "Backend-of-line compatible Conductive Bridging RAM based on Cu and SiO <sub>2</sub> "(2011) with permission from Elsevier.                                                                                                                                    |

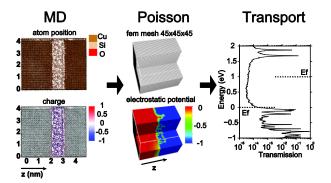

| 5.3 Simulation flow. Structures and charge profiles are generated by MD simulations.  The electrostatic potential is calculated based on atomic charges. Current is calculated by NEGF and conductance is extracted                                                                                                                                                                                                                                                            |

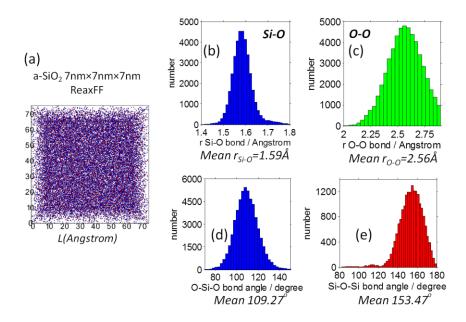

| 5.4 Bond length and bond angle in amorphous SiO <sub>2</sub> generated by ReaxFF. (a) Geometry of amorphous SiO <sub>2</sub> . (b-c) Distribution of bond length. (d-e) Distribution of bond angle                                                                                                                                                                                                                                                                             |

| 5.5 Bandstructure for β-cristobalite obtained with parameters of O'Reilly and Robertson[93]. This parameter set captures band position and could serve as initial values for our TB parameterization.                                                                                                                                                                                                                                                                          |

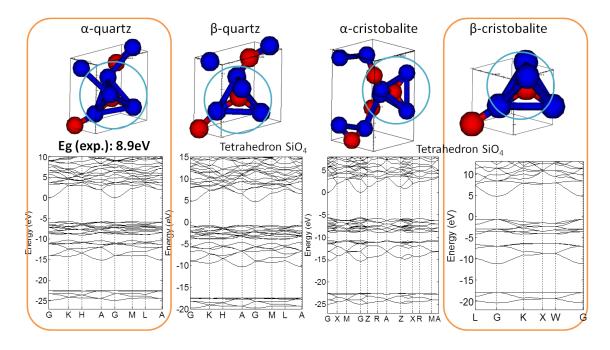

| 5.6 Bandstructure for 4 different crystalline SiO <sub>2</sub> calculated by LDA69                                                                                                                                                                                                                                                                                                                                                                                             |

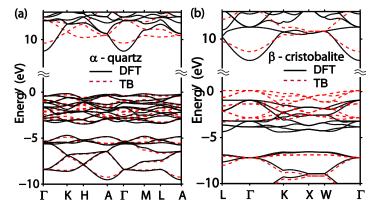

| 5.7 Copyright © 2015, IEEE. Comparison of bandstructure calculated by optimized TB parameters and DFT. Two crystalline SiO <sub>2</sub> are calculated by the same set of parameters.                                                                                                                                                                                                                                                                                          |

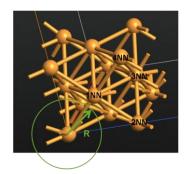

| 5.8 Bond radius in TB determines number of neighbor atoms coupled70                                                                                                                                                                                                                                                                                                                                                                                                            |

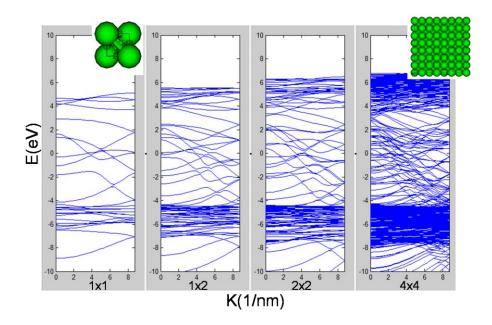

| 5.9 Effects of confinement simulated with environmental dependent TB with 2 <sup>nd</sup> nearest neighbor model. [27]                                                                                                                                                                                                                                                                                                                                                         |

| Figu | Page Page                                                                                                                                                                                                                                                                                                                                                                 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

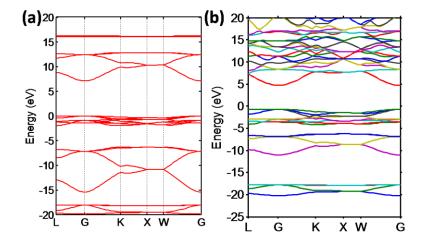

| 5.10 | Comparisons of Cu nanowire bandstructures calculated with DFT and TB72                                                                                                                                                                                                                                                                                                    |

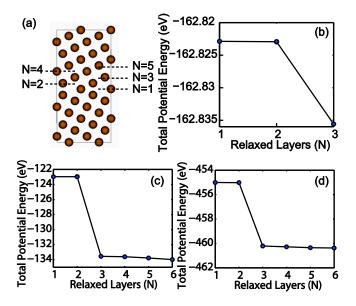

| 5.11 | (a) Relaxation of grain boundary. Atom positions of top and bottom layers are fixed. Periodic boundary condition is applied to directions parallel to GB. N layer atoms from the GB are allowed to move. (b-d) Total potential energies for (b) $\Sigma 3$ (48 atoms), (c) $\Sigma 5$ (40 atoms) and (d) $\Sigma 17a$ (136 atoms) GBs when N layers of atoms are relaxed. |

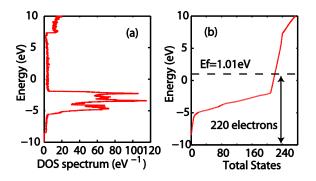

| 5.12 | Extract Fermi level from density calculation. (a) Density of states spectrum. (b) Cumulative total electron states                                                                                                                                                                                                                                                        |

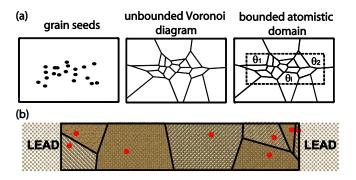

| 5.13 | Geometry generation. (a) Generate random seed → Voronoi diagram → Divide original geometry into grains. (b) Simulation domain with leads attached77                                                                                                                                                                                                                       |

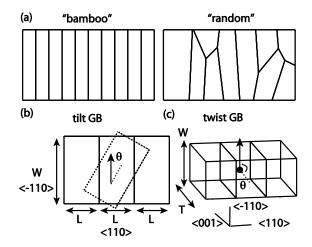

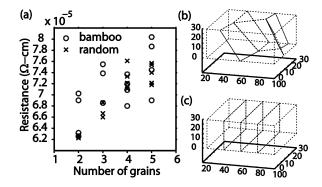

| 5.14 | Definition of special grain boundaries. (a) Bamboo and random GBs. (b) Tilt and twist GBs                                                                                                                                                                                                                                                                                 |

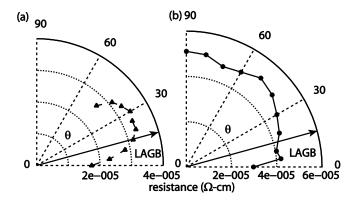

| 5.15 | Resistance of (a) tilt and (b) twist GBs                                                                                                                                                                                                                                                                                                                                  |

| 5.16 | (a) Resistance of GBs with general rotations. (b) Voronoi diagram for random GBs with 4 grains. (c) Voronoi diagram for bamboo GBs with 4 grains79                                                                                                                                                                                                                        |

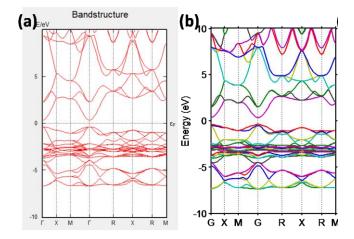

| 5.17 | Bandstructure of $\text{Cu}_2\text{O}$ simulated with GGA and Hybrid functional (VASP results calculated by Yaohua Tan). Only Hybrid functional result shows bandgap close to experimental value. [136]                                                                                                                                                                   |

| 5.18 | Crystal structure constructed from ATK builder. (a) Primitive unit cell of Cu <sub>2</sub> O. (b) Primitive unit cell of CuO. (c) Antiferromagnetic unit cell for CuO. Thick arrows indicate orientations of local magnetic moments. Thin arrows along [011] direction shows atom chain with strongest superexchange                                                      |

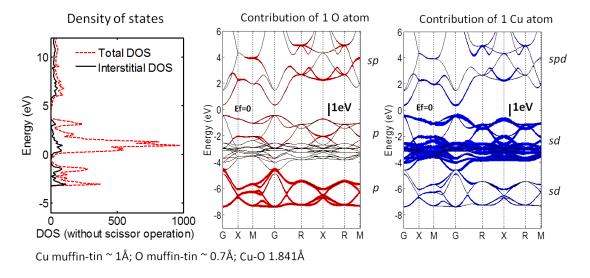

| 5.19 | Bandstructure of $Cu_2O$ calculated with (a) ATK with LDA+U (b) ELK with LDA+U compare to ref [136] with HSE. Results of (b) is calculated with crystal structure from Wyckoff [143] with $11\times11\times11$ k point and plane wave cut-off roughly $400eV$ .                                                                                                           |

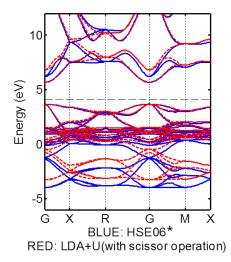

| 5.20 | Comparison of bandstructure calculated by HSE (HSE06 in VASP) and LDA+U (ELK). Bandstructure of LDA+U has been modified with scissor operation to match band gap with HSE                                                                                                                                                                                                 |

| 5.21 | Density of state for Cu <sub>2</sub> O and contributions of O and Cu atom to each band84                                                                                                                                                                                                                                                                                  |

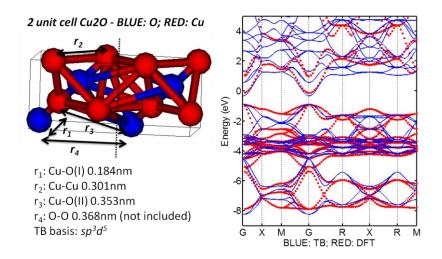

| 5.22 | Geometry of Cu <sub>2</sub> O unit cell. Based on the decomposition of bandstructure, sp <sup>3</sup> d <sup>5</sup> TB model is used and coupled atoms up to 3 <sup>rd</sup> nearest neighbor are included. Bandstructure after optimization captures important band features of DFT85                                                                                   |

| Figure Pa                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ge |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

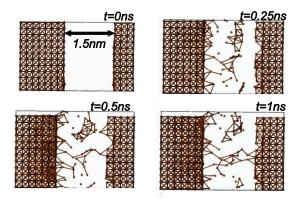

| 5.23 Copyright © 2015, IEEE. Diffusion of Cu atoms in SiO <sub>2</sub> at t=0, 250, 500, 1000ps. Si and O atoms are not plotted for better visibility. (a) Distance between electrodes is 1.5nm in initial structure. (b) Clusters are formed in SiO <sub>2</sub> . Two electrodes are not connected by filaments. (c) Two electrodes are connected by Cu filaments. The connectivity is plotted based on a coupling radius of 0.39nm. (d) More filaments are formed. | 86 |

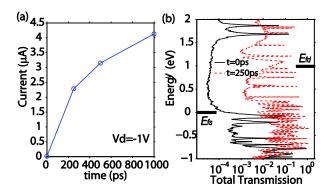

| 5.24 Copyright © 2015, IEEE. (a) Current for structures at Fig.3 at $V_d$ =-1V. (b) Total transmission at t=0ps and t=250ps.                                                                                                                                                                                                                                                                                                                                          | 86 |

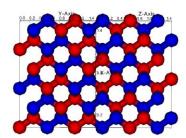

| 6.1 SiGe with RH1 ordering generated by NEMO5.                                                                                                                                                                                                                                                                                                                                                                                                                        | 87 |

| 6.2 Grains of SiGe with different ordering directions in RH2 ordering. (a) Each color shows a grain with uniform ordering direction. (b) SiGe with RH2 ordering                                                                                                                                                                                                                                                                                                       | 88 |

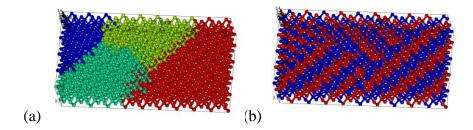

| 6.3 $Si_xGe_{1-x}$ with x=0.2, 0.5, 0.8. Each chunk with 2 grains with degree of ordering=0.9. Ordering direction are (1,1,1) (-1,-1,1) (-1,1,-1) (1,-1,-1) with probabilities (0.2609, 0.3043, 0.2174, 0.2174)                                                                                                                                                                                                                                                       | 89 |

#### **ABSTRACT**

Jiang, Zhengping. Ph.D., Purdue University, December 2015. Multi-Scale Simulations For High Efficiency Low Power Nanoelectronic Devices. Major Professor: Gerhard Klimeck.

Silicon based CMOS technology has been the driven force for semiconductor industry for decades. With higher degree of integration, transistors working under low supply voltage are desired to reduce power consumption. FinFET has been introduced to suppress the short channel effects and quantum tunneling; devices like Tunneling FET (TFET) and Piezoelectronic Transistor have been designed to achieve the subthreshold swing (SS) below 60mV/dec; novel memory cells like conductive bridging RAM (CBRAM) are able to operate at lower voltages and are more scalable than flash memory.

In this work, several emerging logic and memory devices have been studied. The devices are optimized for high efficiency low power applications. Non-equilibrium Green's function formulism with empirical tight binding (ETB) basis is used for quantum transport. The scaling of InGaAs FinFET is studied within virtual crystal approximation in the ballistic limit. The effects of random alloy scattering are discussed. The heterojunction TFETs are designed to achieve both low SS and high on-current. SmSe is parameterized to reproduce the metal insulator transition in Piezoelectronic Transistor. Copper is parameterized with the environmental dependent tight binding model and used for the study of grain boundary resistance in interconnects. Finally to study the resistive

switching of CBRAM, functionalities to import structures generated by Molecular Dynamics simulations and perform quantum transport have been developed. Calculations are done with efficient offloading scheme to accommodate the memory and speed requirements for realistic geometries.

# 1. INTRODUCTION

# 1.1 Scaling of MOSFET and requirements for low power devices

Si based MOSFET has been the most important device in the semiconductor industry history. Scaling of MOSFET has enabled the integration of high density of transistors in a single chip. As a result, modern circuits could accomplish more and more functionalities, while the cost is reduced. In 2011, Intel unveiled the world's first 3-D transistor in a high volume logic process with 22nm Tri-Gate transistor. Innovation in semiconductor technology has revolutionized our lives.

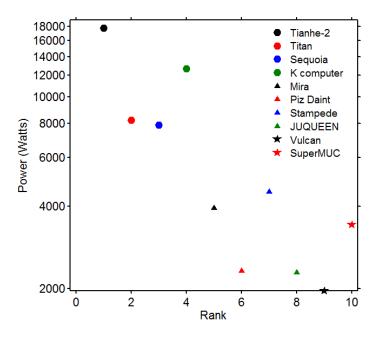

However, higher order of integration brings about another problem. Modern circuit faces severe problem of power consumption. As computer speed increases, power consumption also increases aggressively (Figure 1.1). To reduce power consumption, transistors are required to operate in lower supply voltage. However, logic device must maintain certain ON/OFF current ratio (~10<sup>4</sup>) to distinguish logic states. For MOSFET, the minimum subthreshold swing is 60mV/dec, which makes reducing supply voltage below 0.5V extremely hard. As transistor scales down, subthreshold swing is getting worse because of short channel effects and leakage due to tunneling. As a result, the supply voltage has stopped to scale at around 1V for long time.

Figure 1.1 Power consumption of top 10 supercomputer (Nov. 2013). Source: http://www.top500.org/

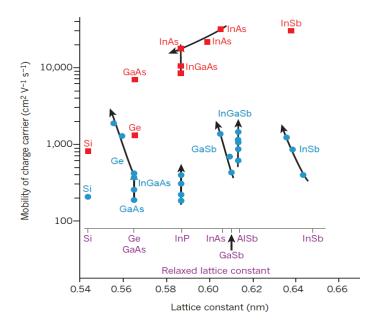

To continue Moore's law, innovations are required to control short channel effects and reduce tunneling to keep subthreshold swing close to or below 60mV/dec. New materials have been explored to increase ON current e.g. InGaAs[1], SiGe because of the high mobility over Si as shown in Table 1.1. Different orientations have been explored to reduce tunneling[2]. Optimizations of geometries are also actively studied. In Chapter 2 the short channel effects and tunneling of InGaAs NFET will be discussed in details. The performance of InGaAs NFET will be optimized and compared with Si NFET.

Table 1.1 Mobility of different materials[3, 4]

|                              | Si   | Ge    | GaAs  | InP   | In <sub>0.53</sub> GaAs |

|------------------------------|------|-------|-------|-------|-------------------------|

| e mob. (cm <sup>2</sup> /Vs) | 1600 | 3900  | 9200  | 5400  | 12000                   |

| $m_e^* (m_t/m_0)$            | 0.19 | 0.082 | 0.067 | 0.082 | 0.041                   |

| h mob.                       | 430  | 1900  | 400   | 200   | -                       |

Figure 1.2 Electron and hole mobility versus lattice constant. The impact of biaxial strain is indicated by an arrow representing increasing compressive biaxial strain.[1] Reprinted by permission from Macmillan Publishers Ltd: Nature (479, 317–323 doi:10.1038/nature10677), copyright (17 November 2011)

#### 1.1.1 Short channel effects

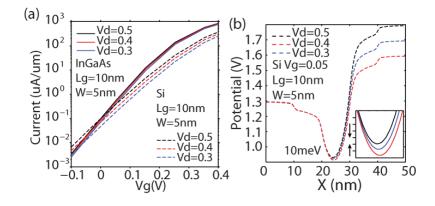

As the transistor is scaled down, one of the major short channel effects is drain introduced barrier lowering (DIBL). DIBL has two effects on device performance. It will firstly shift the threshold voltage. When channel length is further reduced, it will also affect the subthreshold slope. Figure 1.3a shows IV curve for InGaAs and Si MOSFET simulated in 2D double gate ultra-thin-body (UTB) geometry. Shift of threshold voltage shows the effects of DIBL. Barrier height is changed with Vd even with the same gate voltage. It is shown DIBL affects differently for different materials, which gives freedom for optimization.

Copyright © 2015, IEEE

Figure 1.3 Effects of DIBL. (a) IV for InGaAs and Si UTB MOSFET with different Vd.

Shift of threshold voltage shows effects of DIBL. (b) Lowering of barrier due to Vd.

# 1.1.2 Complex bandstructure and tunneling current

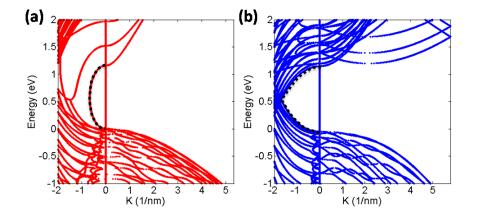

Quantum tunneling is one of the fundamental effects in quantum mechanisms. As shown in Ref. [5], as electron tunnels through a barrier, the electron wave will decay according to its complex wave vectors. In Wentzel-Kramers-Brillouin (WKB) approximation, for Zener tunneling [6], the transmission is  $T(E) = e^{-2\int dx \kappa(x)}$ , where  $\kappa(x)$  is the imaginary wave vector. It has been shown that single band model with parabolic band will underestimate tunneling probability[5]. Compared with the full band tight binding model, for indirect bandgap materials like Si and Ge, it is even hard for fit a single  $\kappa(x)$  as in Figure 1.4.

Figure 1.4 Complex bandstructure of In<sub>0.53</sub>GaAs and Si in 5nm UTB. (a) A single imaginary band will connect conduction and valence band. (b) Imaginary bands cross over each other. A single band could not be separated from other bands.

# 1.2 Emerging logic devices

Improving MOSFET will make subthreshold swing close to 60mV/dec, but that will be the fundamental limitation for MOSFET. To reduce supply voltage further, new device designs are required which is not limited by Boltzmann distribution of carriers in contacts.

# 1.2.1 Tunneling FET

Tunneling FET (TFET) is one of the most promising devices which could provide SS extremely low[7]. As shown in Figure 1.5 InAs UTB MOSFET and TFET with 10nm width are simulated at the same gate bias. In MOSFET, the leakage current is flowing at higher energies over the barrier, while in TFET bandgap of the source material will block the high energy carriers which are distributed according to Boltzmann distribution. In this condition, TFET gives 3 orders of magnitude smaller leakage current. Ideally, TFETs should have a sharp turn on when conduction band edge of channel is lower than valence band edge in source. However, there are new leakage mechanisms: firstly carrier still could tunneling through gate barrier like in MOSFET; secondly, when bandgap is small

and drain bias is big, addition tunneling happens near channel drain junction like shown in Figure 1.5 which is the main leakage path here.

In Chapter 3, a novel design of TFET with gate electric field in-line with tunneling direction is discussed. The advantages and limitations of the L-shaped TFET have been studied. A multi-physics simulation flow is designed to model the broken gap TFET.

Figure 1.5 Comparison of MOSFET and TFET density of states (logarithm scale) and current spectrum (logarithm scale) at V<sub>d</sub>=0.2V.

#### 1.2.2 Piezoelectronic transistor

Another way to overcome the subthreshold limit is by internally boost the gate voltage to generate larger barrier change than gate voltage change. One example is the Piezoelectronic Transistor (PET) [8-10].

In the PET the limitation on the Subthreshold Swing (SS) imposed by the thermal tail of Boltzmann distribution is overcome through internal transduction. A small gate voltage  $(V_g)$  is transduced to an acoustic wave through a high-performance piezoelectric (PE) actuator fabricated from a relaxor piezoelectric material. The expansion of the PE layer exerts pressure to a channel layer consisting of a piezoresistive (PR) material capable of undergoing a pressure-induced insulator to metal transition. Rare earth chalcogenide PR materials - such as SmSe and SmTe - can vary conductance by several

orders of magnitude when subjected to modest pressure changes[11]. Such conductance change is predicted to exceed the maximum conductance gain achievable in the MOSFET, which is  $10 \times V_g/60 mV$ .

Chapter 4 focuses on the material properties of SmSe, which is the key element of PET. The electronic bandstructure of SmSe has been modeled with *ab initio* approach. The metal-insulator transition of SmSe has been explained in terms of strain response of electronic bandstructure. SmSe has been parameterized in empirical tight binding basis which is well suited for large scale transport simulations.

# 1.3 Emerging memory devices

Memory is an indispensable part of computer system, especially non volatile memory (NVM), which retains stored information even when power is cut-off. Floating gate flash memory is the dominating NVM in market, widely used in all sizes of electronic devices. However, scaling of flash memory is far behind scaling of logic devices. Also flash memory requires very high operation voltage. New memory cells which are more scalable, low power are in demand. Many new memory technologies have been proposed. Table 1.2 lists some of the most promising designs. PCM and RRAM attract a lot of interests.

Table 1.2 ITRS 2013 emerging memory technologies. Green color shows the advantages and red color shows major drawbacks.

|             | Prototypical |      |       | Emerging      |        |             |

|-------------|--------------|------|-------|---------------|--------|-------------|

|             | FeRAM        | STT- | PCRAM | Ferroelectric | Redox  | Macromolec- |

|             |              | MRAM |       | memory        | memory | ular memory |

| Scalability |              |      |       |               |        | ?           |

| MLC         |              |      |       |               |        |             |

| Integration |              |      |       |               |        |             |

| Cost        |              |      |       |               |        |             |

| Endurance   |              |      |       |               |        |             |

In Chapter 5 the Conductive Bridging RAM (CBRAM) is introduced. Modeling of CBRAM requires multi-physics, multi-dimensional efforts. In this work, CBRAM based on SiO<sub>2</sub>/Cu is simulated. A complete simulation flow has been proposed to model both the electrochemical process and the electronic properties. Parameter sets for Cu and SiO<sub>2</sub> have been developed and enhanced. The Cu parameterization has been tested in modeling grain boundaries of nanoscale interconnect. The results are compared with literature results and show good agreement with *ab inito* simulations.

#### 1.4 Electronic Bandstructures

When device is at nanometer scale, the atoms in active region are countable. Atomistic simulation is nature choice for future computer aided design. Depending on size of system, different methods are available with different accuracies and convey different physics.

# **1.4.1 Density Functional Theory**

For system with small amount of atoms usually below a few hundreds, density functional theory (DFT) could be used. In DFT, properties of a many electron system are determined by functionals or density here. The Kohn-Sham DFT reduces the many-body problem of interacting electrons into non-interacting electrons moving in an effective potential called Kohn-Sham potential[12, 13]. The non-interacting particles will generate the same density as the original system. The effective potential includes the external potential and effects of the Coulomb interactions. However, the exact functionals for exchange and correlation are not known except for the free electron gas. Approximations are used including local-density approximation (LDA), generalized gradient approximations (GGA), metaGGA and hybrid functionals.

Varieties of quantum chemistry and solid state physics software are available. Different basis sets have been used. Earlier calculations use atomic orbitals composed of Slater-type orbitals (STOs); later STOs are approximated by linear combinations of Gaussian-type orbitals (GTOs); in addition to localized basis sets, plane-wave basis (PW) sets can also be used. Typically, a finite number of plane-wave functions are used defined by a specific cutoff energy; in the linearised augmented planewave (LAPW) method[14], based on atomic spheres approximation (ASA) the basis is atomic-like within muffin-tin spheres and connected to planewaves outside.

Table 1.3 Quantum chemistry softwares used in this work with major features (Hartree-Fock (HF); molecular mechanics (Mol. mech.))

|        | basis   | HF  | post-HF | Mol. mech. |

|--------|---------|-----|---------|------------|

| ELK    | FP-LAPW | Yes | No      | No         |

| VASP   | PW      | Yes | Yes     | Yes        |

| ATK    | NAO/EHT | No  | No      | Yes        |

| SIESTA | NAO     | No  | No      | Yes        |

#### 1.4.2 Empirical Pseudo-potential Method

The Empirical Pseudopotential Method (EPM) was originally developed as an efficient way to solve the Schrodinger's equation for bulk crystals. It assumes that the core electrons are tightly bound to the nuclei (frozen core approximation) and the valence electrons are only influenced by an effective potential. This potential could be represented by a truncated Fourier series. The expansion coefficients are generally fitted to reproduce important material properties.

## 1.4.3 Extended Hückel Theory

Extended Hückel method (EHT) is another semi-empirical method to calculate electronic properties of materials. In the EHT model the Hamiltonian is expanded in a basis of local atomic orbitals. The orbitals are not required to be orthogonal to each other. EHT requires very small number of parameters, which makes the fitting process much easier. However, because EHT uses non-orthogonal basis, transport simulation requires calculation of overlap matrix. This potentially increases the memory and turnaround time.

## 1.4.4 Empirical tight binding

DFT has successfully predicted properties of material properties, but the total atoms in calculation are limited to a few hundreds. For more realistic device, empirical tight binding method could be highly parallelized and handle hundred thousand atoms in quantum transport and over million atoms in electronic calculation [15-17]. The empirical tight binding method or the modified linear combination of atomic orbitals (LCAO) method published by Slater and Koster (SK)[18] is an extension of Bloch's original LCAO method[19]. The parameters could be obtained by fitting to electronic energy bands and density of states [20-23]. In the Naval Research Laboratory tight-binding (NRL-TB)[24, 25], total energy is included as fitting target and distance and environment-dependent SK parameters are used to include transferability. Also there are some recent works which generate SK parameters from directly mapping of DFT[26] and include environmental dependency for metals[27].

# 1.5 High performance computation

# 1.5.1 NEMO5 and nanoHUB.org

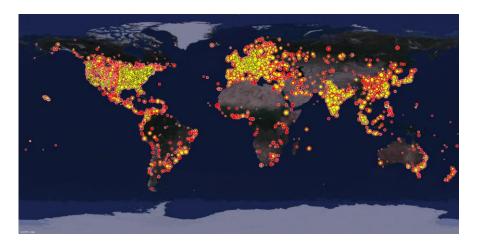

nanoHUB.org is a online platform for computational nanotechnology research, education, and collaboration. People could get free access to online presentations, courses, learning modules, podcasts, animations, teaching materials, and more about nanotechnology. For researchers, simulations could be done in cloud without installing. They could access computation resources which are usually restricted to general users. They could develop their simulation tools and publish them with user-friendly GUI for higher impact. Every year, users from all over the world benefit from nanoHUB.org as shown in Figure 1.6.

Figure 1.6 Nearly 250,000 users participate in nanoHUB, an online meeting place for simulation, research, collaboration, teaching, learning and publishing. The red dots indicate users of online lectures, seminars, courses and teaching materials, while yellow dots indicate simulation users. (Photo illustration by Office of the Vice President for Research)

NEMO5[17] is the fifth edition of the NanoElectronics MOdeling Tools of the Klimeck group. It incorporates the core concepts and insights gained from 15 years of development of NEMO-1D, NEMO-3D, NEMO-3D-Peta and OMEN. Majority of the works shown in this thesis proposal have been performed within NEMO5 and are

incorporated into the NEMO5 development. Some of the functionalities of NEMO5 are accessible through online simulation tools in nanoHUB.org.

## 1.5.2 Parallel computing

In the area of computational nanoelectronics, accurate band models are desired to describe the simulated system. Meanwhile complicated models require more computational resources. Nowadays, it is extremely difficult to achieve meaningful modeling without massive parallelization. Different parallelization schemes have been used for the studies in this thesis including Message Passing Interface (MPI) and Open MPI. Computation is further accelerated by offloading the computationally heavy matrix multiplication operations into coprocessors. The speed up with offloading is presented in Chapter 5.

# 1.6 Contributions of the present work and thesis organization

As the scaling of Si MOSFET becomes more and more difficult, semiconductor industry has been looking for new approaches to continue the Moore's law. This requirement imposes great challenges as well as great opportunities to the advance of computational nanoelectronics. *On one hand*, there is the growing need for more accurate modeling. As device sizes shrink, the granularity of materials starts to show profound effects; random dopants, roughness, grain boundaries, impurities all bring uncertainties to the device performances. Atomistic modeling is getting more and more recognition. As new materials are utilized and devices with new physics are developed, predictive simulations are desired for prototyping and path finding study. Even for the traditional materials and technologies, existing modeling frameworks need recalibration with more advanced models. *On the other hand*, modeling approaches have limitations by

themselves. New modeling approaches need to be developed to fulfill the growing need to match new experimental observations. While the complexities of models are limited by the computational resources; due to the balance of accuracy and productivity, no single modeling approach is able to fulfill all the simulation requirements.

This thesis work deals with the dilemma from the following aspects:

- (1) Path-finding studies on the new materials and new devices with the atomistic modeling approaches.

- (2) Design modeling flows with high accuracy while maintain manageable computational complexities.

- (3) Explore the multi-physics multi-dimensional modeling flow to break the limitation of individual approach.

The thesis is organized as follows:

In Chapter 2, the design space of InGaAs MOSFET is explored to suppress short channel effects and tunneling. Empirical tight binding model and effective mass model are compared for this application and the limitations of both models are revealed. Effects of alloy scattering are studied with the atomistic approach.

In Chapter 3, the semiclassical potential is used for fast prototyping of the novel L-shaped Tunneling FET. The advantages and limitations of the TFET for continuous scaling are studied. The non-equilibrium Green's function approach is compared with the non-local dynamic band to band tunneling model. This study proves the necessity of full quantum transport approach in predictive modeling of TFETs.

In Chapter 4, the working principles of the Piezoelectronic Transistor are introduced which could achieve subthreshold swing below 60mV/dec. One of the key component

materials SmSe has been modeled using the *ab inito* approach with LDA+U functional. A physics based process has been used to parameterize SmSe in the empirical tight binding basis.

In Chapter 5, the multi-physics flow is designed to modeling the Conductive Bridging RAM. Cu and SiO<sub>2</sub> are parameterized in the empirical tight binding basis. Grain boundary resistance is also studied with the obtained Cu parameter set. The results are compared with more advanced DFT-NEGF approach. Both models show consistent results while our approach allows for large scale simulations.

In Chapter 6, future works are presented.

# 1.7 Reuse of published work

The work in this thesis is based on the papers published in different journals. Figures and contents have been reused from these publications in this work. The permissions for the reuse of contents and figures from the publishers have been obtained which are present in the Appendix B.

# 2. SCALING OF INGAAS FINFET

# 2.1 Methods for alloy simulation

Figures and portions of this chapter have been reproduced verbatim from Electron Devices, IEEE Transactions on (Volume:62, Issue: 2) "Tunneling and Short Channel Effects in Ultrascaled InGaAs Double Gate MOSFETs" Zhengping Jiang, Behtash Behin-Aein, Zoran Krivokapic, Michael Povolotskyi, Gerhard Klimeck. Copyright 2015 IEEE.

Scaling of Si based MOSFET has been driven force for semiconductor industry. FinFET with 22nm channel length has been announced and further scaling of channel length is down to 7nm. To continue scaling, InGaAs attracts great attention as alternative channel material and efforts have been made for fabricating non-planar devices [28-30]. With shrinking size, devices will operate beyond drift diffusion regime and quantum effects start to show profound impacts; material properties will alter dramatically under confinement. Understanding of FinFET scaling behavior by quantum transport simulation is in demand.

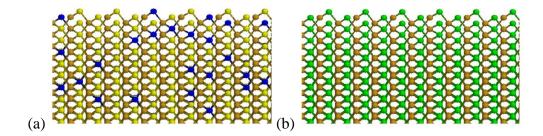

Unlike binary materials, InGaAs is alloy as shown in Figure 2.1a. It could be considered as GaAs binary material with Ga atoms randomly replaced by In according to certain composition.

Figure 2.1 Illustration of InGaAs in random alloy and VCA. (a) Random alloy crystal with In atoms replaced by Ga. (b) VCA crystal with two types of atom: As and virtual atom InGa.

Simulation of alloy material usually has two types of methods. Firstly, randomness of alloy is ignored. Effective mass approximation (EM) and virtual crystal approximation (VCA) [31] fall into this category. Otherwise, alloy is simulated by replacing atoms explicitly[32, 33] which is called random alloy method (RA) in this work.

EM used to provide good approximation when device dimension is big and transport happens near bottom of conduction band. However, under confinement strong non-parabolicity must be taken into consideration. Figure 2.2a shows band structure of bulk InAs and in  $3\times3$ nm nanowire. Confinement raises the subbands and changes the effective masses. Solid and dashed horizontal lines show the first and second subband positions. In EM if non-parabolic parameter is not accurate, the subband position will be overestimated greatly as shown in Figure 2.2b-d with increasing  $\alpha$ , similarly for subbands in FinFET as shown in Figure 2.3.