## **Network for Computational**

# Purdue, Norfolk State, Northwestern, MIT, Molecular Foundry, UC Berkeley, Univ. of Illinois, UTEP DESIGN GUIDELINES FOR LOW POWER TRANSISTORS AND HIGH EFFICIENCY PHOTOVOLTAICS

### Samarth Agarwal

samarth@purdue.edu

Advisors:

Gerhard Klimeck

Ronald Reifenberger

## **Network for Computational**

Purdue, Norfolk State, Northwestern, MIT, Molecular Foundry, UC Berkeley, Univ. of Illinois, UTEP

# DESIGN IDEAS FOR LOW POWER TRANSISTORS

Samarth Agarwal, Mathieu Luisier & Gerhard Klimeck samarth@purdue.edu

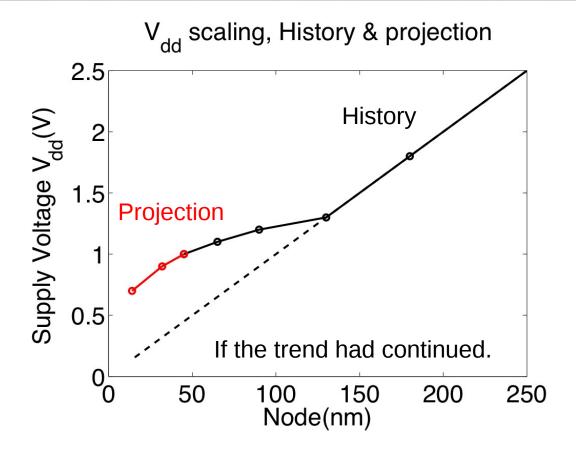

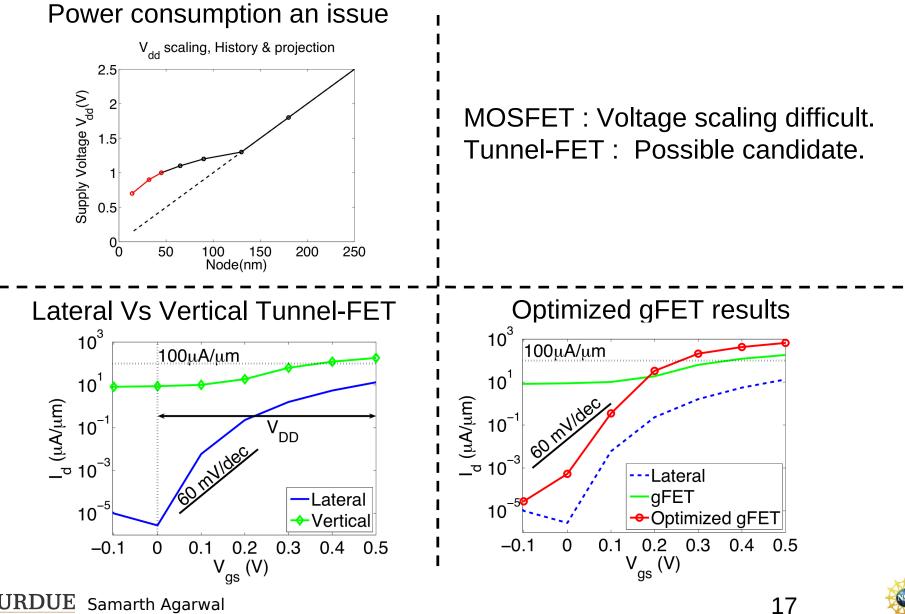

#### **CONTRACT** Motivation: Voltage Scaling in MOSFETs

- Supply Voltage  $V_{DD}$  scaling keeps power consumption per chip under control.

- •Heading for a crisis.

Source: ITRS(2007) & C. Hu, Green Transistor as a solution to the IC power crisis.

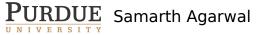

MOSFET

Subthreshold Swing

nanoHUB.org

Supply voltage (V<sub>DD</sub>) scaling

Fundamental 60mV/dec limit at room temperature.

Difficult since either increase of OFF-current or decrease of ON-current, both undesired

ON-current

High, >1000 μA/μm Ve

Tunnel-FET

Theoretically no lower limit.

Possible, without any adverse affects.

Very Low: BIG CHALLENGE!

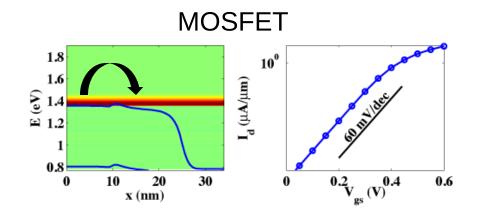

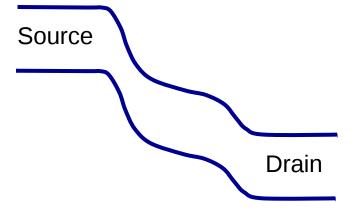

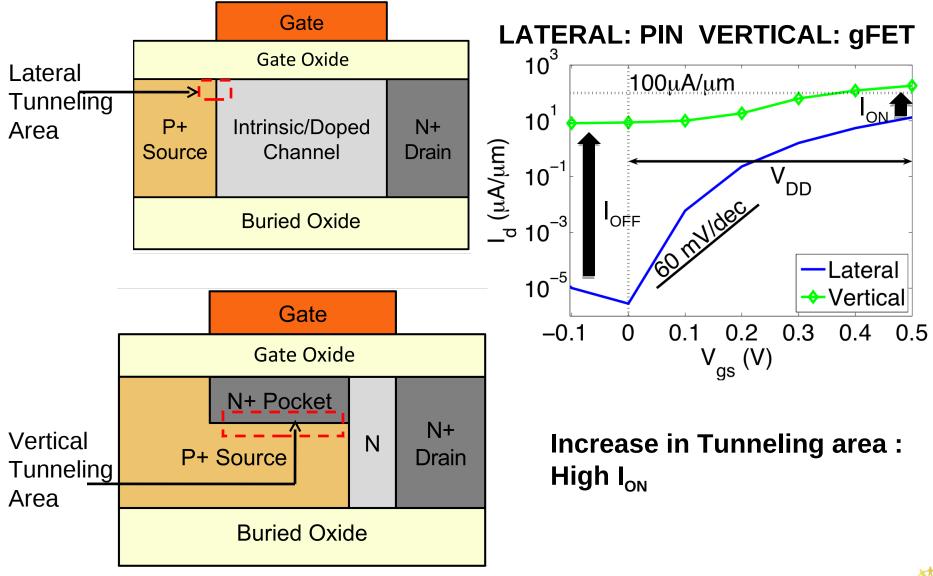

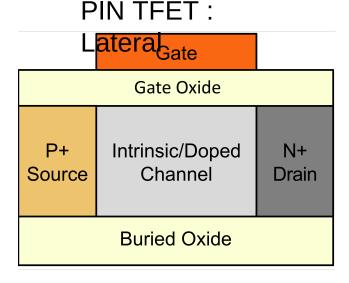

### **Tunnel-FET : PIN structure**

- Low ON current.

- Effect of gate not beyond 5nm.

- Small tunneling area.

- Electric field diminishes from top to bottom (gate to ground).

Equilibrium : OFF STATE

Positive gate bias: ON STATE

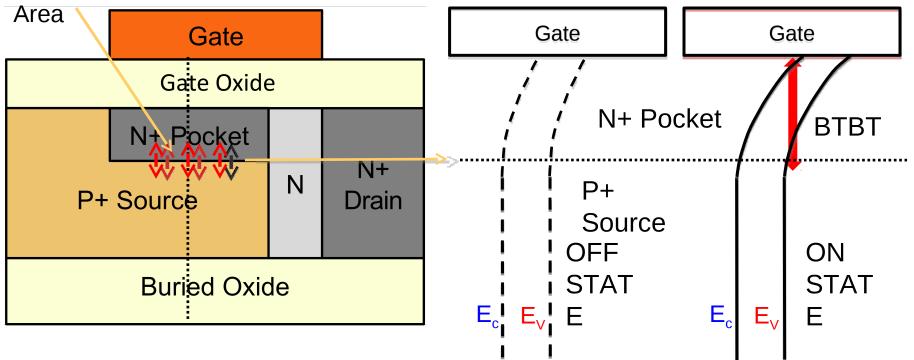

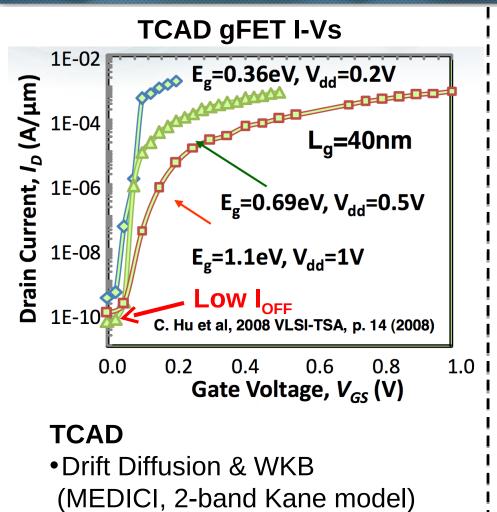

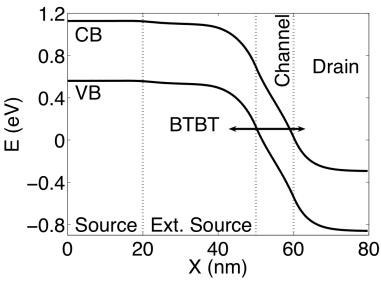

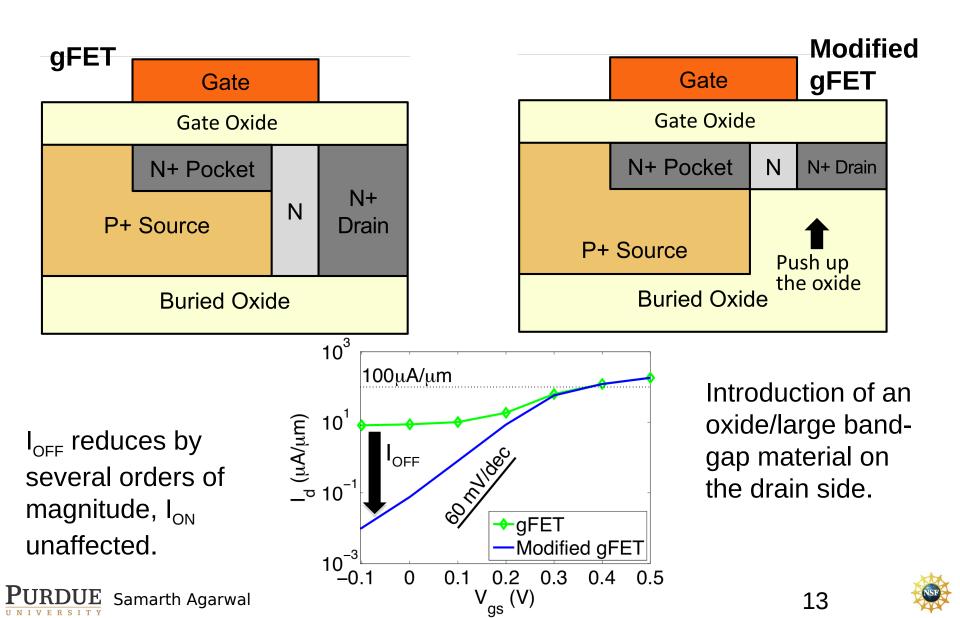

# <sup>οδο</sup> <u>ΛC</u> A special Tunnel-FET: Green-FET (gFET)

#### Tunneling

Source: Chenming Hu, Green Transistor as a solution to the IC power

crisis.

- •Large ON current: Large and uniform field over a substantial area. ( Proportional to pocket length )

- Direct modulation of tunneling current through gate contact.

- •Only commercial TCAD simulations, no Experimental results!

**PURDUE** Samarth Agarwal

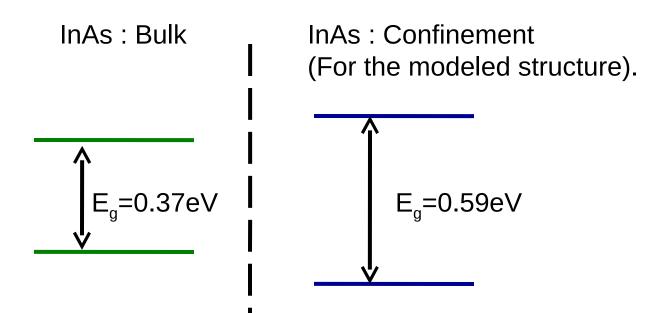

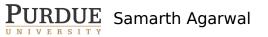

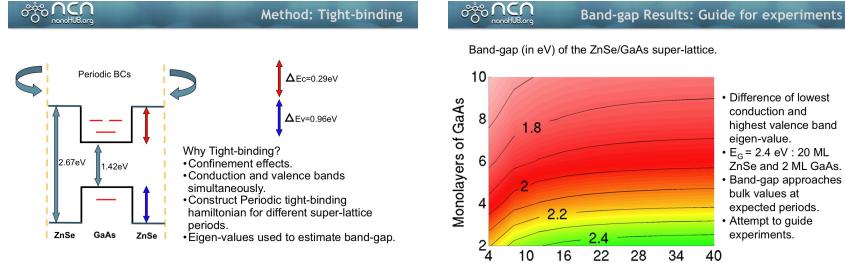

Why Tight-Binding?

- •Band Gap, effective mass: Bulk Vs Confinement

- •Conduction and valence bands simultaneously.

- •Tunneling probability in the forbidden gap.

PURDUE Samarth Agarwal

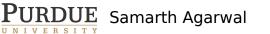

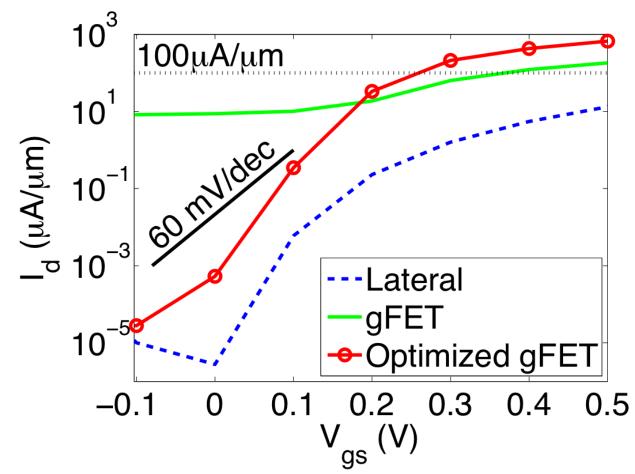

### **Lateral Vs Vertical**

## InAs gFET results: TCAD Vs OMEN

Tunneling in specific regions only

10<sup>3</sup> 100µA/µm **10**<sup>1</sup> (µn/Yn) 10<sup>-3</sup> High I<sub>OFF</sub> DD myldec —Lateral -5 10 Vertical 0.2 -0.10.3 0.1 0.4 0.5 0 V<sub>gs</sub> (V)

LATERAL: PIN VERTICAL: gFET

### OMEN

- •Atomistic, Full Band, Nonequilibrium Quantum transport

- •Tunneling present everywhere.

- High  $I_{ON}$  but high  $I_{OFF}$

• High  $I_{ON}$  and low  $I_{OFF}$

### gFET OFF state current

- •Region below the pocket & PIN TFET, similar.

- •Weak electrostatic control away from the gate.

- Possibility of a current pathway contributing to OFF state current.

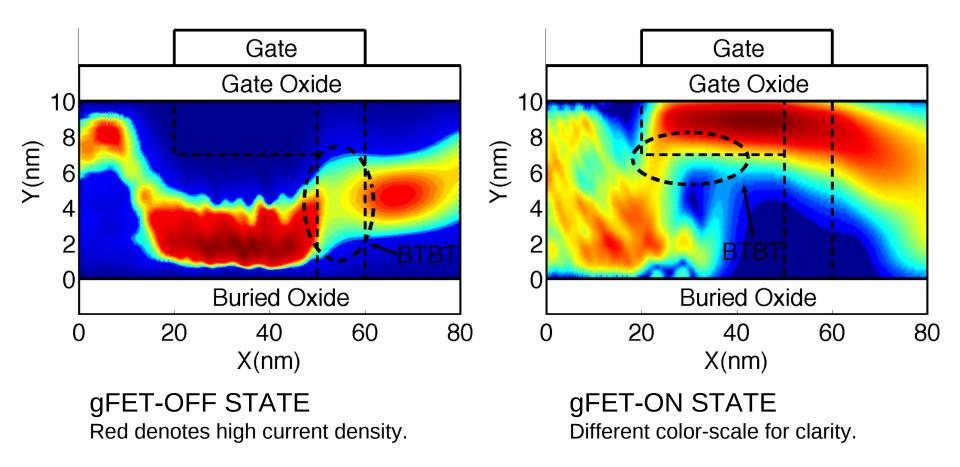

## gFET spatial current distribution

- OFF STATE: Lateral Tunneling

- ON STATE: Vertical Tunneling

- Unsuitable for low power logic applications: Necessitates a modification.

**PURDUE** Samarth Agarwal

12

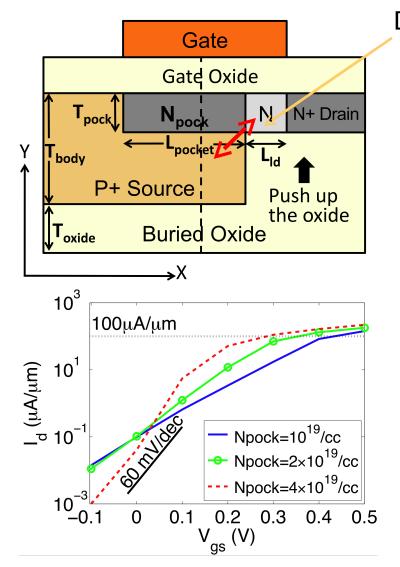

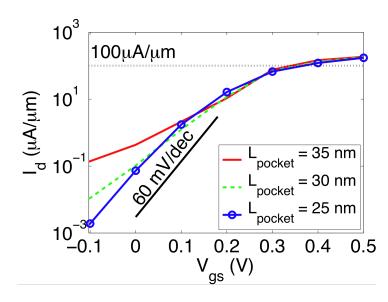

# CONTRACTOR OF Pocket doping & Pocket length

PURDUE Samarth Agarwal

Diagonal current pathway

- Higher pocket doping gives higher electric fields.

- Shorter pocket length increases the length of diagonal current pathways.

14

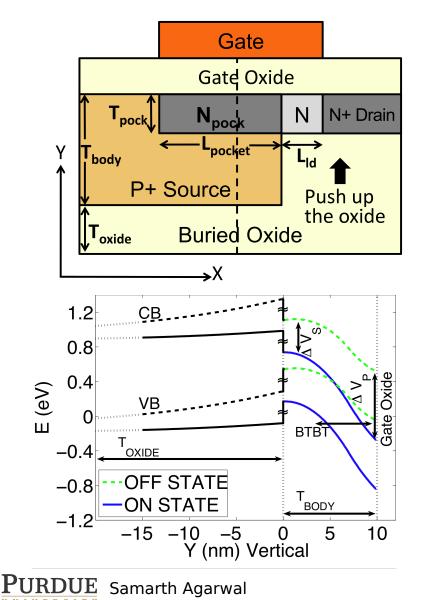

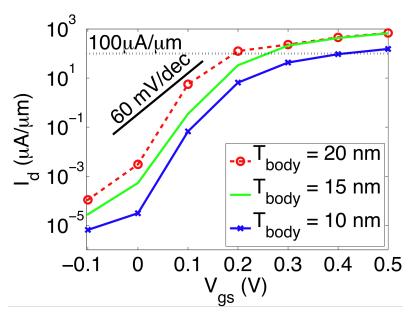

### **Effect of Body thickness**

- •Bands shift, away from the gate.

- Shifting of bands not good for BTBT.

- Shifting can be reduced by increasing body thickness (T<sub>BODY</sub>).

•Optimized gFET: Modified gFET + (optimized pocket doping/length and body thickness)

## **Network for Computational**

Purdue, Norfolk State, Northwestern, MIT, Molecular Foundry, UC Berkeley, Univ. of Illinois, UTEP

# DESIGN GUIDELINES FOR HIGH EFFICIENCY PHOTOVOLTAICS

Samarth Agarwal, Kyle Montgomery, Timothy Boykin, Gerhard Klimeck and Jerry Woodall Network for Computational Nanotechnology (NCN) Birck Nanotechnology Centre samarth@purdue.edu

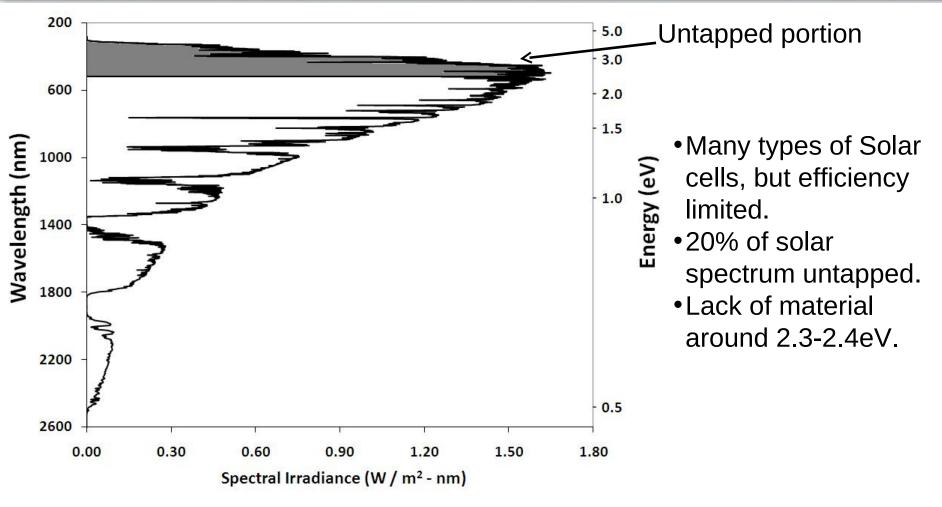

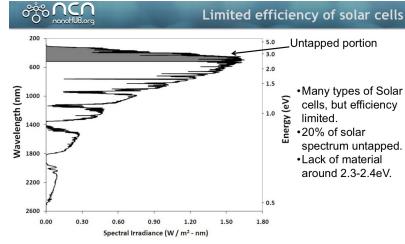

### Limited efficiency of solar cells

AM 1.5 Solar spectrum: Shaded region corresponds to 21.1% of total irradiance. Fig. by Kyle Montgomery.

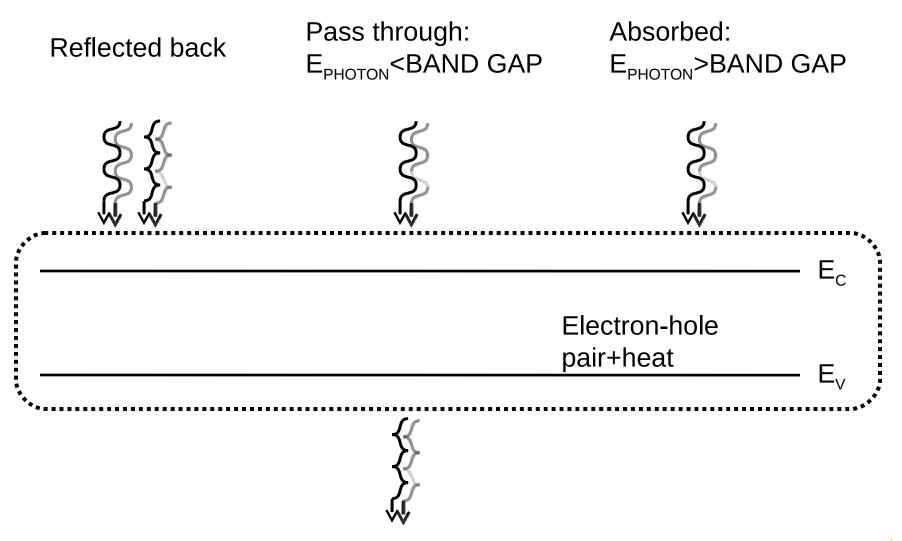

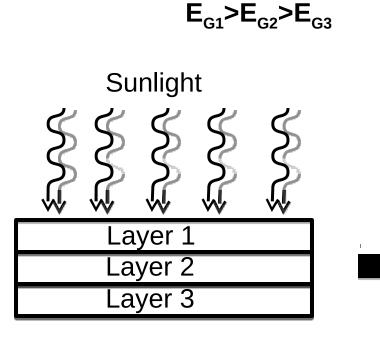

### **Multi-junction Solar cells**

- Pass through :  $E_{PHOTON}$  < BAND GAP

- Absorbed : E<sub>PHOTON</sub>>BAND GAP

- Substantial portion of the spectrum can be tapped.

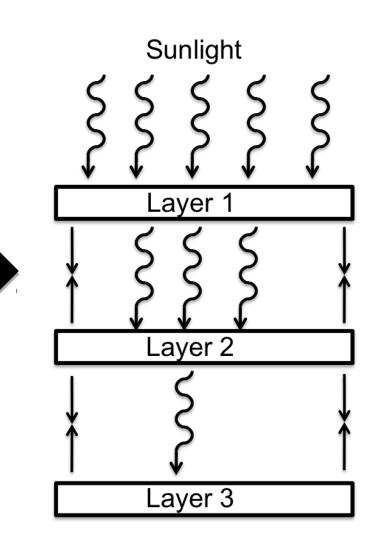

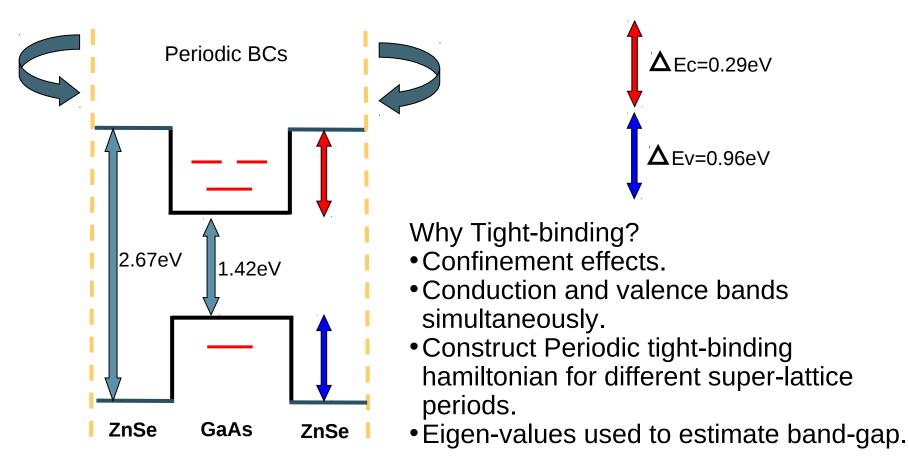

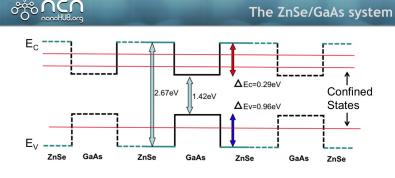

### The ZnSe/GaAs system

- Lattice matched : Can fabricate "Digital Alloys".

- Confined states dominate the band-edge. (Esaki & Tsu(1970), IBM).

- Super-lattice period determines the electronic properties.

Band offsets based on (A.J. Ekpunobi, Materials Science in Semiconductor Processing 8(4))

### For ZnSe:

Parameters from Vogl et. al. Inaccurate effective masses.

Uses low temperature gaps

Does not include spin-orbit coupling.

Need to re-parametrize

More accurate experimental data available. (Landolt–Börnstein tables)

Device operates at room temperature.

Spin-orbit interaction necessary to model the imaginary band linking the conduction and valence bands.

For GaAs: Source T. B. Boykin, G. Klimeck, R. C. Bowen, and R. Lake, PRB 56, 4102 (1997).

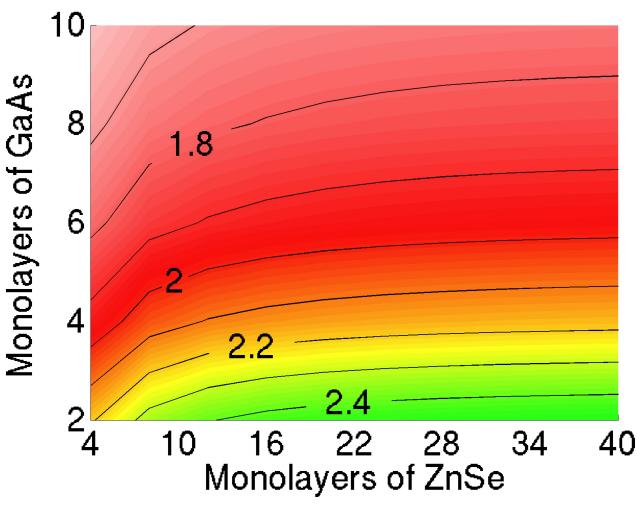

# nanoHUB.organd-gap Results: Guide for experiments

### Band-gap (in eV) of the ZnSe/GaAs super-lattice.

- Difference of lowest conduction and highest valence band eigen-value.

- E<sub>G</sub> = 2.4 eV : 20 ML ZnSe and 2 ML GaAs.

- Band-gap approaches bulk values at expected periods.

- Attempt to guide experiments.

### **Summary**

AM 1.5 Solar spectrum: Shaded region corresponds to 21.1% of total irradiance. Fig. by Kyle Montgomery.

• Lattice matched : Can fabricate "Digital Alloys" with  $E_G$ = 2.3-2.4 eV

• Confined states dominate the band-edge. (Esaki & Tsu(1970), IBM).

· Super-lattice period determines the electronic properties.

Monolayers of ZnSe

Band offsets based on (A.J. Ekpunobi, Materials Science in Semiconductor Processing 8(4))

Patents: co-patentee on,

- Tunneling field effect transistor with Low Leakage Current.

- Solar Cell and LED with lattice matched super-lattice structure and fabrication method thereof.

Journal Publications:

- •Agarwal, S.; Klimeck, G.; Luisier, M.; , "Leakage-Reduction Design Concepts for Low-Power Vertical Tunneling Field-Effect Transistors," Electron Device Letters, IEEE , vol.31, no.6, pp.621-623, June 2010.

- Samarth Agarwal, Kyle H. Montgomery, Timothy B. Boykin, Gerhard Klimeck, and Jerry M. Woodall, Design Guidelines for True Green LEDs and High Efficiency Photovoltaics Using ZnSe/GaAs Digital Alloys, Electrochem. Solid-State Lett. 13, H5 (2010).

- Samarth Agarwal, Michael Povolotskyi, Tillmann Kubis and Gerhard Klimeck, Adaptive quadrature for sharply spiked integrands, Journal of Computational Electronics, vol 9, no.3-4, 252-255.

Other publications:

- S. Agarwal, G. Klimeck, 1D hetero-structure tool for atomistic simulation of nano-devices, Proceedings of TECHCON 2008, Austin, TX, Nov. 3-4, 2008.

- Kyle Montgomery, Samarth Agarwal, Gerhard Klimeck, and Jerry Woodall, Proposal of ZnSe/GaAs Digital Alloys for High Band Gap Solar Cells and True Green LEDs, IEEE Nanotechnology Materials and Devices Conference (NMDC 2009), June 2-5, 2009, Traverse City, Michigan, USA.

Simulation tools on the nanoHUB:

- Transport in 1D heterostructures.

- Poisson Schrödinger Solver for 1D heterostructures.

- Transfer matrix and tight-binding tool for 1D Heterostructures. Supporting documents and chapters for a book by World Scientific.

### Prof. Klimeck & Prof. Reifenberger

### Prof. Datta & Prof. Savikhin

### Prof. Vasileska, Prof. Boykin & Prof. Woodall

### Dr. Mathieu Luisier

### All NCN students and group members

Thank You!