# Design and Simulation of Two-dimensional Superlattice Steep Transistors

Pengyu Long,

Network for Computational Nanotechnology, Purdue University,

West Lafayette, IN 47907, USA

long106@purdue.edu

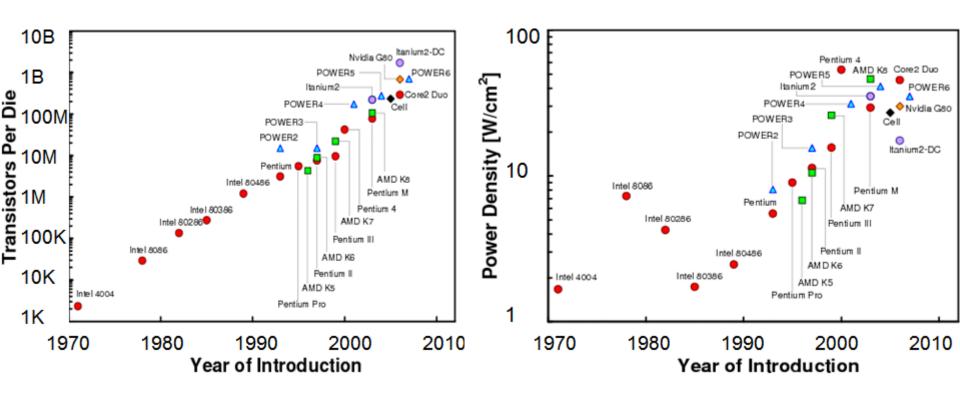

transistor density increase → power density increase

Isci C. Workload adaptive power management with live phase monitoring and prediction[D]. Princeton University, 2007.

### Motivation: reduce power density

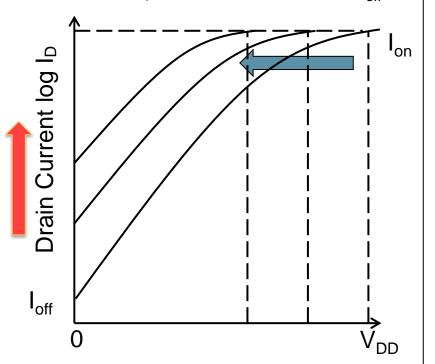

- Constant Subthreshold Swing:

- » Reducing the supply voltage(V<sub>DD</sub>)

- → reduced power, but increase in I<sub>off</sub>

- Steeper Subthreshold Swing:

- » Reducing V<sub>DD</sub> → reduced power, I<sub>off</sub> doesn't increase!

Low power design → require steep Subthreshold Swing

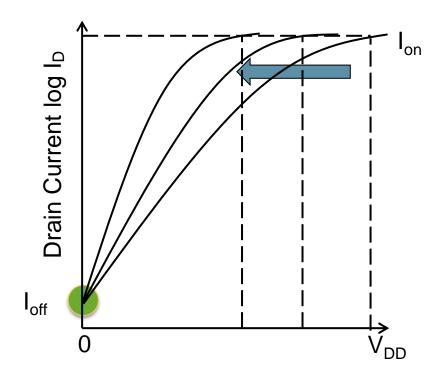

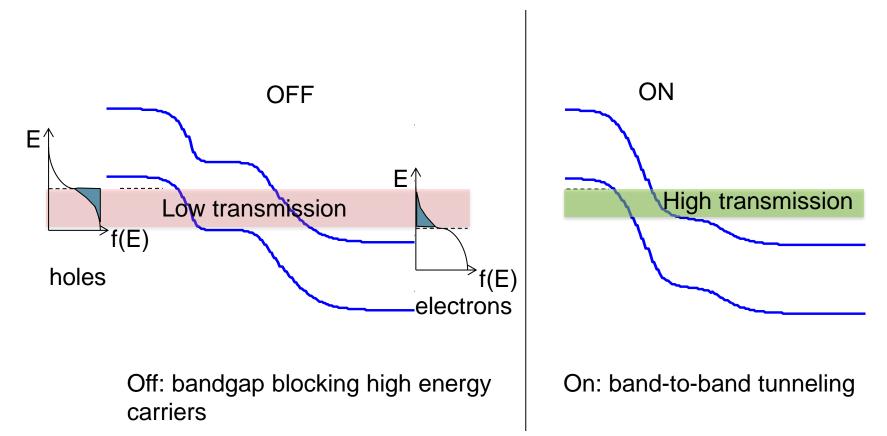

Problem: The 60mV/dec limit: comes from high energy electrons in f(E)

High energy electrons have high transmission to get into channel.

Solution: add an energy filter to suppress high energy electrons

# How to reduce the Subthreshold Swing

Existing energy filter design: Tunneling FET (TFET)

Energy filter → High energy carriers are suppressed → steep Subthreshold Swing

Problem: At on-state, the tunneling transmission is small → limited I<sub>on</sub>

#### Band-to-band tunneling:

- high energy electrons are blocked → Steep subthreshold swing

- Limited tunneling probability → Limited I<sub>on</sub>

Any energy filters that has both steep subthreshold swing and high lon?

|                        | Suppress high energy carries | High transmission at on-state |

|------------------------|------------------------------|-------------------------------|

| Band-to-band tunneling | Yes                          | limited                       |

| Resonant tunneling     | Yes                          | Yes                           |

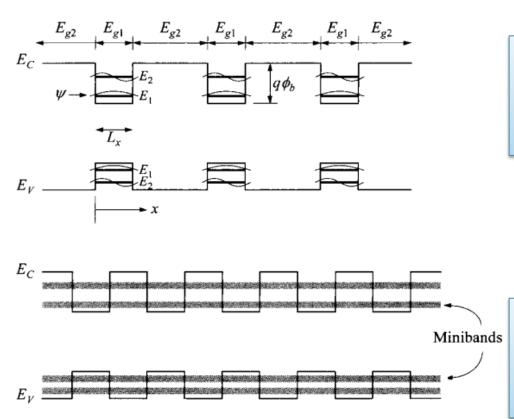

### New solution: superlattice energy filter

#### Superlattice:

- Minigap: intrinsic energy filter → steep Subthreshold swing.

- Wide and smooth miniband → high I<sub>on</sub>

- Separated quantum wells

- wavefunction are separated

→ discrete confined states

- Superlattice

- wavefunction are overlapped

→smooth minibands

Sze S M, Ng K K. Physics of semiconductor devices[M]. John Wiley & Sons, 2006.

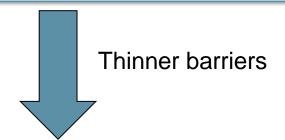

### Nanowire superlattice MOSFET

Proposed in literature

The superlattice has to be in the source

- If placed in channel: distorted by Vgs

- If placed in the drain: distorted by Vds

Vertical nanowires might be hard to fabricate and achieve high Ion per die.

- Maiorano P, Gnani E, Grassi R, et al.. Solid-State Electronics, 2014, 98: 45-49.

- Gnani E, Reggiani S, Gnudi A, et al. ICSICT, 2010, 1: 2.

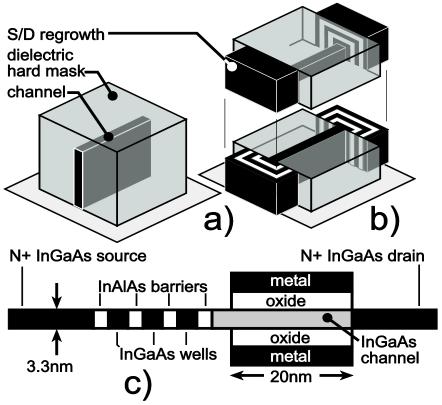

In this work, the concept is applied to 2D geometry.

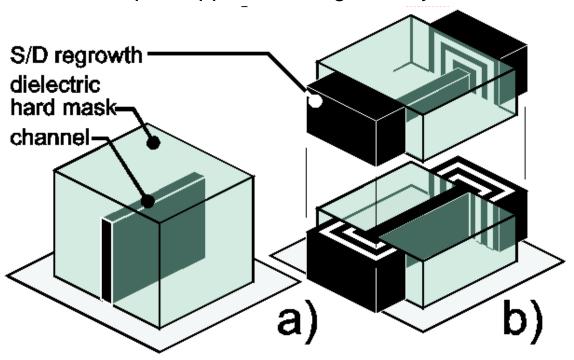

Step 1: first form an InGaAs fin

Step 2: growth of InGaAs and InAlAs

more easily fabricated and achieve higher I<sub>on</sub> per die than vertical nanowires

### 2D superlattice MOSFET

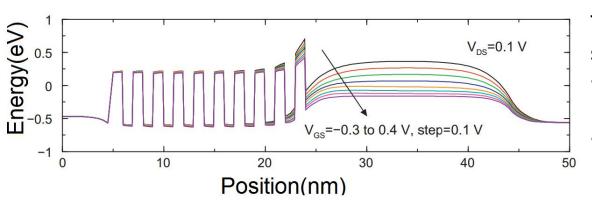

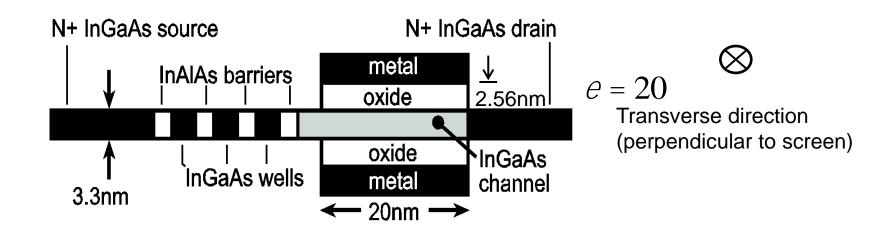

- Double Gate MOSFET with 4-barrier superlattice in the source.

- The transverse direction is periodic(infinitely long).

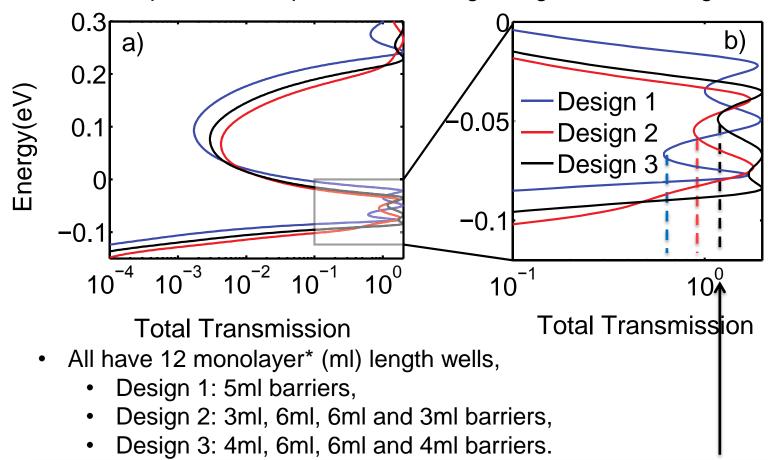

### Superlattices considered:

- InGaAs/InAlAs

- InAs/InAlAs

Can achieve higher I<sub>on</sub> per die than vertical nanowires

#### Method:

- Ballistic transport : quantum transmitting boundary method(QTBM)

- sp3d5s\* tight binding basis to represent band structure

- Open-boundary Schrödinger equation & Poisson equation solved selfconsistently.

- Optimization design for superlattice MOSFETs

- Target:

- steep Subthreshold Swing

- o High I<sub>on</sub>

- Strategy:

- Geometry optimization

- Material

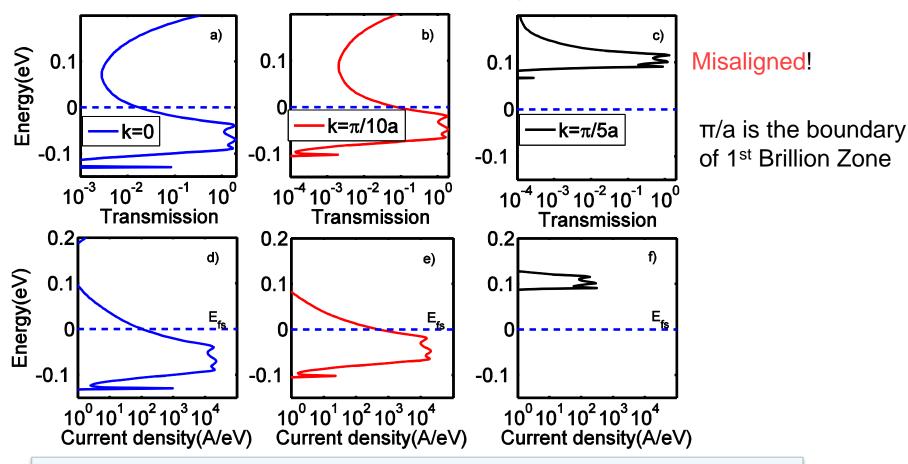

**Design Target 1**: steep Subthreshold Swing  $\rightarrow$  source  $E_f$  should be aligned with max of 1<sup>st</sup> miniband

High Energy electrons: Low transmission

However, the max of 1<sup>st</sup> miniband varies with k<sub>t</sub>

The max of 1st miniband is misaligned with Ef at high kt.

→ Does steep S.S. hold?

Steep SS still hold, because small k<sub>t</sub> carries most current.

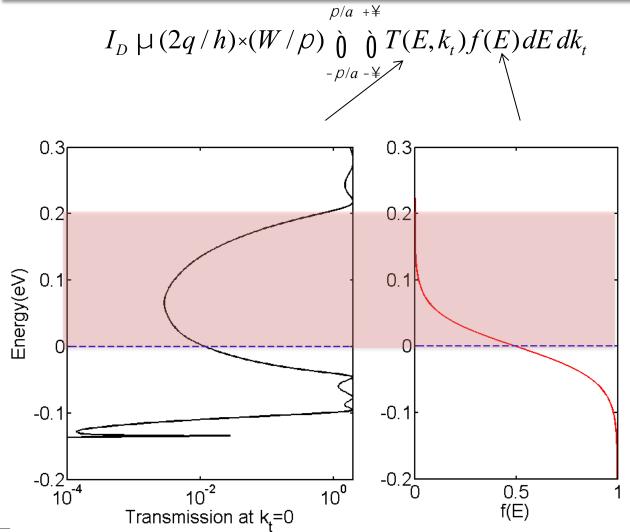

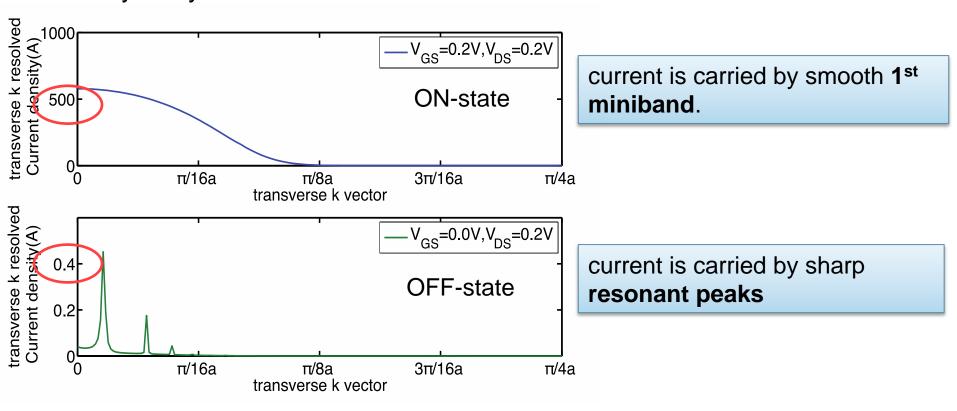

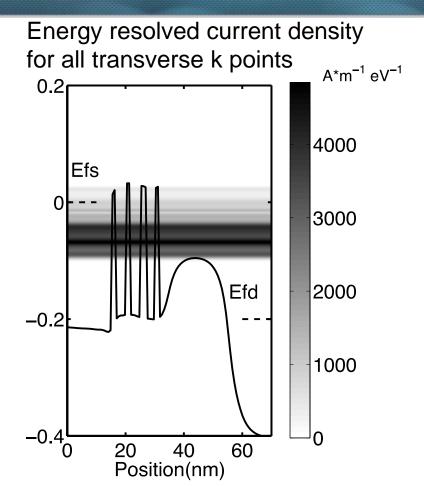

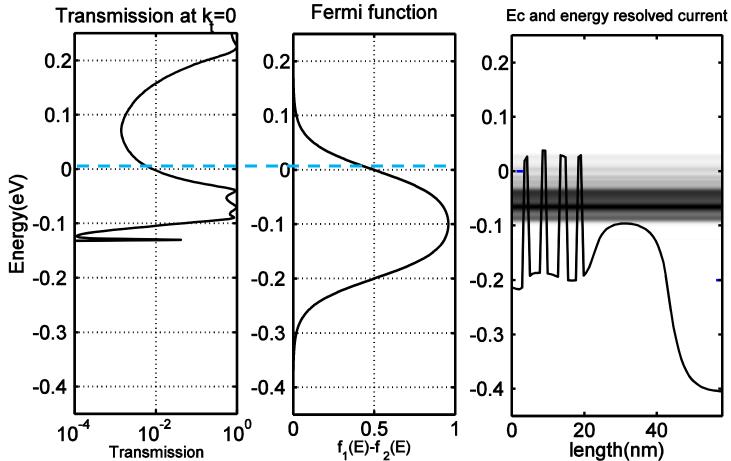

# Transverse k resolved current density

- At high k, the 1<sup>st</sup> miniband is far away from the source E<sub>f</sub>.

- → Less electrons are conducting.

- → They carry much less current than k=0.

Current is always carried by small k<sub>t</sub>.

- OFF-state: current carried by narrow resonance peaks.

- ON-state: current carried by 1st miniband.

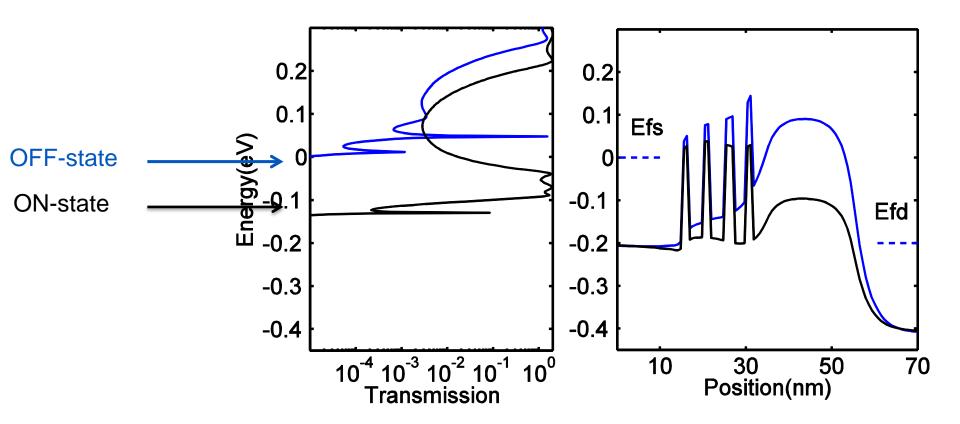

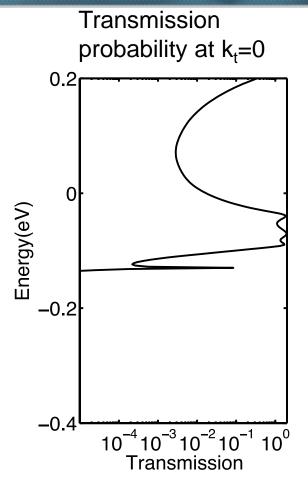

### Energy resolved current density

Current density is strongly confined to the  $1^{st}$  miniband of  $k_t$ =0. Current contribution from higher  $k_t$  are small

# Design target 1: steep Subthreshold Swing

### • Conclusion:

- » source Ef should be aligned with upper edge of 1st miniband for small kt.

- » High k<sub>t</sub> carriers little current

Design Target 2: maximum I<sub>on</sub> → minimize fluctuations in 1<sup>st</sup> miniband → adjust barrier thickness

|                | miniband                                 | minigap                                     |

|----------------|------------------------------------------|---------------------------------------------|

| Thin barriers  | small fluctuations(big I <sub>on</sub> ) | bigger transmission (big I <sub>off</sub> ) |

|                |                                          |                                             |

| Thick barriers | big fluctuations(big I <sub>on</sub> )   | small transmission (low I <sub>off</sub> )  |

|                |                                          |                                             |

How to balance between off-state and on-state performance?

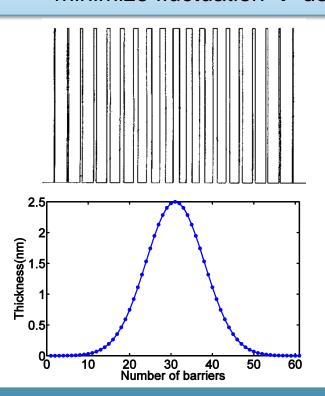

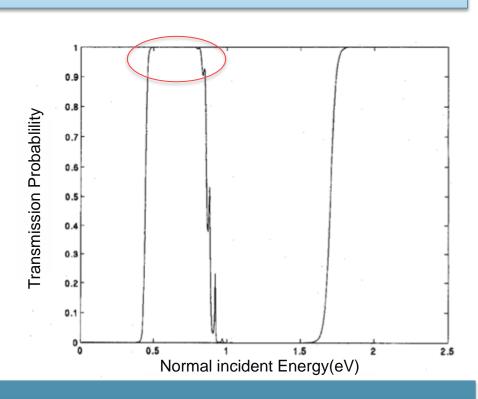

# Maximum I<sub>on</sub>: design guideline

Similar to designing a band-pass wave filter:

fluctuation comes from mismatch between contact and heterojunction minimize fluctuation → decrease the mismatch

#### **Conclusion:**

Barrier thickness close to Gaussian distribution → flat miniband → maximum I<sub>on</sub>

Tung H H, Lee C P.. Quantum Electronics, IEEE Journal of, 1996, 32(12): 2122-2127.

- However, too many barriers add to the total length of the device.

- A 4-barrier superlattice is optimized following the "graded barrier" guideline.

Design 3 has the flattest passband → the biggest on-current

\*One monolayer is made up of one layer of cations and one layer of anions.

- Design 3 has the flattest passband → biggest I<sub>on</sub>

- Superlattice MOSFET has better S.S. and higher I<sub>on</sub> than conventional MOSFETs

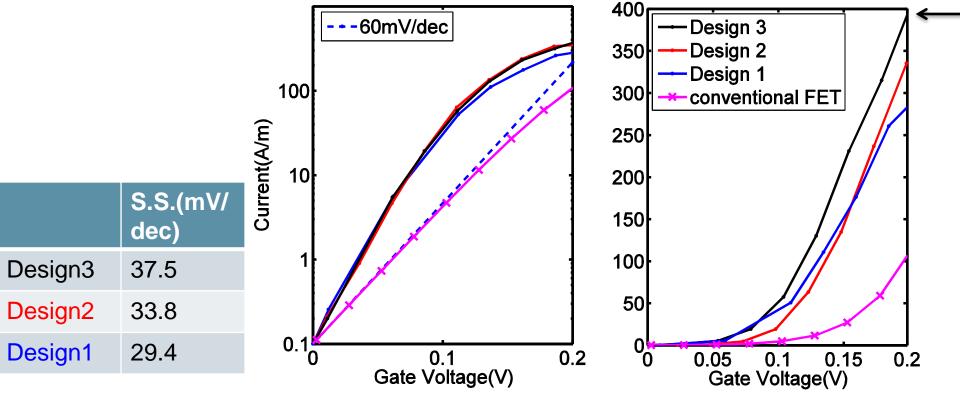

**Result**: The current saturates at  $\sim 0.2V$  for  $V_{gs}$ =0.2V .

Reason: 1st miniband is no wider than 0.2eV

Conclusion: This device should work under low V<sub>DD</sub>

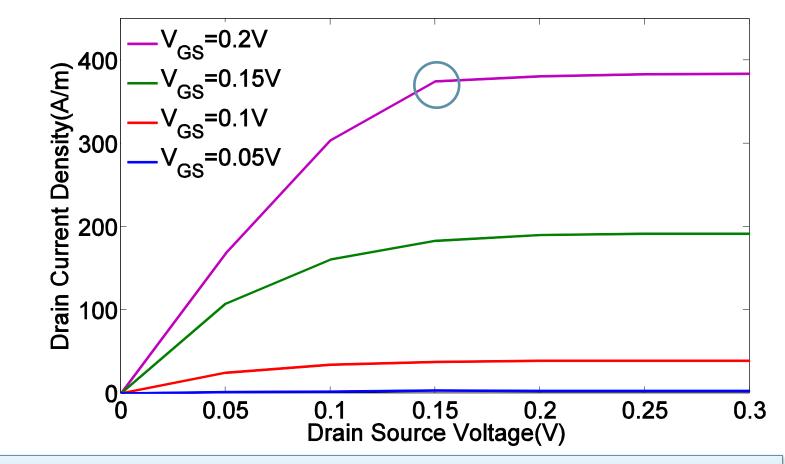

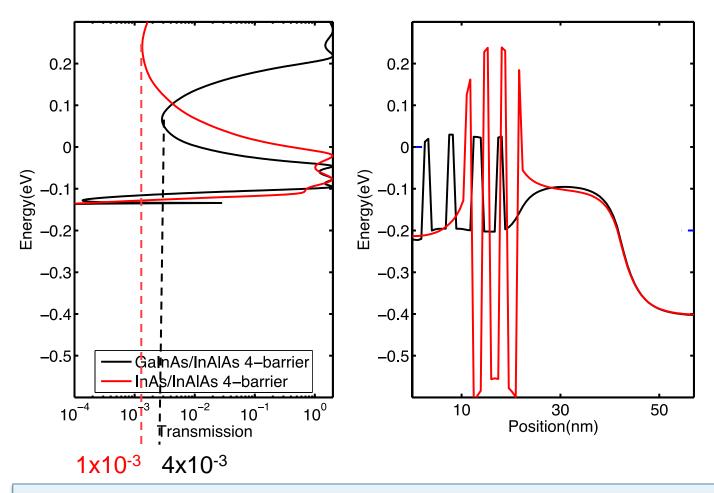

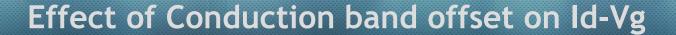

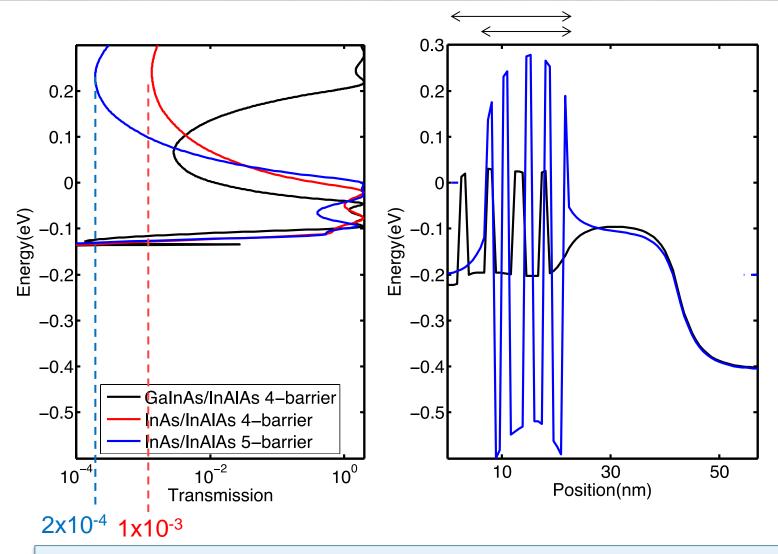

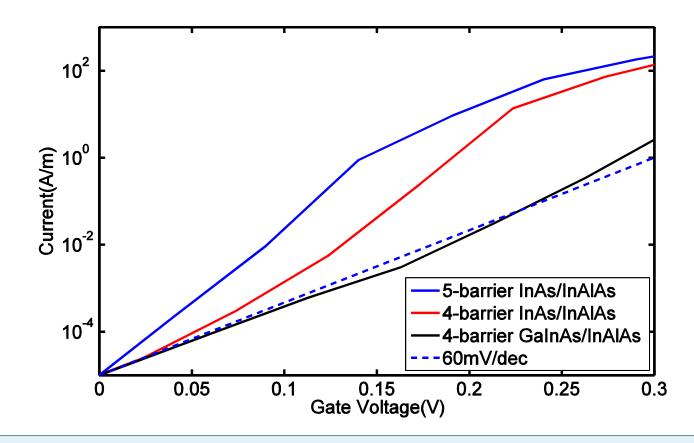

- Motivation: InAs/InAlAs superlattice has a bigger band offset than InGaAs/InAlAs.

- → lower transmission in the minigap

- → lower I<sub>off</sub>

Vurgaftman I, Meyer J R, Ram-Mohan L R.. *Journal of applied physics*, 2001, 89(11): 5815-5875.

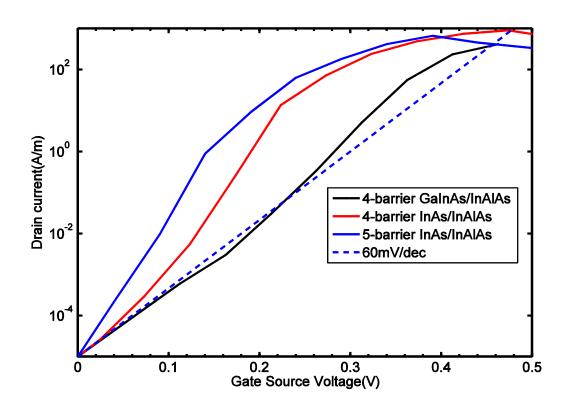

- Transmission in the minigap reaches ~1x10<sup>-3</sup>

- 1st Miniband is wider, carries more current

1x10<sup>-5</sup>A/m Low power VLSI I<sub>off</sub> standard is used.

InAs/InAlAs shows both sharper S.S. and higher ON/OFF ratio

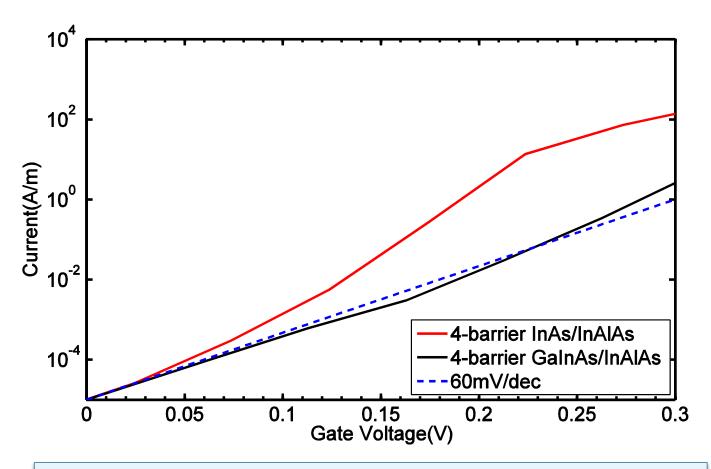

- InAs has a lower E<sub>c</sub> than InGaAs.

- To still align max of 1st miniband with source E<sub>f</sub>

→ thinner InAs wells

**Conclusion**: For InAs, we can fit more superlattice periods to fit into the same length.

Transmission in the minigap reaches ~1x10<sup>-3</sup> in 5 barrier design The length of InAs/InAlAs superlattice is no longer than InGaAs/InAlAs

Using 10<sup>-5</sup>A/m as I<sub>off</sub>, the 5-barrier design has the steepest S.S. and biggest I<sub>on</sub>/I<sub>off</sub> ratio

**Conclusion**: InAs/InAlAs superlattice may be more suitable for low power applications than InGaAs/InAlAs superlattice MOSFET.

- InAs and InAlAs have different lattice constant.

- If the structure is relaxed, there might be strain in both InAs and InAlAs.

- $\rightarrow$  E<sub>c</sub> and 1<sup>st</sup> miniband might shift.

- Conclusion: The optimum design might be different from discussed above.

- Currently we don't have strain tight binding parameters for InAlAs.

- Future work: relaxes the structure and then calculates transport.

### power density increase:

- » Reducing  $V_{\rm DD}$  can solve this problem, but causes increase in  $I_{\rm off}$

- Steep S.S. devices

- » adding an energy filter can reduce S.S. to steeper than 60mV/dec

- » TFET has sharp S.S., but limited I<sub>on</sub>

### Superlattice MOSFET

- » Nanowire superlattice MOSFETs have both sharp S.S. and big  $I_{\text{on}}$ , but hard to get high  $I_{\text{on}}$  per die.

- » We propose 2D superlattice MOSFET

### Design and simulation

- » Most of the current carried by small wave vector k<sub>t</sub>

- » Wells and barriers are adjusted for max I<sub>on</sub>

### Material Optimization

- » Bigger band offset, InAs/InAlAs gives smaller Ioff

- » 5-barrier design gives sharper S.S. and higher I<sub>on</sub>/I<sub>off</sub> ratio.

#### Committee members:

Prof. Klimeck, Prof. Rodwell, Prof. Ye

Faculty members and group members:

Prof. Povolotskyi, Prof. Kubis

Bozidar Novakovic, Jun Huang, Zhengping Jiang, Yaohua Tan, Yu He, Xufeng Wang and all other NCN friends for help and thoughtful discussions

# Radical transport vs planar transport

- Radial transport might result in different confinement.

- To maintain the desired transmission, wells and barrier thickness need to be adjusted.

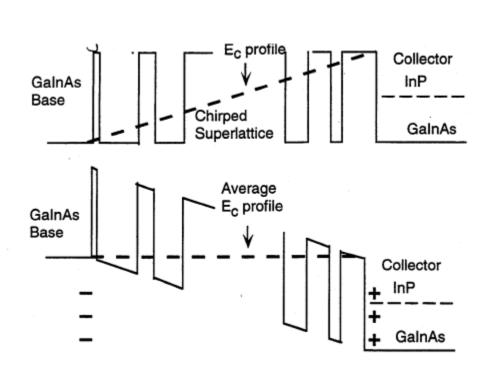

### Superlattice in both source & drain

- Output characteristics might be distorted.

- This can be eliminated by growing the source and drain separately.

Nguyen C, Sun H C, Liu T. Chirped superlattice hot electron transistor[C]//Device Research Conference, 1995. Digest. 1995 53rd Annual. IEEE, 1995: 82-83.

# Exact design for InAs/InAlAs superlattice

- 4-barrier design:3ml, 5.5ml, 5.5ml and 3ml thick InAlAs barriers, and

6.5ml, 7.5ml 6.5ml thick InAs wells.

- 5-barrier design: 3ml, 5.5ml, 5.5ml, 5.5ml, 5.5ml, 3ml InAlAs barriers, and 6ml, 8ml, 8ml, 6ml InAs wells,